Representation of each machine instruction. More...

#include "llvm/CodeGen/MachineInstr.h"

Public Types | |

| enum | CommentFlag { ReloadReuse = 0x1, NoSchedComment = 0x2, TAsmComments = 0x4 } |

| Flags to specify different kinds of comments to output in assembly code. More... | |

| enum | MIFlag { NoFlags = 0, FrameSetup = 1 << 0, FrameDestroy = 1 << 1, BundledPred = 1 << 2, BundledSucc = 1 << 3, FmNoNans = 1 << 4, FmNoInfs = 1 << 5, FmNsz = 1 << 6, FmArcp = 1 << 7, FmContract = 1 << 8, FmAfn = 1 << 9, FmReassoc = 1 << 10, NoUWrap = 1 << 11, NoSWrap = 1 << 12, IsExact = 1 << 13 } |

| enum | QueryType { IgnoreBundle, AnyInBundle, AllInBundle } |

| API for querying MachineInstr properties. More... | |

| enum | MICheckType { CheckDefs, CheckKillDead, IgnoreDefs, IgnoreVRegDefs } |

| using | mmo_iterator = ArrayRef< MachineMemOperand * >::iterator |

| using | mop_iterator = MachineOperand * |

| iterator/begin/end - Iterate over all operands of a machine instruction. More... | |

| using | const_mop_iterator = const MachineOperand * |

Public Member Functions | |

| MachineInstr (const MachineInstr &)=delete | |

| MachineInstr & | operator= (const MachineInstr &)=delete |

| ~MachineInstr ()=delete | |

| const MachineBasicBlock * | getParent () const |

| MachineBasicBlock * | getParent () |

| const MachineFunction * | getMF () const |

| Return the function that contains the basic block that this instruction belongs to. More... | |

| MachineFunction * | getMF () |

| uint8_t | getAsmPrinterFlags () const |

| Return the asm printer flags bitvector. More... | |

| void | clearAsmPrinterFlags () |

| Clear the AsmPrinter bitvector. More... | |

| bool | getAsmPrinterFlag (CommentFlag Flag) const |

| Return whether an AsmPrinter flag is set. More... | |

| void | setAsmPrinterFlag (uint8_t Flag) |

| Set a flag for the AsmPrinter. More... | |

| void | clearAsmPrinterFlag (CommentFlag Flag) |

| Clear specific AsmPrinter flags. More... | |

| uint16_t | getFlags () const |

| Return the MI flags bitvector. More... | |

| bool | getFlag (MIFlag Flag) const |

| Return whether an MI flag is set. More... | |

| void | setFlag (MIFlag Flag) |

| Set a MI flag. More... | |

| void | setFlags (unsigned flags) |

| void | clearFlag (MIFlag Flag) |

| clearFlag - Clear a MI flag. More... | |

| bool | isInsideBundle () const |

| Return true if MI is in a bundle (but not the first MI in a bundle). More... | |

| bool | isBundled () const |

| Return true if this instruction part of a bundle. More... | |

| bool | isBundledWithPred () const |

| Return true if this instruction is part of a bundle, and it is not the first instruction in the bundle. More... | |

| bool | isBundledWithSucc () const |

| Return true if this instruction is part of a bundle, and it is not the last instruction in the bundle. More... | |

| void | bundleWithPred () |

| Bundle this instruction with its predecessor. More... | |

| void | bundleWithSucc () |

| Bundle this instruction with its successor. More... | |

| void | unbundleFromPred () |

| Break bundle above this instruction. More... | |

| void | unbundleFromSucc () |

| Break bundle below this instruction. More... | |

| const DebugLoc & | getDebugLoc () const |

| Returns the debug location id of this MachineInstr. More... | |

| const DILocalVariable * | getDebugVariable () const |

| Return the debug variable referenced by this DBG_VALUE instruction. More... | |

| const DIExpression * | getDebugExpression () const |

| Return the complex address expression referenced by this DBG_VALUE instruction. More... | |

| const DILabel * | getDebugLabel () const |

| Return the debug label referenced by this DBG_LABEL instruction. More... | |

| void | emitError (StringRef Msg) const |

| Emit an error referring to the source location of this instruction. More... | |

| const MCInstrDesc & | getDesc () const |

| Returns the target instruction descriptor of this MachineInstr. More... | |

| unsigned | getOpcode () const |

| Returns the opcode of this MachineInstr. More... | |

| unsigned | getNumOperands () const |

| Retuns the total number of operands. More... | |

| const MachineOperand & | getOperand (unsigned i) const |

| MachineOperand & | getOperand (unsigned i) |

| unsigned | getNumDefs () const |

| Returns the total number of definitions. More... | |

| bool | isOperandSubregIdx (unsigned OpIdx) const |

Return true if operand OpIdx is a subregister index. More... | |

| unsigned | getNumExplicitOperands () const |

| Returns the number of non-implicit operands. More... | |

| unsigned | getNumExplicitDefs () const |

| Returns the number of non-implicit definitions. More... | |

| mop_iterator | operands_begin () |

| mop_iterator | operands_end () |

| const_mop_iterator | operands_begin () const |

| const_mop_iterator | operands_end () const |

| iterator_range< mop_iterator > | operands () |

| iterator_range< const_mop_iterator > | operands () const |

| iterator_range< mop_iterator > | explicit_operands () |

| iterator_range< const_mop_iterator > | explicit_operands () const |

| iterator_range< mop_iterator > | implicit_operands () |

| iterator_range< const_mop_iterator > | implicit_operands () const |

| iterator_range< mop_iterator > | defs () |

| Returns a range over all explicit operands that are register definitions. More... | |

| iterator_range< const_mop_iterator > | defs () const |

| Returns a range over all explicit operands that are register definitions. More... | |

| iterator_range< mop_iterator > | uses () |

| Returns a range that includes all operands that are register uses. More... | |

| iterator_range< const_mop_iterator > | uses () const |

| Returns a range that includes all operands that are register uses. More... | |

| iterator_range< mop_iterator > | explicit_uses () |

| iterator_range< const_mop_iterator > | explicit_uses () const |

| unsigned | getOperandNo (const_mop_iterator I) const |

Returns the number of the operand iterator I points to. More... | |

| ArrayRef< MachineMemOperand * > | memoperands () const |

| Access to memory operands of the instruction. More... | |

| mmo_iterator | memoperands_begin () const |

| Access to memory operands of the instruction. More... | |

| mmo_iterator | memoperands_end () const |

| Access to memory operands of the instruction. More... | |

| bool | memoperands_empty () const |

| Return true if we don't have any memory operands which described the memory access done by this instruction. More... | |

| bool | hasOneMemOperand () const |

| Return true if this instruction has exactly one MachineMemOperand. More... | |

| unsigned | getNumMemOperands () const |

| Return the number of memory operands. More... | |

| MCSymbol * | getPreInstrSymbol () const |

| Helper to extract a pre-instruction symbol if one has been added. More... | |

| MCSymbol * | getPostInstrSymbol () const |

| Helper to extract a post-instruction symbol if one has been added. More... | |

| bool | hasProperty (unsigned MCFlag, QueryType Type=AnyInBundle) const |

| Return true if the instruction (or in the case of a bundle, the instructions inside the bundle) has the specified property. More... | |

| bool | isVariadic (QueryType Type=IgnoreBundle) const |

| Return true if this instruction can have a variable number of operands. More... | |

| bool | hasOptionalDef (QueryType Type=IgnoreBundle) const |

| Set if this instruction has an optional definition, e.g. More... | |

| bool | isPseudo (QueryType Type=IgnoreBundle) const |

| Return true if this is a pseudo instruction that doesn't correspond to a real machine instruction. More... | |

| bool | isReturn (QueryType Type=AnyInBundle) const |

| bool | isEHScopeReturn (QueryType Type=AnyInBundle) const |

| Return true if this is an instruction that marks the end of an EH scope, i.e., a catchpad or a cleanuppad instruction. More... | |

| bool | isCall (QueryType Type=AnyInBundle) const |

| bool | isBarrier (QueryType Type=AnyInBundle) const |

| Returns true if the specified instruction stops control flow from executing the instruction immediately following it. More... | |

| bool | isTerminator (QueryType Type=AnyInBundle) const |

| Returns true if this instruction part of the terminator for a basic block. More... | |

| bool | isBranch (QueryType Type=AnyInBundle) const |

| Returns true if this is a conditional, unconditional, or indirect branch. More... | |

| bool | isIndirectBranch (QueryType Type=AnyInBundle) const |

| Return true if this is an indirect branch, such as a branch through a register. More... | |

| bool | isConditionalBranch (QueryType Type=AnyInBundle) const |

| Return true if this is a branch which may fall through to the next instruction or may transfer control flow to some other block. More... | |

| bool | isUnconditionalBranch (QueryType Type=AnyInBundle) const |

| Return true if this is a branch which always transfers control flow to some other block. More... | |

| bool | isPredicable (QueryType Type=AllInBundle) const |

| Return true if this instruction has a predicate operand that controls execution. More... | |

| bool | isCompare (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a comparison. More... | |

| bool | isMoveImmediate (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a move immediate (including conditional moves) instruction. More... | |

| bool | isMoveReg (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a register move. More... | |

| bool | isBitcast (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a bitcast instruction. More... | |

| bool | isSelect (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a select instruction. More... | |

| bool | isNotDuplicable (QueryType Type=AnyInBundle) const |

| Return true if this instruction cannot be safely duplicated. More... | |

| bool | isConvergent (QueryType Type=AnyInBundle) const |

| Return true if this instruction is convergent. More... | |

| bool | hasDelaySlot (QueryType Type=AnyInBundle) const |

| Returns true if the specified instruction has a delay slot which must be filled by the code generator. More... | |

| bool | canFoldAsLoad (QueryType Type=IgnoreBundle) const |

| Return true for instructions that can be folded as memory operands in other instructions. More... | |

| bool | isRegSequenceLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic REG_SEQUENCE instructions. More... | |

| bool | isExtractSubregLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic EXTRACT_SUBREG instructions. More... | |

| bool | isInsertSubregLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic INSERT_SUBREG instructions. More... | |

| bool | mayLoad (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly read memory. More... | |

| bool | mayStore (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly modify memory. More... | |

| bool | mayLoadOrStore (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly read or modify memory. More... | |

| bool | isCommutable (QueryType Type=IgnoreBundle) const |

| Return true if this may be a 2- or 3-address instruction (of the form "X = op Y, Z, ..."), which produces the same result if Y and Z are exchanged. More... | |

| bool | isConvertibleTo3Addr (QueryType Type=IgnoreBundle) const |

| Return true if this is a 2-address instruction which can be changed into a 3-address instruction if needed. More... | |

| bool | usesCustomInsertionHook (QueryType Type=IgnoreBundle) const |

| Return true if this instruction requires custom insertion support when the DAG scheduler is inserting it into a machine basic block. More... | |

| bool | hasPostISelHook (QueryType Type=IgnoreBundle) const |

| Return true if this instruction requires adjustment after instruction selection by calling a target hook. More... | |

| bool | isRematerializable (QueryType Type=AllInBundle) const |

| Returns true if this instruction is a candidate for remat. More... | |

| bool | isAsCheapAsAMove (QueryType Type=AllInBundle) const |

| Returns true if this instruction has the same cost (or less) than a move instruction. More... | |

| bool | hasExtraSrcRegAllocReq (QueryType Type=AnyInBundle) const |

| Returns true if this instruction source operands have special register allocation requirements that are not captured by the operand register classes. More... | |

| bool | hasExtraDefRegAllocReq (QueryType Type=AnyInBundle) const |

| Returns true if this instruction def operands have special register allocation requirements that are not captured by the operand register classes. More... | |

| bool | isIdenticalTo (const MachineInstr &Other, MICheckType Check=CheckDefs) const |

Return true if this instruction is identical to Other. More... | |

| MachineInstr * | removeFromParent () |

| Unlink 'this' from the containing basic block, and return it without deleting it. More... | |

| MachineInstr * | removeFromBundle () |

| Unlink this instruction from its basic block and return it without deleting it. More... | |

| void | eraseFromParent () |

| Unlink 'this' from the containing basic block and delete it. More... | |

| void | eraseFromParentAndMarkDBGValuesForRemoval () |

| Unlink 'this' from the containing basic block and delete it. More... | |

| void | eraseFromBundle () |

| Unlink 'this' form its basic block and delete it. More... | |

| bool | isEHLabel () const |

| bool | isGCLabel () const |

| bool | isAnnotationLabel () const |

| bool | isLabel () const |

| Returns true if the MachineInstr represents a label. More... | |

| bool | isCFIInstruction () const |

| bool | isPosition () const |

| bool | isDebugValue () const |

| bool | isDebugLabel () const |

| bool | isDebugInstr () const |

| bool | isIndirectDebugValue () const |

| A DBG_VALUE is indirect iff the first operand is a register and the second operand is an immediate. More... | |

| bool | isPHI () const |

| bool | isKill () const |

| bool | isImplicitDef () const |

| bool | isInlineAsm () const |

| bool | isMSInlineAsm () const |

| bool | isStackAligningInlineAsm () const |

| InlineAsm::AsmDialect | getInlineAsmDialect () const |

| bool | isInsertSubreg () const |

| bool | isSubregToReg () const |

| bool | isRegSequence () const |

| bool | isBundle () const |

| bool | isCopy () const |

| bool | isFullCopy () const |

| bool | isExtractSubreg () const |

| bool | isCopyLike () const |

| Return true if the instruction behaves like a copy. More... | |

| bool | isIdentityCopy () const |

| Return true is the instruction is an identity copy. More... | |

| bool | isMetaInstruction () const |

| Return true if this instruction doesn't produce any output in the form of executable instructions. More... | |

| bool | isTransient () const |

| Return true if this is a transient instruction that is either very likely to be eliminated during register allocation (such as copy-like instructions), or if this instruction doesn't have an execution-time cost. More... | |

| unsigned | getBundleSize () const |

| Return the number of instructions inside the MI bundle, excluding the bundle header. More... | |

| bool | readsRegister (unsigned Reg, const TargetRegisterInfo *TRI=nullptr) const |

| Return true if the MachineInstr reads the specified register. More... | |

| bool | readsVirtualRegister (unsigned Reg) const |

| Return true if the MachineInstr reads the specified virtual register. More... | |

| std::pair< bool, bool > | readsWritesVirtualRegister (unsigned Reg, SmallVectorImpl< unsigned > *Ops=nullptr) const |

| Return a pair of bools (reads, writes) indicating if this instruction reads or writes Reg. More... | |

| bool | killsRegister (unsigned Reg, const TargetRegisterInfo *TRI=nullptr) const |

| Return true if the MachineInstr kills the specified register. More... | |

| bool | definesRegister (unsigned Reg, const TargetRegisterInfo *TRI=nullptr) const |

| Return true if the MachineInstr fully defines the specified register. More... | |

| bool | modifiesRegister (unsigned Reg, const TargetRegisterInfo *TRI) const |

| Return true if the MachineInstr modifies (fully define or partially define) the specified register. More... | |

| bool | registerDefIsDead (unsigned Reg, const TargetRegisterInfo *TRI=nullptr) const |

| Returns true if the register is dead in this machine instruction. More... | |

| bool | hasRegisterImplicitUseOperand (unsigned Reg) const |

| Returns true if the MachineInstr has an implicit-use operand of exactly the given register (not considering sub/super-registers). More... | |

| int | findRegisterUseOperandIdx (unsigned Reg, bool isKill=false, const TargetRegisterInfo *TRI=nullptr) const |

| Returns the operand index that is a use of the specific register or -1 if it is not found. More... | |

| MachineOperand * | findRegisterUseOperand (unsigned Reg, bool isKill=false, const TargetRegisterInfo *TRI=nullptr) |

| Wrapper for findRegisterUseOperandIdx, it returns a pointer to the MachineOperand rather than an index. More... | |

| const MachineOperand * | findRegisterUseOperand (unsigned Reg, bool isKill=false, const TargetRegisterInfo *TRI=nullptr) const |

| int | findRegisterDefOperandIdx (unsigned Reg, bool isDead=false, bool Overlap=false, const TargetRegisterInfo *TRI=nullptr) const |

| Returns the operand index that is a def of the specified register or -1 if it is not found. More... | |

| MachineOperand * | findRegisterDefOperand (unsigned Reg, bool isDead=false, const TargetRegisterInfo *TRI=nullptr) |

| Wrapper for findRegisterDefOperandIdx, it returns a pointer to the MachineOperand rather than an index. More... | |

| int | findFirstPredOperandIdx () const |

| Find the index of the first operand in the operand list that is used to represent the predicate. More... | |

| int | findInlineAsmFlagIdx (unsigned OpIdx, unsigned *GroupNo=nullptr) const |

| Find the index of the flag word operand that corresponds to operand OpIdx on an inline asm instruction. More... | |

| const TargetRegisterClass * | getRegClassConstraint (unsigned OpIdx, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI) const |

| Compute the static register class constraint for operand OpIdx. More... | |

| const TargetRegisterClass * | getRegClassConstraintEffectForVReg (unsigned Reg, const TargetRegisterClass *CurRC, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI, bool ExploreBundle=false) const |

Applies the constraints (def/use) implied by this MI on Reg to the given CurRC. More... | |

| const TargetRegisterClass * | getRegClassConstraintEffect (unsigned OpIdx, const TargetRegisterClass *CurRC, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI) const |

Applies the constraints (def/use) implied by the OpIdx operand to the given CurRC. More... | |

| void | tieOperands (unsigned DefIdx, unsigned UseIdx) |

| Add a tie between the register operands at DefIdx and UseIdx. More... | |

| unsigned | findTiedOperandIdx (unsigned OpIdx) const |

| Given the index of a tied register operand, find the operand it is tied to. More... | |

| bool | isRegTiedToUseOperand (unsigned DefOpIdx, unsigned *UseOpIdx=nullptr) const |

| Given the index of a register def operand, check if the register def is tied to a source operand, due to either two-address elimination or inline assembly constraints. More... | |

| bool | isRegTiedToDefOperand (unsigned UseOpIdx, unsigned *DefOpIdx=nullptr) const |

| Return true if the use operand of the specified index is tied to a def operand. More... | |

| void | clearKillInfo () |

| Clears kill flags on all operands. More... | |

| void | substituteRegister (unsigned FromReg, unsigned ToReg, unsigned SubIdx, const TargetRegisterInfo &RegInfo) |

| Replace all occurrences of FromReg with ToReg:SubIdx, properly composing subreg indices where necessary. More... | |

| bool | addRegisterKilled (unsigned IncomingReg, const TargetRegisterInfo *RegInfo, bool AddIfNotFound=false) |

| We have determined MI kills a register. More... | |

| void | clearRegisterKills (unsigned Reg, const TargetRegisterInfo *RegInfo) |

| Clear all kill flags affecting Reg. More... | |

| bool | addRegisterDead (unsigned Reg, const TargetRegisterInfo *RegInfo, bool AddIfNotFound=false) |

| We have determined MI defined a register without a use. More... | |

| void | clearRegisterDeads (unsigned Reg) |

Clear all dead flags on operands defining register Reg. More... | |

| void | setRegisterDefReadUndef (unsigned Reg, bool IsUndef=true) |

Mark all subregister defs of register Reg with the undef flag. More... | |

| void | addRegisterDefined (unsigned Reg, const TargetRegisterInfo *RegInfo=nullptr) |

| We have determined MI defines a register. More... | |

| void | setPhysRegsDeadExcept (ArrayRef< unsigned > UsedRegs, const TargetRegisterInfo &TRI) |

| Mark every physreg used by this instruction as dead except those in the UsedRegs list. More... | |

| bool | isSafeToMove (AliasAnalysis *AA, bool &SawStore) const |

| Return true if it is safe to move this instruction. More... | |

| bool | mayAlias (AliasAnalysis *AA, MachineInstr &Other, bool UseTBAA) |

| Returns true if this instruction's memory access aliases the memory access of Other. More... | |

| bool | hasOrderedMemoryRef () const |

| Return true if this instruction may have an ordered or volatile memory reference, or if the information describing the memory reference is not available. More... | |

| bool | isDereferenceableInvariantLoad (AliasAnalysis *AA) const |

| Return true if this load instruction never traps and points to a memory location whose value doesn't change during the execution of this function. More... | |

| unsigned | isConstantValuePHI () const |

| If the specified instruction is a PHI that always merges together the same virtual register, return the register, otherwise return 0. More... | |

| bool | hasUnmodeledSideEffects () const |

| Return true if this instruction has side effects that are not modeled by mayLoad / mayStore, etc. More... | |

| bool | isLoadFoldBarrier () const |

| Returns true if it is illegal to fold a load across this instruction. More... | |

| bool | allDefsAreDead () const |

| Return true if all the defs of this instruction are dead. More... | |

| void | copyImplicitOps (MachineFunction &MF, const MachineInstr &MI) |

| Copy implicit register operands from specified instruction to this instruction. More... | |

| void | addOperand (MachineFunction &MF, const MachineOperand &Op) |

| Add the specified operand to the instruction. More... | |

| void | addOperand (const MachineOperand &Op) |

| Add an operand without providing an MF reference. More... | |

| void | setDesc (const MCInstrDesc &tid) |

| Replace the instruction descriptor (thus opcode) of the current instruction with a new one. More... | |

| void | setDebugLoc (DebugLoc dl) |

| Replace current source information with new such. More... | |

| void | RemoveOperand (unsigned OpNo) |

| Erase an operand from an instruction, leaving it with one fewer operand than it started with. More... | |

| void | dropMemRefs (MachineFunction &MF) |

| Clear this MachineInstr's memory reference descriptor list. More... | |

| void | setMemRefs (MachineFunction &MF, ArrayRef< MachineMemOperand *> MemRefs) |

| Assign this MachineInstr's memory reference descriptor list. More... | |

| void | addMemOperand (MachineFunction &MF, MachineMemOperand *MO) |

| Add a MachineMemOperand to the machine instruction. More... | |

| void | cloneMemRefs (MachineFunction &MF, const MachineInstr &MI) |

| Clone another MachineInstr's memory reference descriptor list and replace ours with it. More... | |

| void | cloneMergedMemRefs (MachineFunction &MF, ArrayRef< const MachineInstr *> MIs) |

| Clone the merge of multiple MachineInstrs' memory reference descriptors list and replace ours with it. More... | |

| void | setPreInstrSymbol (MachineFunction &MF, MCSymbol *Symbol) |

| Set a symbol that will be emitted just prior to the instruction itself. More... | |

| void | setPostInstrSymbol (MachineFunction &MF, MCSymbol *Symbol) |

| Set a symbol that will be emitted just after the instruction itself. More... | |

| uint16_t | mergeFlagsWith (const MachineInstr &Other) const |

| Return the MIFlags which represent both MachineInstrs. More... | |

| void | copyIRFlags (const Instruction &I) |

| Copy all flags to MachineInst MIFlags. More... | |

| void | untieRegOperand (unsigned OpIdx) |

| Break any tie involving OpIdx. More... | |

| void | addImplicitDefUseOperands (MachineFunction &MF) |

| Add all implicit def and use operands to this instruction. More... | |

| void | collectDebugValues (SmallVectorImpl< MachineInstr *> &DbgValues) |

| Scan instructions following MI and collect any matching DBG_VALUEs. More... | |

| void | changeDebugValuesDefReg (unsigned Reg) |

Find all DBG_VALUEs immediately following this instruction that point to a register def in this instruction and point them to Reg instead. More... | |

| LLT | getTypeToPrint (unsigned OpIdx, SmallBitVector &PrintedTypes, const MachineRegisterInfo &MRI) const |

| Debugging supportDetermine the generic type to be printed (if needed) on uses and defs. More... | |

| bool | hasComplexRegisterTies () const |

| Return true when an instruction has tied register that can't be determined by the instruction's descriptor. More... | |

| void | print (raw_ostream &OS, bool IsStandalone=true, bool SkipOpers=false, bool SkipDebugLoc=false, bool AddNewLine=true, const TargetInstrInfo *TII=nullptr) const |

Print this MI to OS. More... | |

| void | print (raw_ostream &OS, ModuleSlotTracker &MST, bool IsStandalone=true, bool SkipOpers=false, bool SkipDebugLoc=false, bool AddNewLine=true, const TargetInstrInfo *TII=nullptr) const |

| void | dump () const |

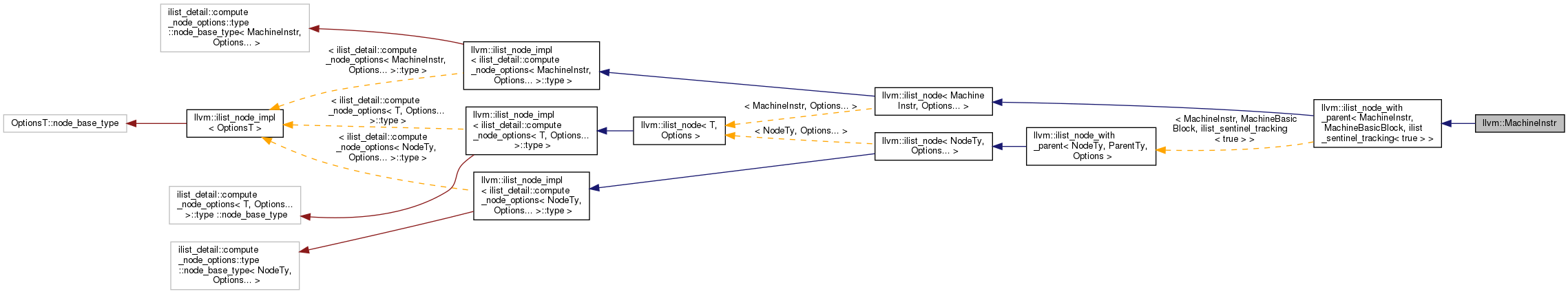

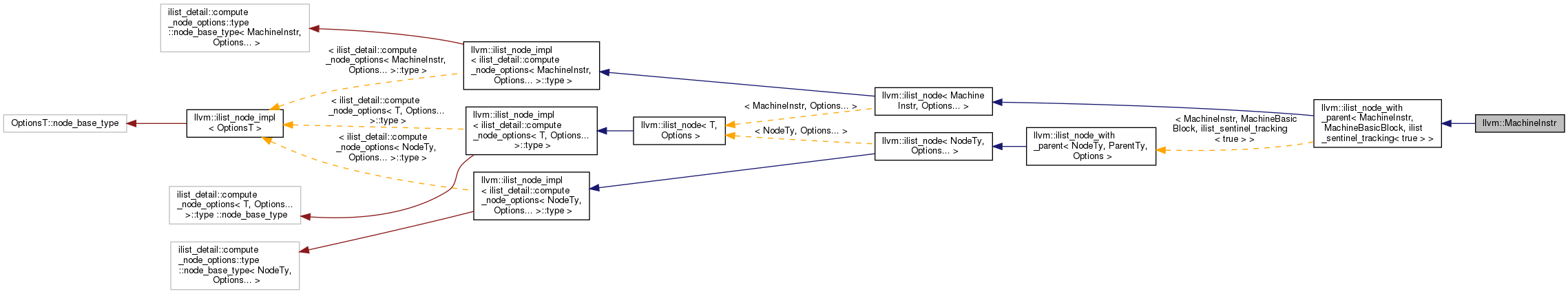

Public Member Functions inherited from llvm::ilist_node_with_parent< MachineInstr, MachineBasicBlock, ilist_sentinel_tracking< true > > Public Member Functions inherited from llvm::ilist_node_with_parent< MachineInstr, MachineBasicBlock, ilist_sentinel_tracking< true > > | |

| MachineInstr * | getPrevNode () |

| const MachineInstr * | getPrevNode () const |

Get the previous node, or nullptr for the list head. More... | |

| MachineInstr * | getNextNode () |

Get the next node, or nullptr for the list tail. More... | |

| const MachineInstr * | getNextNode () const |

Get the next node, or nullptr for the list tail. More... | |

Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type > Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type > | |

| self_iterator | getIterator () |

| const_self_iterator | getIterator () const |

| reverse_self_iterator | getReverseIterator () |

| const_reverse_self_iterator | getReverseIterator () const |

| bool | isSentinel () const |

| Check whether this is the sentinel node. More... | |

Friends | |

| struct | ilist_traits< MachineInstr > |

| struct | ilist_callback_traits< MachineBasicBlock > |

| class | MachineFunction |

Detailed Description

Representation of each machine instruction.

This class isn't a POD type, but it must have a trivial destructor. When a MachineFunction is deleted, all the contained MachineInstrs are deallocated without having their destructor called.

Definition at line 64 of file MachineInstr.h.

Member Typedef Documentation

◆ const_mop_iterator

Definition at line 451 of file MachineInstr.h.

◆ mmo_iterator

| using llvm::MachineInstr::mmo_iterator = ArrayRef<MachineMemOperand *>::iterator |

Definition at line 68 of file MachineInstr.h.

◆ mop_iterator

iterator/begin/end - Iterate over all operands of a machine instruction.

Definition at line 450 of file MachineInstr.h.

Member Enumeration Documentation

◆ CommentFlag

Flags to specify different kinds of comments to output in assembly code.

These flags carry semantic information not otherwise easily derivable from the IR text.

| Enumerator | |

|---|---|

| ReloadReuse | |

| NoSchedComment | |

| TAsmComments | |

Definition at line 74 of file MachineInstr.h.

◆ MICheckType

| Enumerator | |

|---|---|

| CheckDefs | |

| CheckKillDead | |

| IgnoreDefs | |

| IgnoreVRegDefs | |

Definition at line 931 of file MachineInstr.h.

◆ MIFlag

| Enumerator | |

|---|---|

| NoFlags | |

| FrameSetup | |

| FrameDestroy | |

| BundledPred | |

| BundledSucc | |

| FmNoNans | |

| FmNoInfs | |

| FmNsz | |

| FmArcp | |

| FmContract | |

| FmAfn | |

| FmReassoc | |

| NoUWrap | |

| NoSWrap | |

| IsExact | |

Definition at line 80 of file MachineInstr.h.

◆ QueryType

API for querying MachineInstr properties.

They are the same as MCInstrDesc queries but they are bundle aware.

| Enumerator | |

|---|---|

| IgnoreBundle | |

| AnyInBundle | |

| AllInBundle | |

Definition at line 581 of file MachineInstr.h.

Constructor & Destructor Documentation

◆ MachineInstr()

|

delete |

◆ ~MachineInstr()

|

delete |

Member Function Documentation

◆ addImplicitDefUseOperands()

| void MachineInstr::addImplicitDefUseOperands | ( | MachineFunction & | MF | ) |

Add all implicit def and use operands to this instruction.

Definition at line 102 of file MachineInstr.cpp.

References addOperand(), llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::MachineFunction::allocateOperandArray(), assert(), llvm::MachineOperand::CreateReg(), getDebugLoc(), getDesc(), llvm::MCInstrDesc::getImplicitDefs(), llvm::MCInstrDesc::getImplicitUses(), llvm::MCInstrDesc::getNumImplicitDefs(), llvm::MCInstrDesc::getNumImplicitUses(), llvm::MCInstrDesc::getNumOperands(), getNumOperands(), getParent(), llvm::DebugLoc::hasTrivialDestructor(), llvm::MCInstrDesc::ImplicitDefs, llvm::MCInstrDesc::ImplicitUses, MI, MRI, operands(), llvm::MachineRegisterInfo::removeRegOperandFromUseList(), and setFlags().

Referenced by buildEXP(), llvm::SIInstrInfo::FoldImmediate(), hoistAndMergeSGPRInits(), llvm::SIInstrInfo::moveToVALU(), and untieRegOperand().

◆ addMemOperand()

| void MachineInstr::addMemOperand | ( | MachineFunction & | MF, |

| MachineMemOperand * | MO | ||

| ) |

Add a MachineMemOperand to the machine instruction.

This function should be used only occasionally. The setMemRefs function is the primary method for setting up a MachineInstr's MemRefs list.

Definition at line 360 of file MachineInstr.cpp.

References llvm::SmallVectorImpl< T >::append(), memoperands_begin(), memoperands_end(), llvm::SmallVectorTemplateBase< T >::push_back(), and setMemRefs().

Referenced by llvm::MachineInstrBuilder::addMemOperand(), computeBytesPoppedByCalleeForSRet(), llvm::TargetLoweringBase::emitPatchPoint(), llvm::TargetInstrInfo::foldMemoryOperand(), and setDebugLoc().

◆ addOperand() [1/2]

| void MachineInstr::addOperand | ( | MachineFunction & | MF, |

| const MachineOperand & | Op | ||

| ) |

Add the specified operand to the instruction.

addOperand - Add the specified operand to the instruction.

If it is an implicit operand, it is added to the end of the operand list. If it is an explicit operand it is added at the end of the explicit operand list (before the first implicit operand).

MF must be the machine function that was used to allocate this instruction.

MachineInstrBuilder provides a more convenient interface for creating instructions and adding operands.

If it is an implicit operand, it is added to the end of the operand list. If it is an explicit operand it is added at the end of the explicit operand list (before the first implicit operand).

Definition at line 199 of file MachineInstr.cpp.

References llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::MachineFunction::allocateOperandArray(), assert(), llvm::MachineFunction::deallocateOperandArray(), llvm::MCOI::EARLY_CLOBBER, llvm::MCInstrDesc::getNumOperands(), getNumOperands(), llvm::MCInstrDesc::getOperandConstraint(), llvm::MachineOperand::getType(), llvm::MachineOperand::isImplicit(), isInlineAsm(), isReg(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), llvm::MachineOperand::isUse(), llvm::MCInstrDesc::isVariadic(), llvm::MachineOperand::MO_MCSymbol, llvm::MachineOperand::MO_Metadata, moveOperands(), llvm::MachineOperand::Reg, llvm::MachineOperand::setIsEarlyClobber(), llvm::MCOI::TIED_TO, and tieOperands().

Referenced by llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addBlockAddress(), llvm::MachineInstrBuilder::addCFIIndex(), llvm::MachineInstrBuilder::addCImm(), llvm::MachineInstrBuilder::addConstantPoolIndex(), llvm::MachineInstrBuilder::addExternalSymbol(), llvm::MachineInstrBuilder::addFPImm(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addGlobalAddress(), llvm::MachineInstrBuilder::addImm(), addImplicitDefUseOperands(), llvm::MachineInstrBuilder::addIntrinsicID(), llvm::MachineInstrBuilder::addJumpTableIndex(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addMetadata(), addOperand(), llvm::MachineInstrBuilder::addPredicate(), llvm::MachineInstrBuilder::addReg(), addRegisterDead(), addRegisterDefined(), addRegisterKilled(), llvm::MachineInstrBuilder::addRegMask(), llvm::MachineInstrBuilder::addSym(), llvm::MachineInstrBuilder::addTargetIndex(), AppendEndToFunction(), llvm::SIInstrInfo::buildExtractSubRegOrImm(), changeFCMPPredToAArch64CC(), ConvertImplicitDefToConstZero(), copyExtraImplicitOps(), copyImplicitOps(), createPHIsForSelects(), llvm::createSIFixWWMLivenessPass(), llvm::XCoreFrameLowering::emitEpilogue(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::HexagonFrameLowering::emitPrologue(), enableAllocFrameElim(), fixupGlobalSaddr(), llvm::HexagonFrameLowering::getAlignaInstr(), getLeaOP(), llvm::LiveVariables::HandleVirtRegDef(), ImposeStackOrdering(), INITIALIZE_PASS(), isCopy(), isImmValidForOpcode(), isRegTiedToDefOperand(), llvm::SIInstrInfo::moveToVALU(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::HexagonInstrInfo::PredicateInstruction(), llvm::rewriteT2FrameIndex(), and swapMIOperands().

◆ addOperand() [2/2]

| void MachineInstr::addOperand | ( | const MachineOperand & | Op | ) |

Add an operand without providing an MF reference.

This only works for instructions that are inserted in a basic block.

MachineInstrBuilder and the two-argument addOperand(MF, MO) should be preferred.

Definition at line 176 of file MachineInstr.cpp.

References addOperand(), assert(), llvm::MachineBasicBlock::getParent(), and getParent().

◆ addRegisterDead()

| bool MachineInstr::addRegisterDead | ( | unsigned | Reg, |

| const TargetRegisterInfo * | RegInfo, | ||

| bool | AddIfNotFound = false |

||

| ) |

We have determined MI defined a register without a use.

Look for the operand that defines it and mark it as IsDead. If AddIfNotFound is true, add a implicit operand if it's not found. Returns true if the operand exists / is added.

Definition at line 1837 of file MachineInstr.cpp.

References addOperand(), llvm::SmallVectorTemplateCommon< T, typename >::back(), llvm::MachineOperand::CreateReg(), llvm::SmallVectorBase::empty(), findInlineAsmFlagIdx(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), isInlineAsm(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), llvm::MCRegisterInfo::isSubRegister(), llvm::MCRegisterInfo::isSuperRegister(), llvm::MCRegAliasIterator::isValid(), llvm::SmallVectorTemplateBase< T, bool >::pop_back(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), RemoveOperand(), and llvm::MachineOperand::setIsDead().

Referenced by llvm::LiveVariables::addVirtualRegisterDead(), llvm::Thumb1InstrInfo::copyPhysReg(), llvm::LiveRangeEdit::eraseVirtReg(), llvm::LiveVariables::HandleVirtRegDef(), isEFLAGSLive(), isFullCopyOf(), isRegTiedToDefOperand(), and llvm::LiveIntervals::shrinkToUses().

◆ addRegisterDefined()

| void MachineInstr::addRegisterDefined | ( | unsigned | Reg, |

| const TargetRegisterInfo * | RegInfo = nullptr |

||

| ) |

We have determined MI defines a register.

Make sure there is an operand defining Reg.

Definition at line 1906 of file MachineInstr.cpp.

References addOperand(), llvm::MachineOperand::CreateReg(), findRegisterDefOperand(), llvm::TargetRegisterInfo::isPhysicalRegister(), and operands().

Referenced by canInstrSubstituteCmpInstr(), llvm::SparcInstrInfo::copyPhysReg(), llvm::ARMBaseInstrInfo::copyPhysReg(), INITIALIZE_PASS(), isRegTiedToDefOperand(), llvm::LanaiInstrInfo::optimizeCompareInstr(), and setPhysRegsDeadExcept().

◆ addRegisterKilled()

| bool MachineInstr::addRegisterKilled | ( | unsigned | IncomingReg, |

| const TargetRegisterInfo * | RegInfo, | ||

| bool | AddIfNotFound = false |

||

| ) |

We have determined MI kills a register.

Look for the operand that uses it and mark it as IsKill. If AddIfNotFound is true, add a implicit operand if it's not found. Returns true if the operand exists / is added.

Definition at line 1757 of file MachineInstr.cpp.

References addOperand(), llvm::SmallVectorTemplateCommon< T, typename >::back(), llvm::MachineOperand::CreateReg(), llvm::SmallVectorBase::empty(), findInlineAsmFlagIdx(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDebug(), isInlineAsm(), llvm::MachineOperand::isKill(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), isRegTiedToDefOperand(), llvm::MCRegisterInfo::isSubRegister(), llvm::MCRegisterInfo::isSuperRegister(), llvm::MachineOperand::isUndef(), llvm::MachineOperand::isUse(), llvm::MCRegAliasIterator::isValid(), llvm::SmallVectorTemplateBase< T, bool >::pop_back(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), RemoveOperand(), and llvm::MachineOperand::setIsKill().

Referenced by addExclusiveRegPair(), llvm::LiveIntervals::addKillFlags(), llvm::LiveVariables::addVirtualRegisterKilled(), llvm::ARMBaseInstrInfo::breakPartialRegDependency(), llvm::X86InstrInfo::breakPartialRegDependency(), llvm::SparcInstrInfo::copyPhysReg(), llvm::ARMBaseInstrInfo::copyPhysReg(), emitAlignedDPRCS2Restores(), emitAlignedDPRCS2Spills(), llvm::XCoreFrameLowering::emitPrologue(), llvm::ARMBaseInstrInfo::expandPostRAPseudo(), llvm::LiveVariables::HandleVirtRegDef(), INITIALIZE_PASS(), isRegTiedToDefOperand(), and ReplaceDominatedUses().

◆ allDefsAreDead()

| bool MachineInstr::allDefsAreDead | ( | ) | const |

Return true if all the defs of this instruction are dead.

allDefsAreDead - Return true if all the defs of this instruction are dead.

Definition at line 1368 of file MachineInstr.cpp.

References operands().

Referenced by llvm::LiveRangeEdit::eraseVirtReg(), INITIALIZE_PASS(), isFullCopyOf(), isRegTiedToDefOperand(), and llvm::LiveIntervals::shrinkToUses().

◆ bundleWithPred()

| void MachineInstr::bundleWithPred | ( | ) |

Bundle this instruction with its predecessor.

This can be an unbundled instruction, or it can be the first instruction in a bundle.

Definition at line 721 of file MachineInstr.cpp.

References assert(), BundledPred, BundledSucc, llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type >::getIterator(), isBundledWithPred(), and setFlag().

Referenced by llvm::MachineFunction::CloneMachineInstrBundle(), llvm::createR600ExpandSpecialInstrsPass(), llvm::SplitEditor::dump(), getMopState(), llvm::MIBundleBuilder::insert(), isBundledWithSucc(), and llvm::MIBundleBuilder::MIBundleBuilder().

◆ bundleWithSucc()

| void MachineInstr::bundleWithSucc | ( | ) |

Bundle this instruction with its successor.

This can be an unbundled instruction, or it can be the last instruction in a bundle.

Definition at line 730 of file MachineInstr.cpp.

References assert(), BundledPred, BundledSucc, llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type >::getIterator(), isBundledWithSucc(), and setFlag().

Referenced by llvm::MIBundleBuilder::insert(), and isBundledWithSucc().

◆ canFoldAsLoad()

|

inline |

Return true for instructions that can be folded as memory operands in other instructions.

The most common use for this is instructions that are simple loads from memory that don't modify the loaded value in any way, but it can also be used for instructions that can be expressed as constant-pool loads, such as V_SETALLONES on x86, to allow them to be folded when it is beneficial. This should only be set on instructions that return a value in their only virtual register definition.

Definition at line 753 of file MachineInstr.h.

References llvm::MCID::FoldableAsLoad, and hasProperty().

Referenced by llvm::LiveRangeEdit::eraseVirtReg(), llvm::TargetInstrInfo::foldMemoryOperand(), getNewSource(), isCopyFeedingInvariantStore(), and isFullCopyOf().

◆ changeDebugValuesDefReg()

| void MachineInstr::changeDebugValuesDefReg | ( | unsigned | Reg | ) |

Find all DBG_VALUEs immediately following this instruction that point to a register def in this instruction and point them to Reg instead.

Definition at line 2095 of file MachineInstr.cpp.

References collectDebugValues().

Referenced by untieRegOperand().

◆ clearAsmPrinterFlag()

|

inline |

Clear specific AsmPrinter flags.

Definition at line 285 of file MachineInstr.h.

◆ clearAsmPrinterFlags()

|

inline |

Clear the AsmPrinter bitvector.

Definition at line 272 of file MachineInstr.h.

◆ clearFlag()

|

inline |

clearFlag - Clear a MI flag.

Definition at line 311 of file MachineInstr.h.

Referenced by moveInstrOut(), llvm::MachineBasicBlock::remove_instr(), unbundleFromPred(), and unbundleFromSucc().

◆ clearKillInfo()

| void MachineInstr::clearKillInfo | ( | ) |

Clears kill flags on all operands.

clearKillInfo - Clears kill flags on all operands.

Definition at line 1118 of file MachineInstr.cpp.

References operands().

Referenced by isRegTiedToDefOperand(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), and llvm::rdf::Liveness::resetKills().

◆ clearRegisterDeads()

| void MachineInstr::clearRegisterDeads | ( | unsigned | Reg | ) |

Clear all dead flags on operands defining register Reg.

Definition at line 1890 of file MachineInstr.cpp.

References operands(), and Reg.

Referenced by isCallerPreservedOrConstPhysReg(), isRegTiedToDefOperand(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), and llvm::PPCInstrInfo::optimizeCompareInstr().

◆ clearRegisterKills()

| void MachineInstr::clearRegisterKills | ( | unsigned | Reg, |

| const TargetRegisterInfo * | RegInfo | ||

| ) |

Clear all kill flags affecting Reg.

If RegInfo is provided, this includes all aliasing registers.

Definition at line 1824 of file MachineInstr.cpp.

References llvm::TargetRegisterInfo::isPhysicalRegister(), operands(), and llvm::TargetRegisterInfo::regsOverlap().

Referenced by llvm::LiveIntervals::addKillFlags(), isNopCopy(), and isRegTiedToDefOperand().

◆ cloneMemRefs()

| void MachineInstr::cloneMemRefs | ( | MachineFunction & | MF, |

| const MachineInstr & | MI | ||

| ) |

Clone another MachineInstr's memory reference descriptor list and replace ours with it.

Note that *this may be the incoming MI!

Prefer this API whenever possible as it can avoid allocations in common cases.

Definition at line 368 of file MachineInstr.cpp.

References assert(), getMF(), getPostInstrSymbol(), getPreInstrSymbol(), memoperands(), and setMemRefs().

Referenced by llvm::MachineInstrBuilder::cloneMemRefs(), cloneMergedMemRefs(), fixupGlobalSaddr(), and setDebugLoc().

◆ cloneMergedMemRefs()

| void MachineInstr::cloneMergedMemRefs | ( | MachineFunction & | MF, |

| ArrayRef< const MachineInstr *> | MIs | ||

| ) |

Clone the merge of multiple MachineInstrs' memory reference descriptors list and replace ours with it.

Note that *this may be one of the incoming MIs!

Prefer this API whenever possible as it can avoid allocations in common cases.

Definition at line 401 of file MachineInstr.cpp.

References llvm::SmallVectorImpl< T >::append(), assert(), cloneMemRefs(), dropMemRefs(), llvm::ArrayRef< T >::empty(), getMF(), hasIdenticalMMOs(), llvm::make_pointee_range(), memoperands(), memoperands_begin(), memoperands_empty(), memoperands_end(), setMemRefs(), llvm::ArrayRef< T >::size(), and llvm::ArrayRef< T >::slice().

Referenced by llvm::MachineInstrBuilder::cloneMergedMemRefs(), and setDebugLoc().

◆ collectDebugValues()

| void MachineInstr::collectDebugValues | ( | SmallVectorImpl< MachineInstr *> & | DbgValues | ) |

Scan instructions following MI and collect any matching DBG_VALUEs.

Definition at line 2078 of file MachineInstr.cpp.

References llvm::MachineBasicBlock::end(), getOperand(), getParent(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isReg(), MI, and llvm::SmallVectorTemplateBase< T, bool >::push_back().

Referenced by changeDebugValuesDefReg(), performSink(), untieRegOperand(), and llvm::WebAssemblyDebugValueManager::WebAssemblyDebugValueManager().

◆ copyImplicitOps()

| void MachineInstr::copyImplicitOps | ( | MachineFunction & | MF, |

| const MachineInstr & | MI | ||

| ) |

Copy implicit register operands from specified instruction to this instruction.

copyImplicitOps - Copy implicit register operands from specified instruction to this instruction.

Definition at line 1380 of file MachineInstr.cpp.

References addOperand(), getDesc(), llvm::MCInstrDesc::getNumOperands(), getNumOperands(), getOperand(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::isRegMask().

Referenced by llvm::MachineInstrBuilder::copyImplicitOps(), enableAllocFrameElim(), fixupGlobalSaddr(), llvm::HexagonFrameLowering::getFrameIndexReference(), InsertLDR_STR(), and isRegTiedToDefOperand().

◆ copyIRFlags()

| void MachineInstr::copyIRFlags | ( | const Instruction & | I | ) |

Copy all flags to MachineInst MIFlags.

Definition at line 522 of file MachineInstr.cpp.

References AllInBundle, llvm::FastMathFlags::allowContract(), llvm::FastMathFlags::allowReassoc(), llvm::FastMathFlags::allowReciprocal(), AnyInBundle, llvm::FastMathFlags::approxFunc(), assert(), llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type >::getIterator(), isBundledWithPred(), llvm::BitmaskEnumDetail::Mask(), llvm::FastMathFlags::noInfs(), llvm::FastMathFlags::noNaNs(), llvm::FastMathFlags::noSignedZeros(), llvm::X86II::OB, and setFlag().

Referenced by computeValueLLTs(), getOffsetFromIndices(), and setDebugLoc().

◆ definesRegister()

|

inline |

Return true if the MachineInstr fully defines the specified register.

If TargetRegisterInfo is passed, then it also checks if there is a def of a super-register. NOTE: It's ignoring subreg indices on virtual registers.

Definition at line 1143 of file MachineInstr.h.

References findRegisterDefOperandIdx(), and TRI.

Referenced by addLiveInRegs(), llvm::ARMBaseInstrInfo::breakPartialRegDependency(), checkAndUpdateCPSRKill(), checkAndUpdateEFLAGSKill(), checkCCKill(), convertToNonFlagSettingOpc(), llvm::ARMBaseInstrInfo::expandPostRAPseudo(), getImplicitSPRUseForDPRUse(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), ImposeStackOrdering(), INITIALIZE_PASS(), isCompareZero(), IsSafeToMove(), llvm::ARMBaseInstrInfo::isSchedulingBoundary(), llvm::PPCRegisterInfo::lowerCRBitRestore(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), and llvm::rewriteT2FrameIndex().

◆ defs() [1/2]

|

inline |

Returns a range over all explicit operands that are register definitions.

Implicit definition are not included!

Definition at line 481 of file MachineInstr.h.

References getNumExplicitDefs(), llvm::make_range(), and operands_begin().

Referenced by addRegsToSet(), llvm::biasPhysReg(), llvm::createSIWholeQuadModePass(), llvm::SplitEditor::dump(), findSingleRegDef(), INITIALIZE_PASS(), instModifiesReg(), isCrossCopy(), llvm::WebAssemblyMCInstLower::Lower(), llvm::GCNUpwardRPTracker::recede(), and false::Chain::str().

◆ defs() [2/2]

|

inline |

Returns a range over all explicit operands that are register definitions.

Implicit definition are not included!

Definition at line 486 of file MachineInstr.h.

References getNumExplicitDefs(), llvm::make_range(), and operands_begin().

◆ dropMemRefs()

| void MachineInstr::dropMemRefs | ( | MachineFunction & | MF | ) |

Clear this MachineInstr's memory reference descriptor list.

This resets the memrefs to their most conservative state. This should be used only as a last resort since it greatly pessimizes our knowledge of the memory access performed by the instruction.

Definition at line 319 of file MachineInstr.cpp.

References llvm::MachineFunction::createMIExtraInfo(), getPostInstrSymbol(), getPreInstrSymbol(), and memoperands_empty().

Referenced by cloneMergedMemRefs(), INITIALIZE_PASS(), setDebugLoc(), and setMemRefs().

◆ dump()

| LLVM_DUMP_METHOD void MachineInstr::dump | ( | ) | const |

Definition at line 1430 of file MachineInstr.cpp.

References llvm::dbgs(), and print().

Referenced by canMoveInstsAcrossMemOp(), llvm::HexagonPacketizerList::canPromoteToDotCur(), llvm::HexagonPacketizerList::cleanUpDotCur(), computeBranchTargetAndInversion(), llvm::PPCInstrInfo::convertToImmediateForm(), llvm::createX86OptimizeLEAs(), doCandidateWalk(), llvm::ScheduleDAGInstrs::dumpNode(), llvm::AArch64TargetLowering::EmitInstrWithCustomInserter(), findPotentialBlockers(), fixupRegionExits(), getNewValueJumpOpcode(), getReassignedChan(), getRegClassForUnfoldedLoad(), INITIALIZE_PASS(), llvm::SMSchedule::insert(), llvm::HexagonInstrInfo::invertAndChangeJumpTarget(), isDataInvariant(), isDataInvariantLoad(), isDbgValueDescribedByReg(), isEFLAGSLive(), isIntersect(), llvm::HexagonInstrInfo::isLateInstrFeedsEarlyInstr(), isLEASimpleIncOrDec(), isNopCopy(), isPHIRegionIndex(), isRegTiedToDefOperand(), MoveAndTeeForMultiUse(), MoveForSingleUse(), llvm::AggressiveAntiDepBreaker::Observe(), packCmovGroup(), populateCandidates(), llvm::HexagonInstrInfo::PredicateInstruction(), RematerializeCheapDef(), removeRedundantBlockingStores(), llvm::HexagonInstrInfo::reversePredSense(), swapMIOperands(), and updateOperandRegConstraints().

◆ emitError()

| void MachineInstr::emitError | ( | StringRef | Msg | ) | const |

Emit an error referring to the source location of this instruction.

This should only be used for inline assembly that is somehow impossible to compile. Other errors should have been handled much earlier.

If this method returns, the caller should try to recover from the error.

Definition at line 1965 of file MachineInstr.cpp.

References llvm::LLVMContext::emitError(), llvm::Module::getContext(), llvm::MachineFunction::getMMI(), llvm::MachineModuleInfo::getModule(), getNumOperands(), llvm::MDNode::getNumOperands(), getOperand(), llvm::MDNode::getOperand(), getParent(), and llvm::report_fatal_error().

Referenced by llvm::RegAllocBase::allocatePhysRegs(), getDebugLoc(), INITIALIZE_PASS(), and llvm::LowerARMMachineInstrToMCInst().

◆ eraseFromBundle()

| void MachineInstr::eraseFromBundle | ( | ) |

Unlink 'this' form its basic block and delete it.

If the instruction is part of a bundle, the other instructions in the bundle remain bundled.

Definition at line 683 of file MachineInstr.cpp.

References assert(), llvm::MachineBasicBlock::erase_instr(), and getParent().

Referenced by VerifyLowRegs().

◆ eraseFromParent()

| void MachineInstr::eraseFromParent | ( | ) |

Unlink 'this' from the containing basic block and delete it.

If this instruction is the header of a bundle, the whole bundle is erased. This function can not be used for instructions inside a bundle, use eraseFromBundle() to erase individual bundled instructions.

Definition at line 658 of file MachineInstr.cpp.

References assert(), llvm::MachineBasicBlock::erase(), and getParent().

Referenced by addExclusiveRegPair(), llvm::analyzeArguments(), llvm::ARCInstrInfo::analyzeBranch(), llvm::SparcInstrInfo::analyzeBranch(), llvm::MipsInstrInfo::analyzeBranch(), llvm::ARMBaseInstrInfo::analyzeBranch(), llvm::AArch64InstrInfo::analyzeBranch(), AppendEndToFunction(), buildEXP(), llvm::AArch64InstrInfo::buildOutlinedFrame(), canInstrSubstituteCmpInstr(), llvm::TailDuplicator::canTailDuplicate(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), createPHIsForCMOVsInSinkBB(), createPHIsForSelects(), llvm::createR600ExpandSpecialInstrsPass(), llvm::createSIWholeQuadModePass(), llvm::createX86OptimizeLEAs(), llvm::createXCoreFrameToArgsOffsetEliminationPass(), definesFullReg(), dumpMachineInstrRangeWithSlotIndex(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), emitBuildPairF64Pseudo(), emitClzero(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AArch64TargetLowering::EmitF128CSEL(), emitIndirectDst(), emitIndirectSrc(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::BPFTargetLowering::EmitInstrWithCustomInserter(), llvm::RISCVTargetLowering::EmitInstrWithCustomInserter(), llvm::AVRTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), llvm::AArch64TargetLowering::EmitLoweredCatchPad(), emitMonitor(), llvm::TargetLoweringBase::emitPatchPoint(), emitPostSt(), emitRDPKRU(), llvm::MSP430TargetLowering::EmitShiftInstr(), emitSplitF64Pseudo(), emitWRPKRU(), emitXBegin(), llvm::TargetLoweringBase::emitXRayCustomEvent(), llvm::TargetLoweringBase::emitXRayTypedEvent(), llvm::rdf::DeadCodeElimination::erase(), eraseDeadBBsAndChildren(), eraseFromParentAndMarkDBGValuesForRemoval(), llvm::LiveRangeEdit::eraseVirtReg(), llvm::R600InstrInfo::expandPostRAPseudo(), llvm::SIInstrInfo::expandPostRAPseudo(), llvm::SparcTargetLowering::expandSelectCC(), llvm::LegalizerHelper::fewerElementsVector(), findSingleRegDef(), findStartOfTree(), findUncondBrI(), llvm::fixStackStores(), fixupGlobalSaddr(), llvm::foldFrameOffset(), llvm::SystemZInstrInfo::FoldImmediate(), llvm::SIInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::PPCInstrInfo::FoldImmediate(), foldImmediates(), llvm::X86InstrInfo::foldMemoryOperandImpl(), foldVGPRCopyIntoRegSequence(), llvm::HexagonInstrInfo::genAllInsnTimingClasses(), getAdjustedCmp(), getCmpForPseudo(), getCompareSourceReg(), getConstant(), getDPPOp(), GetDSubRegs(), getMappedOp(), getNewSource(), getNewValueJumpOpcode(), getOModValue(), getRegClassForUnfoldedLoad(), getRegsUsedByPHIs(), getRetpolineSymbol(), getSmrdOpcode(), getStartOrEndSlot(), getSubOpcode(), getUnconditionalBrDisp(), llvm::MachineSSAUpdater::GetValueInMiddleOfBlock(), llvm::MipsTargetLowering::HandleByVal(), HandleVRSaveUpdate(), hasOneNonDBGUseInst(), hasUseAfterLoop(), hoistAndMergeSGPRInits(), INITIALIZE_PASS(), llvm::X86FrameLowering::inlineStackProbe(), insertCopy(), isCallerPreservedOrConstPhysReg(), isCompareZero(), isCopyFeedingInvariantStore(), isDefInSubRange(), isFpMulInstruction(), isFullCopyOf(), isFullUndefDef(), isInRage(), isLiveOut(), isNopCopy(), isPHIRegionIndex(), isRegUsedByPhiNodes(), isSimpleIf(), isSimpleIndexCalc(), isVirtualRegisterOperand(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::libcall(), llvm::LegalizerHelper::lower(), LowerFPToInt(), makeImplicit(), matchSwap(), Mips16WhichOp8uOr16simm(), llvm::SIInstrInfo::moveToVALU(), llvm::LegalizerHelper::narrowScalar(), llvm::LanaiInstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::X86InstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCondBranch(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), optimizeVcndVcmpPair(), parseCond(), readsVCCZ(), llvm::HexagonInstrInfo::reduceLoopCount(), registerDefinedBetween(), RematerializeCheapDef(), RemoveDeadAddBetweenLEAAndJT(), llvm::FastISel::removeDeadCode(), removeExternalCFGEdges(), RemoveVRSaveCode(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::rewriteAArch64FrameIndex(), salvageDebugInfoFromEmptyBlock(), llvm::FastISel::selectPatchpoint(), splitMBB(), llvm::SystemZInstrInfo::SystemZInstrInfo(), llvm::TailDuplicator::tailDuplicateAndUpdate(), llvm::CombinerHelper::tryCombineCopy(), tryOptimizeLEAtoMOV(), trySequenceOfOnes(), and llvm::LegalizerHelper::widenScalar().

◆ eraseFromParentAndMarkDBGValuesForRemoval()

| void MachineInstr::eraseFromParentAndMarkDBGValuesForRemoval | ( | ) |

Unlink 'this' from the containing basic block and delete it.

For all definitions mark their uses in DBG_VALUE nodes as undefined. Otherwise like eraseFromParent().

Definition at line 663 of file MachineInstr.cpp.

References assert(), eraseFromParent(), llvm::MachineBasicBlock::getParent(), getParent(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineRegisterInfo::markUsesInDebugValueAsUndef(), operands(), and Reg.

Referenced by llvm::Combiner::combineMachineInstrs(), INITIALIZE_PASS(), llvm::InstructionSelect::runOnMachineFunction(), and llvm::Legalizer::runOnMachineFunction().

◆ explicit_operands() [1/2]

|

inline |

Definition at line 465 of file MachineInstr.h.

References getNumExplicitOperands(), llvm::make_range(), and operands_begin().

Referenced by getConstant(), getVariantKind(), implicit_operands(), and usesExtendedRegister().

◆ explicit_operands() [2/2]

|

inline |

Definition at line 469 of file MachineInstr.h.

References getNumExplicitOperands(), llvm::make_range(), and operands_begin().

◆ explicit_uses() [1/2]

|

inline |

Definition at line 499 of file MachineInstr.h.

References getNumExplicitDefs(), getNumExplicitOperands(), llvm::make_range(), and operands_begin().

Referenced by findSingleRegDef(), findStartOfTree(), llvm::WebAssemblyMCInstLower::Lower(), and MoveAndTeeForMultiUse().

◆ explicit_uses() [2/2]

|

inline |

Definition at line 503 of file MachineInstr.h.

References getNumExplicitDefs(), getNumExplicitOperands(), llvm::make_range(), and operands_begin().

◆ findFirstPredOperandIdx()

| int MachineInstr::findFirstPredOperandIdx | ( | ) | const |

Find the index of the first operand in the operand list that is used to represent the predicate.

findFirstPredOperandIdx() - Find the index of the first operand in the operand list that is used to represent the predicate.

It returns -1 if none is found.

Definition at line 1006 of file MachineInstr.cpp.

References getDesc(), getNumOperands(), llvm::MCInstrDesc::isPredicable(), llvm::MCOperandInfo::isPredicate(), and llvm::MCInstrDesc::OpInfo.

Referenced by llvm::ARMBaseInstrInfo::commuteInstructionImpl(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), findRegisterDefOperand(), llvm::getInstrPredicate(), llvm::ARMBaseInstrInfo::getPredicate(), llvm::ARMBaseInstrInfo::isPredicated(), llvm::R600InstrInfo::isPredicated(), llvm::ARMBaseInstrInfo::PredicateInstruction(), and llvm::R600InstrInfo::PredicateInstruction().

◆ findInlineAsmFlagIdx()

Find the index of the flag word operand that corresponds to operand OpIdx on an inline asm instruction.

Returns -1 if getOperand(OpIdx) does not belong to an inline asm operand group.

If GroupNo is not NULL, it will receive the number of the operand group containing OpIdx.

The flag operand is an immediate that can be decoded with methods like InlineAsm::hasRegClassConstraint().

Definition at line 772 of file MachineInstr.cpp.

References assert(), llvm::MachineOperand::getImm(), llvm::InlineAsm::getNumOperandRegisters(), getNumOperands(), getOperand(), llvm::MachineOperand::isImm(), isInlineAsm(), and llvm::InlineAsm::MIOp_FirstOperand.

Referenced by addRegisterDead(), addRegisterKilled(), findRegisterDefOperand(), and getRegClassConstraint().

◆ findRegisterDefOperand()

|

inline |

Wrapper for findRegisterDefOperandIdx, it returns a pointer to the MachineOperand rather than an index.

Definition at line 1200 of file MachineInstr.h.

References findFirstPredOperandIdx(), findInlineAsmFlagIdx(), findRegisterDefOperandIdx(), findTiedOperandIdx(), getOperand(), getRegClassConstraint(), getRegClassConstraintEffect(), getRegClassConstraintEffectForVReg(), tieOperands(), TII, and TRI.

Referenced by addRegisterDefined(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), llvm::LiveVariables::HandleVirtRegDef(), isDataInvariant(), isDataInvariantLoad(), llvm::AggressiveAntiDepBreaker::Observe(), transferDeadCC(), and UpdateCPSRUse().

◆ findRegisterDefOperandIdx()

| int MachineInstr::findRegisterDefOperandIdx | ( | unsigned | Reg, |

| bool | isDead = false, |

||

| bool | Overlap = false, |

||

| const TargetRegisterInfo * | TRI = nullptr |

||

| ) | const |

Returns the operand index that is a def of the specified register or -1 if it is not found.

findRegisterDefOperandIdx() - Returns the operand index that is a def of the specified register or -1 if it is not found.

If isDead is true, defs that are not dead are skipped. If Overlap is true, then it also looks for defs that merely overlap the specified register. If TargetRegisterInfo is non-null, then it also checks if there is a def of a super-register. This may also return a register mask operand when Overlap is true.

If isDead is true, defs that are not dead are skipped. If TargetRegisterInfo is non-null, then it also checks if there is a def of a super-register.

Definition at line 977 of file MachineInstr.cpp.

References llvm::MachineOperand::clobbersPhysReg(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), llvm::MCRegisterInfo::isSubRegister(), Reg, and llvm::TargetRegisterInfo::regsOverlap().

Referenced by addSegmentsWithValNo(), canFoldIntoCSel(), CriticalPathStep(), llvm::R600InstrInfo::definesAddressRegister(), definesRegister(), llvm::ARMBaseInstrInfo::expandPostRAPseudo(), findRegisterDefOperand(), findRegisterUseOperand(), getCompareSourceReg(), getMaddPatterns(), llvm::HexagonInstrInfo::getOperandLatency(), modifiesRegister(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCondBranch(), and registerDefIsDead().

◆ findRegisterUseOperand() [1/2]

|

inline |

Wrapper for findRegisterUseOperandIdx, it returns a pointer to the MachineOperand rather than an index.

Definition at line 1175 of file MachineInstr.h.

References findRegisterUseOperandIdx(), getOperand(), isKill(), and TRI.

Referenced by addEpilogOnlyR10(), findRegisterUseOperand(), getRegClassForUnfoldedLoad(), hasVulnerableLoad(), isCopy(), isEFLAGSLive(), llvm::AggressiveAntiDepBreaker::Observe(), regOverlapsSet(), and UpdateCPSRUse().

◆ findRegisterUseOperand() [2/2]

|

inline |

Definition at line 1181 of file MachineInstr.h.

References findRegisterDefOperandIdx(), findRegisterUseOperand(), isKill(), and TRI.

◆ findRegisterUseOperandIdx()

| int MachineInstr::findRegisterUseOperandIdx | ( | unsigned | Reg, |

| bool | isKill = false, |

||

| const TargetRegisterInfo * | TRI = nullptr |

||

| ) | const |

Returns the operand index that is a use of the specific register or -1 if it is not found.

findRegisterUseOperandIdx() - Returns the MachineOperand that is a use of the specific register or -1 if it is not found.

It further tightens the search criteria to a use that kills the register if isKill is true.

Definition at line 928 of file MachineInstr.cpp.

References getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), and llvm::TargetRegisterInfo::regsOverlap().

Referenced by findCondCodeUsedByInstr(), findRegisterUseOperand(), llvm::HexagonInstrInfo::getOperandLatency(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), llvm::CoalescerPair::isCoalescable(), isVirtualRegisterOperand(), killsRegister(), readsRegister(), registerDefIsDead(), llvm::PPCInstrInfo::replaceInstrOperandWithImm(), and llvm::R600InstrInfo::usesAddressRegister().

◆ findTiedOperandIdx()

Given the index of a tied register operand, find the operand it is tied to.

Defs are tied to uses and vice versa. Returns the index of the tied operand which must exist.

Definition at line 1061 of file MachineInstr.cpp.

References assert(), llvm::MachineOperand::getImm(), llvm::InlineAsm::getNumOperandRegisters(), getNumOperands(), getOperand(), llvm::MachineOperand::isImm(), isInlineAsm(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isTied(), llvm::MachineOperand::isUse(), llvm::InlineAsm::isUseOperandTiedToDef(), llvm_unreachable, llvm::InlineAsm::MIOp_FirstOperand, llvm::SmallVectorTemplateBase< T, bool >::push_back(), and llvm::SmallVectorBase::size().

Referenced by findRegisterDefOperand(), findSingleRegDef(), hasComplexRegisterTies(), INITIALIZE_PASS(), isRegTiedToDefOperand(), isRegTiedToUseOperand(), matchPair(), llvm::MIPrinter::print(), print(), untieRegOperand(), and llvm::SIInstrInfo::verifyInstruction().

◆ getAsmPrinterFlag()

|

inline |

Return whether an AsmPrinter flag is set.

Definition at line 275 of file MachineInstr.h.

Referenced by emitComments(), and llvm::X86AsmPrinter::EmitInstruction().

◆ getAsmPrinterFlags()

|

inline |

Return the asm printer flags bitvector.

Definition at line 269 of file MachineInstr.h.

Referenced by llvm::X86AsmPrinter::EmitInstruction().

◆ getBundleSize()

| unsigned MachineInstr::getBundleSize | ( | ) | const |

Return the number of instructions inside the MI bundle, excluding the bundle header.

Return the number of instructions inside the MI bundle, not counting the header instruction.

This is the number of instructions that MachineBasicBlock::iterator skips, 0 for unbundled instructions.

Definition at line 904 of file MachineInstr.cpp.

References llvm::ilist_node_impl< ilist_detail::compute_node_options< MachineInstr, Options... >::type >::getIterator(), I, and Size.

Referenced by INITIALIZE_PASS(), and isTransient().

◆ getDebugExpression()

| const DIExpression * MachineInstr::getDebugExpression | ( | ) | const |

Return the complex address expression referenced by this DBG_VALUE instruction.

Definition at line 810 of file MachineInstr.cpp.

References assert(), llvm::MachineOperand::getMetadata(), getOperand(), and isDebugValue().

Referenced by AssignProtectedObjSet(), computeExprForSpill(), llvm::createX86OptimizeLEAs(), emitDebugValueComment(), llvm::DbgVariableLocation::extractFromMachineInstruction(), getDebugLoc(), getDebugLocValue(), INITIALIZE_PASS(), llvm::DbgVariable::initializeDbgValue(), printExtendedName(), and llvm::SelectionDAGISel::runOnMachineFunction().

◆ getDebugLabel()

Return the debug label referenced by this DBG_LABEL instruction.

Definition at line 800 of file MachineInstr.cpp.

References assert(), llvm::MachineOperand::getMetadata(), getOperand(), and isDebugLabel().

Referenced by llvm::MachineInstrBuilder::addMetadata(), emitDebugLabelComment(), and getDebugLoc().

◆ getDebugLoc()

Returns the debug location id of this MachineInstr.

Definition at line 383 of file MachineInstr.h.

References emitError(), getDebugExpression(), getDebugLabel(), and getDebugVariable().

Referenced by addEpilog(), addEpilogLeaf(), addEpilogOnlyR10(), addExclusiveRegPair(), addImplicitDefUseOperands(), addSegmentsWithValNo(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), allPhiOperandsUndefined(), llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), llvm::analyzeArguments(), AppendEndToFunction(), llvm::HexagonFrameLowering::assignCalleeSavedSpillSlots(), llvm::BTFDebug::beginInstruction(), llvm::CodeViewDebug::beginInstruction(), llvm::DwarfDebug::beginInstruction(), llvm::ARMBaseInstrInfo::breakPartialRegDependency(), llvm::X86InstrInfo::breakPartialRegDependency(), llvm::buildDbgValueForSpill(), buildEXP(), llvm::SIInstrInfo::buildShrunkInst(), canMoveInstsAcrossMemOp(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), llvm::X86InstrInfo::classifyLEAReg(), CombineCVTAToLocal(), llvm::PPCInstrInfo::commuteInstructionImpl(), computeExprForSpill(), llvm::constrainRegToClass(), ContainsReg(), ConvertImplicitDefToConstZero(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::SystemZInstrInfo::convertToThreeAddress(), llvm::X86InstrInfo::convertToThreeAddress(), llvm::SIInstrInfo::convertToThreeAddress(), createPHIsForCMOVsInSinkBB(), createPHIsForSelects(), llvm::createSIAddIMGInitPass(), llvm::createSIWholeQuadModePass(), llvm::createX86FixupBWInsts(), llvm::createX86FixupSetCC(), llvm::createX86OptimizeLEAs(), definesFullReg(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::HexagonFrameLowering::determineCalleeSaves(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::ARCFrameLowering::eliminateCallFramePseudoInstr(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), llvm::PPCTargetLowering::EmitAtomicBinary(), emitBuildPairF64Pseudo(), emitClzero(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AArch64TargetLowering::EmitF128CSEL(), emitIndirectDst(), emitIndirectSrc(), llvm::HexagonHazardRecognizer::EmitInstruction(), llvm::BPFTargetLowering::EmitInstrWithCustomInserter(), llvm::RISCVTargetLowering::EmitInstrWithCustomInserter(), llvm::AVRTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), emitMonitor(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), llvm::TargetLoweringBase::emitPatchPoint(), emitPostSt(), emitRDPKRU(), llvm::MSP430TargetLowering::EmitShiftInstr(), emitSplitF64Pseudo(), emitWRPKRU(), emitXBegin(), llvm::TargetLoweringBase::emitXRayCustomEvent(), llvm::TargetLoweringBase::emitXRayTypedEvent(), eraseDeadBBsAndChildren(), expandLoadStackGuard(), expandMOV32r1(), ExpandMOVImmSExti8(), llvm::HexagonInstrInfo::expandPostRAPseudo(), llvm::AArch64InstrInfo::expandPostRAPseudo(), llvm::PPCInstrInfo::expandPostRAPseudo(), llvm::SparcTargetLowering::expandSelectCC(), llvm::HexagonInstrInfo::expandVGatherPseudo(), extractRsrcPtr(), findIncDecAfter(), findPotentialBlockers(), findSingleRegDef(), findStartOfTree(), llvm::fixStackStores(), fixupGlobalSaddr(), fixupRegionExits(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), foldPatchpoint(), foldVGPRCopyIntoRegSequence(), forceReg(), FuseInst(), FuseTwoAddrInst(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), genFusedMultiply(), genMaddR(), getAdjustedCmp(), getCmpForPseudo(), getCompareSourceReg(), getConstant(), getDPPOp(), GetDSubRegs(), llvm::HexagonHazardRecognizer::getHazardType(), getMappedOp(), getNewSource(), getNewValueJumpOpcode(), getPostIndexedLoadStoreOpcode(), getRegClassFromGRPhysReg(), getRegsUsedByPHIs(), getRetpolineSymbol(), getSmrdOpcode(), getSubOpcode(), getTag(), llvm::BPFTargetLowering::getTargetNodeName(), getUnconditionalBrDisp(), giveUpWithRemarks(), llvm::MipsTargetLowering::HandleByVal(), HandleVRSaveUpdate(), hasUseAfterLoop(), INITIALIZE_PASS(), llvm::DbgVariable::initializeDbgValue(), insertCopy(), insertDivByZeroTrap(), InsertFPConstInst(), InsertFPImmInst(), insertNopBeforeInstruction(), insertPHI(), InsertSPConstInst(), InsertSPImmInst(), llvm::IRTranslator::IRTranslator(), isCopy(), llvm::isCopyMulResult(), isDbgValueDescribedByReg(), isEFLAGSLive(), isFpMulInstruction(), isFullCopyOf(), isFunctionEntryBlock(), isIdenticalTo(), isInRage(), isLEASimpleIncOrDec(), isLiveOut(), IsMovepDestinationRegPair(), isPHIRegionIndex(), IsSafeAndProfitableToMove(), isSimpleIf(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOperandsVOP2(), loadM0FromVGPR(), loadSRsrcFromVGPR(), llvm::PPCRegisterInfo::lowerCRBitRestore(), llvm::PPCRegisterInfo::lowerCRBitSpilling(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::PPCRegisterInfo::lowerDynamicAreaOffset(), LowerFPToInt(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), makeImplicit(), MakeM0Inst(), matchSwap(), Mips16WhichOp8uOr16simm(), MoveAndTeeForMultiUse(), llvm::SIInstrInfo::moveToVALU(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCondBranch(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), parseCond(), performSink(), llvm::HexagonInstrInfo::PredicateInstruction(), llvm::MIPrinter::print(), print(), printExtendedName(), llvm::SIInstrInfo::readlaneVGPRToSGPR(), readsVCCZ(), llvm::TargetInstrInfo::reassociateOps(), llvm::HexagonInstrInfo::reduceLoopCount(), registerDefinedBetween(), llvm::ARMBaseInstrInfo::reMaterialize(), llvm::X86InstrInfo::reMaterialize(), ReplaceFrameIndex(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::reportGISelFailure(), llvm::rewriteAArch64FrameIndex(), llvm::ThumbRegisterInfo::rewriteFrameIndex(), llvm::SelectionDAGISel::runOnMachineFunction(), selectCopy(), selectFP16CopyFromGPR32(), llvm::ARMBaseInstrInfo::setExecutionDomain(), setM0ToIndexFromSGPR(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), splitEdge(), splitMBB(), llvm::SystemZInstrInfo::SystemZInstrInfo(), tryOptimizeLEAtoMOV(), trySequenceOfOnes(), llvm::X86InstrInfo::unfoldMemoryOperand(), updateOperand(), validThroughout(), and VerifyLowRegs().

◆ getDebugVariable()

| const DILocalVariable * MachineInstr::getDebugVariable | ( | ) | const |

Return the debug variable referenced by this DBG_VALUE instruction.

Definition at line 805 of file MachineInstr.cpp.

References assert(), llvm::MachineOperand::getMetadata(), getOperand(), and isDebugValue().