This is used to represent a portion of an LLVM function in a low-level Data Dependence DAG representation suitable for instruction selection. More...

#include "llvm/CodeGen/SelectionDAG.h"

Classes | |

| struct | DAGNodeDeletedListener |

| struct | DAGUpdateListener |

| Clients of various APIs that cause global effects on the DAG can optionally implement this interface. More... | |

Public Types | |

| enum | OverflowKind { OFK_Never, OFK_Sometime, OFK_Always } |

| Used to represent the possible overflow behavior of an operation. More... | |

| using | allnodes_const_iterator = ilist< SDNode >::const_iterator |

| using | allnodes_iterator = ilist< SDNode >::iterator |

Public Member Functions | |

| SelectionDAG (const TargetMachine &TM, CodeGenOpt::Level) | |

| SelectionDAG (const SelectionDAG &)=delete | |

| SelectionDAG & | operator= (const SelectionDAG &)=delete |

| ~SelectionDAG () | |

| void | init (MachineFunction &NewMF, OptimizationRemarkEmitter &NewORE, Pass *PassPtr, const TargetLibraryInfo *LibraryInfo, LegacyDivergenceAnalysis *Divergence) |

| Prepare this SelectionDAG to process code in the given MachineFunction. More... | |

| void | setFunctionLoweringInfo (FunctionLoweringInfo *FuncInfo) |

| void | clear () |

| Clear state and free memory necessary to make this SelectionDAG ready to process a new block. More... | |

| MachineFunction & | getMachineFunction () const |

| const Pass * | getPass () const |

| const DataLayout & | getDataLayout () const |

| const TargetMachine & | getTarget () const |

| const TargetSubtargetInfo & | getSubtarget () const |

| const TargetLowering & | getTargetLoweringInfo () const |

| const TargetLibraryInfo & | getLibInfo () const |

| const SelectionDAGTargetInfo & | getSelectionDAGInfo () const |

| LLVMContext * | getContext () const |

| OptimizationRemarkEmitter & | getORE () const |

| void | viewGraph (const std::string &Title) |

| Pop up a GraphViz/gv window with the DAG rendered using 'dot'. More... | |

| void | viewGraph () |

| void | clearGraphAttrs () |

| Clear all previously defined node graph attributes. More... | |

| void | setGraphAttrs (const SDNode *N, const char *Attrs) |

| Set graph attributes for a node. (eg. "color=red".) More... | |

| const std::string | getGraphAttrs (const SDNode *N) const |

| Get graph attributes for a node. More... | |

| void | setGraphColor (const SDNode *N, const char *Color) |

| Convenience for setting node color attribute. More... | |

| void | setSubgraphColor (SDNode *N, const char *Color) |

| Convenience for setting subgraph color attribute. More... | |

| allnodes_const_iterator | allnodes_begin () const |

| allnodes_const_iterator | allnodes_end () const |

| allnodes_iterator | allnodes_begin () |

| allnodes_iterator | allnodes_end () |

| ilist< SDNode >::size_type | allnodes_size () const |

| iterator_range< allnodes_iterator > | allnodes () |

| iterator_range< allnodes_const_iterator > | allnodes () const |

| const SDValue & | getRoot () const |

| Return the root tag of the SelectionDAG. More... | |

| SDValue | getEntryNode () const |

| Return the token chain corresponding to the entry of the function. More... | |

| const SDValue & | setRoot (SDValue N) |

| Set the current root tag of the SelectionDAG. More... | |

| void | VerifyDAGDiverence () |

| void | Combine (CombineLevel Level, AliasAnalysis *AA, CodeGenOpt::Level OptLevel) |

| This iterates over the nodes in the SelectionDAG, folding certain types of nodes together, or eliminating superfluous nodes. More... | |

| bool | LegalizeTypes () |

| This transforms the SelectionDAG into a SelectionDAG that only uses types natively supported by the target. More... | |

| void | Legalize () |

| This transforms the SelectionDAG into a SelectionDAG that is compatible with the target instruction selector, as indicated by the TargetLowering object. More... | |

| bool | LegalizeOp (SDNode *N, SmallSetVector< SDNode *, 16 > &UpdatedNodes) |

| Transforms a SelectionDAG node and any operands to it into a node that is compatible with the target instruction selector, as indicated by the TargetLowering object. More... | |

| bool | LegalizeVectors () |

| This transforms the SelectionDAG into a SelectionDAG that only uses vector math operations supported by the target. More... | |

| void | RemoveDeadNodes () |

| This method deletes all unreachable nodes in the SelectionDAG. More... | |

| void | DeleteNode (SDNode *N) |

| Remove the specified node from the system. More... | |

| SDVTList | getVTList (EVT VT) |

| Return an SDVTList that represents the list of values specified. More... | |

| SDVTList | getVTList (EVT VT1, EVT VT2) |

| SDVTList | getVTList (EVT VT1, EVT VT2, EVT VT3) |

| SDVTList | getVTList (EVT VT1, EVT VT2, EVT VT3, EVT VT4) |

| SDVTList | getVTList (ArrayRef< EVT > VTs) |

| SDValue | getGlobalAddress (const GlobalValue *GV, const SDLoc &DL, EVT VT, int64_t offset=0, bool isTargetGA=false, unsigned char TargetFlags=0) |

| SDValue | getTargetGlobalAddress (const GlobalValue *GV, const SDLoc &DL, EVT VT, int64_t offset=0, unsigned char TargetFlags=0) |

| SDValue | getFrameIndex (int FI, EVT VT, bool isTarget=false) |

| SDValue | getTargetFrameIndex (int FI, EVT VT) |

| SDValue | getJumpTable (int JTI, EVT VT, bool isTarget=false, unsigned char TargetFlags=0) |

| SDValue | getTargetJumpTable (int JTI, EVT VT, unsigned char TargetFlags=0) |

| SDValue | getConstantPool (const Constant *C, EVT VT, unsigned Align=0, int Offs=0, bool isT=false, unsigned char TargetFlags=0) |

| SDValue | getTargetConstantPool (const Constant *C, EVT VT, unsigned Align=0, int Offset=0, unsigned char TargetFlags=0) |

| SDValue | getConstantPool (MachineConstantPoolValue *C, EVT VT, unsigned Align=0, int Offs=0, bool isT=false, unsigned char TargetFlags=0) |

| SDValue | getTargetConstantPool (MachineConstantPoolValue *C, EVT VT, unsigned Align=0, int Offset=0, unsigned char TargetFlags=0) |

| SDValue | getTargetIndex (int Index, EVT VT, int64_t Offset=0, unsigned char TargetFlags=0) |

| SDValue | getBasicBlock (MachineBasicBlock *MBB) |

| SDValue | getBasicBlock (MachineBasicBlock *MBB, SDLoc dl) |

| SDValue | getExternalSymbol (const char *Sym, EVT VT) |

| SDValue | getExternalSymbol (const char *Sym, const SDLoc &dl, EVT VT) |

| SDValue | getTargetExternalSymbol (const char *Sym, EVT VT, unsigned char TargetFlags=0) |

| SDValue | getMCSymbol (MCSymbol *Sym, EVT VT) |

| SDValue | getValueType (EVT) |

| SDValue | getRegister (unsigned Reg, EVT VT) |

| SDValue | getRegisterMask (const uint32_t *RegMask) |

| SDValue | getEHLabel (const SDLoc &dl, SDValue Root, MCSymbol *Label) |

| SDValue | getLabelNode (unsigned Opcode, const SDLoc &dl, SDValue Root, MCSymbol *Label) |

| SDValue | getBlockAddress (const BlockAddress *BA, EVT VT, int64_t Offset=0, bool isTarget=false, unsigned char TargetFlags=0) |

| SDValue | getTargetBlockAddress (const BlockAddress *BA, EVT VT, int64_t Offset=0, unsigned char TargetFlags=0) |

| SDValue | getCopyToReg (SDValue Chain, const SDLoc &dl, unsigned Reg, SDValue N) |

| SDValue | getCopyToReg (SDValue Chain, const SDLoc &dl, unsigned Reg, SDValue N, SDValue Glue) |

| SDValue | getCopyToReg (SDValue Chain, const SDLoc &dl, SDValue Reg, SDValue N, SDValue Glue) |

| SDValue | getCopyFromReg (SDValue Chain, const SDLoc &dl, unsigned Reg, EVT VT) |

| SDValue | getCopyFromReg (SDValue Chain, const SDLoc &dl, unsigned Reg, EVT VT, SDValue Glue) |

| SDValue | getCondCode (ISD::CondCode Cond) |

| SDValue | getVectorShuffle (EVT VT, const SDLoc &dl, SDValue N1, SDValue N2, ArrayRef< int > Mask) |

| Return an ISD::VECTOR_SHUFFLE node. More... | |

| SDValue | getBuildVector (EVT VT, const SDLoc &DL, ArrayRef< SDValue > Ops) |

| Return an ISD::BUILD_VECTOR node. More... | |

| SDValue | getBuildVector (EVT VT, const SDLoc &DL, ArrayRef< SDUse > Ops) |

| Return an ISD::BUILD_VECTOR node. More... | |

| SDValue | getSplatBuildVector (EVT VT, const SDLoc &DL, SDValue Op) |

| Return a splat ISD::BUILD_VECTOR node, consisting of Op splatted to all elements. More... | |

| SDValue | getCommutedVectorShuffle (const ShuffleVectorSDNode &SV) |

| Returns an ISD::VECTOR_SHUFFLE node semantically equivalent to the shuffle node in input but with swapped operands. More... | |

| SDValue | getFPExtendOrRound (SDValue Op, const SDLoc &DL, EVT VT) |

| Convert Op, which must be of float type, to the float type VT, by either extending or rounding (by truncation). More... | |

| SDValue | getAnyExtOrTrunc (SDValue Op, const SDLoc &DL, EVT VT) |

| Convert Op, which must be of integer type, to the integer type VT, by either any-extending or truncating it. More... | |

| SDValue | getSExtOrTrunc (SDValue Op, const SDLoc &DL, EVT VT) |

| Convert Op, which must be of integer type, to the integer type VT, by either sign-extending or truncating it. More... | |

| SDValue | getZExtOrTrunc (SDValue Op, const SDLoc &DL, EVT VT) |

| Convert Op, which must be of integer type, to the integer type VT, by either zero-extending or truncating it. More... | |

| SDValue | getZeroExtendInReg (SDValue Op, const SDLoc &DL, EVT VT) |

| Return the expression required to zero extend the Op value assuming it was the smaller SrcTy value. More... | |

| SDValue | getBoolExtOrTrunc (SDValue Op, const SDLoc &SL, EVT VT, EVT OpVT) |

| Convert Op, which must be of integer type, to the integer type VT, by using an extension appropriate for the target's BooleanContent for type OpVT or truncating it. More... | |

| SDValue | getNOT (const SDLoc &DL, SDValue Val, EVT VT) |

| Create a bitwise NOT operation as (XOR Val, -1). More... | |

| SDValue | getLogicalNOT (const SDLoc &DL, SDValue Val, EVT VT) |

| Create a logical NOT operation as (XOR Val, BooleanOne). More... | |

| SDValue | getObjectPtrOffset (const SDLoc &SL, SDValue Op, int64_t Offset) |

| Create an add instruction with appropriate flags when used for addressing some offset of an object. More... | |

| SDValue | getObjectPtrOffset (const SDLoc &SL, SDValue Op, SDValue Offset) |

| SDValue | getCALLSEQ_START (SDValue Chain, uint64_t InSize, uint64_t OutSize, const SDLoc &DL) |

| Return a new CALLSEQ_START node, that starts new call frame, in which InSize bytes are set up inside CALLSEQ_START..CALLSEQ_END sequence and OutSize specifies part of the frame set up prior to the sequence. More... | |

| SDValue | getCALLSEQ_END (SDValue Chain, SDValue Op1, SDValue Op2, SDValue InGlue, const SDLoc &DL) |

| Return a new CALLSEQ_END node, which always must have a glue result (to ensure it's not CSE'd). More... | |

| bool | isUndef (unsigned Opcode, ArrayRef< SDValue > Ops) |

| Return true if the result of this operation is always undefined. More... | |

| SDValue | getUNDEF (EVT VT) |

| Return an UNDEF node. UNDEF does not have a useful SDLoc. More... | |

| SDValue | getGLOBAL_OFFSET_TABLE (EVT VT) |

| Return a GLOBAL_OFFSET_TABLE node. This does not have a useful SDLoc. More... | |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, ArrayRef< SDUse > Ops) |

| Gets or creates the specified node. More... | |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, ArrayRef< SDValue > Ops, const SDNodeFlags Flags=SDNodeFlags()) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, ArrayRef< EVT > ResultTys, ArrayRef< SDValue > Ops) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, ArrayRef< SDValue > Ops) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT) |

| Gets or creates the specified node. More... | |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, SDValue Operand, const SDNodeFlags Flags=SDNodeFlags()) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, SDValue N1, SDValue N2, const SDNodeFlags Flags=SDNodeFlags()) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, SDValue N1, SDValue N2, SDValue N3, const SDNodeFlags Flags=SDNodeFlags()) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, SDValue N1, SDValue N2, SDValue N3, SDValue N4) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, EVT VT, SDValue N1, SDValue N2, SDValue N3, SDValue N4, SDValue N5) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, SDValue N) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, SDValue N1, SDValue N2) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, SDValue N1, SDValue N2, SDValue N3) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, SDValue N1, SDValue N2, SDValue N3, SDValue N4) |

| SDValue | getNode (unsigned Opcode, const SDLoc &DL, SDVTList VTList, SDValue N1, SDValue N2, SDValue N3, SDValue N4, SDValue N5) |

| SDValue | getStackArgumentTokenFactor (SDValue Chain) |

| Compute a TokenFactor to force all the incoming stack arguments to be loaded from the stack. More... | |

| SDValue | getMemcpy (SDValue Chain, const SDLoc &dl, SDValue Dst, SDValue Src, SDValue Size, unsigned Align, bool isVol, bool AlwaysInline, bool isTailCall, MachinePointerInfo DstPtrInfo, MachinePointerInfo SrcPtrInfo) |

| SDValue | getMemmove (SDValue Chain, const SDLoc &dl, SDValue Dst, SDValue Src, SDValue Size, unsigned Align, bool isVol, bool isTailCall, MachinePointerInfo DstPtrInfo, MachinePointerInfo SrcPtrInfo) |

| SDValue | getMemset (SDValue Chain, const SDLoc &dl, SDValue Dst, SDValue Src, SDValue Size, unsigned Align, bool isVol, bool isTailCall, MachinePointerInfo DstPtrInfo) |

| SDValue | getAtomicMemcpy (SDValue Chain, const SDLoc &dl, SDValue Dst, unsigned DstAlign, SDValue Src, unsigned SrcAlign, SDValue Size, Type *SizeTy, unsigned ElemSz, bool isTailCall, MachinePointerInfo DstPtrInfo, MachinePointerInfo SrcPtrInfo) |

| SDValue | getAtomicMemmove (SDValue Chain, const SDLoc &dl, SDValue Dst, unsigned DstAlign, SDValue Src, unsigned SrcAlign, SDValue Size, Type *SizeTy, unsigned ElemSz, bool isTailCall, MachinePointerInfo DstPtrInfo, MachinePointerInfo SrcPtrInfo) |

| SDValue | getAtomicMemset (SDValue Chain, const SDLoc &dl, SDValue Dst, unsigned DstAlign, SDValue Value, SDValue Size, Type *SizeTy, unsigned ElemSz, bool isTailCall, MachinePointerInfo DstPtrInfo) |

| SDValue | getSetCC (const SDLoc &DL, EVT VT, SDValue LHS, SDValue RHS, ISD::CondCode Cond) |

| Helper function to make it easier to build SetCC's if you just have an ISD::CondCode instead of an SDValue. More... | |

| SDValue | getSelect (const SDLoc &DL, EVT VT, SDValue Cond, SDValue LHS, SDValue RHS) |

| Helper function to make it easier to build Select's if you just have operands and don't want to check for vector. More... | |

| SDValue | getSelectCC (const SDLoc &DL, SDValue LHS, SDValue RHS, SDValue True, SDValue False, ISD::CondCode Cond) |

| Helper function to make it easier to build SelectCC's if you just have an ISD::CondCode instead of an SDValue. More... | |

| SDValue | simplifySelect (SDValue Cond, SDValue TVal, SDValue FVal) |

| Try to simplify a select/vselect into 1 of its operands or a constant. More... | |

| SDValue | simplifyShift (SDValue X, SDValue Y) |

| Try to simplify a shift into 1 of its operands or a constant. More... | |

| SDValue | getVAArg (EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, SDValue SV, unsigned Align) |

| VAArg produces a result and token chain, and takes a pointer and a source value as input. More... | |

| SDValue | getAtomicCmpSwap (unsigned Opcode, const SDLoc &dl, EVT MemVT, SDVTList VTs, SDValue Chain, SDValue Ptr, SDValue Cmp, SDValue Swp, MachinePointerInfo PtrInfo, unsigned Alignment, AtomicOrdering SuccessOrdering, AtomicOrdering FailureOrdering, SyncScope::ID SSID) |

| Gets a node for an atomic cmpxchg op. More... | |

| SDValue | getAtomicCmpSwap (unsigned Opcode, const SDLoc &dl, EVT MemVT, SDVTList VTs, SDValue Chain, SDValue Ptr, SDValue Cmp, SDValue Swp, MachineMemOperand *MMO) |

| SDValue | getAtomic (unsigned Opcode, const SDLoc &dl, EVT MemVT, SDValue Chain, SDValue Ptr, SDValue Val, const Value *PtrVal, unsigned Alignment, AtomicOrdering Ordering, SyncScope::ID SSID) |

| Gets a node for an atomic op, produces result (if relevant) and chain and takes 2 operands. More... | |

| SDValue | getAtomic (unsigned Opcode, const SDLoc &dl, EVT MemVT, SDValue Chain, SDValue Ptr, SDValue Val, MachineMemOperand *MMO) |

| SDValue | getAtomic (unsigned Opcode, const SDLoc &dl, EVT MemVT, EVT VT, SDValue Chain, SDValue Ptr, MachineMemOperand *MMO) |

| Gets a node for an atomic op, produces result and chain and takes 1 operand. More... | |

| SDValue | getAtomic (unsigned Opcode, const SDLoc &dl, EVT MemVT, SDVTList VTList, ArrayRef< SDValue > Ops, MachineMemOperand *MMO) |

| Gets a node for an atomic op, produces result and chain and takes N operands. More... | |

| SDValue | getMemIntrinsicNode (unsigned Opcode, const SDLoc &dl, SDVTList VTList, ArrayRef< SDValue > Ops, EVT MemVT, MachinePointerInfo PtrInfo, unsigned Align=0, MachineMemOperand::Flags Flags=MachineMemOperand::MOLoad|MachineMemOperand::MOStore, unsigned Size=0) |

| Creates a MemIntrinsicNode that may produce a result and takes a list of operands. More... | |

| SDValue | getMemIntrinsicNode (unsigned Opcode, const SDLoc &dl, SDVTList VTList, ArrayRef< SDValue > Ops, EVT MemVT, MachineMemOperand *MMO) |

| SDValue | getMergeValues (ArrayRef< SDValue > Ops, const SDLoc &dl) |

| Create a MERGE_VALUES node from the given operands. More... | |

| SDValue | getLoad (EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, MachinePointerInfo PtrInfo, unsigned Alignment=0, MachineMemOperand::Flags MMOFlags=MachineMemOperand::MONone, const AAMDNodes &AAInfo=AAMDNodes(), const MDNode *Ranges=nullptr) |

| Loads are not normal binary operators: their result type is not determined by their operands, and they produce a value AND a token chain. More... | |

| SDValue | getLoad (EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, MachineMemOperand *MMO) |

| SDValue | getExtLoad (ISD::LoadExtType ExtType, const SDLoc &dl, EVT VT, SDValue Chain, SDValue Ptr, MachinePointerInfo PtrInfo, EVT MemVT, unsigned Alignment=0, MachineMemOperand::Flags MMOFlags=MachineMemOperand::MONone, const AAMDNodes &AAInfo=AAMDNodes()) |

| SDValue | getExtLoad (ISD::LoadExtType ExtType, const SDLoc &dl, EVT VT, SDValue Chain, SDValue Ptr, EVT MemVT, MachineMemOperand *MMO) |

| SDValue | getIndexedLoad (SDValue OrigLoad, const SDLoc &dl, SDValue Base, SDValue Offset, ISD::MemIndexedMode AM) |

| SDValue | getLoad (ISD::MemIndexedMode AM, ISD::LoadExtType ExtType, EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, SDValue Offset, MachinePointerInfo PtrInfo, EVT MemVT, unsigned Alignment=0, MachineMemOperand::Flags MMOFlags=MachineMemOperand::MONone, const AAMDNodes &AAInfo=AAMDNodes(), const MDNode *Ranges=nullptr) |

| SDValue | getLoad (ISD::MemIndexedMode AM, ISD::LoadExtType ExtType, EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, SDValue Offset, EVT MemVT, MachineMemOperand *MMO) |

| SDValue | getStore (SDValue Chain, const SDLoc &dl, SDValue Val, SDValue Ptr, MachinePointerInfo PtrInfo, unsigned Alignment=0, MachineMemOperand::Flags MMOFlags=MachineMemOperand::MONone, const AAMDNodes &AAInfo=AAMDNodes()) |

| Helper function to build ISD::STORE nodes. More... | |

| SDValue | getStore (SDValue Chain, const SDLoc &dl, SDValue Val, SDValue Ptr, MachineMemOperand *MMO) |

| SDValue | getTruncStore (SDValue Chain, const SDLoc &dl, SDValue Val, SDValue Ptr, MachinePointerInfo PtrInfo, EVT SVT, unsigned Alignment=0, MachineMemOperand::Flags MMOFlags=MachineMemOperand::MONone, const AAMDNodes &AAInfo=AAMDNodes()) |

| SDValue | getTruncStore (SDValue Chain, const SDLoc &dl, SDValue Val, SDValue Ptr, EVT SVT, MachineMemOperand *MMO) |

| SDValue | getIndexedStore (SDValue OrigStore, const SDLoc &dl, SDValue Base, SDValue Offset, ISD::MemIndexedMode AM) |

| SDValue | getMemBasePlusOffset (SDValue Base, unsigned Offset, const SDLoc &DL) |

| Returns sum of the base pointer and offset. More... | |

| SDValue | getMaskedLoad (EVT VT, const SDLoc &dl, SDValue Chain, SDValue Ptr, SDValue Mask, SDValue Src0, EVT MemVT, MachineMemOperand *MMO, ISD::LoadExtType, bool IsExpanding=false) |

| SDValue | getMaskedStore (SDValue Chain, const SDLoc &dl, SDValue Val, SDValue Ptr, SDValue Mask, EVT MemVT, MachineMemOperand *MMO, bool IsTruncating=false, bool IsCompressing=false) |

| SDValue | getMaskedGather (SDVTList VTs, EVT VT, const SDLoc &dl, ArrayRef< SDValue > Ops, MachineMemOperand *MMO) |

| SDValue | getMaskedScatter (SDVTList VTs, EVT VT, const SDLoc &dl, ArrayRef< SDValue > Ops, MachineMemOperand *MMO) |

| template<class TargetMemSDNode > | |

| SDValue | getTargetMemSDNode (SDVTList VTs, ArrayRef< SDValue > Ops, const SDLoc &dl, EVT MemVT, MachineMemOperand *MMO) |

| Return (create a new or find existing) a target-specific node. More... | |

| SDValue | getSrcValue (const Value *v) |

| Construct a node to track a Value* through the backend. More... | |

| SDValue | getMDNode (const MDNode *MD) |

| Return an MDNodeSDNode which holds an MDNode. More... | |

| SDValue | getBitcast (EVT VT, SDValue V) |

| Return a bitcast using the SDLoc of the value operand, and casting to the provided type. More... | |

| SDValue | getAddrSpaceCast (const SDLoc &dl, EVT VT, SDValue Ptr, unsigned SrcAS, unsigned DestAS) |

| Return an AddrSpaceCastSDNode. More... | |

| SDValue | getShiftAmountOperand (EVT LHSTy, SDValue Op) |

| Return the specified value casted to the target's desired shift amount type. More... | |

| SDValue | expandVAArg (SDNode *Node) |

Expand the specified ISD::VAARG node as the Legalize pass would. More... | |

| SDValue | expandVACopy (SDNode *Node) |

Expand the specified ISD::VACOPY node as the Legalize pass would. More... | |

| SDValue | getSymbolFunctionGlobalAddress (SDValue Op, Function **TargetFunction=nullptr) |

| Returs an GlobalAddress of the function from the current module with name matching the given ExternalSymbol. More... | |

| SDNode * | UpdateNodeOperands (SDNode *N, SDValue Op) |

| Mutate the specified node in-place to have the specified operands. More... | |

| SDNode * | UpdateNodeOperands (SDNode *N, SDValue Op1, SDValue Op2) |

| SDNode * | UpdateNodeOperands (SDNode *N, SDValue Op1, SDValue Op2, SDValue Op3) |

| SDNode * | UpdateNodeOperands (SDNode *N, SDValue Op1, SDValue Op2, SDValue Op3, SDValue Op4) |

| SDNode * | UpdateNodeOperands (SDNode *N, SDValue Op1, SDValue Op2, SDValue Op3, SDValue Op4, SDValue Op5) |

| SDNode * | UpdateNodeOperands (SDNode *N, ArrayRef< SDValue > Ops) |

| void | setNodeMemRefs (MachineSDNode *N, ArrayRef< MachineMemOperand *> NewMemRefs) |

| Mutate the specified machine node's memory references to the provided list. More... | |

| void | updateDivergence (SDNode *N) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT) |

| These are used for target selectors to mutate the specified node to have the specified return type, Target opcode, and operands. More... | |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT, SDValue Op1) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT, SDValue Op1, SDValue Op2) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT, SDValue Op1, SDValue Op2, SDValue Op3) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT, ArrayRef< SDValue > Ops) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT1, EVT VT2) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT1, EVT VT2, ArrayRef< SDValue > Ops) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT1, EVT VT2, EVT VT3, ArrayRef< SDValue > Ops) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned TargetOpc, EVT VT1, EVT VT2, SDValue Op1) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, EVT VT1, EVT VT2, SDValue Op1, SDValue Op2) |

| SDNode * | SelectNodeTo (SDNode *N, unsigned MachineOpc, SDVTList VTs, ArrayRef< SDValue > Ops) |

| SDNode * | MorphNodeTo (SDNode *N, unsigned Opc, SDVTList VTs, ArrayRef< SDValue > Ops) |

| This mutates the specified node to have the specified return type, opcode, and operands. More... | |

| SDNode * | mutateStrictFPToFP (SDNode *Node) |

| Mutate the specified strict FP node to its non-strict equivalent, unlinking the node from its chain and dropping the metadata arguments. More... | |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT) |

| These are used for target selectors to create a new node with specified return type(s), MachineInstr opcode, and operands. More... | |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT, SDValue Op1) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT, SDValue Op1, SDValue Op2) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT, SDValue Op1, SDValue Op2, SDValue Op3) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT, ArrayRef< SDValue > Ops) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, SDValue Op1, SDValue Op2) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, SDValue Op1, SDValue Op2, SDValue Op3) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, ArrayRef< SDValue > Ops) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, EVT VT3, SDValue Op1, SDValue Op2) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, EVT VT3, SDValue Op1, SDValue Op2, SDValue Op3) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, EVT VT1, EVT VT2, EVT VT3, ArrayRef< SDValue > Ops) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, ArrayRef< EVT > ResultTys, ArrayRef< SDValue > Ops) |

| MachineSDNode * | getMachineNode (unsigned Opcode, const SDLoc &dl, SDVTList VTs, ArrayRef< SDValue > Ops) |

| SDValue | getTargetExtractSubreg (int SRIdx, const SDLoc &DL, EVT VT, SDValue Operand) |

| A convenience function for creating TargetInstrInfo::EXTRACT_SUBREG nodes. More... | |

| SDValue | getTargetInsertSubreg (int SRIdx, const SDLoc &DL, EVT VT, SDValue Operand, SDValue Subreg) |

| A convenience function for creating TargetInstrInfo::INSERT_SUBREG nodes. More... | |

| SDNode * | getNodeIfExists (unsigned Opcode, SDVTList VTList, ArrayRef< SDValue > Ops, const SDNodeFlags Flags=SDNodeFlags()) |

| Get the specified node if it's already available, or else return NULL. More... | |

| SDDbgValue * | getDbgValue (DIVariable *Var, DIExpression *Expr, SDNode *N, unsigned R, bool IsIndirect, const DebugLoc &DL, unsigned O) |

| Creates a SDDbgValue node. More... | |

| SDDbgValue * | getConstantDbgValue (DIVariable *Var, DIExpression *Expr, const Value *C, const DebugLoc &DL, unsigned O) |

| Creates a constant SDDbgValue node. More... | |

| SDDbgValue * | getFrameIndexDbgValue (DIVariable *Var, DIExpression *Expr, unsigned FI, bool IsIndirect, const DebugLoc &DL, unsigned O) |

| Creates a FrameIndex SDDbgValue node. More... | |

| SDDbgValue * | getVRegDbgValue (DIVariable *Var, DIExpression *Expr, unsigned VReg, bool IsIndirect, const DebugLoc &DL, unsigned O) |

| Creates a VReg SDDbgValue node. More... | |

| SDDbgLabel * | getDbgLabel (DILabel *Label, const DebugLoc &DL, unsigned O) |

| Creates a SDDbgLabel node. More... | |

| void | transferDbgValues (SDValue From, SDValue To, unsigned OffsetInBits=0, unsigned SizeInBits=0, bool InvalidateDbg=true) |

| Transfer debug values from one node to another, while optionally generating fragment expressions for split-up values. More... | |

| void | RemoveDeadNode (SDNode *N) |

| Remove the specified node from the system. More... | |

| void | RemoveDeadNodes (SmallVectorImpl< SDNode *> &DeadNodes) |

| This method deletes the unreachable nodes in the given list, and any nodes that become unreachable as a result. More... | |

| void | ReplaceAllUsesWith (SDValue From, SDValue To) |

| Modify anything using 'From' to use 'To' instead. More... | |

| void | ReplaceAllUsesWith (SDNode *From, SDNode *To) |

| ReplaceAllUsesWith - Modify anything using 'From' to use 'To' instead. More... | |

| void | ReplaceAllUsesWith (SDNode *From, const SDValue *To) |

| ReplaceAllUsesWith - Modify anything using 'From' to use 'To' instead. More... | |

| void | ReplaceAllUsesOfValueWith (SDValue From, SDValue To) |

| Replace any uses of From with To, leaving uses of other values produced by From.getNode() alone. More... | |

| void | ReplaceAllUsesOfValuesWith (const SDValue *From, const SDValue *To, unsigned Num) |

| Like ReplaceAllUsesOfValueWith, but for multiple values at once. More... | |

| SDValue | makeEquivalentMemoryOrdering (LoadSDNode *Old, SDValue New) |

| If an existing load has uses of its chain, create a token factor node with that chain and the new memory node's chain and update users of the old chain to the token factor. More... | |

| unsigned | AssignTopologicalOrder () |

| Topological-sort the AllNodes list and a assign a unique node id for each node in the DAG based on their topological order. More... | |

| void | RepositionNode (allnodes_iterator Position, SDNode *N) |

| Move node N in the AllNodes list to be immediately before the given iterator Position. More... | |

| void | AddDbgValue (SDDbgValue *DB, SDNode *SD, bool isParameter) |

| Add a dbg_value SDNode. More... | |

| void | AddDbgLabel (SDDbgLabel *DB) |

| Add a dbg_label SDNode. More... | |

| ArrayRef< SDDbgValue * > | GetDbgValues (const SDNode *SD) const |

| Get the debug values which reference the given SDNode. More... | |

| bool | hasDebugValues () const |

| Return true if there are any SDDbgValue nodes associated with this SelectionDAG. More... | |

| SDDbgInfo::DbgIterator | DbgBegin () |

| SDDbgInfo::DbgIterator | DbgEnd () |

| SDDbgInfo::DbgIterator | ByvalParmDbgBegin () |

| SDDbgInfo::DbgIterator | ByvalParmDbgEnd () |

| SDDbgInfo::DbgLabelIterator | DbgLabelBegin () |

| SDDbgInfo::DbgLabelIterator | DbgLabelEnd () |

| void | salvageDebugInfo (SDNode &N) |

| To be invoked on an SDNode that is slated to be erased. More... | |

| void | dump () const |

| SDValue | CreateStackTemporary (EVT VT, unsigned minAlign=1) |

| Create a stack temporary, suitable for holding the specified value type. More... | |

| SDValue | CreateStackTemporary (EVT VT1, EVT VT2) |

| Create a stack temporary suitable for holding either of the specified value types. More... | |

| SDValue | FoldSymbolOffset (unsigned Opcode, EVT VT, const GlobalAddressSDNode *GA, const SDNode *N2) |

| SDValue | FoldConstantArithmetic (unsigned Opcode, const SDLoc &DL, EVT VT, SDNode *Cst1, SDNode *Cst2) |

| SDValue | FoldConstantArithmetic (unsigned Opcode, const SDLoc &DL, EVT VT, const ConstantSDNode *Cst1, const ConstantSDNode *Cst2) |

| SDValue | FoldConstantVectorArithmetic (unsigned Opcode, const SDLoc &DL, EVT VT, ArrayRef< SDValue > Ops, const SDNodeFlags Flags=SDNodeFlags()) |

| SDValue | FoldSetCC (EVT VT, SDValue N1, SDValue N2, ISD::CondCode Cond, const SDLoc &dl) |

| Constant fold a setcc to true or false. More... | |

| SDValue | GetDemandedBits (SDValue V, const APInt &Mask) |

| See if the specified operand can be simplified with the knowledge that only the bits specified by Mask are used. More... | |

| bool | SignBitIsZero (SDValue Op, unsigned Depth=0) const |

| Return true if the sign bit of Op is known to be zero. More... | |

| bool | MaskedValueIsZero (SDValue Op, const APInt &Mask, unsigned Depth=0) const |

| Return true if 'Op & Mask' is known to be zero. More... | |

| KnownBits | computeKnownBits (SDValue Op, unsigned Depth=0) const |

| Determine which bits of Op are known to be either zero or one and return them in Known. More... | |

| KnownBits | computeKnownBits (SDValue Op, const APInt &DemandedElts, unsigned Depth=0) const |

| Determine which bits of Op are known to be either zero or one and return them in Known. More... | |

| OverflowKind | computeOverflowKind (SDValue N0, SDValue N1) const |

| Determine if the result of the addition of 2 node can overflow. More... | |

| bool | isKnownToBeAPowerOfTwo (SDValue Val) const |

| Test if the given value is known to have exactly one bit set. More... | |

| unsigned | ComputeNumSignBits (SDValue Op, unsigned Depth=0) const |

| Return the number of times the sign bit of the register is replicated into the other bits. More... | |

| unsigned | ComputeNumSignBits (SDValue Op, const APInt &DemandedElts, unsigned Depth=0) const |

| Return the number of times the sign bit of the register is replicated into the other bits. More... | |

| bool | isBaseWithConstantOffset (SDValue Op) const |

| Return true if the specified operand is an ISD::ADD with a ConstantSDNode on the right-hand side, or if it is an ISD::OR with a ConstantSDNode that is guaranteed to have the same semantics as an ADD. More... | |

| bool | isKnownNeverNaN (SDValue Op, bool SNaN=false, unsigned Depth=0) const |

| Test whether the given SDValue is known to never be NaN. More... | |

| bool | isKnownNeverSNaN (SDValue Op, unsigned Depth=0) const |

| bool | isKnownNeverZeroFloat (SDValue Op) const |

| Test whether the given floating point SDValue is known to never be positive or negative zero. More... | |

| bool | isKnownNeverZero (SDValue Op) const |

| Test whether the given SDValue is known to contain non-zero value(s). More... | |

| bool | isEqualTo (SDValue A, SDValue B) const |

| Test whether two SDValues are known to compare equal. More... | |

| bool | haveNoCommonBitsSet (SDValue A, SDValue B) const |

| Return true if A and B have no common bits set. More... | |

| bool | isSplatValue (SDValue V, const APInt &DemandedElts, APInt &UndefElts) |

Test whether V has a splatted value for all the demanded elements. More... | |

| bool | isSplatValue (SDValue V, bool AllowUndefs=false) |

Test whether V has a splatted value. More... | |

| SDValue | matchBinOpReduction (SDNode *Extract, ISD::NodeType &BinOp, ArrayRef< ISD::NodeType > CandidateBinOps) |

| Match a binop + shuffle pyramid that represents a horizontal reduction over the elements of a vector starting from the EXTRACT_VECTOR_ELT node /p Extract. More... | |

| SDValue | UnrollVectorOp (SDNode *N, unsigned ResNE=0) |

| Utility function used by legalize and lowering to "unroll" a vector operation by splitting out the scalars and operating on each element individually. More... | |

| bool | areNonVolatileConsecutiveLoads (LoadSDNode *LD, LoadSDNode *Base, unsigned Bytes, int Dist) const |

| Return true if loads are next to each other and can be merged. More... | |

| unsigned | InferPtrAlignment (SDValue Ptr) const |

| Infer alignment of a load / store address. More... | |

| std::pair< EVT, EVT > | GetSplitDestVTs (const EVT &VT) const |

| Compute the VTs needed for the low/hi parts of a type which is split (or expanded) into two not necessarily identical pieces. More... | |

| std::pair< SDValue, SDValue > | SplitVector (const SDValue &N, const SDLoc &DL, const EVT &LoVT, const EVT &HiVT) |

| Split the vector with EXTRACT_SUBVECTOR using the provides VTs and return the low/high part. More... | |

| std::pair< SDValue, SDValue > | SplitVector (const SDValue &N, const SDLoc &DL) |

| Split the vector with EXTRACT_SUBVECTOR and return the low/high part. More... | |

| std::pair< SDValue, SDValue > | SplitVectorOperand (const SDNode *N, unsigned OpNo) |

| Split the node's operand with EXTRACT_SUBVECTOR and return the low/high part. More... | |

| void | ExtractVectorElements (SDValue Op, SmallVectorImpl< SDValue > &Args, unsigned Start=0, unsigned Count=0) |

| Append the extracted elements from Start to Count out of the vector Op in Args. More... | |

| unsigned | getEVTAlignment (EVT MemoryVT) const |

| Compute the default alignment value for the given type. More... | |

| SDNode * | isConstantIntBuildVectorOrConstantInt (SDValue N) |

| Test whether the given value is a constant int or similar node. More... | |

| SDNode * | isConstantFPBuildVectorOrConstantFP (SDValue N) |

| Test whether the given value is a constant FP or similar node. More... | |

| bool | isConstantValueOfAnyType (SDValue N) |

| SDValue | getConstant (uint64_t Val, const SDLoc &DL, EVT VT, bool isTarget=false, bool isOpaque=false) |

| Create a ConstantSDNode wrapping a constant value. More... | |

| SDValue | getConstant (const APInt &Val, const SDLoc &DL, EVT VT, bool isTarget=false, bool isOpaque=false) |

| SDValue | getAllOnesConstant (const SDLoc &DL, EVT VT, bool IsTarget=false, bool IsOpaque=false) |

| SDValue | getConstant (const ConstantInt &Val, const SDLoc &DL, EVT VT, bool isTarget=false, bool isOpaque=false) |

| SDValue | getIntPtrConstant (uint64_t Val, const SDLoc &DL, bool isTarget=false) |

| SDValue | getTargetConstant (uint64_t Val, const SDLoc &DL, EVT VT, bool isOpaque=false) |

| SDValue | getTargetConstant (const APInt &Val, const SDLoc &DL, EVT VT, bool isOpaque=false) |

| SDValue | getTargetConstant (const ConstantInt &Val, const SDLoc &DL, EVT VT, bool isOpaque=false) |

| SDValue | getBoolConstant (bool V, const SDLoc &DL, EVT VT, EVT OpVT) |

Create a true or false constant of type VT using the target's BooleanContent for type OpVT. More... | |

| SDValue | getConstantFP (double Val, const SDLoc &DL, EVT VT, bool isTarget=false) |

| Create a ConstantFPSDNode wrapping a constant value. More... | |

| SDValue | getConstantFP (const APFloat &Val, const SDLoc &DL, EVT VT, bool isTarget=false) |

| SDValue | getConstantFP (const ConstantFP &V, const SDLoc &DL, EVT VT, bool isTarget=false) |

| SDValue | getTargetConstantFP (double Val, const SDLoc &DL, EVT VT) |

| SDValue | getTargetConstantFP (const APFloat &Val, const SDLoc &DL, EVT VT) |

| SDValue | getTargetConstantFP (const ConstantFP &Val, const SDLoc &DL, EVT VT) |

Static Public Member Functions | |

| static const fltSemantics & | EVTToAPFloatSemantics (EVT VT) |

| Returns an APFloat semantics tag appropriate for the given type. More... | |

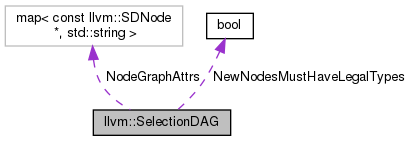

Public Attributes | |

| bool | NewNodesMustHaveLegalTypes = false |

| When true, additional steps are taken to ensure that getConstant() and similar functions return DAG nodes that have legal types. More... | |

| std::map< const SDNode *, std::string > | NodeGraphAttrs |

Friends | |

| struct | DAGUpdateListener |

| DAGUpdateListener is a friend so it can manipulate the listener stack. More... | |

Detailed Description

This is used to represent a portion of an LLVM function in a low-level Data Dependence DAG representation suitable for instruction selection.

This DAG is constructed as the first step of instruction selection in order to allow implementation of machine specific optimizations and code simplifications.

The representation used by the SelectionDAG is a target-independent representation, which has some similarities to the GCC RTL representation, but is significantly more simple, powerful, and is a graph form instead of a linear form.

Definition at line 222 of file SelectionDAG.h.

Member Typedef Documentation

◆ allnodes_const_iterator

| using llvm::SelectionDAG::allnodes_const_iterator = ilist<SDNode>::const_iterator |

Definition at line 435 of file SelectionDAG.h.

◆ allnodes_iterator

| using llvm::SelectionDAG::allnodes_iterator = ilist<SDNode>::iterator |

Definition at line 440 of file SelectionDAG.h.

Member Enumeration Documentation

◆ OverflowKind

Used to represent the possible overflow behavior of an operation.

Never: the operation cannot overflow. Always: the operation will always overflow. Sometime: the operation may or may not overflow.

| Enumerator | |

|---|---|

| OFK_Never | |

| OFK_Sometime | |

| OFK_Always | |

Definition at line 1449 of file SelectionDAG.h.

Constructor & Destructor Documentation

◆ SelectionDAG() [1/2]

|

explicit |

Definition at line 994 of file SelectionDAG.cpp.

References Other.

◆ SelectionDAG() [2/2]

|

delete |

◆ ~SelectionDAG()

| SelectionDAG::~SelectionDAG | ( | ) |

Definition at line 1016 of file SelectionDAG.cpp.

References assert(), llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::SDNode::getDebugLoc(), llvm::SDLoc::getDebugLoc(), llvm::SDNode::getIROrder(), llvm::SDLoc::getIROrder(), llvm::SDNode::getOpcode(), llvm_unreachable, N, and llvm::SDNode::setDebugLoc().

Member Function Documentation

◆ AddDbgLabel()

| void SelectionDAG::AddDbgLabel | ( | SDDbgLabel * | DB | ) |

Add a dbg_label SDNode.

Definition at line 8502 of file SelectionDAG.cpp.

Referenced by getUnderlyingArgReg().

◆ AddDbgValue()

| void SelectionDAG::AddDbgValue | ( | SDDbgValue * | DB, |

| SDNode * | SD, | ||

| bool | isParameter | ||

| ) |

Add a dbg_value SDNode.

AddDbgValue - Add a dbg_value SDNode.

If SD is non-null that means the value is produced by SD.

Definition at line 8494 of file SelectionDAG.cpp.

References assert(), llvm::SDNode::getHasDebugValue(), and llvm::SDNode::setHasDebugValue().

Referenced by getUnderlyingArgReg(), llvm::SelectionDAGBuilder::resolveDanglingDebugInfo(), salvageDebugInfo(), and transferDbgValues().

◆ allnodes() [1/2]

|

inline |

Definition at line 449 of file SelectionDAG.h.

References llvm::make_range().

Referenced by llvm::HexagonDAGToDAGISel::PreprocessISelDAG(), updateDivergence(), and VerifyDAGDiverence().

◆ allnodes() [2/2]

|

inline |

Definition at line 452 of file SelectionDAG.h.

References llvm::make_range().

◆ allnodes_begin() [1/2]

|

inline |

Definition at line 437 of file SelectionDAG.h.

Referenced by AssignTopologicalOrder(), llvm::SelectionDAGISel::getUninvalidatedNodeId(), isTargetConstant(), and llvm::GraphTraits< SelectionDAG * >::nodes_begin().

◆ allnodes_begin() [2/2]

|

inline |

Definition at line 442 of file SelectionDAG.h.

◆ allnodes_end() [1/2]

|

inline |

Definition at line 438 of file SelectionDAG.h.

Referenced by AssignTopologicalOrder(), isTargetConstant(), and llvm::GraphTraits< SelectionDAG * >::nodes_end().

◆ allnodes_end() [2/2]

|

inline |

Definition at line 443 of file SelectionDAG.h.

◆ allnodes_size()

Definition at line 445 of file SelectionDAG.h.

Referenced by llvm::HexagonDAGToDAGISel::PreprocessISelDAG().

◆ areNonVolatileConsecutiveLoads()

| bool SelectionDAG::areNonVolatileConsecutiveLoads | ( | LoadSDNode * | LD, |

| LoadSDNode * | Base, | ||

| unsigned | Bytes, | ||

| int | Dist | ||

| ) | const |

Return true if loads are next to each other and can be merged.

Check that both are nonvolatile and if LD is loading 'Bytes' bytes from a location that is 'Dist' units away from the location that the 'Base' load is loading from.

Definition at line 8976 of file SelectionDAG.cpp.

References llvm::MemSDNode::getChain(), llvm::EVT::getSizeInBits(), llvm::SDNode::getValueType(), llvm::LSBaseSDNode::isIndexed(), llvm::MemSDNode::isVolatile(), and llvm::BaseIndexOffset::match().

Referenced by EltsFromConsecutiveLoads(), and getBuildPairElt().

◆ AssignTopologicalOrder()

| unsigned SelectionDAG::AssignTopologicalOrder | ( | ) |

Topological-sort the AllNodes list and a assign a unique node id for each node in the DAG based on their topological order.

AssignTopologicalOrder - Assign a unique node id for each node in the DAG based on their topological order.

Returns the number of nodes.

It returns the maximum id and a vector of the SDNodes* in assigned order by reference.

Definition at line 8405 of file SelectionDAG.cpp.

References allnodes_begin(), allnodes_end(), assert(), llvm::checkForCycles(), E, llvm::SDNode::getNumOperands(), I, and llvm::SDNode::setNodeId().

Referenced by llvm::SelectionDAGISel::getUninvalidatedNodeId().

◆ ByvalParmDbgBegin()

|

inline |

Definition at line 1364 of file SelectionDAG.h.

References llvm::SDDbgInfo::ByvalParmDbgBegin().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ ByvalParmDbgEnd()

|

inline |

Definition at line 1368 of file SelectionDAG.h.

References llvm::SDDbgInfo::ByvalParmDbgEnd().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ clear()

| void SelectionDAG::clear | ( | ) |

Clear state and free memory necessary to make this SelectionDAG ready to process a new block.

Definition at line 1073 of file SelectionDAG.cpp.

References llvm::SDDbgInfo::clear(), getEntryNode(), and llvm::BumpPtrAllocatorImpl< AllocatorT, SlabSize, SizeThreshold >::Reset().

◆ clearGraphAttrs()

| void SelectionDAG::clearGraphAttrs | ( | ) |

Clear all previously defined node graph attributes.

clearGraphAttrs - Clear all previously defined node graph attributes.

Intended to be used from a debugging tool (eg. gdb).

Definition at line 170 of file SelectionDAGPrinter.cpp.

References llvm::errs().

◆ Combine()

| void SelectionDAG::Combine | ( | CombineLevel | Level, |

| AliasAnalysis * | AA, | ||

| CodeGenOpt::Level | OptLevel | ||

| ) |

This iterates over the nodes in the SelectionDAG, folding certain types of nodes together, or eliminating superfluous nodes.

This is the entry point for the file.

The Level argument controls whether Combine is allowed to produce nodes and types that are illegal on the target.

This is the main entry point to this class.

Definition at line 19397 of file DAGCombiner.cpp.

◆ computeKnownBits() [1/2]

Determine which bits of Op are known to be either zero or one and return them in Known.

For vectors, the known bits are those that are shared by every vector element. Targets can implement the computeKnownBitsForTargetNode method in the TargetLowering class to allow target nodes to be understood.

For vectors, the known bits are those that are shared by every vector element.

Definition at line 2286 of file SelectionDAG.cpp.

References llvm::APInt::getAllOnesValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), and llvm::EVT::isVector().

Referenced by adjustForRedundantAnd(), calculateByteProvider(), llvm::SelectionDAGISel::CheckOrMask(), combineSubToSubus(), combineVectorSignBitsTruncation(), computeKnownBits(), computeKnownBitsBinOp(), llvm::SparcTargetLowering::computeKnownBitsForTargetNode(), llvm::LanaiTargetLowering::computeKnownBitsForTargetNode(), llvm::AMDGPUTargetLowering::computeKnownBitsForTargetNode(), llvm::AArch64TargetLowering::computeKnownBitsForTargetNode(), llvm::ARMTargetLowering::computeKnownBitsForTargetNode(), llvm::SystemZTargetLowering::computeKnownBitsForTargetNode(), llvm::X86TargetLowering::computeKnownBitsForTargetNode(), ComputeNumSignBits(), computeOverflowKind(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), foldMaskAndShiftToScale(), generateEquivalentSub(), haveNoCommonBitsSet(), isBitfieldPositioningOp(), isKnownToBeAPowerOfTwo(), isTruncateOf(), isWordAligned(), LowerAndToBT(), LowerMUL(), LowerTruncateVecI1(), MaskedValueIsZero(), matchRotateSub(), llvm::AMDGPUTargetLowering::numBitsUnsigned(), llvm::ARMTargetLowering::PerformCMOVCombine(), llvm::ARMTargetLowering::PerformCMOVToBFICombine(), llvm::AMDGPUTargetLowering::performShlCombine(), llvm::AMDGPUTargetLowering::performTruncateCombine(), llvm::PPCTargetLowering::SelectAddressRegImm(), llvm::PPCTargetLowering::SelectAddressRegReg(), llvm::TargetLowering::SimplifyDemandedBits(), tryBitfieldInsertOpFromOr(), and tryBitfieldInsertOpFromOrAndImm().

◆ computeKnownBits() [2/2]

| KnownBits SelectionDAG::computeKnownBits | ( | SDValue | Op, |

| const APInt & | DemandedElts, | ||

| unsigned | Depth = 0 |

||

| ) | const |

Determine which bits of Op are known to be either zero or one and return them in Known.

The DemandedElts argument allows us to only collect the known bits that are shared by the requested vector elements. Targets can implement the computeKnownBitsForTargetNode method in the TargetLowering class to allow target nodes to be understood.

The DemandedElts argument allows us to only collect the known bits that are shared by the requested vector elements.

Definition at line 2297 of file SelectionDAG.cpp.

References llvm::ISD::ABS, llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::ADDCARRY, llvm::ISD::ADDE, llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::APInt::ashrInPlace(), assert(), llvm::ISD::AssertZext, llvm::ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS, llvm::ISD::BITCAST, llvm::ISD::BITREVERSE, llvm::ISD::BSWAP, llvm::ISD::BUILD_VECTOR, llvm::ISD::BUILTIN_OP_END, llvm::APInt::byteSwap(), C, llvm::APInt::clearAllBits(), llvm::APInt::clearSignBit(), computeKnownBits(), llvm::TargetLowering::computeKnownBitsForFrameIndex(), llvm::TargetLowering::computeKnownBitsForTargetNode(), llvm::computeKnownBitsFromRangeMetadata(), llvm::ISD::CONCAT_VECTORS, llvm::countLeadingZeros(), llvm::KnownBits::countMaxLeadingZeros(), llvm::KnownBits::countMaxPopulation(), llvm::KnownBits::countMaxTrailingZeros(), llvm::KnownBits::countMinLeadingOnes(), llvm::KnownBits::countMinLeadingZeros(), llvm::KnownBits::countMinTrailingZeros(), llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::dyn_cast(), llvm::ISD::EXTRACT_ELEMENT, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::APInt::extractBits(), llvm::ISD::FGETSIGN, llvm::ISD::FrameIndex, llvm::ISD::FSHL, llvm::ISD::FSHR, llvm::APInt::getAllOnesValue(), llvm::ConstantSDNode::getAPIntValue(), llvm::APInt::getBitsSet(), llvm::APInt::getBitWidth(), llvm::TargetLoweringBase::getBooleanContents(), llvm::APInt::getBoolValue(), llvm::SDValue::getConstantOperandVal(), getDataLayout(), llvm::LoadSDNode::getExtensionType(), llvm::APInt::getHiBits(), llvm::APInt::getHighBitsSet(), llvm::APInt::getLowBitsSet(), llvm::ShuffleVectorSDNode::getMask(), llvm::ShuffleVectorSDNode::getMaskElt(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::SDValue::getNumOperands(), llvm::APInt::getNumSignBits(), llvm::APInt::getOneBitSet(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::MemSDNode::getRanges(), llvm::SDValue::getResNo(), llvm::EVT::getScalarSizeInBits(), llvm::SDValue::getScalarValueSizeInBits(), llvm::APInt::getSignMask(), llvm::EVT::getSizeInBits(), getValidShiftAmountConstant(), llvm::SDValue::getValueSizeInBits(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::ConstantSDNode::getZExtValue(), llvm::APInt::getZExtValue(), llvm::KnownBits::hasConflict(), if(), llvm::ISD::INSERT_SUBVECTOR, llvm::ISD::INSERT_VECTOR_ELT, llvm::APInt::intersects(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::isConstOrConstSplat(), isConstOrDemandedConstSplat(), llvm::EVT::isFloatingPoint(), llvm::EVT::isInteger(), llvm::DataLayout::isLittleEndian(), llvm::APInt::isNegative(), llvm::APInt::isNonNegative(), llvm::APInt::isPowerOf2(), llvm::KnownBits::isUnknown(), llvm::EVT::isVector(), llvm::ISD::isZEXTLoad(), llvm::ARM_MB::LD, LLVM_FALLTHROUGH, llvm::ISD::LOAD, llvm::Log2_32(), llvm::APInt::lshr(), llvm::APInt::lshrInPlace(), llvm::max(), llvm::ISD::MUL, llvm::ISD::NON_EXTLOAD, llvm::KnownBits::One, llvm::ISD::OR, RA, llvm::KnownBits::resetAll(), llvm::APInt::reverseBits(), llvm::ISD::SADDO, llvm::ISD::SCALAR_TO_VECTOR, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::APInt::setAllBits(), llvm::APInt::setBit(), llvm::APInt::setBits(), llvm::APInt::setBitsFrom(), llvm::ISD::SETCC, llvm::APInt::setHighBits(), llvm::APInt::setLowBits(), llvm::KnownBits::sext(), llvm::ISD::SHL, llvm::APInt::shl(), llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SIGN_EXTEND_VECTOR_INREG, llvm::APInt::sle(), llvm::ISD::SMAX, llvm::ISD::SMIN, llvm::ISD::SMULO, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::ISD::SSUBO, llvm::ISD::SUB, llvm::ISD::SUBC, std::swap(), llvm::ISD::TargetFrameIndex, llvm::KnownBits::trunc(), llvm::APInt::trunc(), llvm::ISD::TRUNCATE, llvm::ISD::UADDO, llvm::ISD::UDIV, llvm::APInt::ule(), llvm::APInt::ult(), llvm::ISD::UMAX, llvm::ISD::UMIN, llvm::ISD::UMULO, llvm::ISD::UREM, llvm::ISD::USUBO, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, llvm::ISD::XOR, llvm::KnownBits::Zero, llvm::ISD::ZERO_EXTEND, llvm::ISD::ZERO_EXTEND_VECTOR_INREG, llvm::TargetLoweringBase::ZeroOrOneBooleanContent, llvm::KnownBits::zext(), llvm::APInt::zext(), llvm::APInt::zextOrSelf(), and llvm::APInt::zextOrTrunc().

◆ ComputeNumSignBits() [1/2]

Return the number of times the sign bit of the register is replicated into the other bits.

We know that at least 1 bit is always equal to the sign bit (itself), but other cases can give us information. For example, immediately after an "SRA X, 2", we know that the top 3 bits are all equal to each other, so we return 3. Targets can implement the ComputeNumSignBitsForTarget method in the TargetLowering class to allow target nodes to be understood.

Definition at line 3275 of file SelectionDAG.cpp.

References llvm::APInt::getAllOnesValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), and llvm::EVT::isVector().

Referenced by calculateByteProvider(), canReduceVMulWidth(), combineAndMaskToShift(), combineHorizontalPredicateResult(), combineLogicBlendIntoPBLENDV(), combineMulToPMULDQ(), combineSIntToFP(), combineVectorPack(), combineVectorSignBitsTruncation(), combineVSelectWithAllOnesOrZeros(), ComputeNumSignBits(), computeNumSignBitsBinOp(), llvm::AMDGPUTargetLowering::ComputeNumSignBitsForTargetNode(), llvm::SystemZTargetLowering::ComputeNumSignBitsForTargetNode(), llvm::X86TargetLowering::ComputeNumSignBitsForTargetNode(), llvm::TargetLowering::expandMUL_LOHI(), foldExtendedSignBitTest(), generateEquivalentSub(), getAsCarry(), getFauxShuffleMask(), getShiftAmountTyForConstant(), isADDADDMUL(), isS16(), isTruncateOf(), llvm::AMDGPUTargetLowering::LowerDIVREM24(), llvm::AMDGPUTargetLowering::LowerSDIVREM(), LowerTruncateVecI1(), lowerVSELECTtoVectorShuffle(), matchVectorShuffleWithPACK(), llvm::AMDGPUTargetLowering::numBitsSigned(), llvm::AMDGPUTargetLowering::PerformDAGCombine(), and llvm::X86TargetLowering::SimplifyDemandedBitsForTargetNode().

◆ ComputeNumSignBits() [2/2]

| unsigned SelectionDAG::ComputeNumSignBits | ( | SDValue | Op, |

| const APInt & | DemandedElts, | ||

| unsigned | Depth = 0 |

||

| ) | const |

Return the number of times the sign bit of the register is replicated into the other bits.

We know that at least 1 bit is always equal to the sign bit (itself), but other cases can give us information. For example, immediately after an "SRA X, 2", we know that the top 3 bits are all equal to each other, so we return 3. The DemandedElts argument allows us to only collect the minimum sign bits of the requested vector elements. Targets can implement the ComputeNumSignBitsForTarget method in the TargetLowering class to allow target nodes to be understood.

Definition at line 3283 of file SelectionDAG.cpp.

References llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::AND, assert(), llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::ISD::BUILTIN_OP_END, C, llvm::APInt::clearBit(), computeKnownBits(), ComputeNumSignBits(), llvm::TargetLowering::ComputeNumSignBitsForTargetNode(), llvm::ISD::CONCAT_VECTORS, llvm::APInt::countLeadingZeros(), llvm::dyn_cast(), llvm::ISD::EXTRACT_ELEMENT, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::APInt::extractBits(), llvm::APInt::getAllOnesValue(), llvm::ConstantSDNode::getAPIntValue(), llvm::APInt::getBitsSet(), llvm::APInt::getBitWidth(), llvm::TargetLoweringBase::getBooleanContents(), llvm::SDValue::getConstantOperandVal(), getDataLayout(), llvm::ShuffleVectorSDNode::getMask(), llvm::ShuffleVectorSDNode::getMaskElt(), llvm::SDValue::getNumOperands(), llvm::APInt::getNumSignBits(), llvm::APInt::getOneBitSet(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getResNo(), llvm::EVT::getScalarSizeInBits(), llvm::SDValue::getScalarValueSizeInBits(), llvm::SDValue::getValueSizeInBits(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::ConstantSDNode::getZExtValue(), llvm::APInt::getZExtValue(), llvm::ISD::INSERT_SUBVECTOR, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::isConstOrConstSplat(), isConstOrDemandedConstSplat(), llvm::EVT::isFloatingPoint(), llvm::EVT::isInteger(), llvm::DataLayout::isLittleEndian(), llvm::KnownBits::isNegative(), llvm::KnownBits::isNonNegative(), llvm::EVT::isVector(), llvm::ARM_MB::LD, llvm::APInt::lshr(), llvm::BitmaskEnumDetail::Mask(), llvm::max(), llvm::KnownBits::One, llvm::ISD::OR, llvm::ISD::ROTL, llvm::ISD::ROTR, llvm::ISD::SADDO, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::APInt::setBit(), llvm::ISD::SETCC, llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::APInt::shl(), llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SIGN_EXTEND_VECTOR_INREG, llvm::APInt::sle(), llvm::ISD::SMAX, llvm::ISD::SMIN, llvm::ISD::SMULO, llvm::ISD::SRA, llvm::ISD::SSUBO, llvm::ISD::SUB, std::swap(), llvm::APInt::trunc(), llvm::ISD::TRUNCATE, llvm::ISD::UADDO, llvm::APInt::uge(), llvm::APInt::ule(), llvm::APInt::ult(), llvm::ISD::UMAX, llvm::ISD::UMIN, llvm::ISD::UMULO, llvm::ISD::USUBO, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, llvm::ISD::XOR, llvm::KnownBits::Zero, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, llvm::ISD::ZEXTLOAD, and llvm::APInt::zextOrSelf().

◆ computeOverflowKind()

| SelectionDAG::OverflowKind SelectionDAG::computeOverflowKind | ( | SDValue | N0, |

| SDValue | N1 | ||

| ) | const |

Determine if the result of the addition of 2 node can overflow.

Definition at line 3203 of file SelectionDAG.cpp.

References computeKnownBits(), llvm::APInt::getBoolValue(), llvm::SDValue::getOpcode(), llvm::SDValue::getResNo(), llvm::isNullConstant(), OFK_Never, OFK_Sometime, llvm::ISD::UMUL_LOHI, and llvm::KnownBits::Zero.

Referenced by foldAddSubOfSignBit(), getAsCarry(), and isBooleanFlip().

◆ CreateStackTemporary() [1/2]

Create a stack temporary, suitable for holding the specified value type.

If minAlign is specified, the slot size will have at least that alignment.

Definition at line 1922 of file SelectionDAG.cpp.

References llvm::MachineFrameInfo::CreateStackObject(), getContext(), getDataLayout(), getFrameIndex(), llvm::TargetLoweringBase::getFrameIndexTy(), llvm::MachineFunction::getFrameInfo(), getMachineFunction(), llvm::EVT::getStoreSize(), llvm::EVT::getTypeForEVT(), and llvm::max().

Referenced by llvm::StatepointLoweringState::allocateStackSlot(), llvm::TargetLowering::expandUnalignedLoad(), llvm::TargetLowering::expandUnalignedStore(), getExpandedMinMaxOps(), getMOVL(), llvm::SystemZTargetLowering::LowerCall(), LowerMULH(), lowerUINT_TO_FP_vec(), PrepareCall(), and unpackF64OnRV32DSoftABI().

◆ CreateStackTemporary() [2/2]

Create a stack temporary suitable for holding either of the specified value types.

Definition at line 1933 of file SelectionDAG.cpp.

References llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, llvm::MachineFrameInfo::CreateStackObject(), getContext(), getDataLayout(), getFrameIndex(), llvm::TargetLoweringBase::getFrameIndexTy(), llvm::MachineFunction::getFrameInfo(), getMachineFunction(), llvm::DataLayout::getPrefTypeAlignment(), llvm::EVT::getStoreSize(), llvm::EVT::getTypeForEVT(), and llvm::max().

◆ DbgBegin()

|

inline |

Definition at line 1361 of file SelectionDAG.h.

References llvm::SDDbgInfo::DbgBegin().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ DbgEnd()

|

inline |

Definition at line 1362 of file SelectionDAG.h.

References llvm::SDDbgInfo::DbgEnd().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ DbgLabelBegin()

|

inline |

Definition at line 1372 of file SelectionDAG.h.

References llvm::SDDbgInfo::DbgLabelBegin().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ DbgLabelEnd()

|

inline |

Definition at line 1375 of file SelectionDAG.h.

References llvm::computeKnownBits(), llvm::SDDbgInfo::DbgLabelEnd(), llvm::Depth, llvm::dump(), llvm::MaskedValueIsZero(), and llvm::salvageDebugInfo().

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ DeleteNode()

| void SelectionDAG::DeleteNode | ( | SDNode * | N | ) |

Remove the specified node from the system.

This node must have no referrers.

Definition at line 740 of file SelectionDAG.cpp.

References assert(), llvm::SDNode::DropOperands(), llvm::ilist_node_impl< OptionsT >::getIterator(), N, and llvm::SDNode::use_empty().

Referenced by addStackMapLiveVars(), llvm::TargetLowering::DAGCombinerInfo::CommitTargetLoweringOpt(), and isAnyConstantBuildVector().

◆ dump()

| LLVM_DUMP_METHOD void SelectionDAG::dump | ( | ) | const |

Definition at line 744 of file SelectionDAGDumper.cpp.

Referenced by llvm::HexagonDAGToDAGISel::PreprocessISelDAG().

◆ EVTToAPFloatSemantics()

|

inlinestatic |

Returns an APFloat semantics tag appropriate for the given type.

If VT is a vector type, the element semantics are returned.

Definition at line 1332 of file SelectionDAG.h.

References llvm::MVT::f128, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::f80, llvm::EVT::getScalarType(), llvm::EVT::getSimpleVT(), llvm::APFloatBase::IEEEdouble(), llvm::APFloatBase::IEEEhalf(), llvm::APFloatBase::IEEEquad(), llvm::APFloatBase::IEEEsingle(), llvm_unreachable, llvm::APFloatBase::PPCDoubleDouble(), llvm::MVT::ppcf128, llvm::MVT::SimpleTy, and llvm::APFloatBase::x87DoubleExtended().

Referenced by FoldIntToFPToInt(), getConstantFP(), getExpandedMinMaxOps(), GetFPLibCall(), getMemsetValue(), getNode(), llvm::ConstantFPSDNode::isValueValidForType(), LowerFABSorFNEG(), LowerFCOPYSIGN(), replaceShuffleOfInsert(), and vectorEltWillFoldAway().

◆ expandVAArg()

Expand the specified ISD::VAARG node as the Legalize pass would.

Definition at line 1873 of file SelectionDAG.cpp.

◆ expandVACopy()

Expand the specified ISD::VACOPY node as the Legalize pass would.

Definition at line 1908 of file SelectionDAG.cpp.

Referenced by LowerVACOPY().

◆ ExtractVectorElements()

| void SelectionDAG::ExtractVectorElements | ( | SDValue | Op, |

| SmallVectorImpl< SDValue > & | Args, | ||

| unsigned | Start = 0, |

||

| unsigned | Count = 0 |

||

| ) |

Append the extracted elements from Start to Count out of the vector Op in Args.

If Count is 0, all of the elements will be extracted.

Definition at line 9068 of file SelectionDAG.cpp.

Referenced by adjustLoadValueTypeImpl(), constructRetValue(), llvm::AMDGPUTargetLowering::LowerCONCAT_VECTORS(), llvm::AMDGPUTargetLowering::LowerSIGN_EXTEND_INREG(), parseTexFail(), and widenVectorToPartType().

◆ FoldConstantArithmetic() [1/2]

| SDValue SelectionDAG::FoldConstantArithmetic | ( | unsigned | Opcode, |

| const SDLoc & | DL, | ||

| EVT | VT, | ||

| SDNode * | Cst1, | ||

| SDNode * | Cst2 | ||

| ) |

Definition at line 4573 of file SelectionDAG.cpp.

References assert(), llvm::SmallVectorTemplateCommon< T >::back(), llvm::EVT::bitsGT(), llvm::EVT::bitsLT(), llvm::ISD::BUILTIN_OP_END, llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::dyn_cast(), FoldSymbolOffset(), getBuildVector(), getContext(), getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOperand(), llvm::EVT::getScalarType(), llvm::TargetLoweringBase::getTypeToTransformTo(), getUNDEF(), llvm::SDNode::getValueType(), llvm::EVT::getVectorNumElements(), I, llvm::TargetLoweringBase::isCommutativeBinOp(), llvm::EVT::isInteger(), llvm::SDValue::isUndef(), llvm::SDNode::isUndef(), isUndef(), llvm::EVT::isVector(), NewNodesMustHaveLegalTypes, llvm::SmallVectorTemplateBase< T >::push_back(), llvm::SmallVectorImpl< T >::resize(), llvm::ISD::SIGN_EXTEND, llvm::SmallVectorBase::size(), llvm::ISD::TRUNCATE, and llvm::NVPTX::PTXLdStInstCode::V2.

Referenced by calculateByteProvider(), foldAddSubOfSignBit(), getNode(), isAnyConstantBuildVector(), isBSwapHWordElement(), simplifyDivRem(), and tryFoldToZero().

◆ FoldConstantArithmetic() [2/2]

| SDValue SelectionDAG::FoldConstantArithmetic | ( | unsigned | Opcode, |

| const SDLoc & | DL, | ||

| EVT | VT, | ||

| const ConstantSDNode * | Cst1, | ||

| const ConstantSDNode * | Cst2 | ||

| ) |

Definition at line 4515 of file SelectionDAG.cpp.

References FoldValue(), llvm::ConstantSDNode::getAPIntValue(), getConstant(), and llvm::ConstantSDNode::isOpaque().

◆ FoldConstantVectorArithmetic()

| SDValue SelectionDAG::FoldConstantVectorArithmetic | ( | unsigned | Opcode, |

| const SDLoc & | DL, | ||

| EVT | VT, | ||

| ArrayRef< SDValue > | Ops, | ||

| const SDNodeFlags | Flags = SDNodeFlags() |

||

| ) |

Definition at line 4662 of file SelectionDAG.cpp.

References llvm::all_of(), llvm::EVT::bitsGT(), llvm::EVT::bitsLT(), llvm::ISD::BUILTIN_OP_END, llvm::ISD::CONDCODE, llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::dyn_cast(), getBuildVector(), getContext(), getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOperand(), llvm::EVT::getScalarType(), llvm::TargetLoweringBase::getTypeToTransformTo(), getUNDEF(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::i1, llvm::BuildVectorSDNode::isConstant(), llvm::EVT::isInteger(), llvm::SDValue::isUndef(), isUndef(), llvm::EVT::isVector(), NewNodesMustHaveLegalTypes, NewSDValueDbgMsg(), llvm::SmallVectorTemplateBase< T >::push_back(), llvm::ISD::SETCC, llvm::ISD::SIGN_EXTEND, and llvm::ISD::TRUNCATE.

Referenced by getNode(), and replaceShuffleOfInsert().

◆ FoldSetCC()

| SDValue SelectionDAG::FoldSetCC | ( | EVT | VT, |

| SDValue | N1, | ||

| SDValue | N2, | ||

| ISD::CondCode | Cond, | ||

| const SDLoc & | dl | ||

| ) |

Constant fold a setcc to true or false.

Definition at line 1946 of file SelectionDAG.cpp.

References assert(), llvm::APFloatBase::cmpEqual, llvm::APFloatBase::cmpGreaterThan, llvm::APFloatBase::cmpLessThan, llvm::APFloatBase::cmpUnordered, getBoolConstant(), getSetCC(), llvm::ISD::getSetCCSwappedOperands(), llvm::EVT::getSimpleVT(), getUNDEF(), llvm::SDValue::getValueType(), llvm::TargetLoweringBase::isCondCodeLegal(), llvm::EVT::isInteger(), LLVM_FALLTHROUGH, llvm_unreachable, llvm::ISD::SETEQ, llvm::ISD::SETFALSE, llvm::ISD::SETFALSE2, llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETLE, llvm::ISD::SETLT, llvm::ISD::SETNE, llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::ISD::SETONE, llvm::ISD::SETTRUE, llvm::ISD::SETTRUE2, llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETULE, llvm::ISD::SETULT, llvm::ISD::SETUNE, llvm::ISD::SETUO, llvm::APInt::sge(), llvm::APInt::sgt(), llvm::APInt::sle(), llvm::APInt::slt(), llvm::APInt::uge(), llvm::APInt::ugt(), llvm::APInt::ule(), and llvm::APInt::ult().

Referenced by getNode(), and llvm::TargetLowering::SimplifySetCC().

◆ FoldSymbolOffset()

| SDValue SelectionDAG::FoldSymbolOffset | ( | unsigned | Opcode, |

| EVT | VT, | ||

| const GlobalAddressSDNode * | GA, | ||

| const SDNode * | N2 | ||

| ) |

Definition at line 4528 of file SelectionDAG.cpp.

References llvm::ISD::ADD, llvm::dyn_cast(), llvm::GlobalAddressSDNode::getGlobal(), getGlobalAddress(), llvm::GlobalAddressSDNode::getOffset(), llvm::SDNode::getOpcode(), llvm::ConstantSDNode::getSExtValue(), llvm::ISD::GlobalAddress, llvm::TargetLowering::isOffsetFoldingLegal(), and llvm::ISD::SUB.

Referenced by FoldConstantArithmetic().

◆ getAddrSpaceCast()

| SDValue SelectionDAG::getAddrSpaceCast | ( | const SDLoc & | dl, |

| EVT | VT, | ||

| SDValue | Ptr, | ||

| unsigned | SrcAS, | ||

| unsigned | DestAS | ||

| ) |

Return an AddrSpaceCastSDNode.

Definition at line 1842 of file SelectionDAG.cpp.

References llvm::FoldingSetNodeID::AddInteger(), AddNodeIDNode(), llvm::ISD::ADDRSPACECAST, E, llvm::SDLoc::getDebugLoc(), llvm::SDLoc::getIROrder(), and getVTList().

Referenced by hasOnlySelectUsers().

◆ getAllOnesConstant()

|

inline |

Definition at line 566 of file SelectionDAG.h.

References llvm::APInt::getAllOnesValue(), getConstant(), and llvm::EVT::getScalarSizeInBits().

Referenced by calculateByteProvider(), combineHorizontalPredicateResult(), foldAddSubOfSignBit(), foldExtendedSignBitTest(), getBoolConstant(), getNode(), isBSwapHWordElement(), isLowerSaturatingConditional(), lowerVectorShuffleAsBitBlend(), lowerVectorShuffleAsBitMask(), matchRotateSub(), and simplifyDivRem().

◆ getAnyExtOrTrunc()

Convert Op, which must be of integer type, to the integer type VT, by either any-extending or truncating it.

Definition at line 1100 of file SelectionDAG.cpp.

References llvm::ISD::ANY_EXTEND, llvm::EVT::bitsGT(), getNode(), llvm::SDValue::getValueType(), and llvm::ISD::TRUNCATE.

Referenced by combineBitcast(), combineToExtendBoolVectorInReg(), createGPRPairNode(), createMMXBuildVector(), findUser(), generateEquivalentSub(), getCopyFromPartsVector(), getCopyToPartsVector(), getExpandedMinMaxOps(), getNode(), getShiftAmountTyForConstant(), isTruncateOf(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBuildVectorAsInsert(), LowerBuildVectorv16i8(), LowerMUL(), scalarizeExtractedBinop(), and ShrinkLoadReplaceStoreWithStore().

◆ getAtomic() [1/4]

| SDValue SelectionDAG::getAtomic | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| SDValue | Chain, | ||

| SDValue | Ptr, | ||

| SDValue | Val, | ||

| const Value * | PtrVal, | ||

| unsigned | Alignment, | ||

| AtomicOrdering | Ordering, | ||

| SyncScope::ID | SSID | ||

| ) |

Gets a node for an atomic op, produces result (if relevant) and chain and takes 2 operands.

Definition at line 6425 of file SelectionDAG.cpp.

References llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, getEVTAlignment(), getMachineFunction(), llvm::MachineFunction::getMachineMemOperand(), llvm::EVT::getStoreSize(), llvm::MachineMemOperand::MOLoad, llvm::MachineMemOperand::MOStore, and llvm::MachineMemOperand::MOVolatile.

Referenced by combineSetCCAtomicArith(), getAtomic(), getAtomicCmpSwap(), getExpandedMinMaxOps(), getReductionSDNode(), getShiftAmountTyForConstant(), getUniformBase(), and lowerAtomicArith().

◆ getAtomic() [2/4]

| SDValue SelectionDAG::getAtomic | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| SDValue | Chain, | ||

| SDValue | Ptr, | ||

| SDValue | Val, | ||

| MachineMemOperand * | MMO | ||

| ) |

Definition at line 6454 of file SelectionDAG.cpp.

References assert(), llvm::ISD::ATOMIC_LOAD_ADD, llvm::ISD::ATOMIC_LOAD_AND, llvm::ISD::ATOMIC_LOAD_CLR, llvm::ISD::ATOMIC_LOAD_MAX, llvm::ISD::ATOMIC_LOAD_MIN, llvm::ISD::ATOMIC_LOAD_NAND, llvm::ISD::ATOMIC_LOAD_OR, llvm::ISD::ATOMIC_LOAD_SUB, llvm::ISD::ATOMIC_LOAD_UMAX, llvm::ISD::ATOMIC_LOAD_UMIN, llvm::ISD::ATOMIC_LOAD_XOR, llvm::ISD::ATOMIC_STORE, llvm::ISD::ATOMIC_SWAP, getAtomic(), llvm::SDValue::getValueType(), getVTList(), and llvm::MVT::Other.

◆ getAtomic() [3/4]

| SDValue SelectionDAG::getAtomic | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| EVT | VT, | ||

| SDValue | Chain, | ||

| SDValue | Ptr, | ||

| MachineMemOperand * | MMO | ||

| ) |

Gets a node for an atomic op, produces result and chain and takes 1 operand.

Definition at line 6480 of file SelectionDAG.cpp.

References assert(), llvm::ISD::ATOMIC_LOAD, getAtomic(), getVTList(), and llvm::MVT::Other.

◆ getAtomic() [4/4]

| SDValue SelectionDAG::getAtomic | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| SDVTList | VTList, | ||

| ArrayRef< SDValue > | Ops, | ||

| MachineMemOperand * | MMO | ||

| ) |

Gets a node for an atomic op, produces result and chain and takes N operands.

Definition at line 6365 of file SelectionDAG.cpp.

References llvm::FoldingSetNodeID::AddInteger(), AddNodeIDNode(), E, llvm::MachinePointerInfo::getAddrSpace(), llvm::SDLoc::getDebugLoc(), llvm::SDLoc::getIROrder(), llvm::MachineMemOperand::getPointerInfo(), and llvm::EVT::getRawBits().

◆ getAtomicCmpSwap() [1/2]

| SDValue SelectionDAG::getAtomicCmpSwap | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| SDVTList | VTs, | ||

| SDValue | Chain, | ||

| SDValue | Ptr, | ||

| SDValue | Cmp, | ||

| SDValue | Swp, | ||

| MachinePointerInfo | PtrInfo, | ||

| unsigned | Alignment, | ||

| AtomicOrdering | SuccessOrdering, | ||

| AtomicOrdering | FailureOrdering, | ||

| SyncScope::ID | SSID | ||

| ) |

Gets a node for an atomic cmpxchg op.

There are two valid Opcodes. ISD::ATOMIC_CMO_SWAP produces the value loaded and a chain result. ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS produces the value loaded, a success flag (initially i1), and a chain.

Definition at line 6387 of file SelectionDAG.cpp.

References assert(), llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS, getEVTAlignment(), getMachineFunction(), llvm::MachineFunction::getMachineMemOperand(), llvm::EVT::getStoreSize(), llvm::SDValue::getValueType(), llvm::MachineMemOperand::MOLoad, llvm::MachineMemOperand::MOStore, and llvm::MachineMemOperand::MOVolatile.

Referenced by getExpandedMinMaxOps(), getShiftAmountTyForConstant(), and getUniformBase().

◆ getAtomicCmpSwap() [2/2]

| SDValue SelectionDAG::getAtomicCmpSwap | ( | unsigned | Opcode, |

| const SDLoc & | dl, | ||

| EVT | MemVT, | ||

| SDVTList | VTs, | ||

| SDValue | Chain, | ||

| SDValue | Ptr, | ||

| SDValue | Cmp, | ||

| SDValue | Swp, | ||

| MachineMemOperand * | MMO | ||

| ) |

Definition at line 6413 of file SelectionDAG.cpp.

References assert(), llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS, getAtomic(), and llvm::SDValue::getValueType().

◆ getAtomicMemcpy()

| SDValue SelectionDAG::getAtomicMemcpy | ( | SDValue | Chain, |

| const SDLoc & | dl, | ||

| SDValue | Dst, | ||

| unsigned | DstAlign, | ||

| SDValue | Src, | ||

| unsigned | SrcAlign, | ||

| SDValue | Size, | ||

| Type * | SizeTy, | ||

| unsigned | ElemSz, | ||

| bool | isTailCall, | ||

| MachinePointerInfo | DstPtrInfo, | ||

| MachinePointerInfo | SrcPtrInfo | ||

| ) |

Definition at line 6120 of file SelectionDAG.cpp.

References llvm::AMDGPU::HSAMD::Kernel::Key::Args, getContext(), getDataLayout(), getExternalSymbol(), llvm::DataLayout::getIntPtrType(), llvm::TargetLoweringBase::getLibcallCallingConv(), llvm::TargetLoweringBase::getLibcallName(), llvm::RTLIB::getMEMCPY_ELEMENT_UNORDERED_ATOMIC(), llvm::TargetLoweringBase::getPointerTy(), llvm::Type::getVoidTy(), llvm::TargetLowering::LowerCallTo(), llvm::TargetLoweringBase::ArgListEntry::Node, llvm::report_fatal_error(), llvm::TargetLowering::CallLoweringInfo::setChain(), llvm::TargetLowering::CallLoweringInfo::setDebugLoc(), llvm::TargetLowering::CallLoweringInfo::setLibCallee(), llvm::TargetLowering::CallLoweringInfo::setTailCall(), Size, and llvm::TargetLoweringBase::ArgListEntry::Ty.

Referenced by getUnderlyingArgReg().

◆ getAtomicMemmove()

| SDValue SelectionDAG::getAtomicMemmove | ( | SDValue | Chain, |

| const SDLoc & | dl, | ||

| SDValue | Dst, | ||

| unsigned | DstAlign, | ||

| SDValue | Src, | ||

| unsigned | SrcAlign, | ||

| SDValue | Size, | ||

| Type * | SizeTy, | ||

| unsigned | ElemSz, | ||

| bool | isTailCall, | ||

| MachinePointerInfo | DstPtrInfo, | ||

| MachinePointerInfo | SrcPtrInfo | ||

| ) |

Definition at line 6222 of file SelectionDAG.cpp.