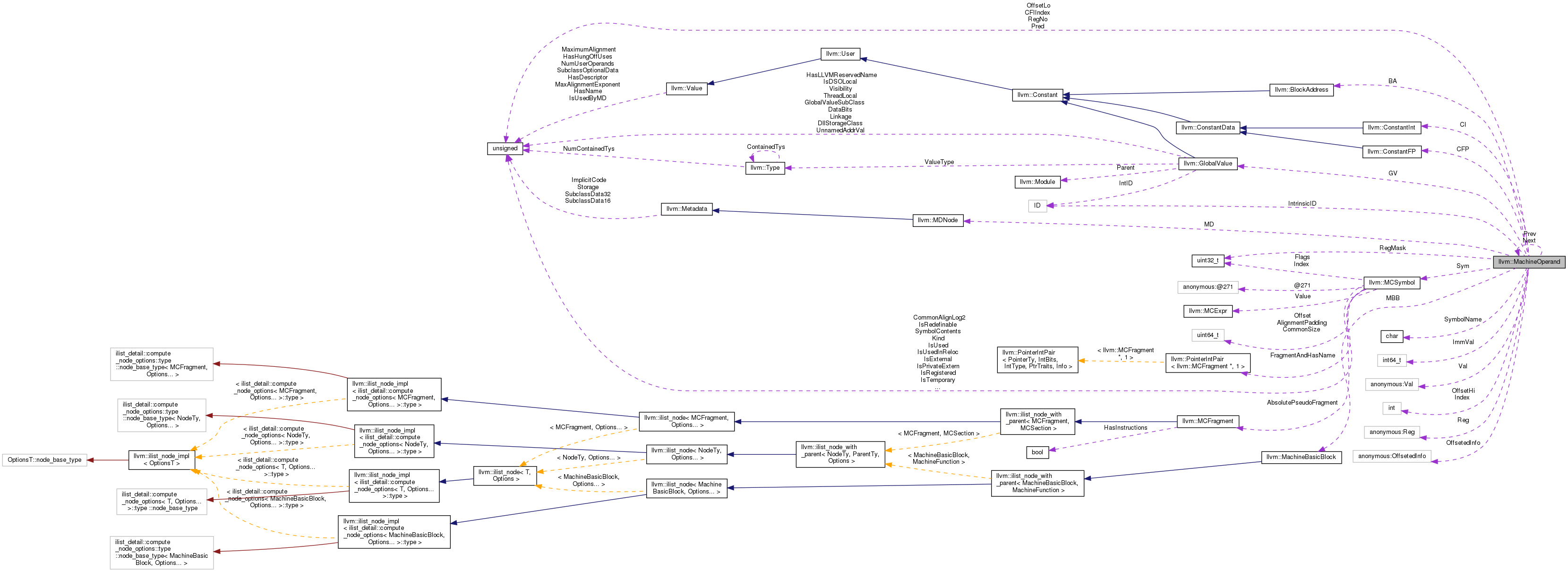

MachineOperand class - Representation of each machine instruction operand. More...

#include "llvm/CodeGen/MachineOperand.h"

Public Types | |

| enum | MachineOperandType : unsigned char { MO_Register, MO_Immediate, MO_CImmediate, MO_FPImmediate, MO_MachineBasicBlock, MO_FrameIndex, MO_ConstantPoolIndex, MO_TargetIndex, MO_JumpTableIndex, MO_ExternalSymbol, MO_GlobalAddress, MO_BlockAddress, MO_RegisterMask, MO_RegisterLiveOut, MO_Metadata, MO_MCSymbol, MO_CFIIndex, MO_IntrinsicID, MO_Predicate, MO_Last = MO_Predicate } |

Public Member Functions | |

| MachineOperandType | getType () const |

| getType - Returns the MachineOperandType for this operand. More... | |

| unsigned | getTargetFlags () const |

| void | setTargetFlags (unsigned F) |

| void | addTargetFlag (unsigned F) |

| MachineInstr * | getParent () |

| getParent - Return the instruction that this operand belongs to. More... | |

| const MachineInstr * | getParent () const |

| void | clearParent () |

| clearParent - Reset the parent pointer. More... | |

| void | print (raw_ostream &os, const TargetRegisterInfo *TRI=nullptr, const TargetIntrinsicInfo *IntrinsicInfo=nullptr) const |

Print the MachineOperand to os. More... | |

| void | print (raw_ostream &os, ModuleSlotTracker &MST, LLT TypeToPrint, bool PrintDef, bool IsStandalone, bool ShouldPrintRegisterTies, unsigned TiedOperandIdx, const TargetRegisterInfo *TRI, const TargetIntrinsicInfo *IntrinsicInfo) const |

| More complex way of printing a MachineOperand. More... | |

| void | print (raw_ostream &os, LLT TypeToPrint, const TargetRegisterInfo *TRI=nullptr, const TargetIntrinsicInfo *IntrinsicInfo=nullptr) const |

| Same as print(os, TRI, IntrinsicInfo), but allows to specify the low-level type to be printed the same way the full version of print(...) does it. More... | |

| void | dump () const |

| bool | isReg () const |

| isReg - Tests if this is a MO_Register operand. More... | |

| bool | isImm () const |

| isImm - Tests if this is a MO_Immediate operand. More... | |

| bool | isCImm () const |

| isCImm - Test if this is a MO_CImmediate operand. More... | |

| bool | isFPImm () const |

| isFPImm - Tests if this is a MO_FPImmediate operand. More... | |

| bool | isMBB () const |

| isMBB - Tests if this is a MO_MachineBasicBlock operand. More... | |

| bool | isFI () const |

| isFI - Tests if this is a MO_FrameIndex operand. More... | |

| bool | isCPI () const |

| isCPI - Tests if this is a MO_ConstantPoolIndex operand. More... | |

| bool | isTargetIndex () const |

| isTargetIndex - Tests if this is a MO_TargetIndex operand. More... | |

| bool | isJTI () const |

| isJTI - Tests if this is a MO_JumpTableIndex operand. More... | |

| bool | isGlobal () const |

| isGlobal - Tests if this is a MO_GlobalAddress operand. More... | |

| bool | isSymbol () const |

| isSymbol - Tests if this is a MO_ExternalSymbol operand. More... | |

| bool | isBlockAddress () const |

| isBlockAddress - Tests if this is a MO_BlockAddress operand. More... | |

| bool | isRegMask () const |

| isRegMask - Tests if this is a MO_RegisterMask operand. More... | |

| bool | isRegLiveOut () const |

| isRegLiveOut - Tests if this is a MO_RegisterLiveOut operand. More... | |

| bool | isMetadata () const |

| isMetadata - Tests if this is a MO_Metadata operand. More... | |

| bool | isMCSymbol () const |

| bool | isCFIIndex () const |

| bool | isIntrinsicID () const |

| bool | isPredicate () const |

| unsigned | getReg () const |

| getReg - Returns the register number. More... | |

| unsigned | getSubReg () const |

| bool | isUse () const |

| bool | isDef () const |

| bool | isImplicit () const |

| bool | isDead () const |

| bool | isKill () const |

| bool | isUndef () const |

| bool | isRenamable () const |

| isRenamable - Returns true if this register may be renamed, i.e. More... | |

| bool | isInternalRead () const |

| bool | isEarlyClobber () const |

| bool | isTied () const |

| bool | isDebug () const |

| bool | readsReg () const |

| readsReg - Returns true if this operand reads the previous value of its register. More... | |

| void | setReg (unsigned Reg) |

| Change the register this operand corresponds to. More... | |

| void | setSubReg (unsigned subReg) |

| void | substVirtReg (unsigned Reg, unsigned SubIdx, const TargetRegisterInfo &) |

| substVirtReg - Substitute the current register with the virtual subregister Reg:SubReg. More... | |

| void | substPhysReg (unsigned Reg, const TargetRegisterInfo &) |

| substPhysReg - Substitute the current register with the physical register Reg, taking any existing SubReg into account. More... | |

| void | setIsUse (bool Val=true) |

| void | setIsDef (bool Val=true) |

| Change a def to a use, or a use to a def. More... | |

| void | setImplicit (bool Val=true) |

| void | setIsKill (bool Val=true) |

| void | setIsDead (bool Val=true) |

| void | setIsUndef (bool Val=true) |

| void | setIsRenamable (bool Val=true) |

| void | setIsInternalRead (bool Val=true) |

| void | setIsEarlyClobber (bool Val=true) |

| void | setIsDebug (bool Val=true) |

| int64_t | getImm () const |

| const ConstantInt * | getCImm () const |

| const ConstantFP * | getFPImm () const |

| MachineBasicBlock * | getMBB () const |

| int | getIndex () const |

| const GlobalValue * | getGlobal () const |

| const BlockAddress * | getBlockAddress () const |

| MCSymbol * | getMCSymbol () const |

| unsigned | getCFIIndex () const |

| Intrinsic::ID | getIntrinsicID () const |

| unsigned | getPredicate () const |

| int64_t | getOffset () const |

| Return the offset from the symbol in this operand. More... | |

| const char * | getSymbolName () const |

| bool | clobbersPhysReg (unsigned PhysReg) const |

| clobbersPhysReg - Returns true if this RegMask operand clobbers PhysReg. More... | |

| const uint32_t * | getRegMask () const |

| getRegMask - Returns a bit mask of registers preserved by this RegMask operand. More... | |

| const uint32_t * | getRegLiveOut () const |

| getRegLiveOut - Returns a bit mask of live-out registers. More... | |

| const MDNode * | getMetadata () const |

| void | setImm (int64_t immVal) |

| void | setCImm (const ConstantInt *CI) |

| void | setFPImm (const ConstantFP *CFP) |

| void | setOffset (int64_t Offset) |

| void | setIndex (int Idx) |

| void | setMetadata (const MDNode *MD) |

| void | setMBB (MachineBasicBlock *MBB) |

| void | setRegMask (const uint32_t *RegMaskPtr) |

| Sets value of register mask operand referencing Mask. More... | |

| bool | isIdenticalTo (const MachineOperand &Other) const |

| Returns true if this operand is identical to the specified operand except for liveness related flags (isKill, isUndef and isDead). More... | |

| void | ChangeToImmediate (int64_t ImmVal) |

| ChangeToImmediate - Replace this operand with a new immediate operand of the specified value. More... | |

| void | ChangeToFPImmediate (const ConstantFP *FPImm) |

| ChangeToFPImmediate - Replace this operand with a new FP immediate operand of the specified value. More... | |

| void | ChangeToES (const char *SymName, unsigned char TargetFlags=0) |

| ChangeToES - Replace this operand with a new external symbol operand. More... | |

| void | ChangeToMCSymbol (MCSymbol *Sym) |

| ChangeToMCSymbol - Replace this operand with a new MC symbol operand. More... | |

| void | ChangeToFrameIndex (int Idx) |

| Replace this operand with a frame index. More... | |

| void | ChangeToTargetIndex (unsigned Idx, int64_t Offset, unsigned char TargetFlags=0) |

| Replace this operand with a target index. More... | |

| void | ChangeToRegister (unsigned Reg, bool isDef, bool isImp=false, bool isKill=false, bool isDead=false, bool isUndef=false, bool isDebug=false) |

| ChangeToRegister - Replace this operand with a new register operand of the specified value. More... | |

Friends | |

| class | MachineInstr |

| class | MachineRegisterInfo |

| struct | DenseMapInfo< MachineOperand > |

| hash_code | hash_value (const MachineOperand &MO) |

| MachineOperand hash_value overload. More... | |

Detailed Description

MachineOperand class - Representation of each machine instruction operand.

This class isn't a POD type because it has a private constructor, but its destructor must be trivial. Functions like MachineInstr::addOperand(), MachineRegisterInfo::moveOperands(), and MF::DeleteMachineInstr() depend on not having to call the MachineOperand destructor.

Definition at line 49 of file MachineOperand.h.

Member Enumeration Documentation

◆ MachineOperandType

| Enumerator | |

|---|---|

| MO_Register | Register operand. |

| MO_Immediate | Immediate operand. |

| MO_CImmediate | Immediate >64bit operand. |

| MO_FPImmediate | Floating-point immediate operand. |

| MO_MachineBasicBlock | MachineBasicBlock reference. |

| MO_FrameIndex | Abstract Stack Frame Index. |

| MO_ConstantPoolIndex | |

| MO_TargetIndex | Target-dependent index+offset operand. |

| MO_JumpTableIndex | Address of indexed Jump Table for switch. |

| MO_ExternalSymbol | Name of external global symbol. |

| MO_GlobalAddress | Address of a global value. |

| MO_BlockAddress | Address of a basic block. |

| MO_RegisterMask | Mask of preserved registers. |

| MO_RegisterLiveOut | Mask of live-out registers. |

| MO_Metadata | Metadata reference (for debug info) |

| MO_MCSymbol | MCSymbol reference (for debug/eh info) |

| MO_CFIIndex | MCCFIInstruction index. |

| MO_IntrinsicID | Intrinsic ID for ISel. |

| MO_Predicate | Generic predicate for ISel. |

| MO_Last | |

Definition at line 51 of file MachineOperand.h.

Member Function Documentation

◆ addTargetFlag()

|

inline |

Definition at line 223 of file MachineOperand.h.

References assert(), F(), and isReg().

Referenced by llvm::HexagonInstrInfo::immediateExtend(), and INITIALIZE_PASS().

◆ ChangeToES()

ChangeToES - Replace this operand with a new external symbol operand.

Definition at line 171 of file MachineOperand.cpp.

References assert(), isReg(), isTied(), MO_ExternalSymbol, setOffset(), and setTargetFlags().

Referenced by getRetpolineSymbol(), and setRegMask().

◆ ChangeToFPImmediate()

| void MachineOperand::ChangeToFPImmediate | ( | const ConstantFP * | FPImm | ) |

ChangeToFPImmediate - Replace this operand with a new FP immediate operand of the specified value.

If an operand is known to be an FP immediate already, the setFPImm method should be used.

Definition at line 162 of file MachineOperand.cpp.

References assert(), isReg(), isTied(), and MO_FPImmediate.

Referenced by setRegMask().

◆ ChangeToFrameIndex()

| void MachineOperand::ChangeToFrameIndex | ( | int | Idx | ) |

Replace this operand with a frame index.

Definition at line 194 of file MachineOperand.cpp.

References assert(), isReg(), isTied(), MO_FrameIndex, and setIndex().

Referenced by changeFCMPPredToAArch64CC(), setRegMask(), swapRegAndNonRegOperand(), llvm::updateDbgValueForSpill(), and updateOperand().

◆ ChangeToImmediate()

| void MachineOperand::ChangeToImmediate | ( | int64_t | ImmVal | ) |

ChangeToImmediate - Replace this operand with a new immediate operand of the specified value.

If an operand is known to be an immediate already, the setImm method should be used.

Definition at line 153 of file MachineOperand.cpp.

References assert(), ImmVal, isReg(), isTied(), and MO_Immediate.

Referenced by buildEXP(), changeFCMPPredToAArch64CC(), llvm::createX86OptimizeLEAs(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::ARCRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::X86RegisterInfo::eliminateFrameIndex(), llvm::SystemZInstrInfo::FoldImmediate(), llvm::SIInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::X86InstrInfo::foldMemoryOperandImpl(), getLeaOP(), getLoadStoreOffsetAlign(), hoistAndMergeSGPRInits(), llvm::Mips16RegisterInfo::intRegClass(), llvm::SIInstrInfo::legalizeOperandsVOP2(), replaceFI(), llvm::PPCInstrInfo::replaceInstrOperandWithImm(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::ThumbRegisterInfo::rewriteFrameIndex(), llvm::rewriteT2FrameIndex(), setRegMask(), shrinkScalarLogicOp(), swapRegAndNonRegOperand(), tryConstantFoldOp(), llvm::updateDbgValueForSpill(), and updateOperand().

◆ ChangeToMCSymbol()

| void MachineOperand::ChangeToMCSymbol | ( | MCSymbol * | Sym | ) |

ChangeToMCSymbol - Replace this operand with a new MC symbol operand.

Definition at line 184 of file MachineOperand.cpp.

References assert(), isReg(), isTied(), MO_MCSymbol, and Sym.

Referenced by setRegMask().

◆ ChangeToRegister()

| void MachineOperand::ChangeToRegister | ( | unsigned | Reg, |

| bool | isDef, | ||

| bool | isImp = false, |

||

| bool | isKill = false, |

||

| bool | isDead = false, |

||

| bool | isUndef = false, |

||

| bool | isDebug = false |

||

| ) |

ChangeToRegister - Replace this operand with a new register operand of the specified value.

If an operand is known to be an register already, the setReg method should be used.

Definition at line 220 of file MachineOperand.cpp.

References llvm::MachineRegisterInfo::addRegOperandToUseList(), assert(), getMFIfAvailable(), isDead(), isDebug(), isDef(), isReg(), isUndef(), MO_Register, Reg, and llvm::MachineRegisterInfo::removeRegOperandFromUseList().

Referenced by AssignProtectedObjSet(), llvm::createX86OptimizeLEAs(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::WebAssemblyRegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::ARCRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::X86RegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), findSingleRegDef(), getLoadStoreOffsetAlign(), llvm::Mips16RegisterInfo::intRegClass(), llvm::SIInstrInfo::legalizeOperandsVOP2(), llvm::SIInstrInfo::legalizeOpWithMove(), replaceFI(), llvm::SIRegisterInfo::resolveFrameIndex(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::ThumbRegisterInfo::rewriteFrameIndex(), llvm::rewriteT2FrameIndex(), setRegMask(), swapMIOperands(), swapRegAndNonRegOperand(), and llvm::X86InstrInfo::unfoldMemoryOperand().

◆ ChangeToTargetIndex()

| void MachineOperand::ChangeToTargetIndex | ( | unsigned | Idx, |

| int64_t | Offset, | ||

| unsigned char | TargetFlags = 0 |

||

| ) |

Replace this operand with a target index.

Definition at line 204 of file MachineOperand.cpp.

References assert(), isReg(), isTied(), MO_TargetIndex, setIndex(), setOffset(), and setTargetFlags().

Referenced by setRegMask().

◆ clearParent()

|

inline |

clearParent - Reset the parent pointer.

The MachineOperand copy constructor also copies ParentMI, expecting the original to be deleted. If a MachineOperand is ever stored outside a MachineInstr, the parent pointer must be cleared.

Never call clearParent() on an operand in a MachineInstr.

Definition at line 243 of file MachineOperand.h.

References dump(), llvm::ISD::FrameIndex, Index, Name, print(), printIRSlotNumber(), printOperandOffset(), printStackObjectReference(), printSubRegIdx(), printSymbol(), printTargetFlags(), Sym, and TRI.

◆ clobbersPhysReg() [1/2]

|

inlinestatic |

clobbersPhysReg - Returns true if this RegMask clobbers PhysReg.

It is sometimes necessary to detach the register mask pointer from its machine operand. This static method can be used for such detached bit mask pointers.

Definition at line 601 of file MachineOperand.h.

References assert().

Referenced by llvm::LiveRegUnits::addRegsInMask(), llvm::MachineOperandIteratorBase::analyzePhysReg(), canClobberPhysRegDefs(), canClobberReachingPhysRegUse(), CheckForLiveRegDefMasked(), clobbersAllYmmAndZmmRegs(), clobbersCTR(), clobbersPhysReg(), llvm::createRegUsageInfoCollector(), CriticalPathStep(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::X86RegisterInfo::getReservedRegs(), handleRegMaskClobber(), llvm::LiveVariables::HandleVirtRegDef(), isNopCopy(), llvm::X86InstrInfo::isSafeToClobberEFLAGS(), isVirtualRegisterOperand(), matchPair(), llvm::LanaiInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::TargetLowering::parametersInCSRMatch(), llvm::PhysicalRegisterUsageInfo::print(), llvm::LivePhysRegs::removeRegsInMask(), llvm::LiveRegUnits::removeRegsNotPreserved(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::LivePhysRegs::stepForward(), and false::Chain::str().

◆ clobbersPhysReg() [2/2]

clobbersPhysReg - Returns true if this RegMask operand clobbers PhysReg.

Definition at line 608 of file MachineOperand.h.

References clobbersPhysReg(), and getRegMask().

◆ CreateBA()

|

inlinestatic |

Definition at line 831 of file MachineOperand.h.

References BA, MO_BlockAddress, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addBlockAddress().

◆ CreateCFIIndex()

|

inlinestatic |

Definition at line 878 of file MachineOperand.h.

References CFIIndex, and MO_CFIIndex.

Referenced by llvm::MachineInstrBuilder::addCFIIndex().

◆ CreateCImm()

|

inlinestatic |

Definition at line 744 of file MachineOperand.h.

References CI, and MO_CImmediate.

Referenced by llvm::MachineInstrBuilder::addCImm(), and llvm::CSEMIRBuilder::buildConstant().

◆ CreateCPI()

|

inlinestatic |

Definition at line 793 of file MachineOperand.h.

References MO_ConstantPoolIndex, setIndex(), setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addConstantPoolIndex(), llvm::X86InstrInfo::foldMemoryOperandImpl(), and getUnconditionalBrDisp().

◆ CreateES()

|

inlinestatic |

Definition at line 823 of file MachineOperand.h.

References MO_ExternalSymbol, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addExternalSymbol(), llvm::createLibcall(), and getOffsetFromIndices().

◆ CreateFI()

|

inlinestatic |

Definition at line 788 of file MachineOperand.h.

References MO_FrameIndex, and setIndex().

Referenced by llvm::MachineInstrBuilder::addFrameIndex(), llvm::X86InstrInfo::foldMemoryOperandImpl(), llvm::X86AddressMode::getFullAddress(), getUnderlyingArgReg(), llvm::FastISel::selectGetElementPtr(), and llvm::LiveDebugVariables::splitRegister().

◆ CreateFPImm()

|

inlinestatic |

Definition at line 750 of file MachineOperand.h.

References CFP, and MO_FPImmediate.

Referenced by llvm::MachineInstrBuilder::addFPImm(), llvm::CSEMIRBuilder::buildFConstant(), and ConvertImplicitDefToConstZero().

◆ CreateGA()

|

inlinestatic |

Definition at line 815 of file MachineOperand.h.

References GV, MO_GlobalAddress, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addGlobalAddress(), llvm::X86AddressMode::getFullAddress(), llvm::CallLowering::lowerCall(), and llvm::FastISel::selectPatchpoint().

◆ CreateImm()

|

inlinestatic |

Definition at line 738 of file MachineOperand.h.

References MO_Immediate, and setImm().

Referenced by llvm::MachineInstrBuilder::addImm(), llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), llvm::WebAssemblyInstrInfo::analyzeBranch(), llvm::XCoreInstrInfo::analyzeBranch(), llvm::MSP430InstrInfo::analyzeBranch(), llvm::LanaiInstrInfo::analyzeBranch(), llvm::AVRInstrInfo::analyzeBranch(), llvm::HexagonInstrInfo::analyzeBranch(), llvm::SystemZInstrInfo::analyzeBranch(), llvm::PPCInstrInfo::analyzeBranch(), llvm::SIInstrInfo::analyzeBranchImpl(), llvm::X86InstrInfo::analyzeBranchPredicate(), AppendEndToFunction(), llvm::SIInstrInfo::buildExtractSubRegOrImm(), canMoveInstsAcrossMemOp(), llvm::X86InstrInfo::commuteInstructionImpl(), ConvertImplicitDefToConstZero(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86InstrInfo::foldMemoryOperandImpl(), getFallThroughMBB(), llvm::X86AddressMode::getFullAddress(), llvm::MipsInstrInfo::GetMemOperand(), getUnconditionalBrDisp(), isImplicitOperandIn(), IsPseudoCallIndirect(), isUseSafeToFold(), llvm::CallLowering::lowerCall(), llvm::SIInstrInfo::moveToVALU(), parseCondBranch(), llvm::predOps(), llvm::HexagonInstrInfo::reduceLoopCount(), llvm::WebAssemblyInstrInfo::reverseBranchCondition(), llvm::FastISel::selectGetElementPtr(), llvm::FastISel::selectPatchpoint(), llvm::FastISel::selectStackmap(), llvm::HexagonInstrInfo::setBundleNoShuf(), and toString().

◆ CreateIntrinsicID()

|

inlinestatic |

Definition at line 884 of file MachineOperand.h.

References IntrinsicID, and MO_IntrinsicID.

Referenced by llvm::MachineInstrBuilder::addIntrinsicID().

◆ CreateJTI()

|

inlinestatic |

Definition at line 809 of file MachineOperand.h.

References MO_JumpTableIndex, setIndex(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addJumpTableIndex().

◆ CreateMBB()

|

inlinestatic |

Definition at line 781 of file MachineOperand.h.

References MO_MachineBasicBlock, setMBB(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addMBB(), isImmValidForOpcode(), splitBlock(), and splitEdge().

◆ CreateMCSymbol()

|

inlinestatic |

Definition at line 869 of file MachineOperand.h.

References MO_MCSymbol, setOffset(), setTargetFlags(), and Sym.

Referenced by llvm::MachineInstrBuilder::addSym(), and EmitNops().

◆ CreateMetadata()

|

inlinestatic |

Definition at line 863 of file MachineOperand.h.

References MD, and MO_Metadata.

Referenced by llvm::MachineInstrBuilder::addMetadata().

◆ CreatePredicate()

|

inlinestatic |

Definition at line 890 of file MachineOperand.h.

References MO_Predicate, and Pred.

Referenced by llvm::MachineInstrBuilder::addPredicate().

◆ CreateReg()

|

inlinestatic |

Definition at line 756 of file MachineOperand.h.

References assert(), isDead(), isDebug(), isDef(), isEarlyClobber(), isInternalRead(), isKill(), isRenamable(), isUndef(), MO_Register, Reg, RegNo, setSubReg(), and SubReg.

Referenced by llvm::MachineInstr::addImplicitDefUseOperands(), llvm::GISelInstProfileBuilder::addNodeIDRegType(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), llvm::R600InstrInfo::analyzeBranch(), llvm::PPCInstrInfo::analyzeBranch(), llvm::SIInstrInfo::buildExtractSubRegOrImm(), canMoveInstsAcrossMemOp(), llvm::condCodeOp(), ConvertImplicitDefToConstZero(), llvm::X86InstrInfo::convertToThreeAddress(), createPHIsForSelects(), llvm::createSIFixWWMLivenessPass(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::HexagonFrameLowering::emitPrologue(), enableAllocFrameElim(), findNextInsertLocation(), fixupGlobalSaddr(), llvm::X86InstrInfo::foldMemoryOperandImpl(), llvm::HexagonFrameLowering::getAlignaInstr(), llvm::X86AddressMode::getFullAddress(), getUnderlyingArgReg(), llvm::LiveVariables::HandleVirtRegDef(), ImposeStackOrdering(), INITIALIZE_PASS(), isCopy(), isFunctionEntryBlock(), isImmValidForOpcode(), isImplicitOperandIn(), llvm::CallLowering::lowerCall(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::predOps(), printExtendedName(), removeExternalCFGEdges(), llvm::rewriteT2FrameIndex(), llvm::FastISel::selectGetElementPtr(), llvm::FastISel::selectIntrinsicCall(), llvm::FastISel::selectPatchpoint(), llvm::FastISel::selectStackmap(), llvm::FastISel::selectXRayCustomEvent(), llvm::FastISel::selectXRayTypedEvent(), llvm::t1CondCodeOp(), llvm::tryFoldSPUpdateIntoPushPop(), and llvm::LiveDebugVariables::~LiveDebugVariables().

◆ CreateRegLiveOut()

|

inlinestatic |

Definition at line 857 of file MachineOperand.h.

References assert(), llvm::BitmaskEnumDetail::Mask(), MO_RegisterLiveOut, and RegMask.

Referenced by INITIALIZE_PASS().

◆ CreateRegMask()

|

inlinestatic |

CreateRegMask - Creates a register mask operand referencing Mask.

The operand does not take ownership of the memory referenced by Mask, it must remain valid for the lifetime of the operand.

A RegMask operand represents a set of non-clobbered physical registers on an instruction that clobbers many registers, typically a call. The bit mask has a bit set for each physreg that is preserved by this instruction, as described in the documentation for TargetRegisterInfo::getCallPreservedMask().

Any physreg with a 0 bit in the mask is clobbered by the instruction.

Definition at line 851 of file MachineOperand.h.

References assert(), llvm::BitmaskEnumDetail::Mask(), MO_RegisterMask, and RegMask.

Referenced by llvm::MachineInstrBuilder::addRegMask(), and llvm::FastISel::selectPatchpoint().

◆ CreateTargetIndex()

|

inlinestatic |

Definition at line 801 of file MachineOperand.h.

References MO_TargetIndex, setIndex(), setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addTargetIndex().

◆ dump()

| LLVM_DUMP_METHOD void MachineOperand::dump | ( | ) | const |

Definition at line 930 of file MachineOperand.cpp.

References llvm::dbgs().

Referenced by clearParent(), doCandidateWalk(), GetVRegRenameMap(), rescheduleCanonically(), and runOnBasicBlock().

◆ getBlockAddress()

|

inline |

Definition at line 557 of file MachineOperand.h.

References assert(), and isBlockAddress().

Referenced by llvm::ARCMCInstLower::ARCMCInstLower(), changeFCMPPredToAArch64CC(), EmitHiLo(), llvm::LanaiMCInstLower::GetBlockAddressSymbol(), llvm::MSP430MCInstLower::GetBlockAddressSymbol(), llvm::SystemZMCInstLower::getExpr(), getRetOpcode(), llvm::hash_value(), llvm::HexagonLowerToMC(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), isIdenticalTo(), isSimilarDispOp(), llvm::AArch64MCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), LowerSymbolOperand(), print(), and llvm::MipsAsmPrinter::printOperand().

◆ getCFIIndex()

|

inline |

Definition at line 567 of file MachineOperand.h.

References assert(), and isCFIIndex().

Referenced by llvm::AsmPrinter::emitCFIInstruction(), getRegsUsedByPHIs(), llvm::hash_value(), INITIALIZE_PASS(), isIdenticalTo(), and print().

◆ getCImm()

|

inline |

Definition at line 531 of file MachineOperand.h.

References assert(), and isCImm().

Referenced by llvm::GISelInstProfileBuilder::addNodeIDMachineOperand(), buildEXP(), changeFCMPPredToAArch64CC(), emitDebugValueComment(), llvm::InstructionSelector::executeMatchTable(), getConstant(), llvm::getConstantVRegVal(), getDebugLocValue(), getLeaOP(), llvm::hash_value(), isConstant(), isIdenticalTo(), llvm::LegalizerHelper::narrowScalar(), print(), and llvm::LegalizerHelper::widenScalar().

◆ getFPImm()

|

inline |

Definition at line 536 of file MachineOperand.h.

References assert(), and isFPImm().

Referenced by llvm::DwarfUnit::addConstantFPValue(), llvm::GISelInstProfileBuilder::addNodeIDMachineOperand(), buildEXP(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), ConvertDoubleToBytes(), emitDebugValueComment(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::getConstantFPVRegVal(), getDebugLocValue(), llvm::hash_value(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::WebAssemblyMCInstLower::Lower(), llvm::ARMAsmPrinter::lowerOperand(), print(), VisitGlobalVariableForEmission(), and llvm::LegalizerHelper::widenScalar().

◆ getGlobal()

|

inline |

Definition at line 552 of file MachineOperand.h.

References assert(), and isGlobal().

Referenced by llvm::MachineInstrBuilder::addDisp(), addExclusiveRegPair(), llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::ARCMCInstLower::ARCMCInstLower(), llvm::EHStreamer::callToNoUnwindFunction(), changeFCMPPredToAArch64CC(), ConvertDoubleToBytes(), createPHIsForCMOVsInSinkBB(), llvm::PPCFrameLowering::emitEpilogue(), EmitHiLo(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), eraseDeadBBsAndChildren(), llvm::getAddressFromInstr(), llvm::SystemZMCInstLower::getExpr(), llvm::MSP430MCInstLower::GetGlobalAddressSymbol(), llvm::BPFMCInstLower::GetGlobalAddressSymbol(), llvm::LanaiMCInstLower::GetGlobalAddressSymbol(), llvm::AArch64MCInstLower::GetGlobalAddressSymbol(), getLeaOP(), GetSymbolFromOperand(), getVariantKind(), hasAnyNonFlatUseOfReg(), llvm::hash_value(), llvm::HexagonLowerToMC(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), INITIALIZE_PASS(), llvm::WebAssembly::isCatchAllTerminatePad(), llvm::WebAssembly::isCatchTerminatePad(), isIdenticalTo(), llvm::PPCInstrInfo::isSignOrZeroExtended(), isSimilarDispOp(), llvm::WebAssemblyMCInstLower::Lower(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), LowerSymbolOperand(), llvm::AVRMCInstLower::lowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), makeImplicit(), llvm::WebAssembly::mayThrow(), llvm::rdf::operator<<(), print(), llvm::WebAssemblyAsmPrinter::PrintAsmOperand(), llvm::AVRAsmPrinter::printOperand(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), llvm::ARMBaseInstrInfo::produceSameValue(), QueryCallee(), llvm::DetectRoundChange::runOnMachineFunction(), llvm::DwarfDebug::shareAcrossDWOCUs(), swapMIOperands(), trySequenceOfOnes(), and VisitGlobalVariableForEmission().

◆ getImm()

|

inline |

Definition at line 526 of file MachineOperand.h.

References assert(), and isImm().

Referenced by llvm::DwarfUnit::addConstantValue(), llvm::MachineInstrBuilder::addDisp(), addExclusiveRegPair(), llvm::R600InstrInfo::addFlag(), llvm::GISelInstProfileBuilder::addNodeIDMachineOperand(), adjustDefLatency(), llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), llvm::LanaiInstrInfo::analyzeCompare(), llvm::AArch64InstrInfo::analyzeCompare(), llvm::SystemZInstrInfo::analyzeCompare(), llvm::HexagonInstrInfo::analyzeCompare(), llvm::ARMBaseInstrInfo::analyzeCompare(), llvm::PPCInstrInfo::analyzeCompare(), llvm::X86InstrInfo::analyzeCompare(), llvm::SwingSchedulerDAG::applyInstrChange(), areCandidatesToMergeOrPair(), llvm::HexagonInstrInfo::areMemAccessesTriviallyDisjoint(), AssignProtectedObjSet(), buildEXP(), llvm::SIInstrInfo::buildExtractSubRegOrImm(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), canBeExpandedToORR(), canCompareBeNewValueJump(), canFoldIntoCSel(), llvm::X86InstrInfo::canMakeTailCallConditional(), canMoveInstsAcrossMemOp(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), llvm::X86InstrInfo::classifyLEAReg(), llvm::R600InstrInfo::clearFlag(), llvm::PPCInstrInfo::commuteInstructionImpl(), llvm::X86InstrInfo::commuteInstructionImpl(), compareMachineOp(), CompareMBBNumbers(), computeExprForSpill(), ConvertDoubleToBytes(), llvm::PPCInstrInfo::convertToImmediateForm(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::SystemZInstrInfo::convertToThreeAddress(), llvm::SIInstrInfo::convertToThreeAddress(), createPHIsForCMOVsInSinkBB(), createPHIsForSelects(), llvm::createR600ExpandSpecialInstrsPass(), llvm::createSIAddIMGInitPass(), llvm::createSIModeRegisterPass(), llvm::createSparcDelaySlotFillerPass(), llvm::createX86OptimizeLEAs(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::HexagonFrameLowering::determineCalleeSaves(), llvm::SparcFrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::ARCFrameLowering::eliminateCallFramePseudoInstr(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::WebAssemblyRegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::ARCRegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::X86RegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), emitClzero(), emitDebugValueComment(), llvm::AArch64FrameLowering::emitEpilogue(), llvm::PPCFrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::AsmPrinter::emitFrameAlloc(), EmitGCCInlineAsmStr(), EmitHiLo(), emitIndirectDst(), emitIndirectSrc(), llvm::SystemZAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::MipsAsmPrinter::EmitInstruction(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::BPFTargetLowering::EmitInstrWithCustomInserter(), llvm::RISCVTargetLowering::EmitInstrWithCustomInserter(), llvm::AVRTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::ARMAsmPrinter::EmitJumpTableTBInst(), EmitMSInlineAsmStr(), EmitNop(), EmitNops(), emitPostSt(), llvm::HexagonEvaluator::evaluate(), llvm::BitTracker::MachineEvaluator::evaluate(), ExpandMOVImmSExti8(), llvm::R600InstrInfo::expandPostRAPseudo(), llvm::HexagonInstrInfo::expandPostRAPseudo(), llvm::SIInstrInfo::expandPostRAPseudo(), llvm::SystemZInstrInfo::expandPostRAPseudo(), llvm::SparcTargetLowering::expandSelectCC(), llvm::X86InstrInfo::findCommutedOpIndices(), findCondCodeUsedByInstr(), llvm::MachineInstr::findInlineAsmFlagIdx(), findSingleRegDef(), findStartOfTree(), llvm::MachineInstr::findTiedOperandIdx(), findUncondBrI(), llvm::SwingSchedulerDAG::fixupRegisterOverlaps(), fixupSEHOpcode(), llvm::foldFrameOffset(), llvm::SystemZInstrInfo::FoldImmediate(), llvm::SIInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::PPCInstrInfo::FoldImmediate(), foldImmediates(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), followSubRegDef(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), genFusedMultiply(), llvm::getAddressFromInstr(), getADDriFromLEA(), getAdjustedCmp(), llvm::HexagonInstrInfo::getBaseAndOffset(), llvm::SystemZInstrInfo::getBranchInfo(), getCmpForPseudo(), getComparePred(), getCompareSourceReg(), llvm::HexagonInstrInfo::getCompoundCandidateGroup(), llvm::HexagonInstrInfo::getCompoundOpcode(), llvm::getConstantVRegVal(), getDebugLocValue(), getDPPOp(), llvm::HexagonInstrInfo::getDuplexCandidateGroup(), getDwarfRegNum(), llvm::X86InstrInfo::getExecutionDomainCustom(), llvm::TargetInstrInfo::getExtractSubregInputs(), llvm::X86InstrInfo::getFrameAdjustment(), llvm::ARMBaseRegisterInfo::getFrameIndexInstrOffset(), llvm::MSP430InstrInfo::getFramePoppedByCallee(), llvm::TargetInstrInfo::getFrameSize(), llvm::TargetInstrInfo::getFrameTotalSize(), llvm::SystemZInstrInfo::getFusedCompare(), getHWReg(), llvm::StackMapOpers::getID(), GetImm(), llvm::HexagonInstrInfo::getIncrementValue(), llvm::MachineInstr::getInlineAsmDialect(), llvm::TargetInstrInfo::getInsertSubregInputs(), llvm::ARMBaseInstrInfo::getInsertSubregLikeInputs(), llvm::getInstrPredicate(), llvm::AArch64InstrInfo::getInstSizeInBytes(), llvm::MipsInstrInfo::getInstSizeInBytes(), llvm::ARMBaseInstrInfo::getInstSizeInBytes(), getLeaOP(), getLoadStoreOffsetAlign(), getLoadStoreOffsetSizeInBits(), getLSMultipleTransferSize(), getMappedOp(), llvm::SIInstrInfo::getMemOperandWithOffset(), llvm::X86InstrInfo::getMemOperandWithOffset(), llvm::LanaiInstrInfo::getMemOperandWithOffsetWidth(), llvm::AArch64InstrInfo::getMemOperandWithOffsetWidth(), getMemoryOpOffset(), llvm::SIRegisterInfo::getMUBUFInstrOffset(), llvm::SIInstrInfo::getNamedImmOperand(), getNewValueJumpOpcode(), llvm::PatchPointOpers::getNumCallArgs(), getNumMicroOpsSwiftLdSt(), llvm::StackMapOpers::getNumPatchBytes(), llvm::SIInstrInfo::getNumWaitStates(), getOModValue(), getPostIndexedLoadStoreOpcode(), llvm::ARMBaseInstrInfo::getPredicate(), getReassignedChan(), llvm::MachineInstr::getRegClassConstraint(), llvm::TargetInstrInfo::getRegSequenceInputs(), llvm::getRegSequenceSubReg(), getRetOpcode(), llvm::X86InstrInfo::getSPAdjust(), getSrcFromCopy(), llvm::R600InstrInfo::getSrcs(), getStoreOffset(), getTruncatedShiftCount(), getUnconditionalBrDisp(), getVariantKind(), llvm::NVPTXAsmPrinter::getVirtualRegisterName(), getWinAllocaAmount(), llvm::hash_value(), HashMachineInstr(), hasLEAOffset(), llvm::SIInstrInfo::hasModifiersSet(), llvm::MachineInstr::hasUnmodeledSideEffects(), llvm::HexagonLowerToMC(), hoistAndMergeSGPRInits(), INITIALIZE_PASS(), insertUndefLaneMask(), llvm::Mips16RegisterInfo::intRegClass(), llvm::isAArch64FrameOffsetLegal(), llvm::ARMBaseInstrInfo::isAddrMode3OpMinusReg(), llvm::ARMBaseInstrInfo::isAm2ScaledReg(), llvm::AArch64InstrInfo::isAsCheapAsAMove(), llvm::AArch64InstrInfo::isCoalescableExtInstr(), isCompareZero(), llvm::HexagonInstrInfo::isConstExtended(), llvm::MachineInstr::isConvergent(), llvm::MipsSEInstrInfo::isCopyInstrImpl(), isCrossCopy(), llvm::AArch64InstrInfo::isFalkorShiftExtFast(), isFpMulInstruction(), llvm::PPCRegisterInfo::isFrameOffsetLegal(), llvm::AArch64InstrInfo::isGPRCopy(), llvm::AArch64InstrInfo::isGPRZero(), isGreaterThanNBitTFRI(), isIdenticalTo(), isImmValidForOpcode(), isImplicitlyDef(), isIncrementOrDecrement(), llvm::SIInstrInfo::isInlineConstant(), isKImmOperand(), isKImmOrKUImmOperand(), isKUImmOperand(), isLdOffsetInRangeOfSt(), llvm::ARMBaseInstrInfo::isLdstScaledReg(), llvm::ARMBaseInstrInfo::isLdstScaledRegNotPlusLsl2(), llvm::ARMBaseInstrInfo::isLdstSoMinusReg(), isLEASimpleIncOrDec(), llvm::RISCVInstrInfo::isLoadFromStackSlot(), llvm::LanaiInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::AVRInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), isMergeableLdStUpdate(), llvm::R600InstrInfo::isPredicable(), llvm::ARMBaseInstrInfo::isPredicated(), isRedundantFlagInstr(), isRelevantAddressingMode(), isReverseInlineImm(), isSafeToFoldImmIntoCopy(), llvm::isScale(), llvm::AArch64InstrInfo::isSchedulingBoundary(), isSendMsgTraceDataOrGDS(), isSignExtendingOp(), isSimpleBD12Move(), isSimpleIf(), isSimpleMove(), llvm::MachineInstr::isStackAligningInlineAsm(), llvm::SystemZInstrInfo::isStackSlotCopy(), llvm::RISCVInstrInfo::isStoreToStackSlot(), llvm::LanaiInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AVRInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), isSuitableForMask(), llvm::ARMBaseInstrInfo::isSwiftFastImmShift(), llvm::PPCInstrInfo::isTOCSaveMI(), isUseSafeToFold(), isZeroExtendingOp(), isZeroImm(), llvm::MipsInstrInfo::isZeroImm(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::SIInstrInfo::legalizeOperandsVOP2(), llvm::MSP430MCInstLower::Lower(), llvm::BPFMCInstLower::Lower(), llvm::LanaiMCInstLower::Lower(), llvm::WebAssemblyMCInstLower::Lower(), llvm::XCoreMCInstLower::LowerOperand(), llvm::ARCMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), llvm::MipsMCInstLower::LowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), lowerRIEfLow(), lowerRIHigh(), lowerRILow(), llvm::LowerRISCVMachineOperandToMCOperand(), lowerSubvectorLoad(), lowerSubvectorStore(), makeImplicit(), matchPair(), matchSwap(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), Mips16WhichOp8uOr16simm(), llvm::SIInstrInfo::moveToVALU(), llvm::LegalizerHelper::narrowScalar(), llvm::PPCRegisterInfo::needsFrameBaseReg(), llvm::LanaiInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCondBranch(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), optimizeVcndVcmpPair(), parseCond(), parseCondBranch(), performCustomAdjustments(), llvm::MIPrinter::print(), print(), llvm::MachineInstr::print(), llvm::SystemZAsmPrinter::PrintAsmMemoryOperand(), llvm::AVRAsmPrinter::PrintAsmMemoryOperand(), llvm::HexagonAsmPrinter::PrintAsmMemoryOperand(), llvm::MipsAsmPrinter::PrintAsmMemoryOperand(), llvm::SystemZAsmPrinter::PrintAsmOperand(), llvm::AVRAsmPrinter::PrintAsmOperand(), llvm::WebAssemblyAsmPrinter::PrintAsmOperand(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::X86AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), llvm::AsmPrinter::PrintAsmOperand(), printConstant(), printExtendedName(), llvm::MipsAsmPrinter::printFCCOperand(), printIntelMemReference(), printLeaMemReference(), llvm::AVRAsmPrinter::printOperand(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printOperand(), printPCRelImm(), profitImm(), readsVCCZ(), llvm::StackMaps::recordStackMap(), llvm::HexagonInstrInfo::reduceLoopCount(), registerDefinedBetween(), removePhis(), removeRedundantBlockingStores(), llvm::SIRegisterInfo::resolveFrameIndex(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::WebAssemblyInstrInfo::reverseBranchCondition(), llvm::R600InstrInfo::reverseBranchCondition(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::ThumbRegisterInfo::rewriteFrameIndex(), RewriteP2Align(), llvm::rewriteT2FrameIndex(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::X86InstrInfo::setExecutionDomainCustom(), llvm::AArch64InstrInfo::shouldClusterMemOps(), shrinkScalarLogicOp(), swapMIOperands(), swapRegAndNonRegOperand(), llvm::SIInstrInfo::swapSourceModifiers(), llvm::SystemZInstrInfo::SystemZInstrInfo(), tieOpsIfNeeded(), tryConstantFoldOp(), tryOptimizeLEAtoMOV(), trySequenceOfOnes(), llvm::X86InstrInfo::unfoldMemoryOperand(), updateKillStatus(), updateOperand(), llvm::HexagonPacketizerList::useCalleesSP(), llvm::HexagonPacketizerList::useCallersSP(), verifyInsExtInstruction(), llvm::SIInstrInfo::verifyInstruction(), VerifyLowRegs(), and VisitGlobalVariableForEmission().

◆ getIndex()

|

inline |

Definition at line 546 of file MachineOperand.h.

References assert(), isCPI(), isFI(), isJTI(), and isTargetIndex().

Referenced by llvm::MachineInstrBuilder::addDisp(), llvm::ARCMCInstLower::ARCMCInstLower(), llvm::HexagonFrameLowering::assignCalleeSavedSpillSlots(), AssignProtectedObjSet(), BBHasFallthrough(), BBIsJumpedOver(), llvm::HexagonFrameLowering::determineCalleeSaves(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::WebAssemblyRegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::ARCRegisterInfo::eliminateFrameIndex(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::MipsRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::X86RegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), emitDebugValueComment(), EmitHiLo(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::MipsAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitJumpTableAddrs(), llvm::ARMAsmPrinter::EmitJumpTableInsts(), llvm::ARMAsmPrinter::EmitJumpTableTBInst(), llvm::TargetLoweringBase::emitPatchPoint(), foldImmediates(), llvm::getAddressFromInstr(), getConstantFromPool(), llvm::MSP430MCInstLower::GetConstantPoolIndexSymbol(), llvm::LanaiMCInstLower::GetConstantPoolIndexSymbol(), llvm::SystemZMCInstLower::getExpr(), llvm::MSP430MCInstLower::GetJumpTableSymbol(), llvm::LanaiMCInstLower::GetJumpTableSymbol(), getRetOpcode(), llvm::X86InstrInfo::getSPAdjust(), getStartOrEndSlot(), getUnconditionalBrDisp(), llvm::hash_value(), HashMachineInstr(), hasSameBaseOpValue(), llvm::HexagonLowerToMC(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), INITIALIZE_PASS(), isIdenticalTo(), llvm::RISCVInstrInfo::isLoadFromStackSlot(), llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::ARCInstrInfo::isLoadFromStackSlot(), llvm::XCoreInstrInfo::isLoadFromStackSlot(), llvm::LanaiInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::AVRInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), llvm::SIInstrInfo::isSGPRStackAccess(), isSimilarDispOp(), isSimpleMove(), llvm::SIInstrInfo::isStackAccess(), llvm::SystemZInstrInfo::isStackSlotCopy(), llvm::RISCVInstrInfo::isStoreToStackSlot(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), llvm::LanaiInstrInfo::isStoreToStackSlot(), llvm::ARCInstrInfo::isStoreToStackSlot(), llvm::XCoreInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AVRInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), lookupCandidateBaseReg(), llvm::AArch64MCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), LowerSymbolOperand(), MatchingStackOffset(), matchPair(), false::IntervalSorter::operator()(), llvm::MIPrinter::print(), print(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), llvm::ARMBaseInstrInfo::produceSameValue(), llvm::ARMBaseInstrInfo::reMaterialize(), llvm::ScheduleDAGMILive::scheduleMI(), llvm::AArch64InstrInfo::shouldClusterMemOps(), swapRegAndNonRegOperand(), trySequenceOfOnes(), and X86SelectAddress().

◆ getIntrinsicID()

|

inline |

Definition at line 572 of file MachineOperand.h.

References assert(), and isIntrinsicID().

Referenced by buildEXP(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), llvm::InstructionSelector::executeMatchTable(), getConstant(), llvm::AMDGPURegisterBankInfo::getInstrMapping(), llvm::hash_value(), isIdenticalTo(), and print().

◆ getMBB()

|

inline |

Definition at line 541 of file MachineOperand.h.

References assert(), and isMBB().

Referenced by addIncomingValuesToPHIs(), allPhiOperandsUndefined(), llvm::XCoreInstrInfo::analyzeBranch(), llvm::NVPTXInstrInfo::analyzeBranch(), llvm::SparcInstrInfo::analyzeBranch(), llvm::MipsInstrInfo::analyzeBranch(), llvm::HexagonInstrInfo::analyzeBranch(), llvm::AArch64InstrInfo::analyzeBranch(), llvm::R600InstrInfo::analyzeBranch(), llvm::SystemZInstrInfo::analyzeBranch(), llvm::PPCInstrInfo::analyzeBranch(), AppendEndToFunction(), llvm::ARCMCInstLower::ARCMCInstLower(), BBIsJumpedOver(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), ConvertDoubleToBytes(), llvm::LiveRangeCalc::createDeadDefs(), llvm::createHexagonHardwareLoops(), createPHIsForCMOVsInSinkBB(), EmitGCCInlineAsmStr(), EmitHiLo(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), EmitNops(), llvm::SystemZPostRASchedStrategy::enterMBB(), eraseDeadBBsAndChildren(), llvm::HexagonEvaluator::evaluate(), llvm::BitTracker::MachineEvaluator::evaluate(), llvm::AArch64InstrInfo::expandPostRAPseudo(), findCorrespondingPred(), fixPHIsInSucc(), llvm::RISCVInstrInfo::getBranchDestBlock(), llvm::AVRInstrInfo::getBranchDestBlock(), llvm::AArch64InstrInfo::getBranchDestBlock(), llvm::SIInstrInfo::getBranchDestBlock(), getCmpForPseudo(), llvm::HexagonInstrInfo::getDotNewPredJumpOp(), llvm::SystemZMCInstLower::getExpr(), llvm::SSAUpdaterTraits< MachineSSAUpdater >::PHI_iterator::getIncomingBlock(), getInitPhiReg(), getLoopPhiReg(), llvm::MipsInstrInfo::GetMemOperand(), getNewValueJumpOpcode(), getPHIDeps(), getPHIPred(), getPhiRegs(), getPHISrcRegOpIdx(), getRegsUsedByPHIs(), getTargetMBB(), getUnconditionalBrDisp(), getVariantKind(), llvm::hash_value(), HashMachineInstr(), hasVulnerableLoad(), llvm::HexagonLowerToMC(), hoistAndMergeSGPRInits(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), INITIALIZE_PASS(), insertPHI(), isIdenticalTo(), isImmValidForOpcode(), isIntersect(), isSimilarDispOp(), IsUnconditionalJump(), llvm::SIInstrInfo::legalizeOperands(), llvm::MSP430MCInstLower::Lower(), llvm::BPFMCInstLower::Lower(), llvm::LanaiMCInstLower::Lower(), llvm::AArch64MCInstLower::lowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), LowerSymbolOperand(), matchPair(), llvm::rdf::operator<<(), llvm::AArch64InstrInfo::optimizeCondBranch(), parseCondBranch(), llvm::PPCInstrInfo::PredicateInstruction(), print(), llvm::WebAssemblyAsmPrinter::PrintAsmOperand(), llvm::AVRAsmPrinter::printOperand(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), llvm::HexagonInstrInfo::reduceLoopCount(), removePhis(), llvm::RegBankSelect::RepairingPlacement::RepairingPlacement(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), splitBlock(), splitEdge(), splitMBB(), llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs(), llvm::CombinerHelper::tryCombineCopy(), updatePHIs(), VisitGlobalVariableForEmission(), and llvm::LegalizerHelper::widenScalar().

◆ getMCSymbol()

|

inline |

Definition at line 562 of file MachineOperand.h.

References assert(), and isMCSymbol().

Referenced by emitDirectiveRelocJalr(), llvm::AsmPrinter::emitFrameAlloc(), llvm::MipsInstrInfo::genInstrWithNewOpc(), getRetOpcode(), getRetpolineSymbol(), llvm::hash_value(), llvm::MipsMCInstLower::Initialize(), isIdenticalTo(), isSimilarDispOp(), llvm::WebAssemblyMCInstLower::Lower(), llvm::AArch64MCInstLower::lowerOperand(), and print().

◆ getMetadata()

Definition at line 630 of file MachineOperand.h.

References assert(), and isMetadata().

Referenced by EmitGCCInlineAsmStr(), EmitHiLo(), llvm::MachineInstr::getDebugExpression(), llvm::MachineInstr::getDebugLabel(), llvm::MachineInstr::getDebugVariable(), llvm::hash_value(), isIdenticalTo(), print(), and llvm::MachineInstr::print().

◆ getOffset()

|

inline |

Return the offset from the symbol in this operand.

This always returns 0 for ExternalSymbol operands.

Definition at line 584 of file MachineOperand.h.

References assert(), isBlockAddress(), isCPI(), isGlobal(), isMCSymbol(), isSymbol(), and isTargetIndex().

Referenced by llvm::MachineInstrBuilder::addDisp(), addExclusiveRegPair(), llvm::ARCMCInstLower::ARCMCInstLower(), changeFCMPPredToAArch64CC(), llvm::createX86OptimizeLEAs(), llvm::X86RegisterInfo::eliminateFrameIndex(), llvm::PPCFrameLowering::emitEpilogue(), getConstantFromPool(), llvm::HexagonInstrInfo::getDuplexCandidateGroup(), llvm::SystemZMCInstLower::getExpr(), GetSymbolRef(), getVariantKind(), llvm::hash_value(), HashMachineInstr(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), isIdenticalTo(), llvm::WebAssemblyMCInstLower::Lower(), lowerSymbolOperand(), llvm::AVRMCInstLower::lowerSymbolOperand(), llvm::MSP430MCInstLower::LowerSymbolOperand(), llvm::BPFMCInstLower::LowerSymbolOperand(), llvm::LanaiMCInstLower::LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandCOFF(), llvm::AArch64MCInstLower::lowerSymbolOperandDarwin(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), makeImplicit(), print(), llvm::WebAssemblyAsmPrinter::PrintAsmOperand(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), llvm::ARMBaseInstrInfo::produceSameValue(), and trySequenceOfOnes().

◆ getParent() [1/2]

|

inline |

getParent - Return the instruction that this operand belongs to.

Definition at line 232 of file MachineOperand.h.

Referenced by addSegmentsWithValNo(), llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), llvm::MachineOperandIteratorBase::analyzeVirtReg(), changeFCMPPredToAArch64CC(), createBBSelectReg(), createDeadDef(), llvm::createSIFixWWMLivenessPass(), llvm::createX86OptimizeLEAs(), CriticalPathStep(), llvm::LiveRangeEdit::eraseVirtReg(), llvm::SMSchedule::finalizeSchedule(), findSingleRegDef(), findSingleRegUse(), llvm::Localizer::getAnalysisUsage(), llvm::RegBankSelect::getAnalysisUsage(), getFoldableImm(), getLoadStoreOffsetSizeInBits(), getMFIfAvailable(), llvm::MachineRegisterInfo::defusechain_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::getOperandNo(), GetSymbolRef(), getUsedRegMask(), getVariantKind(), INITIALIZE_PASS(), isConstant(), isCrossCopy(), llvm::SIInstrInfo::isInlineConstant(), isKilled(), isKImmOperand(), isKUImmOperand(), isNoReturnDef(), isRenamable(), isUseSafeToFold(), isVirtualRegisterOperand(), matchPair(), MoveForSingleUse(), OneUseDominatesOtherUses(), llvm::MachineRegisterInfo::defusechain_instr_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator*(), llvm::MachineRegisterInfo::defusechain_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator++(), llvm::MachineRegisterInfo::defusechain_instr_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator++(), llvm::MIPrinter::print(), RematerializeCheapDef(), removeExternalCFGEdges(), removePhis(), ReplaceDominatedUses(), llvm::CombinerHelper::replaceRegOpWith(), replaceRegUsesAfterLoop(), llvm::MachineSSAUpdater::RewriteUse(), llvm::Localizer::runOnMachineFunction(), scavengeVReg(), llvm::ScheduleDAGMILive::scheduleMI(), llvm::AArch64InstrInfo::shouldClusterMemOps(), llvm::SIInstrInfo::shouldClusterMemOps(), false::Chain::str(), llvm::TailDuplicator::tailDuplicateAndUpdate(), llvm::CombinerHelper::tryCombineCopy(), llvm::CombinerHelper::tryCombineExtendingLoads(), tryFoldInst(), llvm::FastISel::tryToFoldLoad(), updateKillStatus(), UpdatePredRedefs(), llvm::MachineTraceMetrics::Ensemble::verify(), llvm::MachineFunction::verify(), and llvm::MachineRegisterInfo::verifyUseList().

◆ getParent() [2/2]

|

inline |

Definition at line 233 of file MachineOperand.h.

◆ getPredicate()

|

inline |

Definition at line 577 of file MachineOperand.h.

References assert(), and isPredicate().

Referenced by llvm::GISelInstProfileBuilder::addNodeIDMachineOperand(), canTurnIntoCOPY(), changeFCMPPredToAArch64CC(), llvm::hash_value(), isIdenticalTo(), llvm::ARMLegalizerInfo::legalizeCustom(), print(), and llvm::LegalizerHelper::widenScalar().

◆ getReg()

|

inline |

getReg - Returns the register number.

Definition at line 349 of file MachineOperand.h.

References assert(), and isReg().