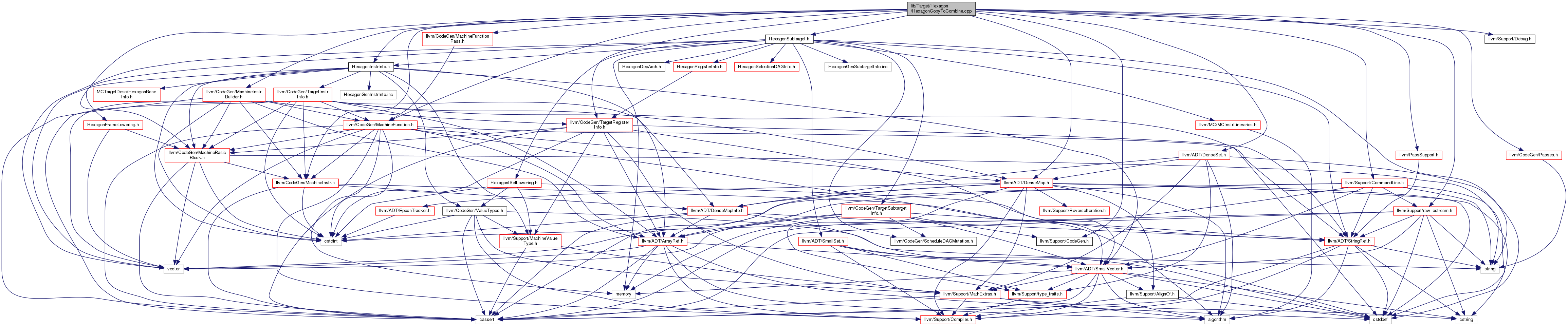

Definition at line 128 of file HexagonCopyToCombine.cpp.

Referenced by addEpilogOnlyR10(), addExclusiveRegPair(), llvm::MachineBasicBlock::addLiveIn(), llvm::ARMFrameLowering::adjustForSegmentedStacks(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), allPhiOperandsUndefined(), llvm::analyzeArguments(), AppendEndToFunction(), areCandidatesToMergeOrPair(), AssignProtectedObjSet(), BBHasFallthrough(), BBIsJumpedOver(), bitOpWithConstantIsReducible(), BlockData::BlockData(), branchMaxOffsets(), buildMUBUFOffsetLoadStore(), buildVector(), CalcNodeSethiUllmanNumber(), callHasRegMask(), canClobberPhysRegDefs(), canEnableCoalescing(), canMoveInstsAcrossMemOp(), llvm::LiveRangeEdit::canRematerializeAt(), llvm::MachineBasicBlock::canSplitCriticalEdge(), canTurnIntoCOPY(), CC_MipsO32_FP64(), changeFCMPPredToAArch64CC(), llvm::LiveRangeEdit::checkRematerializable(), CombineCVTAToLocal(), combineRestoreSETHIi(), CompareMBBNumbers(), llvm::computeBlockSize(), computeBranchTargetAndInversion(), computeBytesPoppedByCalleeForSRet(), llvm::MachineFrameInfo::computeMaxCallFrameSize(), ContainsReg(), createBBSelectReg(), llvm::createBURRListDAGScheduler(), llvm::createCopyConstrainDAGMutation(), llvm::createFalkorMarkStridedAccessesPass(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::createLoadClusterDAGMutation(), createPHIsForCMOVsInSinkBB(), createPHIsForSelects(), llvm::createR600ExpandSpecialInstrsPass(), llvm::createR600ISelDag(), llvm::createSIAddIMGInitPass(), llvm::createSIDebuggerInsertNopsPass(), llvm::createSIFixWWMLivenessPass(), llvm::createSIModeRegisterPass(), llvm::createSIWholeQuadModePass(), llvm::createSourceListDAGScheduler(), llvm::createSparcDelaySlotFillerPass(), llvm::createStoreClusterDAGMutation(), llvm::createSystemZLDCleanupPass(), llvm::createSystemZShortenInstPass(), llvm::createX86CondBrFolding(), llvm::createX86FixupBWInsts(), llvm::createX86FixupLEAs(), llvm::createX86FixupSetCC(), llvm::createX86IndirectBranchTrackingPass(), llvm::createX86OptimizeLEAs(), llvm::createX86RetpolineThunksPass(), llvm::createXCoreFrameToArgsOffsetEliminationPass(), llvm::Mips16FrameLowering::determineCalleeSaves(), llvm::ARMFrameLowering::determineCalleeSaves(), doesNotGeneratecode(), llvm::VirtRegMap::dump(), dumpMachineInstrRangeWithSlotIndex(), llvm::AArch64FrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::WebAssemblyFrameLowering::eliminateCallFramePseudoInstr(), llvm::AVRFrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::ARCFrameLowering::eliminateCallFramePseudoInstr(), llvm::PPCFrameLowering::eliminateCallFramePseudoInstr(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::WebAssemblyRegisterInfo::eliminateFrameIndex(), llvm::RISCVRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), llvm::ARCRegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::SystemZRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), emitAlignedDPRCS2Restores(), emitAlignedDPRCS2Spills(), llvm::PPCTargetLowering::EmitAtomicBinary(), emitBuildPairF64Pseudo(), llvm::AArch64FrameLowering::emitCalleeSavedFrameMoves(), emitClzero(), emitComments(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AVRFrameLowering::emitEpilogue(), llvm::Thumb1FrameLowering::emitEpilogue(), llvm::Mips16FrameLowering::emitEpilogue(), llvm::MipsSEFrameLowering::emitEpilogue(), llvm::SparcFrameLowering::emitEpilogue(), llvm::MSP430FrameLowering::emitEpilogue(), llvm::XCoreFrameLowering::emitEpilogue(), llvm::ARMFrameLowering::emitEpilogue(), llvm::AArch64FrameLowering::emitEpilogue(), llvm::ARCFrameLowering::emitEpilogue(), llvm::WebAssemblyFrameLowering::emitEpilogue(), llvm::PPCFrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), emitGPDisp(), emitIndirectDst(), emitIndirectSrc(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::BPFTargetLowering::EmitInstrWithCustomInserter(), llvm::RISCVTargetLowering::EmitInstrWithCustomInserter(), llvm::AVRTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), llvm::ARMBaseRegisterInfo::emitLoadConstPool(), emitMonitor(), EmitNop(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), emitPostSt(), llvm::AVRFrameLowering::emitPrologue(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::Mips16FrameLowering::emitPrologue(), llvm::MipsSEFrameLowering::emitPrologue(), llvm::SparcFrameLowering::emitPrologue(), llvm::MSP430FrameLowering::emitPrologue(), llvm::XCoreFrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::ARCFrameLowering::emitPrologue(), llvm::AArch64FrameLowering::emitPrologue(), llvm::WebAssemblyFrameLowering::emitPrologue(), llvm::PPCFrameLowering::emitPrologue(), emitRDPKRU(), llvm::MSP430TargetLowering::EmitShiftInstr(), emitSplitF64Pseudo(), emitThumb1LoadConstPool(), emitThumb2LoadConstPool(), emitWRPKRU(), eraseDeadBBsAndChildren(), llvm::LiveRangeEdit::eraseVirtReg(), llvm::InstructionSelector::executeMatchTable(), llvm::AArch64InstrInfo::expandPostRAPseudo(), llvm::SparcTargetLowering::expandSelectCC(), llvm::FastISel::fastEmitBranch(), llvm::LegalizerHelper::fewerElementsVector(), llvm::finalizeBundle(), FindCallSeqStart(), findIncDecAfter(), findPotentialBlockers(), llvm::MachineInstr::findRegisterDefOperand(), findStartOfTree(), findTemporariesForLR(), findUncondBrI(), fixupGlobalSaddr(), fuseInstructionPair(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), getAdjustedCmp(), getAllSGPRs(), llvm::HexagonFrameLowering::getCalleeSavedSpillSlots(), getCmpForPseudo(), getCombinerObjective(), getCompareCC(), getComparePred(), getCompareSourceReg(), GetDSubRegs(), llvm::getEHScopeMembership(), getEquivalentCallShort(), llvm::ARMTargetLowering::getExceptionSelectorRegister(), llvm::MachineBasicBlock::getFallThrough(), getFrameIndexOperandNum(), llvm::ARMHazardRecognizer::getHazardType(), getImplicitScaleFactor(), llvm::RegisterBankInfo::getInstrMappingImpl(), llvm::MSP430InstrInfo::getInstSizeInBytes(), llvm::AVRInstrInfo::getInstSizeInBytes(), llvm::SystemZTTIImpl::getIntImmCost(), llvm::RegisterBankInfo::getInvalidInstructionMapping(), getLeaOP(), getLoadStoreOffsetAlign(), getLSMultipleTransferSize(), getMappedOp(), llvm::GCNSubtarget::getMaxNumVGPRs(), getMFHiLoOpc(), getMopState(), getOffsetFromIndices(), getOModValue(), llvm::SDNode::getOperationName(), getPermuteMask(), getPHIDestReg(), getPostIndexedLoadStoreOpcode(), llvm::PPCTargetLowering::getPrefLoopAlignment(), getReassignedChan(), llvm::MachineInstr::getRegClassConstraintEffectForVReg(), getRegClassForUnfoldedLoad(), getRegClassFromGRPhysReg(), llvm::FastISel::getRegForValue(), llvm::R600RegisterInfo::getReservedRegs(), getRetpolineSymbol(), getSchedRegions(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::X86InstrInfo::getSerializableDirectMachineOperandTargetFlags(), llvm::Legalizer::getSetProperties(), getSplatConstantFP(), getSubOpcode(), getTag(), getTargetIndexName(), llvm::BPFTargetLowering::getTargetNodeName(), llvm::rdf::DataFlowGraph::getTII(), llvm::HexagonSubtarget::getTypeAlignment(), getUnconditionalBrDisp(), getUnderlyingArgReg(), getVariantKind(), getZeroLatency(), llvm::MipsTargetLowering::HandleByVal(), hasAnyNonFlatUseOfReg(), HasArgumentDef(), llvm::RISCVFrameLowering::hasFP(), hasOneNonDBGUseInst(), hasVulnerableLoad(), llvm::HexagonBlockRanges::HexagonBlockRanges(), hoistAndMergeSGPRInits(), llvm::ConvergingVLIWScheduler::initialize(), INITIALIZE_PASS(), initSlots2Values(), llvm::SITargetLowering::insertCopiesSplitCSR(), llvm::AArch64TargetLowering::insertCopiesSplitCSR(), llvm::PPCTargetLowering::insertCopiesSplitCSR(), insertCopy(), insertCSRRestores(), insertCSRSaves(), insertDAGNode(), insertDeleteInstructions(), InsertLDR_STR(), insertNopBeforeInstruction(), insertPHI(), InsertReturnAddressAuth(), llvm::Mips16RegisterInfo::intRegClass(), IsChainDependent(), isCompareZero(), isCopy(), llvm::isCopyMulResult(), isDbgValueDescribedByReg(), isEFLAGSLive(), isFpMulInstruction(), isFullCopyOf(), isFullUndefDef(), isHardwareLoop(), isImplicitlyDef(), isInRage(), llvm::X86TargetLowering::isIntDivCheap(), isLEA(), isLEASimpleIncOrDec(), isLiveOut(), llvm::ARMBaseInstrInfo::isLoadFromStackSlotPostFE(), isMergeableLdStUpdate(), isMulPowOf2(), isOperandOf(), llvm::rdf::TargetOperandInfo::isPreserving(), llvm::rdf::DataFlowGraph::IsPreservingDef(), IsPseudoCallIndirect(), llvm::isPushOpcode(), IsSafeAndProfitableToMove(), isSecondInstructionInSequence(), isSExtLoad(), isSimpleIf(), isStackPtrRelative(), IsUnconditionalJump(), isUseSafeToFold(), llvm::MachineRegisterInfo::liveins(), llvm::X86CallLowering::lowerCall(), llvm::PPCRegisterInfo::lowerCRBitRestore(), llvm::PPCRegisterInfo::lowerCRBitSpilling(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::PPCRegisterInfo::lowerDynamicAreaOffset(), LowerFPToInt(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), llvm::LiveRangeEdit::Delegate::LRE_DidCloneVirtReg(), makeImplicit(), MatchingStackOffset(), matchSwap(), llvm::SIRegisterInfo::materializeFrameBaseRegister(), llvm::AArch64RegisterInfo::materializeFrameBaseRegister(), llvm::PPCRegisterInfo::materializeFrameBaseRegister(), llvm::ARMBaseRegisterInfo::materializeFrameBaseRegister(), mayAlias(), Mips16WhichOp8uOr16simm(), MoveAndTeeForMultiUse(), llvm::X86TargetLowering::needsFixedCatchObjects(), optimizeVcndVcmpPair(), packCmovGroup(), parseCond(), performCustomAdjustments(), llvm::R600TargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PostISelFolding(), llvm::MIPrinter::print(), llvm::MachineBasicBlock::print(), llvm::HexagonBlockRanges::PrintRangeMap::PrintRangeMap(), llvm::MachineOperand::printTargetFlags(), llvm::AArch64FrameLowering::processFunctionBeforeFrameFinalized(), profitImm(), readsVCCZ(), llvm::TargetInstrInfo::reassociateOps(), llvm::MachineRegisterInfo::recomputeRegClass(), llvm::PostGenericScheduler::releaseBottomNode(), llvm::LiveRangeEdit::rematerializeAt(), removeRedundantBlockingStores(), replaceFI(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::ThumbRegisterInfo::resolveFrameIndex(), llvm::SIRegisterInfo::resolveFrameIndex(), llvm::AArch64RegisterInfo::resolveFrameIndex(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::ARMBaseRegisterInfo::resolveFrameIndex(), llvm::ARMFrameLowering::ResolveFrameIndexReference(), llvm::AVRFrameLowering::restoreCalleeSavedRegisters(), llvm::Thumb1FrameLowering::restoreCalleeSavedRegisters(), llvm::SystemZFrameLowering::restoreCalleeSavedRegisters(), llvm::XCoreFrameLowering::restoreCalleeSavedRegisters(), llvm::MSP430FrameLowering::restoreCalleeSavedRegisters(), llvm::AArch64FrameLowering::restoreCalleeSavedRegisters(), llvm::PPCFrameLowering::restoreCalleeSavedRegisters(), restoreCRs(), llvm::SIRegisterInfo::restoreSGPR(), llvm::rewriteAArch64FrameIndex(), llvm::UnreachableBlockElimPass::run(), llvm::InsertNOPLoad::runOnMachineFunction(), llvm::VirtRegMap::runOnMachineFunction(), llvm::FixAllFDIVSQRT::runOnMachineFunction(), llvm::MachinePipeliner::runOnMachineFunction(), llvm::AMDGPUAsmPrinter::runOnMachineFunction(), llvm::AVRDynAllocaSR::runOnMachineFunction(), llvm::Mips16RegisterInfo::saveScavengerRegister(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::ScheduleDAGMILive::scheduleMI(), llvm::FastISel::selectBitCast(), llvm::FastISel::selectCall(), llvm::FastISel::selectIntrinsicCall(), llvm::FastISel::selectPatchpoint(), llvm::FastISel::selectStackmap(), llvm::FastISel::selectXRayCustomEvent(), llvm::FastISel::selectXRayTypedEvent(), llvm::FunctionLoweringInfo::set(), setCallTargetReg(), llvm::MachineMemOperand::setOffset(), llvm::RegScavenger::setRegUsed(), llvm::DwarfDebug::shareAcrossDWOCUs(), llvm::SIFrameLowering::SIFrameLowering(), llvm::MachineBasicBlock::SkipPHIsAndLabels(), llvm::MachineBasicBlock::SkipPHIsLabelsAndDebug(), llvm::SparcFrameLowering::SparcFrameLowering(), llvm::AVRFrameLowering::spillCalleeSavedRegisters(), llvm::Thumb1FrameLowering::spillCalleeSavedRegisters(), llvm::SystemZFrameLowering::spillCalleeSavedRegisters(), llvm::MipsSEFrameLowering::spillCalleeSavedRegisters(), llvm::XCoreFrameLowering::spillCalleeSavedRegisters(), llvm::MSP430FrameLowering::spillCalleeSavedRegisters(), llvm::AArch64FrameLowering::spillCalleeSavedRegisters(), llvm::PPCFrameLowering::spillCalleeSavedRegisters(), llvm::SIRegisterInfo::spillSGPR(), splitBlock(), llvm::MachineBasicBlock::SplitCriticalEdge(), llvm::SITargetLowering::splitKillBlock(), splitMBB(), llvm::LiveDebugVariables::splitRegister(), subRangeLiveAt(), llvm::InstructionSelector::testMIPredicate_MI(), tieOpsIfNeeded(), tryFoldInst(), tryOptimizeLEAtoMOV(), trySequenceOfOnes(), updateKillStatus(), UpdateOperandRegClass(), llvm::MachineBasicBlock::updateTerminator(), usedAsAddr(), llvm::LegalizerHelper::widenScalar(), WindowsRequiresStackProbe(), llvm::SITargetLowering::wrapAddr64Rsrc(), llvm::WebAssemblyFrameLowering::writeSPToGlobal(), X86ChooseCmpImmediateOpcode(), X86SelectAddress(), and llvm::AntiDepBreaker::~AntiDepBreaker().

1.8.13

1.8.13