#include "llvm/CodeGen/TargetRegisterInfo.h"

Public Types | |

| using | iterator = const MCPhysReg * |

| using | const_iterator = const MCPhysReg * |

| using | sc_iterator = const TargetRegisterClass *const * |

Public Member Functions | |

| unsigned | getID () const |

| Return the register class ID number. More... | |

| iterator | begin () const |

| begin/end - Return all of the registers in this class. More... | |

| iterator | end () const |

| unsigned | getNumRegs () const |

| Return the number of registers in this class. More... | |

| iterator_range< SmallVectorImpl< MCPhysReg >::const_iterator > | getRegisters () const |

| unsigned | getRegister (unsigned i) const |

| Return the specified register in the class. More... | |

| bool | contains (unsigned Reg) const |

| Return true if the specified register is included in this register class. More... | |

| bool | contains (unsigned Reg1, unsigned Reg2) const |

| Return true if both registers are in this class. More... | |

| int | getCopyCost () const |

| Return the cost of copying a value between two registers in this class. More... | |

| bool | isAllocatable () const |

| Return true if this register class may be used to create virtual registers. More... | |

| bool | hasSubClass (const TargetRegisterClass *RC) const |

| Return true if the specified TargetRegisterClass is a proper sub-class of this TargetRegisterClass. More... | |

| bool | hasSubClassEq (const TargetRegisterClass *RC) const |

| Returns true if RC is a sub-class of or equal to this class. More... | |

| bool | hasSuperClass (const TargetRegisterClass *RC) const |

| Return true if the specified TargetRegisterClass is a proper super-class of this TargetRegisterClass. More... | |

| bool | hasSuperClassEq (const TargetRegisterClass *RC) const |

| Returns true if RC is a super-class of or equal to this class. More... | |

| const uint32_t * | getSubClassMask () const |

| Returns a bit vector of subclasses, including this one. More... | |

| const uint16_t * | getSuperRegIndices () const |

| Returns a 0-terminated list of sub-register indices that project some super-register class into this register class. More... | |

| sc_iterator | getSuperClasses () const |

| Returns a NULL-terminated list of super-classes. More... | |

| bool | isASubClass () const |

| Return true if this TargetRegisterClass is a subset class of at least one other TargetRegisterClass. More... | |

| ArrayRef< MCPhysReg > | getRawAllocationOrder (const MachineFunction &MF) const |

| Returns the preferred order for allocating registers from this register class in MF. More... | |

| LaneBitmask | getLaneMask () const |

| Returns the combination of all lane masks of register in this class. More... | |

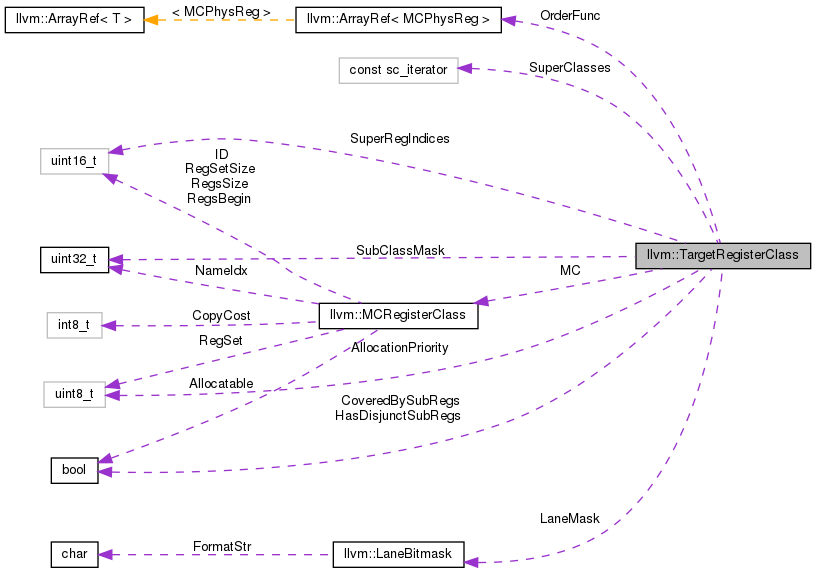

Public Attributes | |

| const MCRegisterClass * | MC |

| const uint32_t * | SubClassMask |

| const uint16_t * | SuperRegIndices |

| const LaneBitmask | LaneMask |

| const uint8_t | AllocationPriority |

| Classes with a higher priority value are assigned first by register allocators using a greedy heuristic. More... | |

| const bool | HasDisjunctSubRegs |

| Whether the class supports two (or more) disjunct subregister indices. More... | |

| const bool | CoveredBySubRegs |

| Whether a combination of subregisters can cover every register in the class. More... | |

| const sc_iterator | SuperClasses |

| ArrayRef< MCPhysReg >(* | OrderFunc )(const MachineFunction &) |

Detailed Description

Definition at line 45 of file TargetRegisterInfo.h.

Member Typedef Documentation

◆ const_iterator

Definition at line 48 of file TargetRegisterInfo.h.

◆ iterator

Definition at line 47 of file TargetRegisterInfo.h.

◆ sc_iterator

Definition at line 49 of file TargetRegisterInfo.h.

Member Function Documentation

◆ begin()

|

inline |

begin/end - Return all of the registers in this class.

Definition at line 72 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::begin().

Referenced by allocateCCRegs(), allocateSGPR32InputImpl(), llvm::PPCInstrInfo::DefinesPredicate(), llvm::HexagonBlockRanges::expandToSubRegs(), getRawAllocationOrder(), GetRegistersForValue(), and llvm::MipsTargetLowering::getTypeForExtReturn().

◆ contains() [1/2]

Return true if the specified register is included in this register class.

This does not include virtual registers.

Definition at line 90 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::contains().

Referenced by llvm::MachineFunction::addLiveIn(), canFoldCopy(), llvm::SystemZInstrInfo::convertToThreeAddress(), copyHint(), llvm::createBreakFalseDeps(), definesFullReg(), llvm::PPCInstrInfo::DefinesPredicate(), getComparePred(), llvm::R600InstrInfo::getIndirectIndexBegin(), llvm::SystemZRegisterInfo::getRegAllocationHints(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), INITIALIZE_PASS(), llvm::PPCInstrInfo::insertSelect(), isNopCopy(), llvm::R600SchedStrategy::releaseBottomNode(), selectCopy(), llvm::CoalescerPair::setRegisters(), llvm::SystemZRegisterInfo::shouldCoalesce(), UpdateOperandRegClass(), and llvm::SIInstrInfo::verifyInstruction().

◆ contains() [2/2]

Return true if both registers are in this class.

Definition at line 95 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::contains().

◆ end()

|

inline |

Definition at line 73 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::end().

Referenced by llvm::PPCInstrInfo::DefinesPredicate(), and GetRegistersForValue().

◆ getCopyCost()

|

inline |

Return the cost of copying a value between two registers in this class.

A negative number means the register class is very expensive to copy e.g. status flag register classes.

Definition at line 102 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::getCopyCost().

Referenced by CheckForPhysRegDependency().

◆ getID()

|

inline |

Return the register class ID number.

Definition at line 68 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::getID().

Referenced by llvm::RegsForValue::AddInlineAsmOperands(), buildMUBUFOffsetLoadStore(), llvm::SIInstrInfo::canInsertSelect(), llvm::HexagonEvaluator::composeWithSubRegIndex(), llvm::RegisterBank::covers(), findSRegBaseAndIndex(), llvm::HexagonRegisterInfo::getCallerSavedRegs(), llvm::HexagonRegisterInfo::getHexagonSubRegIndex(), llvm::ARMBaseRegisterInfo::getLargestLegalSuperClass(), llvm::MipsRegisterBankInfo::getRegBankFromRegClass(), llvm::ARMRegisterBankInfo::getRegBankFromRegClass(), llvm::AArch64RegisterBankInfo::getRegBankFromRegClass(), llvm::TargetRegisterInfo::getRegClassInfo(), llvm::MipsRegisterInfo::getRegPressureLimit(), llvm::PPCRegisterInfo::getRegPressureLimit(), llvm::X86RegisterInfo::getRegPressureLimit(), llvm::AArch64RegisterInfo::getRegPressureLimit(), llvm::ARMBaseRegisterInfo::getRegPressureLimit(), llvm::SIRegisterInfo::getRegPressureLimit(), hasSubClassEq(), INITIALIZE_PASS(), isOpcWithIntImmediate(), isUseSafeToFold(), llvm::BitMaskClassIterator::isValid(), llvm::HexagonEvaluator::mask(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::RegisterClassInfo::runOnMachineFunction(), llvm::ResourcePriorityQueue::scheduledNode(), and llvm::HexagonRegisterInfo::shouldCoalesce().

◆ getLaneMask()

|

inline |

Returns the combination of all lane masks of register in this class.

The lane masks of the registers are the combination of all lane masks of their subregisters. Returns 1 if there are no subregisters.

Definition at line 195 of file TargetRegisterInfo.h.

References LaneMask.

Referenced by llvm::ScheduleDAGInstrs::getLaneMaskForMO(), and llvm::MachineRegisterInfo::getMaxLaneMaskForVReg().

◆ getNumRegs()

|

inline |

Return the number of registers in this class.

Definition at line 76 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::getNumRegs().

Referenced by llvm::RegisterClassInfo::computePSetLimit(), constrainRegClass(), llvm::createGreedyRegisterAllocator(), llvm::R600InstrInfo::getIndirectIndexBegin(), getRawAllocationOrder(), llvm::RegisterClassInfo::runOnMachineFunction(), llvm::ExecutionDomainFix::runOnMachineFunction(), and llvm::SystemZRegisterInfo::shouldCoalesce().

◆ getRawAllocationOrder()

|

inline |

Returns the preferred order for allocating registers from this register class in MF.

The raw order comes directly from the .td file and may include reserved registers that are not allocatable. Register allocators should also make sure to allocate callee-saved registers only after all the volatiles are used. The RegisterClassInfo class provides filtered allocation orders with callee-saved registers moved to the end.

The MachineFunction argument can be used to tune the allocatable registers based on the characteristics of the function, subtarget, or other criteria.

By default, this method returns all registers in the class.

Definition at line 188 of file TargetRegisterInfo.h.

References begin(), getNumRegs(), llvm::makeArrayRef(), and OrderFunc.

Referenced by llvm::HexagonFrameLowering::determineCalleeSaves(), getAllocatableSetForRC(), isACalleeSavedRegister(), llvm::RegisterClassInfo::runOnMachineFunction(), and llvm::RegScavenger::scavengeRegisterBackwards().

◆ getRegister()

Return the specified register in the class.

Definition at line 84 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::getRegister().

Referenced by llvm::R600InstrInfo::expandPostRAPseudo(), llvm::R600InstrInfo::getIndirectIndexBegin(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), and llvm::tryFoldSPUpdateIntoPushPop().

◆ getRegisters()

|

inline |

Definition at line 79 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::begin(), llvm::MCRegisterClass::end(), and llvm::make_range().

◆ getSubClassMask()

Returns a bit vector of subclasses, including this one.

The vector is indexed by class IDs.

To use it, consider the returned array as a chunk of memory that contains an array of bits of size NumRegClasses. Each 32-bit chunk contains a bitset of the ID of the subclasses in big-endian style. I.e., the representation of the memory from left to right at the bit level looks like: [31 30 ... 1 0] [ 63 62 ... 33 32] ... [ XXX NumRegClasses NumRegClasses - 1 ... ] Where the number represents the class ID and XXX bits that should be ignored.

See the implementation of hasSubClassEq for an example of how it can be used.

Definition at line 147 of file TargetRegisterInfo.h.

References SubClassMask.

Referenced by llvm::TargetRegisterInfo::getAllocatableClass(), llvm::TargetRegisterInfo::getCommonSubClass(), and llvm::TargetRegisterInfo::getMatchingSuperRegClass().

◆ getSuperClasses()

|

inline |

Returns a NULL-terminated list of super-classes.

The classes are ordered by ID which is also a topological ordering from large to small classes. The list does NOT include the current class.

Definition at line 165 of file TargetRegisterInfo.h.

References SuperClasses.

Referenced by llvm::HexagonRegisterInfo::getHexagonSubRegIndex(), llvm::X86RegisterInfo::getLargestLegalSuperClass(), llvm::ARMBaseRegisterInfo::getLargestLegalSuperClass(), and isNopCopy().

◆ getSuperRegIndices()

|

inline |

Returns a 0-terminated list of sub-register indices that project some super-register class into this register class.

The list has an entry for each Idx such that:

There exists SuperRC where: For all Reg in SuperRC: this->contains(Reg:Idx)

Definition at line 158 of file TargetRegisterInfo.h.

References SuperRegIndices.

◆ hasSubClass()

|

inline |

Return true if the specified TargetRegisterClass is a proper sub-class of this TargetRegisterClass.

Definition at line 110 of file TargetRegisterInfo.h.

References hasSubClassEq().

Referenced by llvm::TargetRegisterInfo::getMinimalPhysRegClass(), and hasSuperClass().

◆ hasSubClassEq()

|

inline |

Returns true if RC is a sub-class of or equal to this class.

Definition at line 115 of file TargetRegisterInfo.h.

References getID().

Referenced by llvm::MachineFunction::addLiveIn(), canFoldCopy(), llvm::HexagonFrameLowering::determineCalleeSaves(), getRegClassFromGRPhysReg(), hasSubClass(), hasSuperClassEq(), and UpdateOperandRegClass().

◆ hasSuperClass()

|

inline |

Return true if the specified TargetRegisterClass is a proper super-class of this TargetRegisterClass.

Definition at line 122 of file TargetRegisterInfo.h.

References hasSubClass().

◆ hasSuperClassEq()

|

inline |

Returns true if RC is a super-class of or equal to this class.

Definition at line 127 of file TargetRegisterInfo.h.

References hasSubClassEq().

Referenced by getComparePred(), llvm::PPCInstrInfo::getOperandLatency(), isEFLAGSLive(), isFPR64(), isFRClass(), isGRClass(), llvm::Thumb1InstrInfo::loadRegFromStackSlot(), matchPair(), llvm::SystemZRegisterInfo::shouldCoalesce(), and swapMIOperands().

◆ isAllocatable()

|

inline |

Return true if this register class may be used to create virtual registers.

Definition at line 106 of file TargetRegisterInfo.h.

References llvm::MCRegisterClass::isAllocatable().

Referenced by llvm::constrainOperandRegClass(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::TargetRegisterInfo::getAllocatableClass(), getAllocatableSetForRC(), and llvm::MachineRegisterInfo::setRegClass().

◆ isASubClass()

|

inline |

Return true if this TargetRegisterClass is a subset class of at least one other TargetRegisterClass.

Definition at line 171 of file TargetRegisterInfo.h.

Member Data Documentation

◆ AllocationPriority

| const uint8_t llvm::TargetRegisterClass::AllocationPriority |

Classes with a higher priority value are assigned first by register allocators using a greedy heuristic.

The value is in the range [0,63].

Definition at line 58 of file TargetRegisterInfo.h.

Referenced by llvm::createGreedyRegisterAllocator().

◆ CoveredBySubRegs

Whether a combination of subregisters can cover every register in the class.

See also the CoveredBySubRegs description in Target.td.

Definition at line 63 of file TargetRegisterInfo.h.

Referenced by isCrossCopy().

◆ HasDisjunctSubRegs

Whether the class supports two (or more) disjunct subregister indices.

Definition at line 60 of file TargetRegisterInfo.h.

Referenced by llvm::ScheduleDAGInstrs::getLaneMaskForMO(), and llvm::MachineRegisterInfo::shouldTrackSubRegLiveness().

◆ LaneMask

| const LaneBitmask llvm::TargetRegisterClass::LaneMask |

Definition at line 55 of file TargetRegisterInfo.h.

Referenced by llvm::rdf::PhysicalRegisterInfo::getAliasSet(), getLaneMask(), isCrossCopy(), llvm::TargetRegisterInfo::reverseComposeSubRegIndexLaneMask(), and llvm::rdf::CopyPropagation::run().

◆ MC

| const MCRegisterClass* llvm::TargetRegisterClass::MC |

Definition at line 52 of file TargetRegisterInfo.h.

Referenced by llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::TargetRegisterInfo::getRegClassName(), and llvm::SIRegisterInfo::getRegSplitParts().

◆ OrderFunc

| ArrayRef<MCPhysReg>(* llvm::TargetRegisterClass::OrderFunc) (const MachineFunction &) |

Definition at line 65 of file TargetRegisterInfo.h.

Referenced by getRawAllocationOrder().

◆ SubClassMask

Definition at line 53 of file TargetRegisterInfo.h.

Referenced by getSubClassMask().

◆ SuperClasses

| const sc_iterator llvm::TargetRegisterClass::SuperClasses |

Definition at line 64 of file TargetRegisterInfo.h.

Referenced by getSuperClasses().

◆ SuperRegIndices

| const uint16_t* llvm::TargetRegisterClass::SuperRegIndices |

Definition at line 54 of file TargetRegisterInfo.h.

Referenced by getSuperRegIndices().

The documentation for this class was generated from the following file:

- include/llvm/CodeGen/TargetRegisterInfo.h

1.8.13

1.8.13