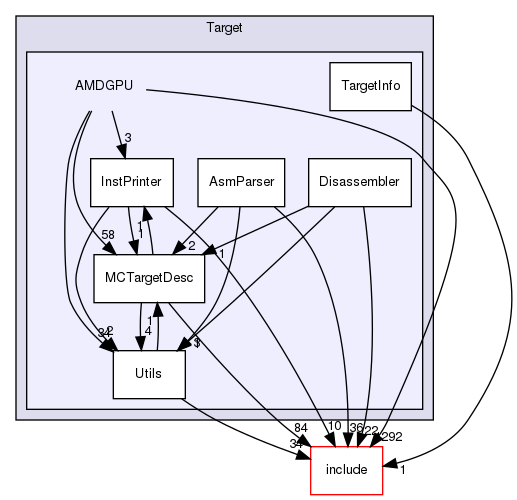

Directory dependency graph for AMDGPU:

Directories | |

| directory | AsmParser |

| directory | Disassembler |

| directory | InstPrinter |

| directory | MCTargetDesc |

| directory | TargetInfo |

| directory | Utils |

Files | |

| file | AMDGPU.h [code] |

| file | AMDGPUAliasAnalysis.cpp [code] |

| This is the AMGPU address space based alias analysis pass. | |

| file | AMDGPUAliasAnalysis.h [code] |

| This is the AMGPU address space based alias analysis pass. | |

| file | AMDGPUAlwaysInlinePass.cpp [code] |

| This pass marks all internal functions as always_inline and creates duplicates of all other functions and marks the duplicates as always_inline. | |

| file | AMDGPUAnnotateKernelFeatures.cpp [code] |

| file | AMDGPUAnnotateUniformValues.cpp [code] |

| This pass adds amdgpu.uniform metadata to IR values so this information can be used during instruction selection. | |

| file | AMDGPUArgumentUsageInfo.cpp [code] |

| file | AMDGPUArgumentUsageInfo.h [code] |

| file | AMDGPUAsmPrinter.cpp [code] |

| The AMDGPUAsmPrinter is used to print both assembly string and also binary code. | |

| file | AMDGPUAsmPrinter.h [code] |

| AMDGPU Assembly printer class. | |

| file | AMDGPUAtomicOptimizer.cpp [code] |

| This pass optimizes atomic operations by using a single lane of a wavefront to perform the atomic operation, thus reducing contention on that memory location. | |

| file | AMDGPUCallLowering.cpp [code] |

| This file implements the lowering of LLVM calls to machine code calls for GlobalISel. | |

| file | AMDGPUCallLowering.h [code] |

| This file describes how to lower LLVM calls to machine code calls. | |

| file | AMDGPUCodeGenPrepare.cpp [code] |

| This pass does misc. | |

| file | AMDGPUFixFunctionBitcasts.cpp [code] |

| Promote indirect (bitcast) calls to direct calls when they are statically known to be direct. | |

| file | AMDGPUFrameLowering.cpp [code] |

| file | AMDGPUFrameLowering.h [code] |

| Interface to describe a layout of a stack frame on an AMDGPU target. | |

| file | AMDGPUHSAMetadataStreamer.cpp [code] |

| AMDGPU HSA Metadata Streamer. | |

| file | AMDGPUHSAMetadataStreamer.h [code] |

| AMDGPU HSA Metadata Streamer. | |

| file | AMDGPUInline.cpp [code] |

| This is AMDGPU specific replacement of the standard inliner. | |

| file | AMDGPUInstrInfo.cpp [code] |

| Implementation of the TargetInstrInfo class that is common to all AMD GPUs. | |

| file | AMDGPUInstrInfo.h [code] |

| Contains the definition of a TargetInstrInfo class that is common to all AMD GPUs. | |

| file | AMDGPUInstructionSelector.cpp [code] |

| This file implements the targeting of the InstructionSelector class for AMDGPU. | |

| file | AMDGPUInstructionSelector.h [code] |

| This file declares the targeting of the InstructionSelector class for AMDGPU. | |

| file | AMDGPUIntrinsicInfo.cpp [code] |

| AMDGPU Implementation of the IntrinsicInfo class. | |

| file | AMDGPUIntrinsicInfo.h [code] |

| Interface for the AMDGPU Implementation of the Intrinsic Info class. | |

| file | AMDGPUISelDAGToDAG.cpp [code] |

| Defines an instruction selector for the AMDGPU target. | |

| file | AMDGPUISelLowering.cpp [code] |

| This is the parent TargetLowering class for hardware code gen targets. | |

| file | AMDGPUISelLowering.h [code] |

| Interface definition of the TargetLowering class that is common to all AMD GPUs. | |

| file | AMDGPULegalizerInfo.cpp [code] |

| This file implements the targeting of the Machinelegalizer class for AMDGPU. | |

| file | AMDGPULegalizerInfo.h [code] |

| This file declares the targeting of the Machinelegalizer class for AMDGPU. | |

| file | AMDGPULibCalls.cpp [code] |

| This file does AMD library function optimizations. | |

| file | AMDGPULibFunc.cpp [code] |

| file | AMDGPULibFunc.h [code] |

| file | AMDGPULowerIntrinsics.cpp [code] |

| file | AMDGPULowerKernelArguments.cpp [code] |

| file | AMDGPULowerKernelAttributes.cpp [code] |

| file | AMDGPUMachineCFGStructurizer.cpp [code] |

| file | AMDGPUMachineFunction.cpp [code] |

| file | AMDGPUMachineFunction.h [code] |

| file | AMDGPUMachineModuleInfo.cpp [code] |

| AMDGPU Machine Module Info. | |

| file | AMDGPUMachineModuleInfo.h [code] |

| AMDGPU Machine Module Info. | |

| file | AMDGPUMacroFusion.cpp [code] |

| file | AMDGPUMacroFusion.h [code] |

| file | AMDGPUMCInstLower.cpp [code] |

| Code to lower AMDGPU MachineInstrs to their corresponding MCInst. | |

| file | AMDGPUOpenCLEnqueuedBlockLowering.cpp [code] |

| file | AMDGPUPerfHintAnalysis.cpp [code] |

| Analyzes if a function potentially memory bound and if a kernel kernel may benefit from limiting number of waves to reduce cache thrashing. | |

| file | AMDGPUPerfHintAnalysis.h [code] |

| Analyzes if a function potentially memory bound and if a kernel kernel may benefit from limiting number of waves to reduce cache thrashing. | |

| file | AMDGPUPromoteAlloca.cpp [code] |

| file | AMDGPUPTNote.h [code] |

| Enums and constants for AMDGPU PT_NOTE sections. | |

| file | AMDGPURegAsmNames.inc.cpp [code] |

| file | AMDGPURegisterBankInfo.cpp [code] |

| This file implements the targeting of the RegisterBankInfo class for AMDGPU. | |

| file | AMDGPURegisterBankInfo.h [code] |

| This file declares the targeting of the RegisterBankInfo class for AMDGPU. | |

| file | AMDGPURegisterInfo.cpp [code] |

| Parent TargetRegisterInfo class common to all hw codegen targets. | |

| file | AMDGPURegisterInfo.h [code] |

| TargetRegisterInfo interface that is implemented by all hw codegen targets. | |

| file | AMDGPURewriteOutArguments.cpp [code] |

| file | AMDGPUSubtarget.cpp [code] |

| Implements the AMDGPU specific subclass of TargetSubtarget. | |

| file | AMDGPUSubtarget.h [code] |

| AMDGPU specific subclass of TargetSubtarget. | |

| file | AMDGPUTargetMachine.cpp [code] |

| The AMDGPU target machine contains all of the hardware specific information needed to emit code for R600 and SI GPUs. | |

| file | AMDGPUTargetMachine.h [code] |

| The AMDGPU TargetMachine interface definition for hw codgen targets. | |

| file | AMDGPUTargetObjectFile.cpp [code] |

| file | AMDGPUTargetObjectFile.h [code] |

| This file declares the AMDGPU-specific subclass of TargetLoweringObjectFile. | |

| file | AMDGPUTargetTransformInfo.cpp [code] |

| file | AMDGPUTargetTransformInfo.h [code] |

| This file a TargetTransformInfo::Concept conforming object specific to the AMDGPU target machine. | |

| file | AMDGPUUnifyDivergentExitNodes.cpp [code] |

| file | AMDGPUUnifyMetadata.cpp [code] |

| file | AMDILCFGStructurizer.cpp [code] |

| file | AMDKernelCodeT.h [code] |

| file | GCNDPPCombine.cpp [code] |

| file | GCNHazardRecognizer.cpp [code] |

| file | GCNHazardRecognizer.h [code] |

| file | GCNILPSched.cpp [code] |

| file | GCNIterativeScheduler.cpp [code] |

| file | GCNIterativeScheduler.h [code] |

| file | GCNMinRegStrategy.cpp [code] |

| file | GCNRegPressure.cpp [code] |

| file | GCNRegPressure.h [code] |

| file | GCNSchedStrategy.cpp [code] |

| This contains a MachineSchedStrategy implementation for maximizing wave occupancy on GCN hardware. | |

| file | GCNSchedStrategy.h [code] |

| file | R600AsmPrinter.cpp [code] |

| The R600AsmPrinter is used to print both assembly string and also binary code. | |

| file | R600AsmPrinter.h [code] |

| R600 Assembly printer class. | |

| file | R600ClauseMergePass.cpp [code] |

| R600EmitClauseMarker pass emits CFAlu instruction in a conservative maneer. | |

| file | R600ControlFlowFinalizer.cpp [code] |

| This pass compute turns all control flow pseudo instructions into native one computing their address on the fly; it also sets STACK_SIZE info. | |

| file | R600Defines.h [code] |

| file | R600EmitClauseMarkers.cpp [code] |

| Add CF_ALU. | |

| file | R600ExpandSpecialInstrs.cpp [code] |

| Vector, Reduction, and Cube instructions need to fill the entire instruction group to work correctly. | |

| file | R600FrameLowering.cpp [code] |

| file | R600FrameLowering.h [code] |

| file | R600InstrInfo.cpp [code] |

| R600 Implementation of TargetInstrInfo. | |

| file | R600InstrInfo.h [code] |

| Interface definition for R600InstrInfo. | |

| file | R600ISelLowering.cpp [code] |

| Custom DAG lowering for R600. | |

| file | R600ISelLowering.h [code] |

| R600 DAG Lowering interface definition. | |

| file | R600MachineFunctionInfo.cpp [code] |

| file | R600MachineFunctionInfo.h [code] |

| file | R600MachineScheduler.cpp [code] |

| R600 Machine Scheduler interface. | |

| file | R600MachineScheduler.h [code] |

| R600 Machine Scheduler interface. | |

| file | R600OpenCLImageTypeLoweringPass.cpp [code] |

| This pass resolves calls to OpenCL image attribute, image resource ID and sampler resource ID getter functions. | |

| file | R600OptimizeVectorRegisters.cpp [code] |

| This pass merges inputs of swizzeable instructions into vector sharing common data and/or have enough undef subreg using swizzle abilities. | |

| file | R600Packetizer.cpp [code] |

| This pass implements instructions packetization for R600. | |

| file | R600RegisterInfo.cpp [code] |

| R600 implementation of the TargetRegisterInfo class. | |

| file | R600RegisterInfo.h [code] |

| Interface definition for R600RegisterInfo. | |

| file | SIAddIMGInit.cpp [code] |

| Any MIMG instructions that use tfe or lwe require an initialization of the result register that will be written in the case of a memory access failure The required code is also added to tie this init code to the result of the img instruction. | |

| file | SIAnnotateControlFlow.cpp [code] |

| Annotates the control flow with hardware specific intrinsics. | |

| file | SIDebuggerInsertNops.cpp [code] |

| Inserts one nop instruction for each high level source statement for debugger usage. | |

| file | SIDefines.h [code] |

| file | SIFixSGPRCopies.cpp [code] |

| Copies from VGPR to SGPR registers are illegal and the register coalescer will sometimes generate these illegal copies in situations like this: | |

| file | SIFixupVectorISel.cpp [code] |

| SIFixupVectorISel pass cleans up post ISEL Vector issues. | |

| file | SIFixVGPRCopies.cpp [code] |

| Add implicit use of exec to vector register copies. | |

| file | SIFixWWMLiveness.cpp [code] |

| Computations in WWM can overwrite values in inactive channels for variables that the register allocator thinks are dead. | |

| file | SIFoldOperands.cpp [code] |

| file | SIFormMemoryClauses.cpp [code] |

| This pass creates bundles of SMEM and VMEM instructions forming memory clauses if XNACK is enabled. | |

| file | SIFrameLowering.cpp [code] |

| file | SIFrameLowering.h [code] |

| file | SIInsertSkips.cpp [code] |

| This pass inserts branches on the 0 exec mask over divergent branches branches when it's expected that jumping over the untaken control flow will be cheaper than having every workitem no-op through it. | |

| file | SIInsertWaitcnts.cpp [code] |

| Insert wait instructions for memory reads and writes. | |

| file | SIInstrInfo.cpp [code] |

| SI Implementation of TargetInstrInfo. | |

| file | SIInstrInfo.h [code] |

| Interface definition for SIInstrInfo. | |

| file | SIISelLowering.cpp [code] |

| Custom DAG lowering for SI. | |

| file | SIISelLowering.h [code] |

| SI DAG Lowering interface definition. | |

| file | SILoadStoreOptimizer.cpp [code] |

| file | SILowerControlFlow.cpp [code] |

| This pass lowers the pseudo control flow instructions to real machine instructions. | |

| file | SILowerI1Copies.cpp [code] |

| file | SIMachineFunctionInfo.cpp [code] |

| file | SIMachineFunctionInfo.h [code] |

| file | SIMachineScheduler.cpp [code] |

| SI Machine Scheduler interface. | |

| file | SIMachineScheduler.h [code] |

| SI Machine Scheduler interface. | |

| file | SIMemoryLegalizer.cpp [code] |

| Memory legalizer - implements memory model. | |

| file | SIModeRegister.cpp [code] |

| This pass inserts changes to the Mode register settings as required. | |

| file | SIOptimizeExecMasking.cpp [code] |

| file | SIOptimizeExecMaskingPreRA.cpp [code] |

| This pass removes redundant S_OR_B64 instructions enabling lanes in the exec. | |

| file | SIPeepholeSDWA.cpp [code] |

| file | SIProgramInfo.h [code] |

| Defines struct to track resource usage for kernels and entry functions. | |

| file | SIRegisterInfo.cpp [code] |

| SI implementation of the TargetRegisterInfo class. | |

| file | SIRegisterInfo.h [code] |

| Interface definition for SIRegisterInfo. | |

| file | SIShrinkInstructions.cpp [code] |

| file | SIWholeQuadMode.cpp [code] |

| This pass adds instructions to enable whole quad mode for pixel shaders, and whole wavefront mode for all programs. | |

1.8.13

1.8.13