This pass merges inputs of swizzeable instructions into vector sharing common data and/or have enough undef subreg using swizzle abilities. More...

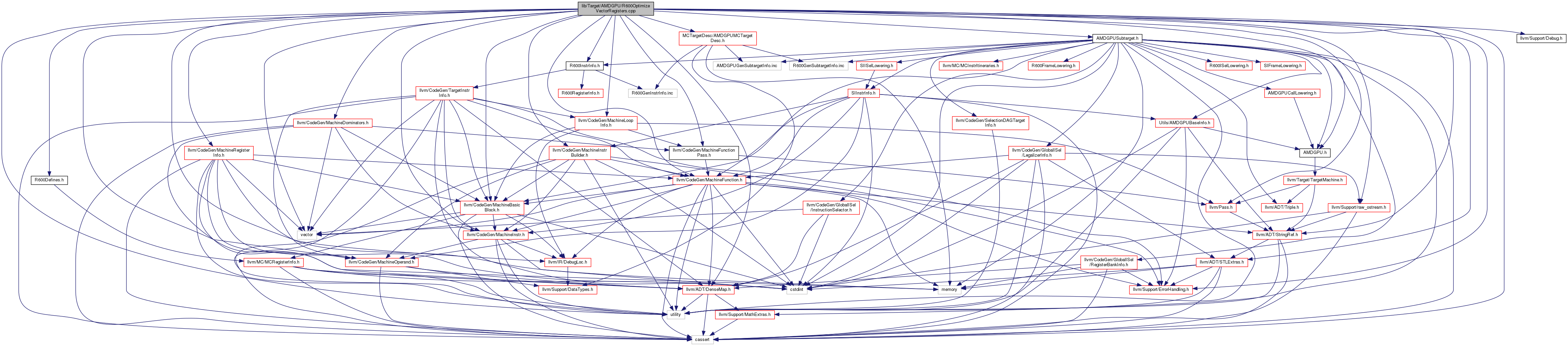

#include "AMDGPU.h"#include "AMDGPUSubtarget.h"#include "R600Defines.h"#include "R600InstrInfo.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "llvm/ADT/DenseMap.h"#include "llvm/ADT/STLExtras.h"#include "llvm/ADT/StringRef.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineDominators.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineLoopInfo.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/IR/DebugLoc.h"#include "llvm/Pass.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/raw_ostream.h"#include <cassert>#include <utility>#include <vector>

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "vec-merger" |

Functions | |

| static bool | isImplicitlyDef (MachineRegisterInfo &MRI, unsigned Reg) |

| INITIALIZE_PASS_BEGIN (R600VectorRegMerger, DEBUG_TYPE, "R600 Vector Reg Merger", false, false) INITIALIZE_PASS_END(R600VectorRegMerger | |

| static unsigned | getReassignedChan (const std::vector< std::pair< unsigned, unsigned >> &RemapChan, unsigned Chan) |

Variables | |

| DEBUG_TYPE | |

| R600 Vector Reg | Merger |

| R600 Vector Reg | false |

Detailed Description

This pass merges inputs of swizzeable instructions into vector sharing common data and/or have enough undef subreg using swizzle abilities.

For instance let's consider the following pseudo code : %5 = REG_SEQ %1, sub0, %2, sub1, %3, sub2, undef, sub3 ... %7 = REG_SEQ %1, sub0, %3, sub1, undef, sub2, %4, sub3 (swizzable Inst) %7, SwizzleMask : sub0, sub1, sub2, sub3

is turned into : %5 = REG_SEQ %1, sub0, %2, sub1, %3, sub2, undef, sub3 ... %7 = INSERT_SUBREG %4, sub3 (swizzable Inst) %7, SwizzleMask : sub0, sub2, sub1, sub3

This allow regalloc to reduce register pressure for vector registers and to reduce MOV count.

Definition in file R600OptimizeVectorRegisters.cpp.

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "vec-merger" |

Definition at line 58 of file R600OptimizeVectorRegisters.cpp.

Referenced by isImplicitlyDef().

Function Documentation

◆ getReassignedChan()

|

static |

Definition at line 193 of file R600OptimizeVectorRegisters.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::MachineBasicBlock::begin(), llvm::MachineFunction::begin(), llvm::BuildMI(), llvm::MachineBasicBlock::clear(), llvm::dbgs(), llvm::MachineInstr::dump(), E, llvm::empty(), llvm::MachineBasicBlock::end(), llvm::MachineFunction::end(), llvm::find(), first, llvm::AMDGPUSubtarget::get(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getImm(), llvm::R600Subtarget::getInstrInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), llvm::is_contained(), LLVM_DEBUG, llvm_unreachable, MI, MRI, Reg, second, llvm::MachineOperand::setImm(), llvm::ARM_MB::ST, SubReg, Swizzle(), R600_InstFlag::TEX_INST, and TII.

◆ INITIALIZE_PASS_BEGIN()

| INITIALIZE_PASS_BEGIN | ( | R600VectorRegMerger | , |

| DEBUG_TYPE | , | ||

| "R600 Vector Reg Merger" | , | ||

| false | , | ||

| false | |||

| ) |

Referenced by isImplicitlyDef().

◆ isImplicitlyDef()

|

static |

Definition at line 61 of file R600OptimizeVectorRegisters.cpp.

References llvm::AnalysisUsage::addPreserved(), llvm::AnalysisUsage::addRequired(), assert(), DEBUG_TYPE, llvm::MachineRegisterInfo::def_instr_begin(), llvm::MachineRegisterInfo::def_instr_end(), E, llvm::MachineFunctionPass::getAnalysisUsage(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), INITIALIZE_PASS_BEGIN(), llvm::MachineRegisterInfo::isReserved(), llvm_unreachable, MI, MRI, llvm::operator==(), Reg, llvm::AnalysisUsage::setPreservesCFG(), and TII.

Variable Documentation

◆ DEBUG_TYPE

| DEBUG_TYPE |

Definition at line 150 of file R600OptimizeVectorRegisters.cpp.

◆ false

| R600 Vector Reg false |

Definition at line 150 of file R600OptimizeVectorRegisters.cpp.

◆ Merger

| R600 Vector Reg Merger |

Definition at line 150 of file R600OptimizeVectorRegisters.cpp.

Referenced by llvm::windows_manifest::WindowsManifestMerger::getMergedManifest().

1.8.13

1.8.13