This is the parent TargetLowering class for hardware code gen targets. More...

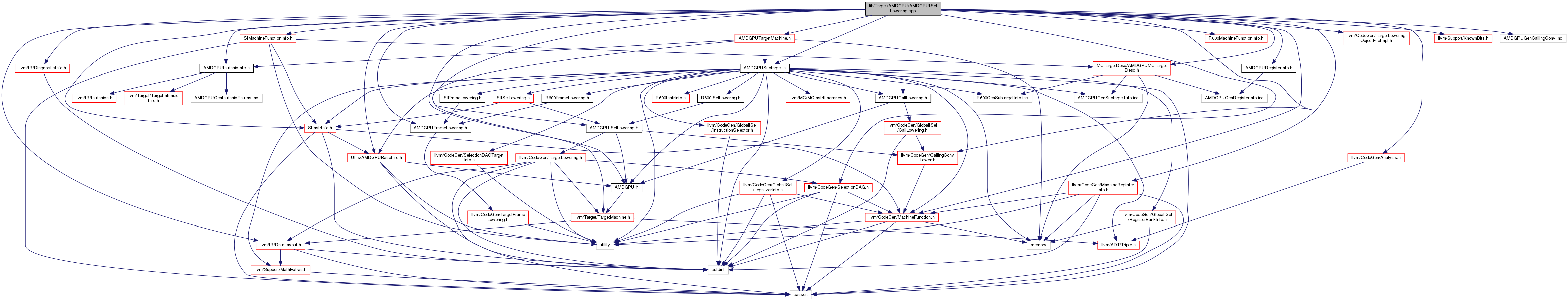

#include "AMDGPUISelLowering.h"#include "AMDGPU.h"#include "AMDGPUCallLowering.h"#include "AMDGPUFrameLowering.h"#include "AMDGPUIntrinsicInfo.h"#include "AMDGPURegisterInfo.h"#include "AMDGPUSubtarget.h"#include "AMDGPUTargetMachine.h"#include "Utils/AMDGPUBaseInfo.h"#include "R600MachineFunctionInfo.h"#include "SIInstrInfo.h"#include "SIMachineFunctionInfo.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "llvm/CodeGen/Analysis.h"#include "llvm/CodeGen/CallingConvLower.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/SelectionDAG.h"#include "llvm/CodeGen/TargetLoweringObjectFileImpl.h"#include "llvm/IR/DataLayout.h"#include "llvm/IR/DiagnosticInfo.h"#include "llvm/Support/KnownBits.h"#include "AMDGPUGenCallingConv.inc"

Go to the source code of this file.

Macros | |

| #define | AMDGPU_LOG2E_F 1.44269504088896340735992468100189214f |

| #define | AMDGPU_LN2_F 0.693147180559945309417232121458176568f |

| #define | AMDGPU_LN10_F 2.30258509299404568401799145468436421f |

| #define | NODE_NAME_CASE(node) case AMDGPUISD::node: return #node; |

Detailed Description

This is the parent TargetLowering class for hardware code gen targets.

Definition in file AMDGPUISelLowering.cpp.

Macro Definition Documentation

◆ AMDGPU_LN10_F

| #define AMDGPU_LN10_F 2.30258509299404568401799145468436421f |

Definition at line 18 of file AMDGPUISelLowering.cpp.

Referenced by llvm::AMDGPUTargetLowering::LowerOperation().

◆ AMDGPU_LN2_F

| #define AMDGPU_LN2_F 0.693147180559945309417232121458176568f |

Definition at line 17 of file AMDGPUISelLowering.cpp.

Referenced by llvm::AMDGPUTargetLowering::LowerOperation().

◆ AMDGPU_LOG2E_F

| #define AMDGPU_LOG2E_F 1.44269504088896340735992468100189214f |

Definition at line 16 of file AMDGPUISelLowering.cpp.

Referenced by llvm::AMDGPUTargetLowering::LowerOperation().

◆ NODE_NAME_CASE

| #define NODE_NAME_CASE | ( | node | ) | case AMDGPUISD::node: return #node; |

Definition at line 4077 of file AMDGPUISelLowering.cpp.

Referenced by llvm::AMDGPUTargetLowering::getTargetNodeName().

Function Documentation

◆ allocateCCRegs()

|

static |

Definition at line 44 of file AMDGPUISelLowering.cpp.

References llvm::CCState::addLoc(), llvm::CCState::AllocateReg(), llvm::TargetRegisterClass::begin(), llvm::CCValAssign::getReg(), and llvm::makeArrayRef().

Referenced by allocateSGPRTuple(), and allocateVGPRTuple().

◆ allocateSGPRTuple()

|

static |

Definition at line 58 of file AMDGPUISelLowering.cpp.

References allocateCCRegs(), llvm::MVT::f64, llvm::MVT::i64, llvm::MVT::SimpleTy, llvm::MVT::v2f32, llvm::MVT::v2i32, llvm::MVT::v4f16, and llvm::MVT::v4i16.

◆ allocateVGPRTuple()

|

static |

Definition at line 81 of file AMDGPUISelLowering.cpp.

References allocateCCRegs(), llvm::MVT::f64, llvm::MVT::i64, llvm::MVT::SimpleTy, llvm::MVT::v16f32, llvm::MVT::v16i32, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v4f16, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v8f32, and llvm::MVT::v8i32.

◆ constantFoldBFE()

|

static |

Definition at line 2750 of file AMDGPUISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), and llvm::MVT::i32.

◆ distributeOpThroughSelect()

|

static |

Definition at line 3380 of file AMDGPUISelLowering.cpp.

References llvm::TargetLowering::DAGCombinerInfo::AddToWorklist(), llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SDValue::getValueType(), and llvm::ISD::SELECT.

Referenced by foldFreeOpFromSelect().

◆ extractF64Exponent()

|

static |

Definition at line 1998 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::BFE_U32, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::MVT::i32, and llvm::ISD::SUB.

Referenced by llvm::AMDGPUTargetLowering::LowerFROUND64(), and llvm::AMDGPUTargetLowering::LowerFTRUNC().

◆ fnegFoldsIntoOp()

|

static |

Definition at line 544 of file AMDGPUISelLowering.cpp.

References llvm::ISD::FADD, llvm::ISD::FCANONICALIZE, llvm::ISD::FMA, llvm::ISD::FMAD, llvm::AMDGPUISD::FMAX_LEGACY, llvm::ISD::FMAXNUM, llvm::ISD::FMAXNUM_IEEE, llvm::AMDGPUISD::FMED3, llvm::AMDGPUISD::FMIN_LEGACY, llvm::ISD::FMINNUM, llvm::ISD::FMINNUM_IEEE, llvm::ISD::FMUL, llvm::AMDGPUISD::FMUL_LEGACY, llvm::ISD::FNEARBYINT, llvm::ISD::FRINT, llvm::ISD::FSIN, llvm::ISD::FSUB, llvm::ISD::FTRUNC, LLVM_READONLY, llvm::AMDGPUISD::RCP, llvm::AMDGPUISD::RCP_IFLAG, llvm::AMDGPUISD::RCP_LEGACY, and llvm::AMDGPUISD::SIN_HW.

Referenced by foldFreeOpFromSelect(), and llvm::AMDGPUTargetLowering::performFNegCombine().

◆ foldFreeOpFromSelect()

|

static |

Definition at line 3402 of file AMDGPUISelLowering.cpp.

References llvm::TargetLowering::DAGCombinerInfo::AddToWorklist(), llvm::TargetLowering::DAGCombinerInfo::DAG, distributeOpThroughSelect(), llvm::dyn_cast(), llvm::ISD::FABS, llvm::ISD::FMUL, llvm::ISD::FNEG, fnegFoldsIntoOp(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDValue::getValueType(), llvm::SDValue::hasOneUse(), llvm::ConstantFPSDNode::isNegative(), llvm::ISD::SELECT, and std::swap().

Referenced by llvm::AMDGPUTargetLowering::performSelectCombine().

◆ getLog2EVal()

|

static |

Definition at line 2237 of file AMDGPUISelLowering.cpp.

References llvm::lltok::APFloat, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::SelectionDAG::getConstantFP(), llvm::EVT::getScalarType(), llvm::EVT::getSimpleVT(), llvm::APFloatBase::IEEEdouble(), llvm::APFloatBase::IEEEhalf(), llvm_unreachable, and llvm::MVT::SimpleTy.

Referenced by llvm::AMDGPUTargetLowering::lowerFEXP().

◆ getMul24()

|

static |

Definition at line 3174 of file AMDGPUISelLowering.cpp.

References llvm::ISD::BUILD_PAIR, llvm::SelectionDAG::getNode(), llvm::SDValue::getValue(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, llvm::MVT::i64, llvm::AMDGPUISD::MUL_I24, llvm::AMDGPUISD::MUL_LOHI_I24, llvm::AMDGPUISD::MUL_LOHI_U24, and llvm::AMDGPUISD::MUL_U24.

Referenced by llvm::AMDGPUTargetLowering::performMulCombine().

◆ hasDefinedInitializer()

|

static |

Definition at line 1195 of file AMDGPUISelLowering.cpp.

References llvm::dyn_cast(), llvm::GlobalVariable::getInitializer(), and llvm::GlobalVariable::hasInitializer().

Referenced by llvm::AMDGPUTargetLowering::LowerGlobalAddress().

◆ hasSourceMods()

|

static |

Definition at line 585 of file AMDGPUISelLowering.cpp.

References llvm::ISD::BITCAST, llvm::ISD::CopyToReg, llvm::AMDGPUISD::DIV_SCALE, llvm::ISD::FDIV, llvm::ISD::FREM, llvm::SDNode::getOpcode(), llvm::ISD::INLINEASM, llvm::AMDGPUISD::INTERP_P1, llvm::AMDGPUISD::INTERP_P2, and llvm::ISD::SELECT.

Referenced by llvm::AMDGPUTargetLowering::allUsesHaveSourceMods().

◆ hasVolatileUser()

Definition at line 2761 of file AMDGPUISelLowering.cpp.

References llvm::SDNode::uses().

Referenced by llvm::AMDGPUTargetLowering::performLoadCombine().

◆ inverseMinMax()

Definition at line 3534 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::FMAX_LEGACY, llvm::ISD::FMAXNUM, llvm::ISD::FMAXNUM_IEEE, llvm::AMDGPUISD::FMIN_LEGACY, llvm::ISD::FMINNUM, llvm::ISD::FMINNUM_IEEE, and llvm_unreachable.

Referenced by llvm::AMDGPUTargetLowering::performFNegCombine().

◆ isCtlzOpc()

Definition at line 2264 of file AMDGPUISelLowering.cpp.

References llvm::ISD::CTLZ, and llvm::ISD::CTLZ_ZERO_UNDEF.

Referenced by llvm::AMDGPUTargetLowering::LowerCTLZ_CTTZ(), and llvm::AMDGPUTargetLowering::performCtlz_CttzCombine().

◆ isCttzOpc()

Definition at line 2268 of file AMDGPUISelLowering.cpp.

References llvm::ISD::CTTZ, and llvm::ISD::CTTZ_ZERO_UNDEF.

Referenced by llvm::AMDGPUTargetLowering::LowerCTLZ_CTTZ(), and llvm::AMDGPUTargetLowering::performCtlz_CttzCombine().

◆ isI24()

|

static |

Definition at line 2713 of file AMDGPUISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), and llvm::AMDGPUTargetLowering::numBitsSigned().

Referenced by llvm::AMDGPUTargetLowering::performMulCombine(), and llvm::AMDGPUTargetLowering::performMulhsCombine().

◆ isInv2Pi()

Definition at line 3510 of file AMDGPUISelLowering.cpp.

References llvm::APFloat::bitwiseIsEqual(), llvm::APFloatBase::IEEEdouble(), llvm::APFloatBase::IEEEhalf(), and llvm::APFloatBase::IEEEsingle().

Referenced by llvm::AMDGPUTargetLowering::isConstantCostlierToNegate().

◆ isNegativeOne()

Definition at line 3312 of file AMDGPUISelLowering.cpp.

References C, llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getTypeToTransformTo(), llvm::SDValue::getValueType(), llvm::AMDGPUSubtarget::has16BitInsts(), llvm::MVT::i16, llvm::MVT::i32, llvm::ISD::TRUNCATE, and llvm::ISD::ZERO_EXTEND.

Referenced by llvm::AMDGPUTargetLowering::performCtlz_CttzCombine().

◆ isU24()

|

static |

Definition at line 2709 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUTargetLowering::numBitsUnsigned().

Referenced by llvm::AMDGPUTargetLowering::performMulCombine(), and llvm::AMDGPUTargetLowering::performMulhuCombine().

◆ opMustUseVOP3Encoding()

|

static |

returns true if the operation will definitely need to use a 64-bit encoding, and thus will use a VOP3 encoding regardless of the source modifiers.

Definition at line 578 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f64, llvm::SDNode::getNumOperands(), and LLVM_READONLY.

Referenced by llvm::AMDGPUTargetLowering::allUsesHaveSourceMods().

◆ simplifyI24()

|

static |

Definition at line 2720 of file AMDGPUISelLowering.cpp.

References llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::SelectionDAG::GetDemandedBits(), llvm::APInt::getLowBitsSet(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SDValue::getValueSizeInBits(), llvm::SDNode::getVTList(), and llvm::TargetLowering::SimplifyDemandedBits().

Referenced by llvm::AMDGPUTargetLowering::PerformDAGCombine(), and llvm::AMDGPUTargetLowering::performMulLoHi24Combine().

1.8.13

1.8.13