SIFixupVectorISel pass cleans up post ISEL Vector issues. More...

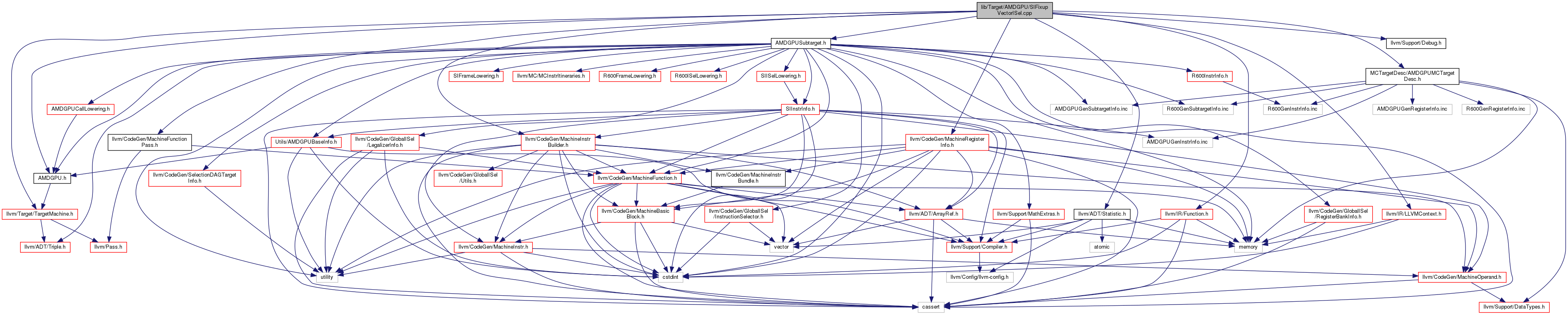

#include "AMDGPU.h"#include "AMDGPUSubtarget.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/IR/Function.h"#include "llvm/IR/LLVMContext.h"#include "llvm/Support/Debug.h"#include "llvm/Target/TargetMachine.h"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "si-fixup-vector-isel" |

Functions | |

| STATISTIC (NumSGPRGlobalOccurs, "Number of global ld/st opportunities") | |

| STATISTIC (NumSGPRGlobalSaddrs, "Number of global sgpr instructions converted") | |

| static bool | findSRegBaseAndIndex (MachineOperand *Op, unsigned &BaseReg, unsigned &IndexReg, MachineRegisterInfo &MRI, const SIRegisterInfo *TRI) |

| static bool | fixupGlobalSaddr (MachineBasicBlock &MBB, MachineFunction &MF, MachineRegisterInfo &MRI, const GCNSubtarget &ST, const SIInstrInfo *TII, const SIRegisterInfo *TRI) |

Variables | |

| static cl::opt< bool > | EnableGlobalSGPRAddr ("amdgpu-enable-global-sgpr-addr", cl::desc("Enable use of SGPR regs for GLOBAL LOAD/STORE instructions"), cl::init(false)) |

Detailed Description

SIFixupVectorISel pass cleans up post ISEL Vector issues.

Currently this will convert GLOBAL_{LOAD|STORE}_* and GLOBAL_Atomic_* instructions into their _SADDR variants, feeding the sreg into the saddr field of the new instruction. We currently handle a REG_SEQUENCE feeding the vaddr and decompose it into a base and index.

Transform: %17:vgpr_32, %19:sreg_64_xexec = V_ADD_I32_e64 %21:sgpr_32, %22:vgpr_32 %18:vgpr_32, %20:sreg_64_xexec = V_ADDC_U32_e64 %25:vgpr_32, %24:vgpr_32, %19:sreg_64_xexec %16:vreg_64 = REG_SEQUENCE %17:vgpr_32, sub0, %18:vgpr_32, sub1 %11:vreg_64 = COPY %16:vreg_64 %10:vgpr_32 = GLOBAL_LOAD_DWORD killed %11:vreg_64, 16, 0, 0 Into: %4:sreg_64_xexec = S_LOAD_DWORDX2_IMM %1:sgpr_64, 36, 0 %14:vreg_64 = REG_SEQUENCE %6:vgpr_32, sub0, %15:vgpr_32, sub1 %10:vgpr_32 = GLOBAL_LOAD_DWORD_SADDR %14:vreg_64, %4:sreg_64_xexec,16...

Definition in file SIFixupVectorISel.cpp.

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "si-fixup-vector-isel" |

Definition at line 42 of file SIFixupVectorISel.cpp.

Function Documentation

◆ findSRegBaseAndIndex()

|

static |

Definition at line 86 of file SIFixupVectorISel.cpp.

References llvm::MachineRegisterInfo::clearKillFlags(), llvm::SmallVectorBase::empty(), llvm::TargetRegisterClass::getID(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::AMDGPU::getRegBitWidth(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineOperand::getSubReg(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::SIRegisterInfo::hasVGPRs(), llvm::MachineInstr::isCopy(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRReg(), llvm::TargetRegisterInfo::isVirtualRegister(), MI, llvm::SmallVectorImpl< T >::pop_back_val(), and llvm::SmallVectorTemplateBase< T >::push_back().

Referenced by fixupGlobalSaddr().

◆ fixupGlobalSaddr()

|

static |

Definition at line 157 of file SIFixupVectorISel.cpp.

References llvm::MachineInstr::addOperand(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineInstr::cloneMemRefs(), llvm::MachineInstr::copyImplicitOps(), llvm::MachineOperand::CreateReg(), llvm::dbgs(), EnableGlobalSGPRAddr, llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), findSRegBaseAndIndex(), llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFunction(), llvm::AMDGPU::getGlobalSaddrOp(), llvm::GCNSubtarget::getInstrInfo(), llvm::SIInstrInfo::getNamedOperand(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineFunction::getRegInfo(), llvm::GCNSubtarget::getRegisterInfo(), llvm::MachineFunction::getSubtarget(), I, LLVM_DEBUG, MI, MRI, llvm::ARM_MB::ST, TII, and TRI.

◆ STATISTIC() [1/2]

| STATISTIC | ( | NumSGPRGlobalOccurs | , |

| "Number of global ld/st opportunities" | |||

| ) |

◆ STATISTIC() [2/2]

| STATISTIC | ( | NumSGPRGlobalSaddrs | , |

| "Number of global sgpr instructions converted" | |||

| ) |

Variable Documentation

◆ EnableGlobalSGPRAddr

|

static |

Referenced by fixupGlobalSaddr().

1.8.13

1.8.13