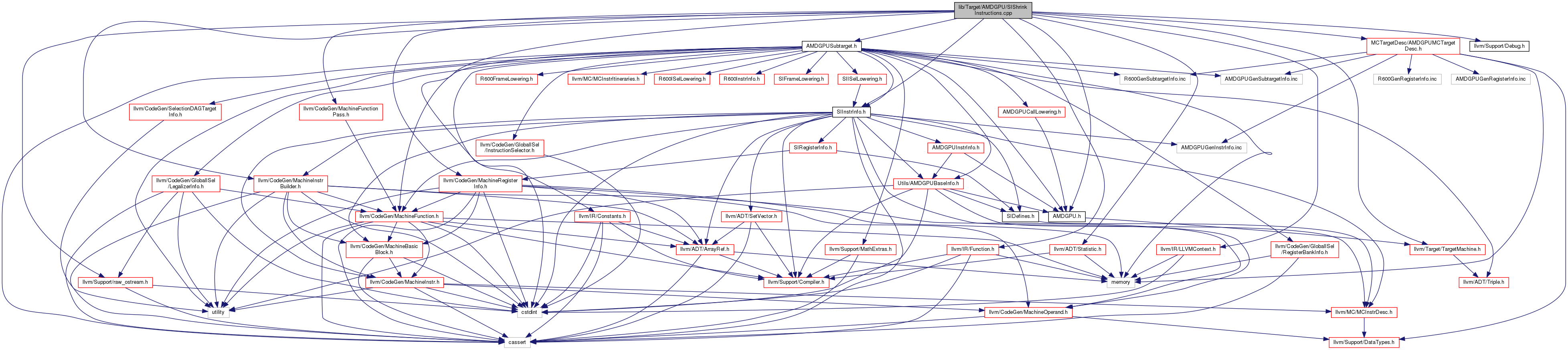

#include "AMDGPU.h"#include "AMDGPUSubtarget.h"#include "SIInstrInfo.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/IR/Constants.h"#include "llvm/IR/Function.h"#include "llvm/IR/LLVMContext.h"#include "llvm/Support/Debug.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetMachine.h"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "si-shrink-instructions" |

| The pass tries to use the 32-bit encoding for instructions when possible. More... | |

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "si-shrink-instructions" |

The pass tries to use the 32-bit encoding for instructions when possible.

Definition at line 27 of file SIShrinkInstructions.cpp.

Function Documentation

◆ copyExtraImplicitOps()

|

static |

Copy implicit register operands from specified instruction to this instruction that are not part of the instruction definition.

Definition at line 165 of file SIShrinkInstructions.cpp.

References llvm::MachineInstr::addOperand(), llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumImplicitDefs(), llvm::MCInstrDesc::getNumImplicitUses(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::isRegMask().

Referenced by matchSwap().

◆ foldImmediates()

|

static |

This function checks MI for operands defined by a move immediate instruction and then folds the literal constant into the instruction if it can.

This function assumes that MI is a VOP1, VOP2, or VOPC instructions.

Definition at line 70 of file SIShrinkInstructions.cpp.

References assert(), llvm::tgtok::Def, llvm::MachineInstr::eraseFromParent(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::MachineRegisterInfo::hasOneUse(), llvm::MachineInstr::isCommutable(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), llvm::isInt< 32 >(), llvm::MachineInstr::isMoveImmediate(), llvm::isUInt< 32 >(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::SIInstrInfo::isVOP1(), llvm::SIInstrInfo::isVOP2(), llvm::SIInstrInfo::isVOPC(), Reg, llvm::MachineOperand::setSubReg(), and llvm::MachineRegisterInfo::use_empty().

Referenced by matchSwap().

◆ getSubRegForIndex()

|

static |

Definition at line 328 of file SIShrinkInstructions.cpp.

References llvm::countTrailingZeros(), llvm::LaneBitmask::getAsInteger(), llvm::AMDGPURegisterInfo::getSubRegFromChannel(), and llvm::TargetRegisterInfo::isPhysicalRegister().

Referenced by matchSwap().

◆ instAccessReg()

|

static |

Definition at line 293 of file SIShrinkInstructions.cpp.

References llvm::LaneBitmask::any(), llvm::TargetRegisterInfo::isPhysicalRegister(), and llvm::TargetRegisterInfo::isVirtualRegister().

Referenced by instModifiesReg(), and instReadsReg().

◆ instModifiesReg()

|

static |

Definition at line 321 of file SIShrinkInstructions.cpp.

References llvm::MachineInstr::defs(), instAccessReg(), Reg, SubReg, and TRI.

Referenced by matchSwap().

◆ instReadsReg()

|

static |

Definition at line 315 of file SIShrinkInstructions.cpp.

References instAccessReg(), Reg, SubReg, TRI, and llvm::MachineInstr::uses().

Referenced by matchSwap().

◆ isKImmOperand()

|

static |

Definition at line 123 of file SIShrinkInstructions.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperandNo(), llvm::MachineOperand::getParent(), llvm::SIInstrInfo::isInlineConstant(), and llvm::isInt< 16 >().

Referenced by matchSwap(), and shrinkScalarCompare().

◆ isKImmOrKUImmOperand()

|

static |

Definition at line 135 of file SIShrinkInstructions.cpp.

References llvm::MachineOperand::getImm(), llvm::SIInstrInfo::isInlineConstant(), llvm::isInt< 16 >(), and llvm::isUInt< 16 >().

Referenced by shrinkScalarCompare().

◆ isKUImmOperand()

|

static |

Definition at line 129 of file SIShrinkInstructions.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperandNo(), llvm::MachineOperand::getParent(), llvm::SIInstrInfo::isInlineConstant(), and llvm::isUInt< 16 >().

Referenced by shrinkScalarCompare().

◆ isReverseInlineImm()

|

static |

- Returns

- true if the constant in

Srcshould be replaced with a bitreverse of an inline immediate.

Definition at line 153 of file SIShrinkInstructions.cpp.

References llvm::MachineOperand::getImm(), llvm::SIInstrInfo::isInlineConstant(), and llvm::isInt< 32 >().

Referenced by matchSwap().

◆ matchSwap()

|

static |

Definition at line 360 of file SIShrinkInstructions.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::MachineBasicBlock::begin(), llvm::MachineFunction::begin(), llvm::BuildMI(), copyExtraImplicitOps(), llvm::dbgs(), E, llvm::MachineBasicBlock::end(), llvm::MachineFunction::end(), llvm::MachineInstr::eraseFromParent(), foldImmediates(), llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getImm(), llvm::MachineInstrBuilder::getInstr(), llvm::GCNSubtarget::getInstrInfo(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::SIInstrInfo::getOpSize(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::SIInstrInfo::getRegisterInfo(), llvm::MachineOperand::getSubReg(), getSubRegForIndex(), llvm::MachineFunction::getSubtarget(), llvm::AMDGPU::getVOPe32(), llvm::GCNSubtarget::hasSwap(), I, instModifiesReg(), llvm::MachineBasicBlock::instr_end(), instReadsReg(), llvm::MachineInstr::isCommutable(), llvm::MachineInstr::isCompare(), llvm::MachineOperand::isImm(), isKImmOperand(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), isReverseInlineImm(), llvm::SIRegisterInfo::isVGPR(), llvm::TargetRegisterInfo::isVirtualRegister(), LLVM_DEBUG, MI, MRI, llvm::TargetInstrInfo::RegSubRegPair::Reg, llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), llvm::MachineOperand::setIsKill(), llvm::MachineRegisterInfo::setRegAllocationHint(), shrinkScalarCompare(), shrinkScalarLogicOp(), Size, llvm::ARM_MB::ST, llvm::TargetInstrInfo::RegSubRegPair::SubReg, std::swap(), llvm::MachineInstr::tieOperands(), TII, TRI, llvm::MachineRegisterInfo::use_nodbg_empty(), llvm::MachineRegisterInfo::use_nodbg_operands(), X, and Y.

◆ shrinkScalarCompare()

|

static |

Definition at line 177 of file SIShrinkInstructions.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::AMDGPU::getSOPKOp(), llvm::MachineOperand::isImm(), isKImmOperand(), isKImmOrKUImmOperand(), isKUImmOperand(), llvm::MachineOperand::isReg(), llvm::MachineInstr::setDesc(), and llvm::SIInstrInfo::sopkIsZext().

Referenced by matchSwap().

◆ shrinkScalarLogicOp()

|

static |

Attempt to shink AND/OR/XOR operations requiring non-inlineable literals.

For AND or OR, try using S_BITSET{0,1} to clear or set bits. If the inverse of the immediate is legal, use ANDN2, ORN2 or XNOR (as a ^ b == ~(a ^ ~b)).

- Returns

- true if the caller should continue the machine function iterator

Definition at line 220 of file SIShrinkInstructions.cpp.

References llvm::MachineOperand::ChangeToImmediate(), llvm::countTrailingOnes(), llvm::countTrailingZeros(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::MachineOperand::isImm(), llvm::AMDGPU::isInlinableLiteral32(), llvm::isPowerOf2_32(), llvm::MachineOperand::isReg(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm_unreachable, llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), and llvm::MachineRegisterInfo::setRegAllocationHint().

Referenced by matchSwap().

◆ STATISTIC() [1/2]

| STATISTIC | ( | NumInstructionsShrunk | , |

| "Number of 64-bit instruction reduced to 32-bit." | |||

| ) |

◆ STATISTIC() [2/2]

| STATISTIC | ( | NumLiteralConstantsFolded | , |

| "Number of literal constants folded into 32-bit instructions." | |||

| ) |

1.8.13

1.8.13