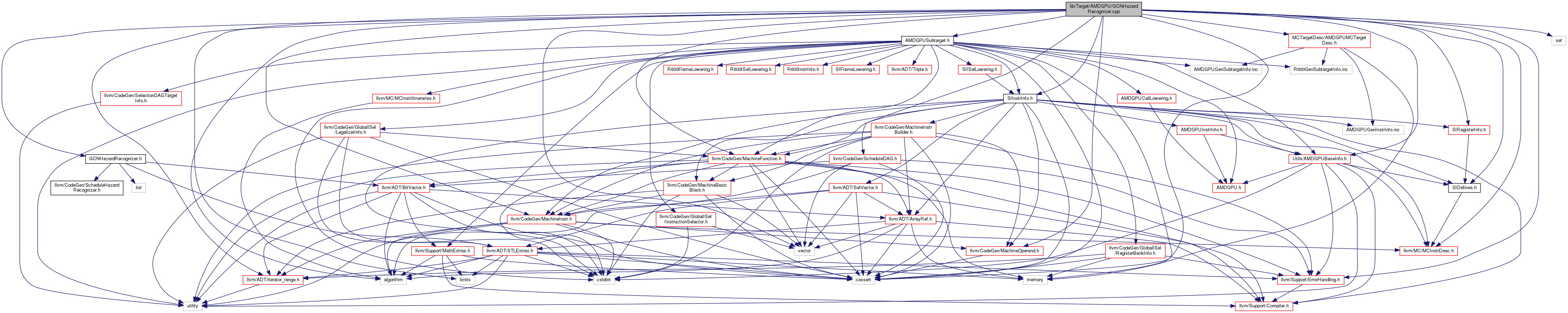

#include "GCNHazardRecognizer.h"#include "AMDGPUSubtarget.h"#include "SIDefines.h"#include "SIInstrInfo.h"#include "SIRegisterInfo.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "Utils/AMDGPUBaseInfo.h"#include "llvm/ADT/iterator_range.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/ScheduleDAG.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/Support/ErrorHandling.h"#include <algorithm>#include <cassert>#include <limits>#include <set>#include <vector>

Go to the source code of this file.

Functions | |

| static bool | isDivFMas (unsigned Opcode) |

| static bool | isSGetReg (unsigned Opcode) |

| static bool | isSSetReg (unsigned Opcode) |

| static bool | isRWLane (unsigned Opcode) |

| static bool | isRFE (unsigned Opcode) |

| static bool | isSMovRel (unsigned Opcode) |

| static bool | isSendMsgTraceDataOrGDS (const SIInstrInfo &TII, const MachineInstr &MI) |

| static unsigned | getHWReg (const SIInstrInfo *TII, const MachineInstr &RegInstr) |

| static void | addRegUnits (const SIRegisterInfo &TRI, BitVector &BV, unsigned Reg) |

| static void | addRegsToSet (const SIRegisterInfo &TRI, iterator_range< MachineInstr::const_mop_iterator > Ops, BitVector &Set) |

Function Documentation

◆ addRegsToSet()

|

static |

Definition at line 316 of file GCNHazardRecognizer.cpp.

References addRegUnits(), llvm::BitVector::anyCommon(), assert(), llvm::tgtok::Def, llvm::MachineInstr::defs(), llvm::SIInstrFlags::DPP, E, llvm::MachineInstr::getDesc(), llvm::GCNSubtarget::getGeneration(), getHWReg(), llvm::GCNSubtarget::getInstrInfo(), llvm::SIInstrInfo::getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::AMDGPU::getRegBitWidth(), llvm::MachineFunction::getRegInfo(), llvm::GCNSubtarget::getRegisterInfo(), llvm::MachineFunction::getSubtarget(), llvm::GCNSubtarget::has12DWordStoreHazard(), llvm::GCNSubtarget::hasSMovFedHazard(), I, llvm::AMDGPU::Hwreg::ID_TRAPSTS, llvm::SIInstrInfo::isBufferSMRD(), llvm::MachineInstr::isDebugInstr(), llvm::MachineOperand::isDef(), llvm::SIInstrInfo::isFLAT(), llvm::SIInstrInfo::isMIMG(), llvm::SIInstrInfo::isMTBUF(), llvm::SIInstrInfo::isMUBUF(), llvm::MachineOperand::isReg(), llvm::SIInstrInfo::isSALU(), llvm::SIRegisterInfo::isSGPRReg(), llvm::SIInstrInfo::isSMRD(), llvm::SIInstrInfo::isVALU(), llvm::SIRegisterInfo::isVGPR(), llvm::GCNSubtarget::isXNACKEnabled(), llvm::max(), llvm::MachineInstr::mayStore(), MI, llvm::InlineAsm::MIOp_FirstOperand, MRI, llvm::BitVector::none(), llvm::MCInstrDesc::OpInfo, Reg, llvm::MCOperandInfo::RegClass, llvm::AMDGPUSubtarget::SEA_ISLANDS, llvm::SIInstrFlags::SMRD, llvm::AMDGPUSubtarget::SOUTHERN_ISLANDS, llvm::MachineInstr::uses(), llvm::SIInstrFlags::VALU, and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

◆ addRegUnits()

|

static |

Definition at line 310 of file GCNHazardRecognizer.cpp.

References llvm::MCRegisterInfo::DiffListIterator::isValid(), and llvm::BitVector::set().

Referenced by addRegsToSet(), and llvm::RegScavenger::enterBasicBlockEnd().

◆ getHWReg()

|

static |

Definition at line 117 of file GCNHazardRecognizer.cpp.

References llvm::MachineOperand::getImm(), llvm::SIInstrInfo::getNamedOperand(), and llvm::AMDGPU::Hwreg::ID_MASK_.

Referenced by addRegsToSet(), and llvm::createR600MCCodeEmitter().

◆ isDivFMas()

Definition at line 59 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isRFE()

Definition at line 75 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isRWLane()

Definition at line 71 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isSendMsgTraceDataOrGDS()

|

static |

Definition at line 91 of file GCNHazardRecognizer.cpp.

References llvm::MachineOperand::getImm(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::SIInstrInfo::isAlwaysGDS(), and llvm::SIInstrInfo::isDS().

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isSGetReg()

Definition at line 63 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isSMovRel()

Definition at line 79 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ isSSetReg()

Definition at line 67 of file GCNHazardRecognizer.cpp.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), llvm::GCNHazardRecognizer::PreEmitNoops(), and llvm::GCNHazardRecognizer::RecedeCycle().

1.8.13

1.8.13