#include "Target/ARM/ARMBaseInstrInfo.h"

Static Public Member Functions | |

| static bool | isCPSRDefined (const MachineInstr &MI) |

Protected Member Functions | |

| ARMBaseInstrInfo (const ARMSubtarget &STI) | |

| void | expandLoadStackGuardBase (MachineBasicBlock::iterator MI, unsigned LoadImmOpc, unsigned LoadOpc) const |

| bool | getRegSequenceLikeInputs (const MachineInstr &MI, unsigned DefIdx, SmallVectorImpl< RegSubRegPairAndIdx > &InputRegs) const override |

Build the equivalent inputs of a REG_SEQUENCE for the given MI and DefIdx. More... | |

| bool | getExtractSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPairAndIdx &InputReg) const override |

Build the equivalent inputs of a EXTRACT_SUBREG for the given MI and DefIdx. More... | |

| bool | getInsertSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPair &BaseReg, RegSubRegPairAndIdx &InsertedReg) const override |

Build the equivalent inputs of a INSERT_SUBREG for the given MI and DefIdx. More... | |

| MachineInstr * | commuteInstructionImpl (MachineInstr &MI, bool NewMI, unsigned OpIdx1, unsigned OpIdx2) const override |

| Commutes the operands in the given instruction. More... | |

| bool | isCopyInstrImpl (const MachineInstr &MI, const MachineOperand *&Source, const MachineOperand *&Destination) const override |

| If the specific machine instruction is a instruction that moves/copies value from one register to another register return true along with machine operand and machine operand. More... | |

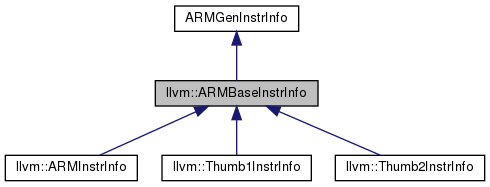

Detailed Description

Definition at line 36 of file ARMBaseInstrInfo.h.

Constructor & Destructor Documentation

◆ ARMBaseInstrInfo()

|

explicitprotected |

Definition at line 110 of file ARMBaseInstrInfo.cpp.

References llvm::array_lengthof(), llvm::SmallSet< T, N, C >::insert(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::insert(), llvm_unreachable, and ARM_MLxEntry::MLxOpc.

Member Function Documentation

◆ AddDReg()

| const MachineInstrBuilder & ARMBaseInstrInfo::AddDReg | ( | MachineInstrBuilder & | MIB, |

| unsigned | Reg, | ||

| unsigned | SubIdx, | ||

| unsigned | State, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 962 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MCRegisterInfo::getSubReg(), llvm::TargetRegisterInfo::isPhysicalRegister(), and storeRegToStackSlot().

Referenced by getPredicate(), llvm::Thumb2InstrInfo::loadRegFromStackSlot(), loadRegFromStackSlot(), llvm::Thumb2InstrInfo::storeRegToStackSlot(), and storeRegToStackSlot().

◆ analyzeBranch()

|

override |

Definition at line 312 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineBasicBlock::begin(), llvm::SmallVectorImpl< T >::clear(), llvm::SmallVectorBase::empty(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), I, llvm::isCondBranchOpcode(), llvm::isIndirectBranchOpcode(), llvm::isJumpTableBranchOpcode(), isPredicated(), llvm::isUncondBranchOpcode(), and llvm::SmallVectorTemplateBase< T >::push_back().

Referenced by getSubtarget(), and registerDefinedBetween().

◆ analyzeCompare()

|

override |

analyzeCompare - For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue.

Return true if the comparison instruction can be analyzed.

Definition at line 2531 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

Referenced by isProfitableToDupForIfCvt(), and shouldSink().

◆ analyzeSelect()

|

override |

Definition at line 2079 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::SmallVectorTemplateBase< T >::push_back().

Referenced by isProfitableToDupForIfCvt().

◆ areLoadsFromSameBasePtr()

|

override |

areLoadsFromSameBasePtr - This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address.

It should only return true if the base pointers are the same and the only differences between the two addresses is the offset. It also returns the offsets by reference.

It should only return true if the base pointers are the same and the only differences between the two addresses is the offset. It also returns the offsets by reference.

FIXME: remove this in favor of the MachineInstr interface once pre-RA-sched is permanently disabled.

Definition at line 1737 of file ARMBaseInstrInfo.cpp.

References llvm::SDNode::getMachineOpcode(), llvm::SDNode::getOperand(), and llvm::SDNode::isMachineOpcode().

Referenced by getPredicate().

◆ breakPartialRegDependency()

|

override |

Definition at line 4955 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstr::addRegisterKilled(), llvm::ARMCC::AL, assert(), llvm::BuildMI(), contains(), llvm::MachineInstr::definesRegister(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MCRegisterInfo::isSuperRegister(), MI, llvm::predOps(), and Reg.

Referenced by isProfitableToDupForIfCvt().

◆ canCauseFpMLxStall()

canCauseFpMLxStall - Return true if an instruction of the specified opcode will cause stalls when scheduled after (within 4-cycle window) a fp MLA / MLS instruction.

Definition at line 430 of file ARMBaseInstrInfo.h.

References llvm::SmallSet< T, N, C >::count(), and isSwiftFastImmShift().

Referenced by llvm::ARMHazardRecognizer::getHazardType().

◆ commuteInstructionImpl()

|

overrideprotected |

Commutes the operands in the given instruction.

The commutable operands are specified by their indices OpIdx1 and OpIdx2.

Do not call this method for a non-commutable instruction or for non-commutable pair of operand indices OpIdx1 and OpIdx2. Even though the instruction is commutable, the method may still fail to commute the operands, null pointer is returned in such cases.

Definition at line 2015 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::TargetInstrInfo::commuteInstructionImpl(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::getInstrPredicate(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::ARMCC::getOppositeCondition().

◆ convertToThreeAddress()

|

override |

Definition at line 142 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMII::AddrMode2, llvm::ARMII::AddrMode3, llvm::ARMII::AddrModeMask, llvm::LiveVariables::addVirtualRegisterDead(), llvm::LiveVariables::addVirtualRegisterKilled(), llvm::BuildMI(), llvm::condCodeOp(), EnableARM3Addr, llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::ARM_AM::getAM3Offset(), llvm::ARM_AM::getAM3Op(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::ARM_AM::getSOImmVal(), llvm::ARM_AM::getSORegOpc(), getUnindexedOpcode(), llvm::LiveVariables::getVarInfo(), llvm::ARMII::IndexModeMask, llvm::ARMII::IndexModePost, llvm::ARMII::IndexModePre, llvm::ARMII::IndexModeShift, llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isKill(), isLoad(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::LiveVariables::VarInfo::Kills, llvm_unreachable, llvm::MachineInstr::mayStore(), llvm::predOps(), llvm::MachineInstr::readsRegister(), Reg, llvm::LiveVariables::VarInfo::removeKill(), llvm::MachineOperand::setIsDead(), llvm::ARM_AM::sub, llvm::MCInstrDesc::TSFlags, and VI.

◆ copyFromCPSR()

| void ARMBaseInstrInfo::copyFromCPSR | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | DestReg, | ||

| bool | KillSrc, | ||

| const ARMSubtarget & | Subtarget | ||

| ) | const |

Definition at line 769 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::getKillRegState(), llvm::RegState::Implicit, llvm::ARMSubtarget::isMClass(), llvm::ARMSubtarget::isThumb(), and llvm::predOps().

Referenced by copyPhysReg(), and getPredicate().

◆ copyPhysReg()

|

override |

Definition at line 809 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::ARMCC::AL, assert(), llvm::BuildMI(), llvm::condCodeOp(), contains(), copyFromCPSR(), copyToCPSR(), llvm::SmallSet< T, N, C >::count(), llvm::getKillRegState(), getRegisterInfo(), llvm::MCRegisterInfo::getSubReg(), llvm::SmallSet< T, N, C >::insert(), llvm::predOps(), llvm::TargetRegisterInfo::regsOverlap(), TRI, and llvm::ARMISD::VMOVSR.

Referenced by llvm::Thumb2InstrInfo::copyPhysReg(), and getPredicate().

◆ copyToCPSR()

| void ARMBaseInstrInfo::copyToCPSR | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | SrcReg, | ||

| bool | KillSrc, | ||

| const ARMSubtarget & | Subtarget | ||

| ) | const |

Definition at line 789 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::RegState::Define, llvm::getKillRegState(), llvm::RegState::Implicit, llvm::ARMSubtarget::isMClass(), llvm::ARMSubtarget::isThumb(), and llvm::predOps().

Referenced by copyPhysReg(), and getPredicate().

◆ CreateTargetHazardRecognizer()

|

override |

Definition at line 124 of file ARMBaseInstrInfo.cpp.

References llvm::TargetInstrInfo::CreateTargetHazardRecognizer(), and CreateTargetPostRAHazardRecognizer().

Referenced by getSubtarget().

◆ CreateTargetPostRAHazardRecognizer()

|

override |

Definition at line 135 of file ARMBaseInstrInfo.cpp.

References llvm::TargetInstrInfo::CreateTargetPostRAHazardRecognizer(), llvm::ARMSubtarget::hasVFP2(), and llvm::ARMSubtarget::isThumb2().

Referenced by CreateTargetHazardRecognizer(), and getSubtarget().

◆ decomposeMachineOperandsTargetFlags()

|

override |

Definition at line 5083 of file ARMBaseInstrInfo.cpp.

References llvm::BitmaskEnumDetail::Mask(), and llvm::ARMII::MO_OPTION_MASK.

Referenced by isProfitableToDupForIfCvt().

◆ DefinesPredicate()

|

override |

Definition at line 546 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::clobbersPhysReg(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::isRegMask().

Referenced by getPredicate().

◆ duplicate()

|

override |

Definition at line 1618 of file ARMBaseInstrInfo.cpp.

References llvm::TargetInstrInfo::duplicate(), duplicateCPV(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineBasicBlock::getParent(), and I.

Referenced by getPredicate().

◆ expandLoadStackGuardBase()

|

protected |

Definition at line 4525 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addGlobalAddress(), llvm::ARMCC::AL, assert(), llvm::BuildMI(), llvm::MachinePointerInfo::getGOT(), llvm::RegState::Kill, llvm::ARMII::MO_NONLAZY, llvm::MachineMemOperand::MODereferenceable, llvm::MachineMemOperand::MOInvariant, llvm::MachineMemOperand::MOLoad, and llvm::predOps().

Referenced by llvm::ARMInstrInfo::getUnindexedOpcode(), llvm::Thumb1InstrInfo::loadRegFromStackSlot(), and llvm::Thumb2InstrInfo::loadRegFromStackSlot().

◆ expandPostRAPseudo()

|

override |

Definition at line 1465 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::addRegisterKilled(), llvm::ARMCC::AL, assert(), contains(), llvm::dbgs(), llvm::MachineInstr::definesRegister(), llvm::MachineBasicBlock::erase(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), getSubtarget(), llvm::RegState::Implicit, llvm::MachineInstr::isCopy(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isKill(), LLVM_DEBUG, llvm::ARMISD::MEMCPY, MI, llvm::predOps(), llvm::MachineInstr::readsRegister(), llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setIsUndef(), llvm::MachineOperand::setReg(), and TRI.

Referenced by getPredicate().

◆ FoldImmediate()

|

override |

FoldImmediate - 'Reg' is known to be defined by a move immediate instruction, try to fold the immediate into the use instruction.

Definition at line 2989 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::MachineOperand::ChangeToImmediate(), llvm::condCodeOp(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::getKillRegState(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::ARM_AM::getSOImmTwoPartFirst(), llvm::ARM_AM::getSOImmTwoPartSecond(), llvm::ARM_AM::getT2SOImmTwoPartFirst(), llvm::ARM_AM::getT2SOImmTwoPartSecond(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), llvm::MCInstrDesc::hasOptionalDef(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isKill(), llvm::ARM_AM::isSOImmTwoPartVal(), llvm::ARM_AM::isT2SOImmTwoPartVal(), llvm::predOps(), Reg, llvm::MachineInstr::setDesc(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setReg(), and UseMI.

Referenced by isProfitableToDupForIfCvt().

◆ getExecutionDomain()

|

override |

VFP/NEON execution domains.

Definition at line 4596 of file ARMBaseInstrInfo.cpp.

References llvm::ARMII::DomainMask, llvm::ARMII::DomainNEON, llvm::ARMII::DomainNEONA8, llvm::ARMII::DomainVFP, ExeGeneric, ExeNEON, ExeVFP, llvm::MachineInstr::getDesc(), llvm::MachineInstr::getOpcode(), isPredicated(), llvm::MCInstrDesc::TSFlags, and llvm::ARMISD::VMOVSR.

Referenced by isProfitableToDupForIfCvt().

◆ getExtractSubregLikeInputs()

|

overrideprotected |

Build the equivalent inputs of a EXTRACT_SUBREG for the given MI and DefIdx.

[out] InputReg of the equivalent EXTRACT_SUBREG. E.g., EXTRACT_SUBREG %1:sub1, sub0, sub1 would produce:

- %1:sub1, sub0

- Returns

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition

- MI.isExtractSubregLike().

Definition at line 5034 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isExtractSubregLike(), llvm::MachineOperand::isUndef(), llvm_unreachable, llvm::TargetInstrInfo::RegSubRegPair::Reg, llvm::TargetInstrInfo::RegSubRegPairAndIdx::SubIdx, llvm::TargetInstrInfo::RegSubRegPair::SubReg, and llvm::ARMISD::VMOVRRD.

◆ getFramePred()

|

inline |

Returns predicate register associated with the given frame instruction.

Definition at line 439 of file ARMBaseInstrInfo.h.

References assert(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

Referenced by llvm::ARMFrameLowering::determineCalleeSaves().

◆ getInsertSubregLikeInputs()

|

overrideprotected |

Build the equivalent inputs of a INSERT_SUBREG for the given MI and DefIdx.

[out] BaseReg and [out] InsertedReg contain the equivalent inputs of INSERT_SUBREG. E.g., INSERT_SUBREG %0:sub0, %1:sub1, sub3 would produce:

- BaseReg: %0:sub0

- InsertedReg: %1:sub1, sub3

- Returns

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition

- MI.isInsertSubregLike().

Definition at line 5057 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isInsertSubregLike(), llvm::MachineOperand::isUndef(), llvm_unreachable, llvm::TargetInstrInfo::RegSubRegPair::Reg, llvm::TargetInstrInfo::RegSubRegPairAndIdx::SubIdx, and llvm::TargetInstrInfo::RegSubRegPair::SubReg.

◆ getInstSizeInBytes()

|

override |

GetInstSize - Returns the size of the specified MachineInstr.

GetInstSize - Return the size of the specified MachineInstr.

Definition at line 701 of file ARMBaseInstrInfo.cpp.

References llvm::alignTo(), assert(), E, llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MachineFunction::getInfo(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::TargetMachine::getMCAsmInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MCInstrDesc::getSize(), llvm::MachineOperand::getSymbolName(), llvm::MachineFunction::getTarget(), I, llvm::ISD::INLINEASM, llvm::MachineBasicBlock::instr_end(), llvm::ARMFunctionInfo::isThumbFunction(), MI, and Size.

Referenced by llvm::computeBlockSize(), GetFunctionSizeInBytes(), getPredicate(), getUnconditionalBrDisp(), and registerDefinedBetween().

◆ getLDMVariableDefsSize()

| unsigned ARMBaseInstrInfo::getLDMVariableDefsSize | ( | const MachineInstr & | MI | ) | const |

Definition at line 3581 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MCInstrDesc::getOpcode(), llvm::InstrItineraryData::getOperandCycle(), llvm::InstrItineraryData::getOperandLatency(), getOperandLatency(), llvm::MCInstrDesc::getSchedClass(), and llvm::InstrItineraryData::hasPipelineForwarding().

Referenced by getPredicate().

◆ getNumLDMAddresses()

| unsigned ARMBaseInstrInfo::getNumLDMAddresses | ( | const MachineInstr & | MI | ) | const |

Get the number of addresses by LDM or VLDM or zero for unknown.

Definition at line 3368 of file ARMBaseInstrInfo.cpp.

References E, I, llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), and Size.

Referenced by isProfitableToDupForIfCvt().

◆ getNumMicroOps()

|

override |

Definition at line 3417 of file ARMBaseInstrInfo.cpp.

References llvm::ARMSubtarget::DoubleIssue, llvm::ARMSubtarget::DoubleIssueCheckUnalignedAccess, getAlignment(), llvm::MachineInstr::getDesc(), llvm::InstrItineraryData::getNumMicroOps(), getNumMicroOpsSingleIssuePlusExtras(), getNumMicroOpsSwiftLdSt(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MCInstrDesc::getOpcode(), llvm::MachineInstr::getOpcode(), llvm::InstrItineraryData::getOperandCycle(), llvm::MCInstrDesc::getSchedClass(), llvm::MachineInstr::hasOneMemOperand(), llvm::InstrItineraryData::isEmpty(), llvm_unreachable, llvm::MCInstrDesc::mayLoad(), llvm::MCInstrDesc::mayStore(), llvm::MachineInstr::memoperands_begin(), llvm::ARMSubtarget::SingleIssue, and llvm::ARMSubtarget::SingleIssuePlusExtras.

Referenced by getOperandLatency(), and isProfitableToDupForIfCvt().

◆ getOperandLatency() [1/2]

|

override |

Definition at line 4036 of file ARMBaseInstrInfo.cpp.

References adjustDefLatency(), DefMI, llvm::ARMISD::FMSTAT, getAlignment(), getBundledDefMI(), getBundledUseMI(), llvm::MachineInstr::getDesc(), llvm::MachineFunction::getFunction(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::Function::hasFnAttribute(), llvm::MachineInstr::hasOneMemOperand(), llvm::MachineInstr::isBranch(), llvm::MachineInstr::isBundle(), llvm::MachineInstr::isCopyLike(), llvm::InstrItineraryData::isEmpty(), llvm::MachineOperand::isImplicit(), llvm::MachineInstr::isImplicitDef(), llvm::MachineInstr::isInsertSubreg(), llvm::MachineInstr::isRegSequence(), llvm::Latency, llvm::MachineInstr::memoperands_begin(), llvm::Attribute::OptimizeForSize, Reg, and UseMI.

Referenced by getLDMVariableDefsSize(), getOperandLatency(), and isProfitableToDupForIfCvt().

◆ getOperandLatency() [2/2]

|

override |

Definition at line 4133 of file ARMBaseInstrInfo.cpp.

References adjustDefLatency(), llvm::dyn_cast(), E, getAlignment(), llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::MachineInstr::getDesc(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::SDNode::getMachineOpcode(), llvm::InstrItineraryData::getNumMicroOps(), getNumMicroOps(), llvm::MCInstrDesc::getOpcode(), llvm::SDNode::getOperand(), llvm::InstrItineraryData::getOperandCycle(), getOperandLatency(), llvm::MachineInstr::getParent(), llvm::MCInstrDesc::getSchedClass(), llvm::InstrItineraryData::getStageLatency(), llvm::MCInstrDesc::hasImplicitDefOfPhysReg(), llvm::MachineInstr::hasOneMemOperand(), I, llvm::MachineBasicBlock::instr_end(), llvm::MachineInstr::isBundle(), llvm::MCInstrDesc::isCall(), llvm::MachineInstr::isCopyLike(), llvm::InstrItineraryData::isEmpty(), llvm::MachineInstr::isImplicitDef(), llvm::MachineInstr::isInsertSubreg(), llvm::SDNode::isMachineOpcode(), llvm::MachineInstr::isRegSequence(), llvm::Latency, llvm::ARM_AM::lsl, llvm::ARM_AM::lsr, llvm::MCInstrDesc::mayLoad(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::memoperands_begin(), llvm::MachineSDNode::memoperands_begin(), llvm::MachineSDNode::memoperands_empty(), llvm::MCInstrDesc::Opcode, and Threshold.

◆ getPartialRegUpdateClearance()

|

override |

Definition at line 4894 of file ARMBaseInstrInfo.cpp.

References assert(), contains(), llvm::MachineInstr::definesRegister(), llvm::MachineInstr::findRegisterUseOperandIdx(), llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineOperand::readsReg(), llvm::MachineInstr::readsVirtualRegister(), and llvm::ARMISD::VMOVSR.

Referenced by isProfitableToDupForIfCvt().

◆ getPredicate()

|

inline |

Definition at line 151 of file ARMBaseInstrInfo.h.

References AddDReg(), llvm::ARMCC::AL, areLoadsFromSameBasePtr(), copyFromCPSR(), copyPhysReg(), copyToCPSR(), DefinesPredicate(), duplicate(), expandPostRAPseudo(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::ISD::FrameIndex, llvm::MachineOperand::getImm(), getInstSizeInBytes(), getLDMVariableDefsSize(), llvm::MachineInstr::getOperand(), I, isAddrMode3OpImm(), isAddrMode3OpMinusReg(), isAm2ScaledReg(), isCPSRDefined(), isLDMBaseRegInList(), isLdstScaledReg(), isLdstScaledRegNotPlusLsl2(), isLdstSoMinusReg(), isLoadFromStackSlot(), isLoadFromStackSlotPostFE(), isPredicable(), isProfitableToIfCvt(), isSchedulingBoundary(), isStoreToStackSlot(), isStoreToStackSlotPostFE(), loadRegFromStackSlot(), MRI, PredicateInstruction(), produceSameValue(), Reg, reMaterialize(), shouldScheduleLoadsNear(), shouldSink(), storeRegToStackSlot(), SubsumesPredicate(), and TRI.

◆ getRegisterInfo()

|

pure virtual |

Implemented in llvm::Thumb2InstrInfo, llvm::ARMInstrInfo, and llvm::Thumb1InstrInfo.

Referenced by addExclusiveRegPair(), copyPhysReg(), expandPostRAPseudo(), llvm::ARMHazardRecognizer::getHazardType(), getOperandLatency(), isLoadFromStackSlotPostFE(), loadRegFromStackSlot(), optimizeCompareInstr(), setExecutionDomain(), and storeRegToStackSlot().

◆ getRegSequenceLikeInputs()

|

overrideprotected |

Build the equivalent inputs of a REG_SEQUENCE for the given MI and DefIdx.

[out] InputRegs of the equivalent REG_SEQUENCE. Each element of the list is modeled as <Reg:SubReg, SubIdx>. E.g., REG_SEQUENCE %1:sub1, sub0, %2, sub1 would produce two elements:

- %1:sub1, sub0

- %2<:0>, sub1

- Returns

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition

- MI.isRegSequenceLike().

Definition at line 5007 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isRegSequenceLike(), llvm::MachineOperand::isUndef(), llvm_unreachable, llvm::SmallVectorTemplateBase< T >::push_back(), and llvm::ARMISD::VMOVDRR.

◆ getSerializableBitmaskMachineOperandTargetFlags()

|

override |

Definition at line 5098 of file ARMBaseInstrInfo.cpp.

References llvm::makeArrayRef(), llvm::AArch64II::MO_COFFSTUB, llvm::AArch64II::MO_DLLIMPORT, llvm::AArch64II::MO_GOT, llvm::ARMII::MO_NONLAZY, llvm::ARMII::MO_SBREL, and llvm::ARMII::MO_SECREL.

Referenced by isProfitableToDupForIfCvt().

◆ getSerializableDirectMachineOperandTargetFlags()

|

override |

Definition at line 5089 of file ARMBaseInstrInfo.cpp.

References llvm::makeArrayRef(), llvm::ARMII::MO_HI16, and llvm::ARMII::MO_LO16.

Referenced by isProfitableToDupForIfCvt().

◆ getSubtarget()

|

inline |

Definition at line 123 of file ARMBaseInstrInfo.h.

References analyzeBranch(), CreateTargetHazardRecognizer(), CreateTargetPostRAHazardRecognizer(), insertBranch(), isPredicated(), removeBranch(), and reverseBranchCondition().

Referenced by expandPostRAPseudo(), llvm::ARMHazardRecognizer::getHazardType(), isPredicable(), selectMergeValues(), and selectUnmergeValues().

◆ getUnindexedOpcode()

Implemented in llvm::Thumb2InstrInfo, llvm::ARMInstrInfo, and llvm::Thumb1InstrInfo.

Referenced by convertToThreeAddress().

◆ hasNOP()

| bool ARMBaseInstrInfo::hasNOP | ( | ) | const |

Definition at line 4989 of file ARMBaseInstrInfo.cpp.

Referenced by llvm::ARMInstrInfo::getNoop().

◆ insertBranch()

|

override |

Definition at line 429 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::ARMCC::AL, assert(), B, llvm::BuildMI(), llvm::ArrayRef< T >::empty(), llvm::MachineFunction::getInfo(), llvm::MachineBasicBlock::getParent(), isThumb(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::ARMFunctionInfo::isThumbFunction(), llvm::predOps(), reverseBranchCondition(), and llvm::ArrayRef< T >::size().

Referenced by getSubtarget().

◆ isAddrMode3OpImm()

| bool ARMBaseInstrInfo::isAddrMode3OpImm | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 568 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

Referenced by getPredicate().

◆ isAddrMode3OpMinusReg()

| bool ARMBaseInstrInfo::isAddrMode3OpMinusReg | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 576 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::ARM_AM::getAM3Op(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isReg(), and llvm::ARM_AM::sub.

Referenced by getPredicate().

◆ isAm2ScaledReg()

| bool ARMBaseInstrInfo::isAm2ScaledReg | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 617 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::getAM2ShiftOpc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), and llvm::ARM_AM::no_shift.

Referenced by getPredicate().

◆ isCopyInstrImpl()

|

overrideprotected |

If the specific machine instruction is a instruction that moves/copies value from one register to another register return true along with machine operand and machine operand.

Definition at line 942 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), and llvm::MachineInstr::isMoveReg().

◆ isCPSRDefined()

|

static |

Definition at line 561 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::operands().

Referenced by getPredicate(), and isEligibleForITBlock().

◆ isFpMLxInstruction() [1/2]

isFpMLxInstruction - Return true if the specified opcode is a fp MLA / MLS instruction.

Definition at line 416 of file ARMBaseInstrInfo.h.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::count().

Referenced by llvm::ARMHazardRecognizer::getHazardType().

◆ isFpMLxInstruction() [2/2]

| bool ARMBaseInstrInfo::isFpMLxInstruction | ( | unsigned | Opcode, |

| unsigned & | MulOpc, | ||

| unsigned & | AddSubOpc, | ||

| bool & | NegAcc, | ||

| bool & | HasLane | ||

| ) | const |

isFpMLxInstruction - This version also returns the multiply opcode and the addition / subtraction opcode to expand to.

Return true for 'HasLane' for the MLX instructions with an extra lane operand.

Definition at line 4560 of file ARMBaseInstrInfo.cpp.

References ARM_MLxEntry::AddSubOpc, llvm::DenseMapBase< DenseMap< KeyT, ValueT, KeyInfoT, BucketT >, KeyT, ValueT, KeyInfoT, BucketT >::end(), ARM_MLxEntry::HasLane, I, ARM_MLxEntry::MulOpc, and ARM_MLxEntry::NegAcc.

◆ isLDMBaseRegInList()

| bool ARMBaseInstrInfo::isLDMBaseRegInList | ( | const MachineInstr & | MI | ) | const |

Definition at line 3571 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

Referenced by getPredicate().

◆ isLdstScaledReg()

| bool ARMBaseInstrInfo::isLdstScaledReg | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 588 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::getAM2ShiftOpc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), and llvm::ARM_AM::no_shift.

Referenced by getPredicate().

◆ isLdstScaledRegNotPlusLsl2()

| bool ARMBaseInstrInfo::isLdstScaledRegNotPlusLsl2 | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 596 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::add, llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), llvm::ARM_AM::lsl, and llvm::ARM_AM::no_shift.

Referenced by getPredicate().

◆ isLdstSoMinusReg()

| bool ARMBaseInstrInfo::isLdstSoMinusReg | ( | const MachineInstr & | MI, |

| unsigned | Op | ||

| ) | const |

Definition at line 610 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::getAM2Op(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), and llvm::ARM_AM::sub.

Referenced by getPredicate().

◆ isLoadFromStackSlot()

|

override |

Definition at line 1348 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MachineOperand::isReg().

Referenced by getPredicate().

◆ isLoadFromStackSlotPostFE()

|

override |

Definition at line 1397 of file ARMBaseInstrInfo.cpp.

References llvm::ARM_AM::add, llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::RegState::Define, llvm::MachineBasicBlock::erase(), llvm::SmallVectorTemplateCommon< T >::front(), llvm::MCRegisterInfo::getEncodingValue(), llvm::MachineMemOperand::getPseudoValue(), getRegisterInfo(), I, llvm::RegState::Kill, llvm::MachineInstr::mayLoad(), llvm::predOps(), llvm::SmallVectorTemplateBase< T >::push_back(), Reg, llvm::sort(), TII, and TRI.

Referenced by getPredicate().

◆ isPredicable()

|

override |

isPredicable - Return true if the specified instruction can be predicated.

By default, this returns true for every instruction with a PredicateOperand.

Definition at line 655 of file ARMBaseInstrInfo.cpp.

References llvm::ARMII::DomainMask, llvm::ARMII::DomainNEON, llvm::MachineInstr::getDesc(), llvm::MachineFunction::getInfo(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), getSubtarget(), llvm::MachineInstr::isBundle(), isEligibleForITBlock(), llvm::MachineInstr::isPredicable(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::isV8EligibleForIT(), llvm::ARMSubtarget::restrictIT(), and llvm::MCInstrDesc::TSFlags.

Referenced by getPredicate().

◆ isPredicated()

|

override |

Definition at line 483 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, E, llvm::MachineInstr::findFirstPredOperandIdx(), llvm::MachineOperand::getImm(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), I, llvm::MachineBasicBlock::instr_end(), and llvm::MachineInstr::isBundle().

Referenced by analyzeBranch(), getExecutionDomain(), getSubtarget(), optimizeCompareInstr(), setExecutionDomain(), and shouldSink().

◆ isProfitableToDupForIfCvt()

|

inlineoverride |

Definition at line 275 of file ARMBaseInstrInfo.h.

References analyzeCompare(), analyzeSelect(), breakPartialRegDependency(), decomposeMachineOperandsTargetFlags(), DefMI, FoldImmediate(), getExecutionDomain(), getNumLDMAddresses(), getNumMicroOps(), getOperandLatency(), getPartialRegUpdateClearance(), getSerializableBitmaskMachineOperandTargetFlags(), getSerializableDirectMachineOperandTargetFlags(), isProfitableToUnpredicate(), optimizeCompareInstr(), optimizeSelect(), setExecutionDomain(), and UseMI.

◆ isProfitableToIfCvt() [1/2]

|

override |

Definition at line 1892 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::MachineBasicBlock::begin(), llvm::MachineBasicBlock::empty(), llvm::MachineFunction::getFunction(), llvm::getInstrPredicate(), llvm::MachineInstr::getOpcode(), llvm::MachineBasicBlock::getParent(), llvm::isARMLowRegister(), llvm::Function::optForSize(), P, llvm::MachineBasicBlock::pred_begin(), llvm::MachineBasicBlock::rbegin(), and Reg.

Referenced by getPredicate(), and isSchedulingBoundary().

◆ isProfitableToIfCvt() [2/2]

|

override |

Definition at line 1927 of file ARMBaseInstrInfo.cpp.

References llvm::BranchProbability::getCompl(), and llvm::BranchProbability::scale().

◆ isProfitableToUnpredicate()

|

override |

Definition at line 1982 of file ARMBaseInstrInfo.cpp.

Referenced by isProfitableToDupForIfCvt().

◆ isSchedulingBoundary()

|

override |

Definition at line 1848 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::definesRegister(), llvm::MachineBasicBlock::end(), I, llvm::MachineInstr::isCall(), llvm::MachineInstr::isDebugInstr(), llvm::MachineInstr::isPosition(), isProfitableToIfCvt(), llvm::MachineInstr::isTerminator(), and MI.

Referenced by getPredicate().

◆ isStoreToStackSlot()

|

override |

Definition at line 1134 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MachineOperand::isReg().

Referenced by getPredicate().

◆ isStoreToStackSlotPostFE()

|

override |

Definition at line 1177 of file ARMBaseInstrInfo.cpp.

References llvm::SmallVectorTemplateCommon< T >::front(), llvm::MachineMemOperand::getPseudoValue(), loadRegFromStackSlot(), and llvm::MachineInstr::mayStore().

Referenced by getPredicate().

◆ isSwiftFastImmShift()

| bool ARMBaseInstrInfo::isSwiftFastImmShift | ( | const MachineInstr * | MI | ) | const |

Returns true if the instruction has a shift by immediate that can be executed in one cycle less.

Definition at line 4993 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::ARM_AM::getSORegOffset(), llvm::ARM_AM::getSORegShOp(), llvm::ARM_AM::lsl, and llvm::ARM_AM::lsr.

Referenced by canCauseFpMLxStall().

◆ loadRegFromStackSlot()

|

override |

Definition at line 1190 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, llvm::BuildMI(), llvm::RegState::DefineNoRead, llvm::MachineBasicBlock::end(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), getRegisterInfo(), llvm::TargetRegisterInfo::getSpillSize(), llvm::RegState::ImplicitDefine, llvm::TargetRegisterInfo::isPhysicalRegister(), llvm_unreachable, llvm::MachineMemOperand::MOLoad, and llvm::predOps().

Referenced by getPredicate(), isStoreToStackSlotPostFE(), and llvm::Thumb2InstrInfo::loadRegFromStackSlot().

◆ optimizeCompareInstr()

|

override |

optimizeCompareInstr - Convert the instruction to set the zero flag so that we can remove a "comparison with zero"; Remove a redundant CMP instruction if the flags can be updated in the same way by an earlier instruction such as SUB.

optimizeCompareInstr - Convert the instruction supplying the argument to the comparison into one that sets the zero bit in the flags register; Remove a redundant Compare instruction if an earlier instruction can set the flags in the same way as Compare.

E.g. SUBrr(r1,r2) and CMPrr(r1,r2). We also handle the case where two operands are swapped: SUBrr(r1,r2) and CMPrr(r2,r1), by updating the condition code of instructions which use the flags.

Definition at line 2715 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, assert(), B, llvm::MachineBasicBlock::begin(), llvm::MachineInstr::clearRegisterDeads(), llvm::MachineOperand::clobbersPhysReg(), E, llvm::MachineBasicBlock::end(), llvm::ARMCC::EQ, llvm::MachineInstr::eraseFromParent(), first, llvm::ARMCC::GE, getCmpToAddCondition(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), getSwappedCondition(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::ARMCC::GT, llvm::ARMCC::HI, llvm::ARMCC::HS, I, llvm::MachineBasicBlock::insert(), llvm::MachineOperand::isDef(), isOptimizeCompareCandidate(), isPredicated(), isRedundantFlagInstr(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), isSuitableForMask(), llvm::ARMCC::LE, llvm::ARMCC::LO, llvm::ARMCC::LS, llvm::ARMCC::LT, llvm::ARMCC::MI, MI, llvm::MachineInstr::modifiesRegister(), llvm::ARMCC::NE, llvm::ARMCC::PL, llvm::SmallVectorTemplateBase< T >::push_back(), llvm::MachineInstr::readsRegister(), llvm::MachineInstr::removeFromParent(), llvm::MachineOperand::setIsDef(), llvm::MachineOperand::setReg(), SI, llvm::SmallVectorBase::size(), llvm::MachineBasicBlock::succ_begin(), llvm::MachineBasicBlock::succ_end(), TRI, llvm::MachineRegisterInfo::use_instr_begin(), llvm::MachineRegisterInfo::use_instr_end(), llvm::ARMCC::VC, and llvm::ARMCC::VS.

Referenced by isProfitableToDupForIfCvt().

◆ optimizeSelect()

|

override |

Definition at line 2101 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), assert(), llvm::BuildMI(), canFoldIntoMOVCC(), llvm::MachineInstr::clearKillInfo(), llvm::condCodeOp(), llvm::MachineRegisterInfo::constrainRegClass(), DefMI, llvm::SmallPtrSetImpl< PtrType >::erase(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::ARMCC::getOppositeCondition(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineInstr::hasOptionalDef(), llvm::SmallPtrSetImpl< PtrType >::insert(), MI, MRI, llvm::MachineOperand::setImplicit(), and llvm::MachineInstr::tieOperands().

Referenced by isProfitableToDupForIfCvt().

◆ PredicateInstruction()

|

override |

Definition at line 499 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::findFirstPredOperandIdx(), llvm::getMatchingCondBranchOpcode(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), getReg(), llvm::isUncondBranchOpcode(), MI, llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), and llvm::MachineOperand::setReg().

Referenced by getPredicate().

◆ produceSameValue()

|

override |

Definition at line 1642 of file ARMBaseInstrInfo.cpp.

References llvm::MachineConstantPoolEntry::ConstVal, llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstants(), llvm::MachineOperand::getGlobal(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getNumOperands(), llvm::MachineOperand::getOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getVRegDef(), llvm::ARMConstantPoolValue::hasSameValue(), llvm::MachineInstr::IgnoreVRegDefs, llvm::MachineOperand::isIdenticalTo(), llvm::MachineInstr::isIdenticalTo(), llvm::MachineConstantPoolEntry::isMachineConstantPoolEntry(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineConstantPoolEntry::MachineCPVal, and llvm::MachineConstantPoolEntry::Val.

Referenced by getPredicate().

◆ reMaterialize()

|

override |

Definition at line 1590 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addConstantPoolIndex(), llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), llvm::MachineFunction::CloneMachineInstr(), llvm::MachineInstrBuilder::cloneMemRefs(), duplicateCPV(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineBasicBlock::insert(), llvm::MachineInstr::substituteRegister(), and TRI.

Referenced by getPredicate().

◆ removeBranch()

|

override |

Definition at line 402 of file ARMBaseInstrInfo.cpp.

References assert(), llvm::MachineBasicBlock::begin(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getLastNonDebugInstr(), I, llvm::isCondBranchOpcode(), and llvm::isUncondBranchOpcode().

Referenced by getSubtarget().

◆ reverseBranchCondition()

|

override |

Definition at line 477 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::getOppositeCondition().

Referenced by getSubtarget(), and insertBranch().

◆ setExecutionDomain()

|

override |

Definition at line 4686 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, assert(), llvm::BuildMI(), llvm::RegState::Define, ExeNEON, getCorrespondingDRegAndLane(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), getImplicitSPRUseForDPRUse(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::getUndefRegState(), llvm::RegState::Implicit, isPredicated(), llvm_unreachable, MI, llvm::predOps(), llvm::MachineInstr::readsRegister(), llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), TRI, llvm::RegState::Undef, and llvm::ARMISD::VMOVSR.

Referenced by isProfitableToDupForIfCvt().

◆ shouldScheduleLoadsNear()

|

override |

shouldScheduleLoadsNear - This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled togther.

On some targets if two loads are loading from addresses in the same cache line, it's better if they are scheduled together. This function takes two integers that represent the load offsets from the common base address. It returns true if it decides it's desirable to schedule the two loads together. "NumLoads" is the number of loads that have already been scheduled after Load1.

On some targets if two loads are loading from addresses in the same cache line, it's better if they are scheduled together. This function takes two integers that represent the load offsets from the common base address. It returns true if it decides it's desirable to schedule the two loads together. "NumLoads" is the number of loads that have already been scheduled after Load1.

FIXME: remove this in favor of the MachineInstr interface once pre-RA-sched is permanently disabled.

Definition at line 1818 of file ARMBaseInstrInfo.cpp.

References assert(), and llvm::SDNode::getMachineOpcode().

Referenced by getPredicate().

◆ shouldSink()

|

override |

Definition at line 2972 of file ARMBaseInstrInfo.cpp.

References analyzeCompare(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::getParent(), isPredicated(), isRedundantFlagInstr(), and MI.

Referenced by getPredicate().

◆ storeRegToStackSlot()

|

override |

Definition at line 974 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, llvm::BuildMI(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::getKillRegState(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), getRegisterInfo(), llvm::TargetRegisterInfo::getSpillSize(), llvm_unreachable, llvm::MachineMemOperand::MOStore, and llvm::predOps().

Referenced by AddDReg(), getPredicate(), and llvm::Thumb2InstrInfo::storeRegToStackSlot().

◆ SubsumesPredicate()

|

override |

Definition at line 520 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::ARMCC::EQ, llvm::ARMCC::GE, llvm::ARMCC::GT, llvm::ARMCC::HI, llvm::ARMCC::HS, llvm::ARMCC::LE, llvm::ARMCC::LO, llvm::ARMCC::LS, llvm::ARMCC::LT, and llvm::ArrayRef< T >::size().

Referenced by getPredicate().

The documentation for this class was generated from the following files:

- lib/Target/ARM/ARMBaseInstrInfo.h

- lib/Target/ARM/ARMBaseInstrInfo.cpp

1.8.13

1.8.13