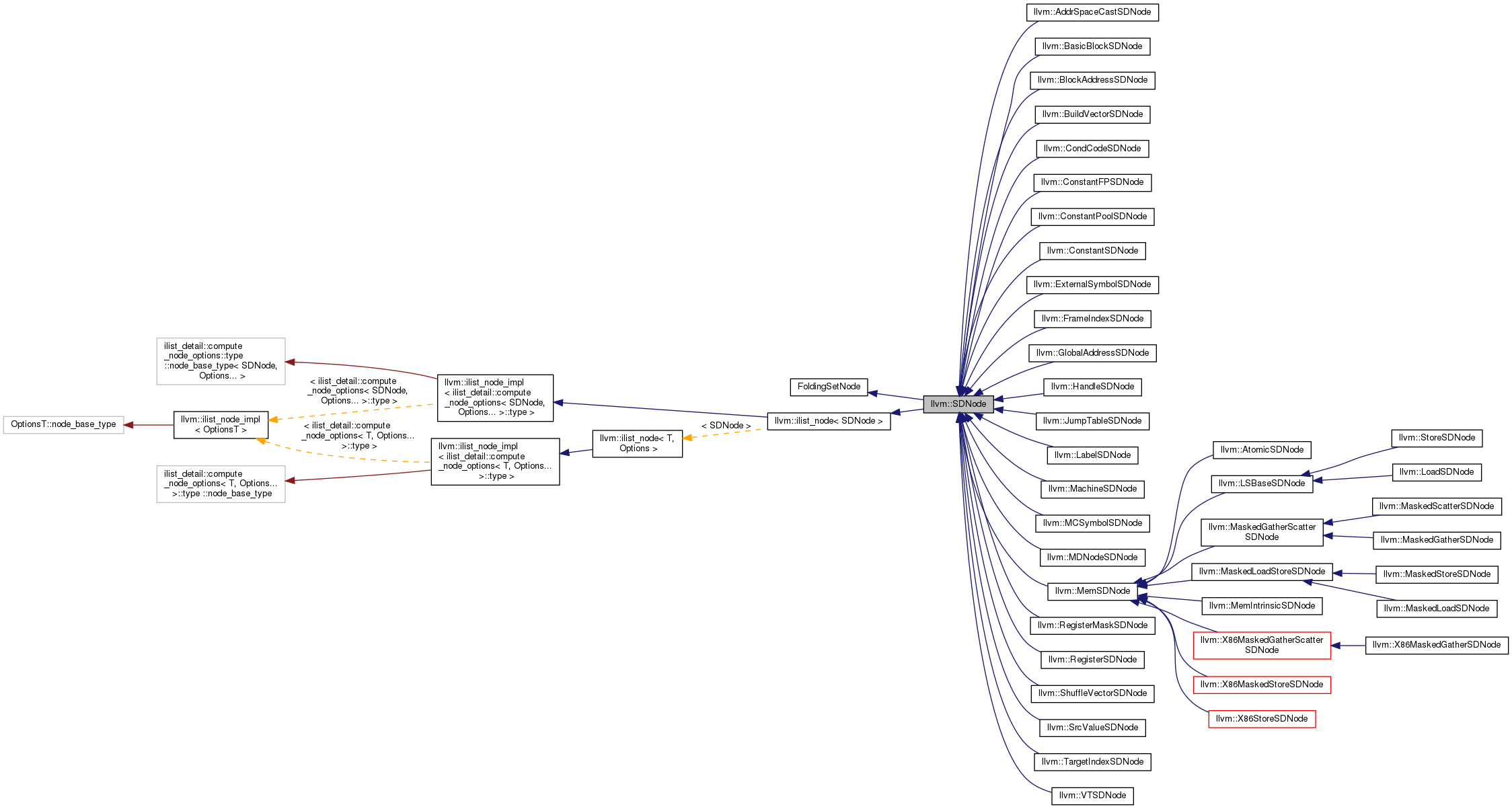

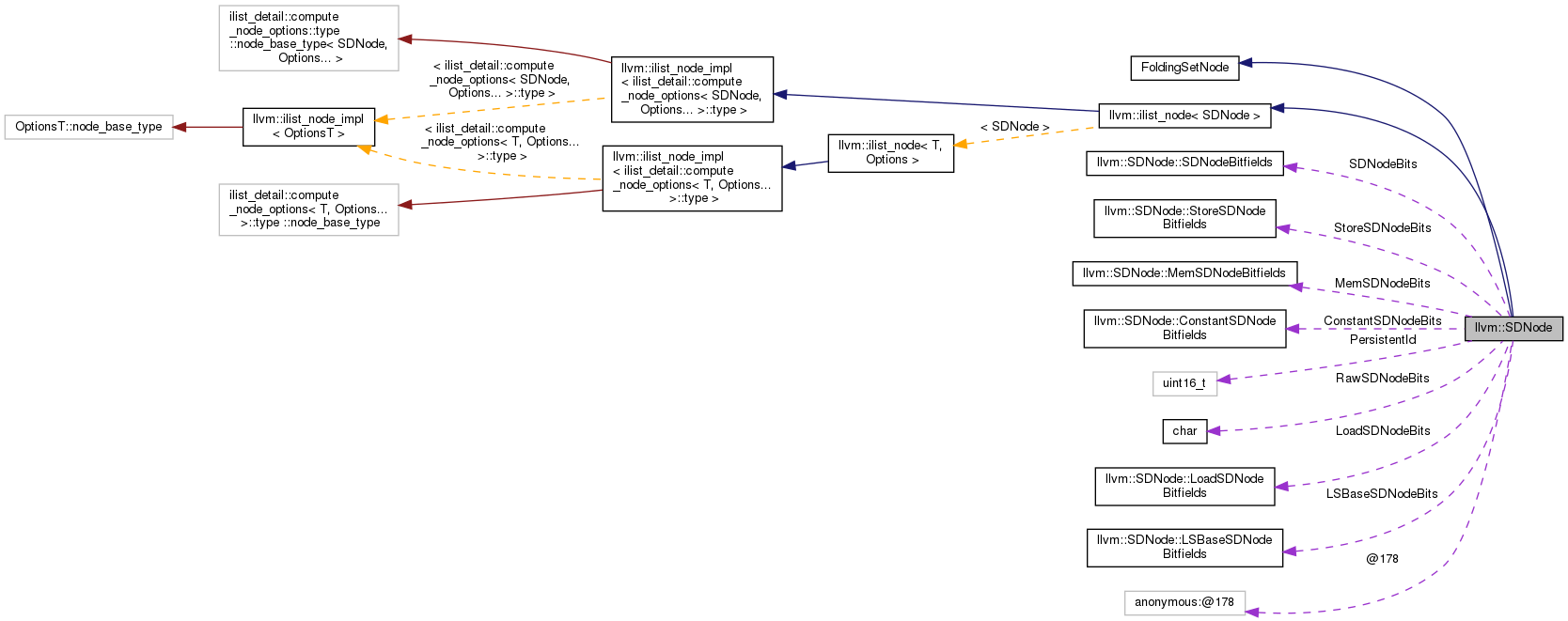

Represents one node in the SelectionDAG. More...

#include "llvm/CodeGen/SelectionDAGNodes.h"

Classes | |

| class | ConstantSDNodeBitfields |

| class | LoadSDNodeBitfields |

| class | LSBaseSDNodeBitfields |

| class | MemSDNodeBitfields |

| class | SDNodeBitfields |

| class | StoreSDNodeBitfields |

| class | use_iterator |

| This class provides iterator support for SDUse operands that use a specific SDNode. More... | |

| struct | value_op_iterator |

| Iterator for directly iterating over the operand SDValue's. More... | |

Public Types | |

| using | op_iterator = SDUse * |

| using | value_iterator = const EVT * |

Public Member Functions | |

| unsigned | getOpcode () const |

| Return the SelectionDAG opcode value for this node. More... | |

| bool | isTargetOpcode () const |

| Test if this node has a target-specific opcode (in the <target>ISD namespace). More... | |

| bool | isTargetMemoryOpcode () const |

| Test if this node has a target-specific memory-referencing opcode (in the <target>ISD namespace and greater than FIRST_TARGET_MEMORY_OPCODE). More... | |

| bool | isUndef () const |

| Return true if the type of the node type undefined. More... | |

| bool | isMemIntrinsic () const |

| Test if this node is a memory intrinsic (with valid pointer information). More... | |

| bool | isStrictFPOpcode () |

| Test if this node is a strict floating point pseudo-op. More... | |

| bool | isMachineOpcode () const |

| Test if this node has a post-isel opcode, directly corresponding to a MachineInstr opcode. More... | |

| unsigned | getMachineOpcode () const |

| This may only be called if isMachineOpcode returns true. More... | |

| bool | getHasDebugValue () const |

| void | setHasDebugValue (bool b) |

| bool | isDivergent () const |

| bool | use_empty () const |

| Return true if there are no uses of this node. More... | |

| bool | hasOneUse () const |

| Return true if there is exactly one use of this node. More... | |

| size_t | use_size () const |

| Return the number of uses of this node. More... | |

| int | getNodeId () const |

| Return the unique node id. More... | |

| void | setNodeId (int Id) |

| Set unique node id. More... | |

| unsigned | getIROrder () const |

| Return the node ordering. More... | |

| void | setIROrder (unsigned Order) |

| Set the node ordering. More... | |

| const DebugLoc & | getDebugLoc () const |

| Return the source location info. More... | |

| void | setDebugLoc (DebugLoc dl) |

| Set source location info. More... | |

| use_iterator | use_begin () const |

| Provide iteration support to walk over all uses of an SDNode. More... | |

| iterator_range< use_iterator > | uses () |

| iterator_range< use_iterator > | uses () const |

| bool | hasNUsesOfValue (unsigned NUses, unsigned Value) const |

| Return true if there are exactly NUSES uses of the indicated value. More... | |

| bool | hasAnyUseOfValue (unsigned Value) const |

| Return true if there are any use of the indicated value. More... | |

| bool | isOnlyUserOf (const SDNode *N) const |

| Return true if this node is the only use of N. More... | |

| bool | isOperandOf (const SDNode *N) const |

| Return true if this node is an operand of N. More... | |

| bool | isPredecessorOf (const SDNode *N) const |

| Return true if this node is a predecessor of N. More... | |

| bool | hasPredecessor (const SDNode *N) const |

| Return true if N is a predecessor of this node. More... | |

| unsigned | getNumOperands () const |

| Return the number of values used by this operation. More... | |

| uint64_t | getConstantOperandVal (unsigned Num) const |

| Helper method returns the integer value of a ConstantSDNode operand. More... | |

| const SDValue & | getOperand (unsigned Num) const |

| op_iterator | op_begin () const |

| op_iterator | op_end () const |

| ArrayRef< SDUse > | ops () const |

| iterator_range< value_op_iterator > | op_values () const |

| SDVTList | getVTList () const |

| SDNode * | getGluedNode () const |

| If this node has a glue operand, return the node to which the glue operand points. More... | |

| SDNode * | getGluedUser () const |

| If this node has a glue value with a user, return the user (there is at most one). More... | |

| const SDNodeFlags | getFlags () const |

| void | setFlags (SDNodeFlags NewFlags) |

| bool | isFast () |

| void | intersectFlagsWith (const SDNodeFlags Flags) |

| Clear any flags in this node that aren't also set in Flags. More... | |

| unsigned | getNumValues () const |

| Return the number of values defined/returned by this operator. More... | |

| EVT | getValueType (unsigned ResNo) const |

| Return the type of a specified result. More... | |

| MVT | getSimpleValueType (unsigned ResNo) const |

| Return the type of a specified result as a simple type. More... | |

| unsigned | getValueSizeInBits (unsigned ResNo) const |

| Returns MVT::getSizeInBits(getValueType(ResNo)). More... | |

| value_iterator | value_begin () const |

| value_iterator | value_end () const |

| std::string | getOperationName (const SelectionDAG *G=nullptr) const |

| Return the opcode of this operation for printing. More... | |

| void | print_types (raw_ostream &OS, const SelectionDAG *G) const |

| void | print_details (raw_ostream &OS, const SelectionDAG *G) const |

| void | print (raw_ostream &OS, const SelectionDAG *G=nullptr) const |

| void | printr (raw_ostream &OS, const SelectionDAG *G=nullptr) const |

| void | printrFull (raw_ostream &O, const SelectionDAG *G=nullptr) const |

| Print a SelectionDAG node and all children down to the leaves. More... | |

| void | printrWithDepth (raw_ostream &O, const SelectionDAG *G=nullptr, unsigned depth=100) const |

| Print a SelectionDAG node and children up to depth "depth." The given SelectionDAG allows target-specific nodes to be printed in human-readable form. More... | |

| void | dump () const |

| Dump this node, for debugging. More... | |

| void | dumpr () const |

| Dump (recursively) this node and its use-def subgraph. More... | |

| void | dump (const SelectionDAG *G) const |

| Dump this node, for debugging. More... | |

| void | dumpr (const SelectionDAG *G) const |

| Dump (recursively) this node and its use-def subgraph. More... | |

| void | dumprFull (const SelectionDAG *G=nullptr) const |

| printrFull to dbgs(). More... | |

| void | dumprWithDepth (const SelectionDAG *G=nullptr, unsigned depth=100) const |

| printrWithDepth to dbgs(). More... | |

| void | Profile (FoldingSetNodeID &ID) const |

| Gather unique data for the node. More... | |

| void | addUse (SDUse &U) |

| This method should only be used by the SDUse class. More... | |

Public Member Functions inherited from llvm::FoldingSetBase::Node Public Member Functions inherited from llvm::FoldingSetBase::Node | |

| Node ()=default | |

| void * | getNextInBucket () const |

| void | SetNextInBucket (void *N) |

Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > | |

| self_iterator | getIterator () |

| const_self_iterator | getIterator () const |

| reverse_self_iterator | getReverseIterator () |

| const_reverse_self_iterator | getReverseIterator () const |

| bool | isSentinel () const |

| Check whether this is the sentinel node. More... | |

Static Public Member Functions | |

| static use_iterator | use_end () |

| static bool | hasPredecessorHelper (const SDNode *N, SmallPtrSetImpl< const SDNode *> &Visited, SmallVectorImpl< const SDNode *> &Worklist, unsigned int MaxSteps=0, bool TopologicalPrune=false) |

| Returns true if N is a predecessor of any node in Worklist. More... | |

| static bool | areOnlyUsersOf (ArrayRef< const SDNode *> Nodes, const SDNode *N) |

| Return true if all the users of N are contained in Nodes. More... | |

| static const char * | getIndexedModeName (ISD::MemIndexedMode AM) |

Public Attributes | |

| uint16_t | PersistentId |

| Unique and persistent id per SDNode in the DAG. More... | |

Protected Types | |

| enum | { NumSDNodeBits = 3 } |

| enum | { NumMemSDNodeBits = NumSDNodeBits + 4 } |

| enum | { NumLSBaseSDNodeBits = NumMemSDNodeBits + 3 } |

Protected Types inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > Protected Types inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > | |

| using | self_iterator = ilist_iterator< ilist_detail::compute_node_options< SDNode, Options... >::type, false, false > |

| using | const_self_iterator = ilist_iterator< ilist_detail::compute_node_options< SDNode, Options... >::type, false, true > |

| using | reverse_self_iterator = ilist_iterator< ilist_detail::compute_node_options< SDNode, Options... >::type, true, false > |

| using | const_reverse_self_iterator = ilist_iterator< ilist_detail::compute_node_options< SDNode, Options... >::type, true, true > |

Protected Member Functions | |

| SDNode (unsigned Opc, unsigned Order, DebugLoc dl, SDVTList VTs) | |

| Create an SDNode. More... | |

| void | DropOperands () |

| Release the operands and set this node to have zero operands. More... | |

Protected Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > Protected Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< SDNode, Options... >::type > | |

| ilist_node_impl ()=default | |

Static Protected Member Functions | |

| static SDVTList | getSDVTList (EVT VT) |

Protected Attributes | |

| union { | |

| char RawSDNodeBits [sizeof(uint16_t)] | |

| SDNodeBitfields SDNodeBits | |

| ConstantSDNodeBitfields ConstantSDNodeBits | |

| MemSDNodeBitfields MemSDNodeBits | |

| LSBaseSDNodeBitfields LSBaseSDNodeBits | |

| LoadSDNodeBitfields LoadSDNodeBits | |

| StoreSDNodeBitfields StoreSDNodeBits | |

| }; | |

Friends | |

| class | SelectionDAG |

| class | HandleSDNode |

Detailed Description

Represents one node in the SelectionDAG.

Definition at line 482 of file SelectionDAGNodes.h.

Member Typedef Documentation

◆ op_iterator

| using llvm::SDNode::op_iterator = SDUse * |

Definition at line 909 of file SelectionDAGNodes.h.

◆ value_iterator

| using llvm::SDNode::value_iterator = const EVT * |

Definition at line 982 of file SelectionDAGNodes.h.

Member Enumeration Documentation

◆ anonymous enum

|

protected |

| Enumerator | |

|---|---|

| NumSDNodeBits | |

Definition at line 502 of file SelectionDAGNodes.h.

◆ anonymous enum

|

protected |

| Enumerator | |

|---|---|

| NumMemSDNodeBits | |

Definition at line 524 of file SelectionDAGNodes.h.

◆ anonymous enum

|

protected |

| Enumerator | |

|---|---|

| NumLSBaseSDNodeBits | |

Definition at line 533 of file SelectionDAGNodes.h.

Constructor & Destructor Documentation

◆ SDNode()

Create an SDNode.

SDNodes are created without any operands, and never own the operand storage. To add operands, see SelectionDAG::createOperands.

Definition at line 1058 of file SelectionDAGNodes.h.

References assert(), llvm::DebugLoc::hasTrivialDestructor(), llvm::Intrinsic::memset, and llvm::SDVTList::NumVTs.

Member Function Documentation

◆ addUse()

|

inline |

This method should only be used by the SDUse class.

Definition at line 1046 of file SelectionDAGNodes.h.

Referenced by llvm::SDValue::dumpr().

◆ areOnlyUsersOf()

Return true if all the users of N are contained in Nodes.

Return true if the only users of N are contained in Nodes.

NOTE: Requires at least one match, but doesn't require them all.

Definition at line 8760 of file SelectionDAG.cpp.

References llvm::any_of(), E, I, llvm::FoldingSetBase::Node::Node(), use_begin(), and use_end().

Referenced by combineX86ShufflesRecursively().

◆ DropOperands()

|

protected |

Release the operands and set this node to have zero operands.

DropOperands - Release the operands and set this node to have zero operands.

Definition at line 7436 of file SelectionDAG.cpp.

Referenced by llvm::SelectionDAG::DeleteNode().

◆ dump() [1/2]

| LLVM_DUMP_METHOD void SDNode::dump | ( | ) | const |

Dump this node, for debugging.

Definition at line 472 of file SelectionDAGDumper.cpp.

Referenced by llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), canFoldInAddressingMode(), llvm::SDValue::dump(), llvm::ScheduleDAGSDNodes::dumpNode(), llvm::InstrEmitter::EmitDbgLabel(), getExpandedMinMaxOps(), GetFPLibCall(), getIPMConversion(), getShiftAmountTyForConstant(), isAnyConstantBuildVector(), isSETCCorConvertedSETCC(), isTargetConstant(), llvm::HexagonTargetLowering::LowerDYNAMIC_STACKALLOC(), mayUseP9Setb(), NewSDValueDbgMsg(), numVectorEltsOrZero(), PeepholePPC64ZExtGather(), PerformSHLSimplify(), llvm::SelectionDAGISel::SelectCodeCommon(), selectI64Imm(), llvm::HvxSelector::selectShuffle(), simplifyDivRem(), tryLowerToSLI(), and VerifySDNode().

◆ dump() [2/2]

| LLVM_DUMP_METHOD void SDNode::dump | ( | const SelectionDAG * | G | ) | const |

Dump this node, for debugging.

The given SelectionDAG allows target-specific nodes to be printed in human-readable form.

Definition at line 474 of file SelectionDAGDumper.cpp.

References llvm::dbgs(), and print().

◆ dumpr() [1/2]

| LLVM_DUMP_METHOD void SDNode::dumpr | ( | ) | const |

Dump (recursively) this node and its use-def subgraph.

Definition at line 815 of file SelectionDAGDumper.cpp.

Referenced by llvm::SDValue::dumpr(), and llvm::HexagonTargetLowering::LowerOperation().

◆ dumpr() [2/2]

| LLVM_DUMP_METHOD void SDNode::dumpr | ( | const SelectionDAG * | G | ) | const |

Dump (recursively) this node and its use-def subgraph.

The given SelectionDAG allows target-specific nodes to be printed in human-readable form.

Definition at line 820 of file SelectionDAGDumper.cpp.

◆ dumprFull()

| LLVM_DUMP_METHOD void SDNode::dumprFull | ( | const SelectionDAG * | G = nullptr | ) | const |

printrFull to dbgs().

The given SelectionDAG allows target-specific nodes to be printed in human-readable form. Unlike dumpr, this will print the whole DAG, including children that appear multiple times.

Definition at line 864 of file SelectionDAGDumper.cpp.

Referenced by checkForCyclesHelper(), and llvm::SelectionDAG::salvageDebugInfo().

◆ dumprWithDepth()

| LLVM_DUMP_METHOD void SDNode::dumprWithDepth | ( | const SelectionDAG * | G = nullptr, |

| unsigned | depth = 100 |

||

| ) | const |

printrWithDepth to dbgs().

The given SelectionDAG allows target-specific nodes to be printed in human-readable form. Unlike dumpr, this will print children that appear multiple times wherever they are used.

Definition at line 860 of file SelectionDAGDumper.cpp.

◆ getConstantOperandVal()

|

inline |

Helper method returns the integer value of a ConstantSDNode operand.

Definition at line 1535 of file SelectionDAGNodes.h.

References llvm::SDValue::getOperand().

Referenced by checkBoolTestAndOrSetCCCombine(), combineBrCond(), combineCMov(), combineExtractVectorElt(), combineExtractWithShuffle(), combineInsertSubvector(), combineOrCmpEqZeroToCtlzSrl(), combineX86SetCC(), ConstantBuildVector(), llvm::InstrEmitter::EmitDbgLabel(), findEXTRHalf(), findUser(), FoldIntToFPToInt(), foldXor1SetCC(), llvm::SDValue::getConstantOperandVal(), getExpandedMinMaxOps(), GetFPLibCall(), getPermuteMask(), getPromotedVectorElementType(), getShiftAmountTyForConstant(), getTargetShuffleMask(), isCalleeLoad(), llvm::AArch64TargetLowering::isDesirableToCommuteWithShift(), isSlicingProfitable(), lowerMSABitClearImm(), lowerMSASplatImm(), mayUseP9Setb(), narrowExtractedVectorLoad(), needCarryOrOverflowFlag(), onlyZeroFlagUsed(), PeepholePPC64ZExtGather(), llvm::PPCTargetLowering::PerformDAGCombine(), replaceZeroVectorStore(), and llvm::SelectionDAG::salvageDebugInfo().

◆ getDebugLoc()

Return the source location info.

Definition at line 727 of file SelectionDAGNodes.h.

Referenced by llvm::InstrEmitter::EmitDbgLabel(), llvm::SDValue::getDebugLoc(), llvm::SelectionDAG::SelectNodeTo(), and llvm::SelectionDAG::~SelectionDAG().

◆ getFlags()

|

inline |

Definition at line 955 of file SelectionDAGNodes.h.

Referenced by llvm::TargetLowering::BuildSDIV(), calculateByteProvider(), CanCombineFCOPYSIGN_EXTEND_ROUND(), CollectOpsToWiden(), combineAdd(), combineFMinNumFMaxNum(), combineFneg(), llvm::createR600ISelDag(), llvm::InstrEmitter::EmitDbgLabel(), EmitTest(), expandf64Toi32(), foldAddSubOfSignBit(), FoldIntToFPToInt(), fp16SrcZerosHighBits(), getFPTernOp(), getLoadExtOrTrunc(), getMad64_32(), GetNegatedExpression(), GetPromotionOpcode(), getReductionSDNode(), isAnyConstantBuildVector(), isBSwapHWordElement(), isClampZeroToOne(), isContractable(), llvm::SelectionDAG::isKnownNeverNaN(), isNegatibleForFree(), isStackPtrRelative(), llvm::AMDGPUTargetLowering::lowerFEXP(), llvm::AMDGPUTargetLowering::mayIgnoreSignedZero(), narrowExtractedVectorBinOp(), llvm::AMDGPUTargetLowering::performFNegCombine(), print_details(), promoteExtBeforeAdd(), replaceShuffleOfInsert(), llvm::TargetLowering::SimplifyDemandedBits(), simplifyDivRem(), llvm::SITargetLowering::splitBinaryVectorOp(), llvm::SITargetLowering::splitUnaryVectorOp(), tryFoldToZero(), and llvm::SelectionDAG::UnrollVectorOp().

◆ getGluedNode()

|

inline |

If this node has a glue operand, return the node to which the glue operand points.

Otherwise return NULL.

Definition at line 939 of file SelectionDAGNodes.h.

References llvm::MVT::Glue.

Referenced by addStackMapLiveVars(), llvm::ScheduleDAGSDNodes::RegDefIter::Advance(), canClobberPhysRegDefs(), llvm::ScheduleDAGSDNodes::computeLatency(), llvm::ScheduleDAGSDNodes::dumpNode(), llvm::ScheduleDAGSDNodes::EmitSchedule(), getARClassRegisterMask(), llvm::ScheduleDAGSDNodes::getGraphNodeLabel(), isOperandOf(), llvm::ResourcePriorityQueue::isResourceAvailable(), llvm::SITargetLowering::legalizeTargetIndependentNode(), llvm::SelectionDAGBuilder::LowerAsSTATEPOINT(), LowerMGATHER(), and llvm::ResourcePriorityQueue::reserveResources().

◆ getGluedUser()

|

inline |

If this node has a glue value with a user, return the user (there is at most one).

Otherwise return NULL.

Definition at line 948 of file SelectionDAGNodes.h.

References llvm::MVT::Glue.

Referenced by llvm::InstrEmitter::EmitDbgLabel(), findGluedUser(), and getARClassRegisterMask().

◆ getHasDebugValue()

|

inline |

Definition at line 697 of file SelectionDAGNodes.h.

Referenced by llvm::SelectionDAG::AddDbgValue(), ProcessSDDbgValues(), llvm::SelectionDAG::salvageDebugInfo(), and llvm::SelectionDAG::transferDbgValues().

◆ getIndexedModeName()

|

static |

Definition at line 425 of file SelectionDAGDumper.cpp.

References llvm::ISD::POST_DEC, llvm::ISD::POST_INC, llvm::ISD::PRE_DEC, and llvm::ISD::PRE_INC.

◆ getIROrder()

|

inline |

Return the node ordering.

Definition at line 721 of file SelectionDAGNodes.h.

Referenced by PerformADDCombineWithOperands(), ProcessSourceNode(), llvm::SelectionDAGBuilder::resolveDanglingDebugInfo(), llvm::SelectionDAG::SelectNodeTo(), and llvm::SelectionDAG::~SelectionDAG().

◆ getMachineOpcode()

|

inline |

This may only be called if isMachineOpcode returns true.

It returns the MachineInstr opcode value that the node's opcode corresponds to.

Definition at line 692 of file SelectionDAGNodes.h.

References assert().

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::SIInstrInfo::areLoadsFromSameBasePtr(), llvm::ARMBaseInstrInfo::areLoadsFromSameBasePtr(), llvm::X86InstrInfo::areLoadsFromSameBasePtr(), llvm::ScheduleDAGSDNodes::BuildSchedGraph(), CalcNodeSethiUllmanNumber(), canClobberPhysRegDefs(), canClobberReachingPhysRegUse(), llvm::Thumb1InstrInfo::canCopyGluedNodeDuringSchedule(), canEnableCoalescing(), CheckForPhysRegDependency(), llvm::ScheduleDAGSDNodes::computeLatency(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), llvm::createR600ISelDag(), llvm::InstrEmitter::EmitDbgLabel(), FindCallSeqStart(), llvm::TargetInstrInfo::getInstrLatency(), llvm::SDValue::getMachineOpcode(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::TargetInstrInfo::getOperandLatency(), getOperationName(), getPhysicalRegisterVT(), llvm::ARMTargetLowering::getSchedulingPreference(), getUsefulBitsForUse(), isBitfieldExtractOp(), isCalleeLoad(), IsChainDependent(), isMemOPCandidate(), llvm::ResourcePriorityQueue::isResourceAvailable(), mayUseP9Setb(), llvm::ScheduleDAGSDNodes::newSUnit(), nodesHaveSameOperandValue(), PeepholePPC64ZExtGather(), PerformANDCombine(), performBitcastCombine(), llvm::R600TargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PostISelFolding(), llvm::ResourcePriorityQueue::reserveResources(), llvm::ARMBaseInstrInfo::shouldScheduleLoadsNear(), llvm::X86InstrInfo::shouldScheduleLoadsNear(), llvm::HexagonDAGToDAGISel::StoreInstrForLoadIntrinsic(), stripExtractLoElt(), and llvm::X86InstrInfo::unfoldMemoryOperand().

◆ getNodeId()

|

inline |

Return the unique node id.

Definition at line 715 of file SelectionDAGNodes.h.

Referenced by canEnableCoalescing(), getContiguousRangeOfSetBits(), llvm::ScheduleDAGSDNodes::getCustomGraphFeatures(), llvm::SelectionDAGISel::getUninvalidatedNodeId(), hasPredecessorHelper(), insertDAGNode(), llvm::SelectionDAGISel::InvalidateNodeId(), isFusableLoadOpStorePattern(), and isOperandOf().

◆ getNumOperands()

|

inline |

Return the number of values used by this operation.

Definition at line 899 of file SelectionDAGNodes.h.

Referenced by AddCombineBUILD_VECTORToVPADDL(), AddCombineTo64bitMLAL(), AddGlue(), addShuffleForVecExtend(), llvm::ISD::allOperandsUndef(), llvm::SelectionDAG::AssignTopologicalOrder(), canReduceVMulWidth(), CollectOpsToWiden(), CombineBaseUpdate(), combineBVOfConsecutiveLoads(), combineBVOfVecSExt(), combineConcatVectorOfExtracts(), combineFMA(), combineFMADDSUB(), combineSelect(), computeZeroableShuffleElements(), ConvertSelectToConcatVector(), llvm::createR600ISelDag(), llvm::SDNodeIterator::end(), ExpandBVWithShuffles(), findMatchingInlineAsmOperand(), foldBitcastedFPLogic(), llvm::PPC::get_VSPLTI_elt(), getARClassRegisterMask(), getConstantValue(), getDivRemArgList(), getExpandedMinMaxOps(), getExtendedControlRegister(), GetFPLibCall(), getInputChainForNode(), llvm::SDValue::getNumOperands(), getReadPerformanceCounter(), getReadTimeStampCounter(), getShiftAmountTyForConstant(), llvm::BuildVectorSDNode::getSplatValue(), getTargetShuffleMask(), getTargetVShiftByConstNode(), getTestBitOperand(), haveEfficientBuildVectorPattern(), llvm::ISD::isBuildVectorAllOnes(), isConstantOrUndefBUILD_VECTOR(), llvm::BuildVectorSDNode::isConstantSplat(), isExtendedBUILD_VECTOR(), isFPExtLoad(), isMemOPCandidate(), isOpcWithIntImmediate(), isPermutation(), isSETCCorConvertedSETCC(), isSplatZeroExtended(), llvm::SITargetLowering::legalizeTargetIndependentNode(), llvm::SelectionDAGBuilder::LowerAsSTATEPOINT(), lowerDSPIntr(), llvm::SparcTargetLowering::LowerF128Op(), LowerInterruptReturn(), LowerMGATHER(), LowerMULH(), mayUseP9Setb(), operator!=(), opMustUseVOP3Encoding(), Passv64i1ArgInRegs(), performANDCombine(), PerformANDCombine(), PerformBUILD_VECTORCombine(), performConcatVectorsCombine(), llvm::AArch64TargetLowering::PerformDAGCombine(), performNEONPostLDSTCombine(), performSRACombine(), pickOpcodeForVT(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), reduceBuildVecToShuffleWithZero(), replaceInChain(), replaceShuffleOfInsert(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), scalarizeExtractedBinop(), llvm::ResourcePriorityQueue::scheduledNode(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::HexagonDAGToDAGISel::SelectNewCircIntrinsic(), ShrinkLoadReplaceStoreWithStore(), simplifyDivRem(), tryBuildVectorByteMask(), llvm::HexagonDAGToDAGISel::tryLoadOfLoadIntrinsic(), llvm::X86InstrInfo::unfoldMemoryOperand(), llvm::SelectionDAG::UnrollVectorOp(), llvm::SelectionDAG::updateDivergence(), llvm::SelectionDAG::UpdateNodeOperands(), and VerifySDNode().

◆ getNumValues()

|

inline |

Return the number of values defined/returned by this operator.

Definition at line 964 of file SelectionDAGNodes.h.

Referenced by AddGlue(), llvm::ScheduleDAGSDNodes::BuildSchedGraph(), BURRSort(), CalcNodeSethiUllmanNumber(), CallingConvSupported(), canChangeToInt(), canClobberPhysRegDefs(), llvm::TargetLowering::DAGCombinerInfo::CommitTargetLoweringOpt(), constructRetValue(), doNotCSE(), llvm::InstrEmitter::EmitDbgLabel(), emitIntrinsicWithCCAndChain(), findGlueUse(), findUser(), getCCResult(), getCmp(), getContiguousRangeOfSetBits(), getExpandedMinMaxOps(), getFPBinOp(), GetFPLibCall(), getFPTernOp(), llvm::ARMTargetLowering::getSchedulingPreference(), getShiftAmountTyForConstant(), getUnderlyingArgReg(), getUniformBase(), llvm::SelectionDAGBuilder::getValueImpl(), GetVBR(), hasAnyUseOfValue(), hasNUsesOfValue(), isAnyConstantBuildVector(), llvm::SelectionDAGISel::IsLegalToFold(), isMemOPCandidate(), isOperandOf(), isSETCCorConvertedSETCC(), llvm::SITargetLowering::legalizeTargetIndependentNode(), lowerCallResult(), LowerCallResult(), LowerInterruptReturn(), LowerLoad(), llvm::R600TargetLowering::LowerOperation(), llvm::SITargetLowering::LowerOperation(), llvm::MipsTargetLowering::LowerOperationWrapper(), llvm::X86TargetLowering::LowerOperationWrapper(), llvm::SelectionDAGBuilder::lowerRangeToAssertZExt(), llvm::DAGTypeLegalizer::NoteDeletion(), Passv64i1ArgInRegs(), llvm::AArch64TargetLowering::PerformDAGCombine(), PrepareCall(), print_types(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), RemoveUnusedGlue(), llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::SelectionDAG::ReplaceAllUsesWith(), llvm::AVRTargetLowering::ReplaceNodeResults(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::ResourcePriorityQueue::scheduledNode(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::TargetLowering::ShrinkDemandedOp(), simplifyDivRem(), llvm::X86InstrInfo::unfoldMemoryOperand(), llvm::SelectionDAG::UnrollVectorOp(), useSinCos(), and VerifySDNode().

◆ getOpcode()

|

inline |

Return the SelectionDAG opcode value for this node.

For pre-isel nodes (those for which isMachineOpcode returns false), these are the opcode values in the ISD and <target>ISD namespaces. For post-isel opcodes, see getMachineOpcode.

Definition at line 625 of file SelectionDAGNodes.h.

Referenced by AddCombineBUILD_VECTORToVPADDL(), AddCombineTo64bitMLAL(), AddCombineTo64bitUMAAL(), AddNodeIDCustom(), AddNodeIDNode(), addStackMapLiveVars(), adjustForFNeg(), adjustForLTGFR(), adjustForSubtraction(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), llvm::ScheduleDAGSDNodes::BuildSchedGraph(), CalcNodeSethiUllmanNumber(), calculateByteProvider(), canEmitConjunction(), canEnableCoalescing(), canFoldInAddressingMode(), CheckAndImm(), checkBoolTestAndOrSetCCCombine(), CheckForMaskedLoad(), CheckForPhysRegDependency(), checkHighLaneIndex(), CheckOpcode(), CheckOrImm(), checkValueWidth(), llvm::AddrSpaceCastSDNode::classof(), llvm::MemSDNode::classof(), llvm::AtomicSDNode::classof(), llvm::X86StoreSDNode::classof(), llvm::MemIntrinsicSDNode::classof(), llvm::X86MaskedStoreSDNode::classof(), llvm::TruncSStoreSDNode::classof(), llvm::TruncUSStoreSDNode::classof(), llvm::MaskedTruncSStoreSDNode::classof(), llvm::MaskedTruncUSStoreSDNode::classof(), llvm::ShuffleVectorSDNode::classof(), llvm::X86MaskedGatherScatterSDNode::classof(), llvm::X86MaskedGatherSDNode::classof(), llvm::ConstantSDNode::classof(), llvm::X86MaskedScatterSDNode::classof(), llvm::ConstantFPSDNode::classof(), llvm::GlobalAddressSDNode::classof(), llvm::FrameIndexSDNode::classof(), llvm::JumpTableSDNode::classof(), llvm::ConstantPoolSDNode::classof(), llvm::TargetIndexSDNode::classof(), llvm::BasicBlockSDNode::classof(), llvm::BuildVectorSDNode::classof(), llvm::SrcValueSDNode::classof(), llvm::MDNodeSDNode::classof(), llvm::RegisterSDNode::classof(), llvm::RegisterMaskSDNode::classof(), llvm::BlockAddressSDNode::classof(), llvm::LabelSDNode::classof(), llvm::ExternalSymbolSDNode::classof(), llvm::MCSymbolSDNode::classof(), llvm::CondCodeSDNode::classof(), llvm::VTSDNode::classof(), llvm::LSBaseSDNode::classof(), llvm::LoadSDNode::classof(), llvm::StoreSDNode::classof(), llvm::MaskedLoadStoreSDNode::classof(), llvm::MaskedLoadSDNode::classof(), llvm::MaskedStoreSDNode::classof(), llvm::MaskedGatherScatterSDNode::classof(), llvm::MaskedGatherSDNode::classof(), llvm::MaskedScatterSDNode::classof(), CloneNodeWithValues(), closestSucc(), CollectOpsToWiden(), combineAddOrSubToADCOrSBB(), combineADDToADDZE(), CombineANDShift(), combineANDXORWithAllOnesIntoANDNP(), CombineBaseUpdate(), combineBitcastvxi1(), combineBVOfConsecutiveLoads(), combineBVOfVecSExt(), combineCastedMaskArithmetic(), combineCCMask(), combineExtractVectorElt(), combineExtSetcc(), combineFaddFsub(), combineFMA(), combineFMADDSUB(), combineFMinFMax(), combineFMinNumFMaxNum(), combineFOr(), combineIncDecVector(), combineLogicBlendIntoPBLENDV(), combineMinNumMaxNum(), combineMul(), combineOrCmpEqZeroToCtlzSrl(), combinePMULDQ(), combineSelect(), combineSelectAndUse(), combineShift(), combineShuffle(), combineShuffleToFMAddSub(), combineToExtendBoolVectorInReg(), combineToExtendCMOV(), combineToExtendVectorInReg(), combineTruncatedArithmetic(), combineVectorCompare(), combineVectorCompareAndMaskUnaryOp(), combineVectorInsert(), combineVectorPack(), combineVectorShiftImm(), combineVectorShiftVar(), CombineVLDDUP(), combineVSelectToBLENDV(), combineVSelectWithAllOnesOrZeros(), llvm::ARMTargetLowering::computeKnownBitsForTargetNode(), llvm::ScheduleDAGSDNodes::computeLatency(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), convertIntLogicToFPLogic(), ConvertSelectToConcatVector(), llvm::createARCISelDag(), createBSWAPShuffleMask(), llvm::createR600ISelDag(), llvm::createXCoreISelDag(), llvm::HexagonDAGToDAGISel::DetectUseSxtw(), doNotCSE(), emitConjunctionRec(), llvm::InstrEmitter::EmitDbgLabel(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), EmitTest(), Expand64BitShift(), ExpandBVWithShuffles(), expandDisp(), llvm::TargetLowering::expandMUL(), llvm::TargetLowering::expandUnalignedLoad(), llvm::PPCTargetLowering::expandVSXLoadForLE(), llvm::PPCTargetLowering::expandVSXStoreForLE(), ExtendUsesToFormExtLoad(), FindCallSeqStart(), findConsecutiveLoad(), findMUL_LOHI(), findUser(), foldAddSubBoolOfMaskedVal(), foldAddSubOfSignBit(), foldBitcastedFPLogic(), foldExtendedSignBitTest(), foldFPToIntToFP(), FoldIntToFPToInt(), foldMaskedShiftToBEXTR(), foldShuffleOfHorizOp(), llvm::SelectionDAG::FoldSymbolOffset(), foldXor1SetCC(), generateEquivalentSub(), getARMIndexedAddressParts(), getAsNonOpaqueConstant(), getBuildPairElt(), getConstantValue(), getContiguousRangeOfSetBits(), getDivRemArgList(), getDivRemLibcall(), getExpandedMinMaxOps(), GetFPLibCall(), getFPTernOp(), getIntrinsicID(), getIPMConversion(), getMad64_32(), getMOVL(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), getOperationName(), getPermuteMask(), getPhysicalRegisterVT(), llvm::AVRTargetLowering::getPostIndexedAddressParts(), llvm::HexagonTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::AVRTargetLowering::getPreIndexedAddressParts(), getPromotedVectorElementType(), GetPromotionOpcode(), getPTXCmpMode(), llvm::AVRTargetLowering::getSetCCResultType(), getShiftAmountTyForConstant(), getSplatConstantFP(), getT2IndexedAddressParts(), getTargetConstantFromNode(), getTargetShuffleMask(), getTestBitOperand(), GetVBR(), hasNonFlagsUse(), hasOnlyLiveInOpers(), hasOnlyLiveOutUses(), hasPredecessorHelper(), hasSingleUsesFromRoot(), hasSourceMods(), hasVRegCycleUse(), isADDADDMUL(), isAddSubOrSubAdd(), isAddSubSExt(), isAddSubZExt(), llvm::ISD::isBinaryOp(), isBitfieldExtractOp(), isBitfieldExtractOpFromAnd(), isBitfieldExtractOpFromSExtInReg(), isBitfieldExtractOpFromShr(), isBitwiseInverse(), llvm::ISD::isBuildVectorAllOnes(), llvm::ISD::isBuildVectorAllZeros(), llvm::ISD::isBuildVectorOfConstantFPSDNodes(), llvm::ISD::isBuildVectorOfConstantSDNodes(), isCalleeLoad(), IsChainDependent(), isConditionalZeroOrAllOnes(), isConsecutiveLS(), isContractable(), isCopyFromRegOfInlineAsm(), llvm::AArch64TargetLowering::isDesirableToCommuteWithShift(), llvm::ARMTargetLowering::isDesirableToCommuteWithShift(), llvm::X86TargetLowering::IsDesirableToPromoteOp(), isExtendedBUILD_VECTOR(), llvm::TargetLowering::isExtendedTrueVal(), isFloatingPointZero(), isFNEG(), isFPExtLoad(), llvm::TargetLowering::isGAPlusOffset(), isHorizontalBinOpPart(), isInt32Immediate(), isInt64Immediate(), isLegalMaskCompare(), isMemOPCandidate(), isOpcodeHandled(), isOpcWithIntImmediate(), llvm::SelectionDAGISel::isOrEquivalentToAdd(), isPerfectIncrement(), isPermutation(), isSaturatingConditional(), llvm::AMDGPUTargetLowering::isSDNodeAlwaysUniform(), llvm::SITargetLowering::isSDNodeSourceOfDivergence(), isSETCCorConvertedSETCC(), isSeveralBitsExtractOpFromShr(), isSignExtended(), IsSingleInstrConstant(), isSlicingProfitable(), isStackPtrRelative(), isTargetConstant(), isTruncateOf(), isVectorAllOnes(), llvm::ARMTargetLowering::isVectorLoadExtDesirable(), IsVUZPShuffleNode(), isXor1OfSetCC(), isZeroExtended(), llvm::SITargetLowering::legalizeTargetIndependentNode(), llvm::HexagonDAGToDAGISel::LoadInstrForLoadIntrinsic(), LowerADDSUBCARRY(), lowerAtomicArith(), lowerAtomicArithWithLOCK(), llvm::SparcTargetLowering::LowerCall_64(), lowerCallFromStatepointLoweringInfo(), llvm::TargetLowering::lowerCmpEqZeroToCtlzSrl(), LowerCTTZ(), LowerEXTRACT_VECTOR_ELT_SSE4(), LowerInterruptReturn(), llvm::MSP430TargetLowering::LowerJumpTable(), LowerMULH(), llvm::HexagonTargetLowering::LowerOperationWrapper(), llvm::SystemZTargetLowering::LowerOperationWrapper(), LowerShift(), LowerVECTOR_SHUFFLE(), lowerX86FPLogicOp(), maskMatters(), llvm::BaseIndexOffset::match(), llvm::SelectionDAG::matchBinOpReduction(), matchLogicBlend(), matchPMADDWD(), MayFoldIntoZeroExtend(), mayUseP9Setb(), needCarryOrOverflowFlag(), numVectorEltsOrZero(), onlyZeroFlagUsed(), llvm::TargetLowering::parametersInCSRMatch(), ParseBFI(), Passv64i1ArgInRegs(), PerformADDCombineWithOperands(), PerformAddcSubcCombine(), PerformAddeSubeCombine(), performAddSubLongCombine(), performANDCombine(), PerformANDCombine(), PerformARMBUILD_VECTORCombine(), llvm::AMDGPUTargetLowering::performAssertSZExtCombine(), performBitcastCombine(), llvm::ARMTargetLowering::PerformBRCONDCombine(), performCMovFPCombine(), llvm::ARMTargetLowering::PerformCMOVToBFICombine(), performConcatVectorsCombine(), performCONDCombine(), llvm::R600TargetLowering::PerformDAGCombine(), llvm::MipsSETargetLowering::PerformDAGCombine(), llvm::RISCVTargetLowering::PerformDAGCombine(), llvm::LanaiTargetLowering::PerformDAGCombine(), llvm::SparcTargetLowering::PerformDAGCombine(), llvm::AMDGPUTargetLowering::PerformDAGCombine(), llvm::AArch64TargetLowering::PerformDAGCombine(), llvm::ARMTargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PerformDAGCombine(), llvm::MipsTargetLowering::PerformDAGCombine(), llvm::SystemZTargetLowering::PerformDAGCombine(), llvm::PPCTargetLowering::PerformDAGCombine(), llvm::X86TargetLowering::PerformDAGCombine(), performDivRemCombine(), performExtendCombine(), PerformExtendCombine(), performFDivCombine(), performFpToIntCombine(), performGlobalAddressCombine(), performIntegerAbsCombine(), performIntToFpCombine(), performMADD_MSUBCombine(), performMulCombine(), llvm::AMDGPUTargetLowering::performMulLoHi24Combine(), performNEONPostLDSTCombine(), performORCombine(), performPostLD1Combine(), PerformREMCombine(), performSetccAddFolding(), PerformSETCCCombine(), PerformShiftCombine(), llvm::AMDGPUTargetLowering::performShlCombine(), PerformSHLSimplify(), performSRACombine(), PerformSTORECombine(), performTBZCombine(), PerformUMLALCombine(), PerformVCVTCombine(), PerformVDIVCombine(), performVectorCompareAndMaskUnaryOpCombine(), performXORCombine(), pickOpcodeForVT(), PrepareCall(), promoteExtBeforeAdd(), PromoteMaskArithmetic(), llvm::SDValue::reachesChainWithoutSideEffects(), reduceBuildVecToShuffleWithZero(), llvm::SelectionDAG::RemoveDeadNodes(), ReplaceCMP_SWAP_128Results(), replaceInChain(), ReplaceINTRINSIC_W_CHAIN(), llvm::R600TargetLowering::ReplaceNodeResults(), llvm::AVRTargetLowering::ReplaceNodeResults(), llvm::XCoreTargetLowering::ReplaceNodeResults(), llvm::HexagonTargetLowering::ReplaceNodeResults(), llvm::AMDGPUTargetLowering::ReplaceNodeResults(), llvm::SparcTargetLowering::ReplaceNodeResults(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::SITargetLowering::ReplaceNodeResults(), llvm::PPCTargetLowering::ReplaceNodeResults(), llvm::X86TargetLowering::ReplaceNodeResults(), replaceShuffleOfInsert(), resetVRegCycle(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), llvm::SelectionDAG::salvageDebugInfo(), scalarizeExtractedBinop(), llvm::HexagonDAGToDAGISel::Select(), llvm::HexagonDAGToDAGISel::SelectAddSubCarry(), llvm::HexagonDAGToDAGISel::SelectBrevLdIntrinsic(), llvm::SelectionDAGISel::SelectCodeCommon(), selectI64Imm(), llvm::AVRDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWOChain(), llvm::HexagonDAGToDAGISel::SelectNewCircIntrinsic(), llvm::HexagonDAGToDAGISel::SelectTypecast(), shouldUseLA(), ShrinkLoadReplaceStoreWithStore(), simplifyDivRem(), simplifyI24(), llvm::TargetLowering::SimplifySetCC(), skipExtensionForVectorMULL(), SkipExtensionForVMULL(), SplitVSETCC(), stripModuloOnShift(), tryBitfieldInsertOpFromOr(), tryBitfieldInsertOpFromOrAndImm(), tryCombineToEXTR(), tryExtendDUPToExtractHigh(), tryFoldToZero(), llvm::HexagonDAGToDAGISel::tryLoadOfLoadIntrinsic(), TryMULWIDECombine(), tryToFoldExtendOfConstant(), llvm::SelectionDAG::UnrollVectorOp(), llvm::X86TargetLowering::unwrapAddress(), usePartialVectorLoads(), useSinCos(), VerifySDNode(), visitFMinMax(), and llvm::SelectionDAG::~SelectionDAG().

◆ getOperand()

Definition at line 904 of file SelectionDAGNodes.h.

References assert().

Referenced by AddCombineBUILD_VECTORToVPADDL(), AddCombineTo64bitMLAL(), AddCombineTo64BitSMLAL16(), AddCombineTo64bitUMAAL(), AddCombineToVPADD(), AddGlue(), llvm::MipsSETargetLowering::addMSAFloatType(), addStackMapLiveVars(), adjustForLTGFR(), adjustForSubtraction(), llvm::SIInstrInfo::areLoadsFromSameBasePtr(), llvm::ARMBaseInstrInfo::areLoadsFromSameBasePtr(), llvm::X86InstrInfo::areLoadsFromSameBasePtr(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), BuildExactSDIV(), llvm::TargetLowering::BuildSDIV(), llvm::PPCTargetLowering::BuildSDIVPow2(), llvm::TargetLowering::BuildUDIV(), buildVector(), calculateByteProvider(), CanCombineFCOPYSIGN_EXTEND_ROUND(), canEmitConjunction(), canEnableCoalescing(), canFoldInAddressingMode(), canLowerToLDG(), canReduceVMulWidth(), CheckAndImm(), checkBoolTestAndOrSetCCCombine(), CheckForMaskedLoad(), CheckForPhysRegDependency(), checkHighLaneIndex(), CheckOrImm(), checkV64LaneV128(), checkValueWidth(), CollectOpsToWiden(), combineAcrossLanesIntrinsic(), combineADC(), combineAdd(), combineAddOrSubToADCOrSBB(), combineADDToADDZE(), combineAddToSUBUS(), combineAnd(), combineAndMaskToShift(), combineAndnp(), CombineANDShift(), combineANDXORWithAllOnesIntoANDNP(), CombineBaseUpdate(), combineBasicSADPattern(), combineBEXTR(), combineBitcast(), combineBitcastvxi1(), combineBrCond(), combineBT(), combineBVOfConsecutiveLoads(), combineBVOfVecSExt(), combineCastedMaskArithmetic(), combineCCMask(), combineCMov(), combineCMP(), combineCompareEqual(), combineConcatVectorOfExtracts(), combineConcatVectorOfScalars(), combineExtractSubvector(), combineExtractVectorElt(), combineExtractWithShuffle(), combineExtSetcc(), combineFaddFsub(), combineFAnd(), combineFAndFNotToFAndn(), combineFAndn(), combineFMA(), combineFMADDSUB(), combineFMinFMax(), combineFMinNumFMaxNum(), combineFOr(), combineGatherScatter(), combineIncDecVector(), combineInsertSubvector(), combineLogicBlendIntoPBLENDV(), combineLoopMAddPattern(), combineLoopSADPattern(), combineMaskedLoadConstantMask(), combineMinNumMaxNum(), combineMOVMSK(), combineMul(), combineMulSpecial(), combineMulToPMADDWD(), combineMulToPMULDQ(), combineOr(), combineOrCmpEqZeroToCtlzSrl(), combineParity(), combinePMULDQ(), combineSBB(), combineScalarToVector(), combineSelect(), combineSelectAndUseCommutative(), combineSelectOfTwoConstants(), combineSetCC(), combineSext(), combineSextInRegCmov(), combineShiftLeft(), combineShiftRightArithmetic(), combineShiftRightLogical(), combineShuffle(), combineShuffleOfConcatUndef(), combineShuffleOfScalars(), combineShuffleOfSplat(), combineShuffleToFMAddSub(), combineShuffleToVectorExtend(), combineSignExtendInReg(), combineSIntToFP(), combineStore(), combineSub(), combineSubToSubus(), combineToExtendBoolVectorInReg(), combineToExtendCMOV(), combineToExtendVectorInReg(), combineTruncate(), combineTruncatedArithmetic(), combineTruncationShuffle(), combineUIntToFP(), combineVectorCompare(), combineVectorCompareAndMaskUnaryOp(), combineVectorPack(), combineVectorShiftImm(), combineVectorShiftVar(), combineVectorSignBitsTruncation(), combineVectorSizedSetCCEquality(), combineVectorTruncation(), combineVectorTruncationWithPACKSS(), combineVectorTruncationWithPACKUS(), CombineVLDDUP(), CombineVMOVDRRCandidateWithVecOp(), combineVSelectToBLENDV(), combineVSelectWithAllOnesOrZeros(), combineX86SetCC(), combineXor(), combineZext(), llvm::LanaiTargetLowering::computeKnownBitsForTargetNode(), llvm::AArch64TargetLowering::computeKnownBitsForTargetNode(), llvm::ARMTargetLowering::computeKnownBitsForTargetNode(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), ConstantBuildVector(), convertIntLogicToFPLogic(), ConvertSelectToConcatVector(), convertShiftLeftToScale(), llvm::createMSP430ISelDag(), llvm::createR600ISelDag(), llvm::createXCoreISelDag(), llvm::HexagonDAGToDAGISel::DetectUseSxtw(), detectZextAbsDiff(), emitConjunctionRec(), llvm::InstrEmitter::EmitDbgLabel(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), Expand64BitShift(), llvm::TargetLowering::expandABS(), ExpandBITCAST(), ExpandBVWithShuffles(), llvm::TargetLowering::expandMUL(), ExpandREAD_REGISTER(), llvm::PPCTargetLowering::expandVSXLoadForLE(), llvm::PPCTargetLowering::expandVSXStoreForLE(), ExtendUsesToFormExtLoad(), FindBFIToCombineWith(), findChainOperand(), findEXTRHalf(), findUser(), foldAddSubBoolOfMaskedVal(), foldAddSubOfSignBit(), foldBitcastedFPLogic(), llvm::SelectionDAG::FoldConstantArithmetic(), llvm::SelectionDAG::FoldConstantVectorArithmetic(), foldExtendedSignBitTest(), foldFPToIntToFP(), FoldIntToFPToInt(), foldShuffleOfHorizOp(), foldVectorXorShiftIntoCmp(), foldXor1SetCC(), foldXorTruncShiftIntoCmp(), fp16SrcZerosHighBits(), generateEquivalentSub(), GeneratePerfectShuffle(), llvm::PPC::get_VSPLTI_elt(), getARClassRegisterMask(), getARMIndexedAddressParts(), getAsCarry(), getAsNonOpaqueConstant(), getBuildPairElt(), llvm::SelectionDAG::getCommutedVectorShuffle(), getConstantValue(), getContiguousRangeOfSetBits(), getDivRemArgList(), getExpandedMinMaxOps(), getExtendedControlRegister(), GetFPLibCall(), getFPTernOp(), getInputChainForNode(), getIntOperandFromRegisterString(), getIntrinsicID(), getIPMConversion(), getMad64_32(), getOneTrueElt(), llvm::SDValue::getOperand(), llvm::ARMBaseInstrInfo::getOperandLatency(), getOperationName(), getPermuteMask(), llvm::AVRTargetLowering::getPostIndexedAddressParts(), llvm::HexagonTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::AVRTargetLowering::getPreIndexedAddressParts(), getPromotedVectorElementType(), GetPromotionOpcode(), getPTXCmpMode(), getReadPerformanceCounter(), getReadTimeStampCounter(), llvm::AVRTargetLowering::getSetCCResultType(), getShiftAmountTyForConstant(), getShuffleScalarElt(), getSplatConstantFP(), llvm::BuildVectorSDNode::getSplatValue(), getT2IndexedAddressParts(), getTargetConstantFromNode(), getTargetShuffleMask(), getTargetVShiftByConstNode(), getTestBitOperand(), getUnderlyingExtractedFromVec(), getUsefulBitsForUse(), getVCmpInst(), getVectorCompareInfo(), llvm::SelectionDAG::getVectorShuffle(), HandleMergeInputChains(), hasNormalLoadOperand(), hasOnlyLiveInOpers(), hasOnlyLiveOutUses(), hasSingleUsesFromRoot(), haveEfficientBuildVectorPattern(), isADDADDMUL(), isAddSubOrSubAdd(), isAddSubSExt(), isAddSubZExt(), isAllConstantBuildVector(), isBitfieldExtractOp(), isBitfieldExtractOpFromAnd(), isBitfieldExtractOpFromSExtInReg(), isBitfieldExtractOpFromShr(), isBitwiseInverse(), isBooleanFlip(), isBSwapHWordElement(), llvm::ISD::isBuildVectorAllOnes(), llvm::ISD::isBuildVectorAllZeros(), isCalleeLoad(), isClampZeroToOne(), isConditionalZeroOrAllOnes(), isConsecutiveLS(), isConstantOrUndefBUILD_VECTOR(), llvm::BuildVectorSDNode::isConstantSplat(), isContractable(), isCopyFromRegOfInlineAsm(), llvm::AArch64TargetLowering::isDesirableToCommuteWithShift(), isDispSafeForFrameIndex(), isExtendedBUILD_VECTOR(), llvm::TargetLowering::isExtendedTrueVal(), isFloatingPointZero(), isFNEG(), isFPExtLoad(), isFusableLoadOpStorePattern(), llvm::TargetLowering::isGAPlusOffset(), isHopBuildVector(), isHorizontalBinOpPart(), isLegalMaskCompare(), llvm::SelectionDAGISel::IsLegalToFold(), isMemOPCandidate(), isOpcodeHandled(), isOpcWithIntImmediate(), llvm::SelectionDAGISel::isOrEquivalentToAdd(), isPerfectIncrement(), isPermutation(), isSaturatingConditional(), llvm::AMDGPUTargetLowering::isSDNodeAlwaysUniform(), llvm::SITargetLowering::isSDNodeSourceOfDivergence(), isSETCCorConvertedSETCC(), isSetCCOrZExtSetCC(), isSeveralBitsExtractOpFromShr(), IsSingleInstrConstant(), isSlicingProfitable(), isSplatZeroExtended(), isStackPtrRelative(), isTargetConstant(), isTruncateOf(), isVectorAllOnes(), isWordAligned(), isXor1OfSetCC(), llvm::PPC::isXXINSERTWMask(), llvm::PPC::isXXPERMDIShuffleMask(), llvm::PPC::isXXSLDWIShuffleMask(), llvm::SITargetLowering::legalizeTargetIndependentNode(), llvm::HexagonDAGToDAGISel::LoadInstrForLoadIntrinsic(), LowerADDSUBCARRY(), LowerANY_EXTEND(), llvm::SelectionDAGBuilder::LowerAsSTATEPOINT(), lowerAtomicArith(), lowerAtomicArithWithLOCK(), LowerAVXExtend(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorToBitOp(), LowerBuildVectorv4x32(), lowerCallFromStatepointLoweringInfo(), LowerCTPOP(), LowerCTTZ(), lowerDSPIntr(), LowerEXTEND_VECTOR_INREG(), lowerFCMPIntrinsic(), lowerICMPIntrinsic(), LowerInterruptReturn(), LowerINTRINSIC_W_CHAIN(), llvm::MSP430TargetLowering::LowerJumpTable(), LowerMGATHER(), lowerMSABinaryBitImmIntr(), lowerMSABitClear(), lowerMSABitClearImm(), lowerMSACopyIntr(), lowerMSALoadIntr(), lowerMSASplatZExt(), lowerMSAStoreIntr(), llvm::LanaiTargetLowering::LowerMUL(), LowerMULH(), llvm::NVPTXTargetLowering::LowerOperation(), llvm::SystemZTargetLowering::LowerOperationWrapper(), LowerShift(), llvm::MSP430TargetLowering::LowerShifts(), LowerSIGN_EXTEND(), LowerSIGN_EXTEND_Mask(), LowerToHorizontalOp(), lowerUINT_TO_FP_vXi32(), LowerVECTOR_SHUFFLE(), lowerVECTOR_SHUFFLE_SHF(), lowerVECTOR_SHUFFLE_VSHF(), LowerVectorAllZeroTest(), lowerVectorShuffleAsBroadcast(), LowerWRITE_REGISTER(), lowerX86CmpEqZeroToCtlzSrl(), lowerX86FPLogicOp(), LowerZERO_EXTEND_Mask(), maskMatters(), llvm::BaseIndexOffset::match(), llvm::SelectionDAG::matchBinOpReduction(), matchLogicBlend(), matchPMADDWD(), mayTailCallThisCC(), mayUseP9Setb(), minMaxOpcToMin3Max3Opc(), narrowExtractedVectorBinOp(), narrowExtractedVectorLoad(), NarrowVector(), nodesHaveSameOperandValue(), numVectorEltsOrZero(), operator!=(), llvm::SDNodeIterator::operator*(), llvm::TargetLowering::parametersInCSRMatch(), ParseBFI(), partitionShuffleOfConcats(), Passv64i1ArgInRegs(), PeepholePPC64ZExtGather(), performADDCombine(), PerformADDCombine(), PerformAddcSubcCombine(), PerformAddeSubeCombine(), performAddSubLongCombine(), performANDCombine(), PerformANDCombine(), PerformARMBUILD_VECTORCombine(), llvm::AMDGPUTargetLowering::performAssertSZExtCombine(), PerformBFICombine(), llvm::SparcTargetLowering::PerformBITCASTCombine(), performBitcastCombine(), llvm::ARMTargetLowering::PerformBRCONDCombine(), performBRCONDCombine(), PerformBUILD_VECTORCombine(), llvm::ARMTargetLowering::PerformCMOVCombine(), performCMovFPCombine(), llvm::ARMTargetLowering::PerformCMOVToBFICombine(), performConcatVectorsCombine(), performCONDCombine(), llvm::R600TargetLowering::PerformDAGCombine(), llvm::RISCVTargetLowering::PerformDAGCombine(), llvm::AMDGPUTargetLowering::PerformDAGCombine(), llvm::AArch64TargetLowering::PerformDAGCombine(), llvm::ARMTargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PerformDAGCombine(), llvm::PPCTargetLowering::PerformDAGCombine(), performDivRemCombine(), performDSPShiftCombine(), performExtendCombine(), PerformExtendCombine(), llvm::AMDGPUTargetLowering::performFAbsCombine(), performFDivCombine(), llvm::AMDGPUTargetLowering::performFNegCombine(), performFpToIntCombine(), performGlobalAddressCombine(), PerformInsertEltCombine(), performIntegerAbsCombine(), performIntrinsicCombine(), PerformIntrinsicCombine(), performIntToFpCombine(), performMADD_MSUBCombine(), llvm::AMDGPUTargetLowering::performMulCombine(), performMULCombine(), performMulCombine(), PerformMULCombine(), llvm::AMDGPUTargetLowering::performMulhsCombine(), llvm::AMDGPUTargetLowering::performMulhuCombine(), llvm::AMDGPUTargetLowering::performMulLoHi24Combine(), performNEONPostLDSTCombine(), performNVCASTCombine(), performORCombine(), PerformORCombine(), PerformORCombineToBFI(), PerformORCombineToSMULWBT(), performPostLD1Combine(), llvm::AMDGPUTargetLowering::performRcpCombine(), PerformREMCombine(), llvm::AMDGPUTargetLowering::performSelectCombine(), performSELECTCombine(), performSelectCombine(), performSetccAddFolding(), performSETCCCombine(), PerformSETCCCombine(), PerformShiftCombine(), llvm::AMDGPUTargetLowering::performShlCombine(), performSHLCombine(), PerformSHLSimplify(), llvm::AMDGPUTargetLowering::performSraCombine(), performSRACombine(), llvm::AMDGPUTargetLowering::performSrlCombine(), performSRLCombine(), performSTORECombine(), PerformSTORECombine(), PerformSUBCombine(), performTBZCombine(), llvm::AMDGPUTargetLowering::performTruncateCombine(), PerformUMLALCombine(), PerformVCVTCombine(), PerformVDIVCombine(), PerformVDUPCombine(), PerformVDUPLANECombine(), PerformVECTOR_SHUFFLECombine(), performVectorCompareAndMaskUnaryOpCombine(), PerformVMOVDRRCombine(), PerformVMOVRRDCombine(), PerformVMULCombine(), performVSELECTCombine(), performVSelectCombine(), performXORCombine(), performXorCombine(), pickOpcodeForVT(), PrepareCall(), promoteExtBeforeAdd(), PromoteMaskArithmetic(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), reduceBuildVecToShuffleWithZero(), reduceVMULWidth(), ReplaceBITCASTResults(), ReplaceCMP_SWAP_128Results(), ReplaceCMP_SWAP_64Results(), replaceInChain(), ReplaceINTRINSIC_W_CHAIN(), ReplaceLongIntrinsic(), llvm::R600TargetLowering::ReplaceNodeResults(), llvm::AVRTargetLowering::ReplaceNodeResults(), llvm::HexagonTargetLowering::ReplaceNodeResults(), llvm::SparcTargetLowering::ReplaceNodeResults(), llvm::SITargetLowering::ReplaceNodeResults(), llvm::PPCTargetLowering::ReplaceNodeResults(), llvm::X86TargetLowering::ReplaceNodeResults(), ReplaceREADCYCLECOUNTER(), replaceShuffleOfInsert(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), llvm::SelectionDAG::salvageDebugInfo(), scalarizeExtractedBinop(), llvm::ResourcePriorityQueue::scheduledNode(), llvm::HexagonDAGToDAGISel::SelectAddSubCarry(), llvm::HexagonDAGToDAGISel::SelectBrevLdIntrinsic(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::HexagonDAGToDAGISel::SelectD2P(), llvm::HexagonDAGToDAGISel::SelectHVXDualOutput(), selectI64Imm(), llvm::AVRDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWChain(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWOChain(), llvm::HexagonDAGToDAGISel::SelectNewCircIntrinsic(), llvm::HexagonDAGToDAGISel::SelectP2D(), llvm::HexagonDAGToDAGISel::SelectQ2V(), llvm::HvxSelector::selectRor(), llvm::HexagonDAGToDAGISel::SelectSHL(), llvm::HvxSelector::selectShuffle(), llvm::HexagonDAGToDAGISel::SelectTypecast(), llvm::HexagonDAGToDAGISel::SelectV2Q(), llvm::HexagonDAGToDAGISel::SelectV65Gather(), llvm::HexagonDAGToDAGISel::SelectV65GatherPred(), llvm::HexagonDAGToDAGISel::SelectVAlign(), llvm::HvxSelector::selectVAlign(), llvm::HexagonDAGToDAGISel::SelectVAlignAddr(), ShrinkLoadReplaceStoreWithStore(), simplifyDivRem(), simplifyI24(), llvm::TargetLowering::SimplifySetCC(), skipExtensionForVectorMULL(), SkipExtensionForVMULL(), llvm::SelectionDAG::SplitVectorOperand(), SplitVSETCC(), llvm::HexagonDAGToDAGISel::StoreInstrForLoadIntrinsic(), stripModuloOnShift(), truncateVecElts(), tryBitfieldInsertOpFromOr(), tryBitfieldInsertOpFromOrAndImm(), tryBuildVectorByteMask(), tryBuildVectorShuffle(), tryCombineCRC32(), tryCombineFixedPointConvert(), tryCombineLongOpWithDup(), tryCombineShiftImm(), tryCombineToBSL(), tryCombineToEXTR(), tryFoldToZero(), llvm::HexagonDAGToDAGISel::tryLoadOfLoadIntrinsic(), tryLowerToSLI(), TryMULWIDECombine(), tryToFoldExtendOfConstant(), llvm::X86InstrInfo::unfoldMemoryOperand(), llvm::SelectionDAG::UnrollVectorOp(), llvm::X86TargetLowering::unwrapAddress(), llvm::SelectionDAG::UpdateNodeOperands(), useSinCos(), vectorEltWillFoldAway(), VerifySDNode(), visitFMinMax(), WinDBZCheckDenominator(), and XFormVExtractWithShuffleIntoLoad().

◆ getOperationName()

| std::string SDNode::getOperationName | ( | const SelectionDAG * | G = nullptr | ) | const |

Return the opcode of this operation for printing.

Definition at line 60 of file SelectionDAGDumper.cpp.

References llvm::ISD::ABS, llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::ADDCARRY, llvm::ISD::ADDE, llvm::ISD::ADDROFRETURNADDR, llvm::ISD::ADDRSPACECAST, llvm::ISD::ADJUST_TRAMPOLINE, llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::ISD::ANY_EXTEND_VECTOR_INREG, llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS, llvm::ISD::ATOMIC_FENCE, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_LOAD_ADD, llvm::ISD::ATOMIC_LOAD_AND, llvm::ISD::ATOMIC_LOAD_CLR, llvm::ISD::ATOMIC_LOAD_MAX, llvm::ISD::ATOMIC_LOAD_MIN, llvm::ISD::ATOMIC_LOAD_NAND, llvm::ISD::ATOMIC_LOAD_OR, llvm::ISD::ATOMIC_LOAD_SUB, llvm::ISD::ATOMIC_LOAD_UMAX, llvm::ISD::ATOMIC_LOAD_UMIN, llvm::ISD::ATOMIC_LOAD_XOR, llvm::ISD::ATOMIC_STORE, llvm::ISD::ATOMIC_SWAP, llvm::ISD::BasicBlock, llvm::ISD::BITCAST, llvm::ISD::BITREVERSE, llvm::ISD::BlockAddress, llvm::ISD::BR, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRCOND, llvm::ISD::BRIND, llvm::ISD::BSWAP, llvm::ISD::BUILD_PAIR, llvm::ISD::BUILD_VECTOR, llvm::ISD::BUILTIN_OP_END, llvm::ISD::CALLSEQ_END, llvm::ISD::CALLSEQ_START, llvm::ISD::CARRY_FALSE, llvm::ISD::CATCHRET, llvm::ISD::CLEANUPRET, llvm::ISD::CONCAT_VECTORS, llvm::ISD::CONDCODE, llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::ISD::ConstantPool, llvm::ISD::CopyFromReg, llvm::ISD::CopyToReg, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::ISD::DEBUGTRAP, llvm::ISD::DELETED_NODE, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_DWARF_CFA, llvm::ISD::EH_LABEL, llvm::ISD::EH_RETURN, llvm::ISD::EH_SJLJ_LONGJMP, llvm::ISD::EH_SJLJ_SETJMP, llvm::ISD::EH_SJLJ_SETUP_DISPATCH, llvm::ISD::EntryToken, llvm::ISD::ExternalSymbol, llvm::ISD::EXTRACT_ELEMENT, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCANONICALIZE, llvm::ISD::FCBRT, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::ISD::FGETSIGN, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FLT_ROUNDS_, llvm::ISD::FMA, llvm::ISD::FMAD, llvm::ISD::FMAXIMUM, llvm::ISD::FMAXNUM, llvm::ISD::FMAXNUM_IEEE, llvm::ISD::FMINIMUM, llvm::ISD::FMINNUM, llvm::ISD::FMINNUM_IEEE, llvm::ISD::FMUL, llvm::ISD::FNEARBYINT, llvm::ISD::FNEG, llvm::ISD::FP16_TO_FP, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_ROUND_INREG, llvm::ISD::FP_TO_FP16, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FPOW, llvm::ISD::FPOWI, llvm::ISD::FRAME_TO_ARGS_OFFSET, llvm::ISD::FRAMEADDR, llvm::ISD::FrameIndex, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FSHL, llvm::ISD::FSHR, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::ISD::FTRUNC, llvm::ISD::GC_TRANSITION_END, llvm::ISD::GC_TRANSITION_START, llvm::ISD::GET_DYNAMIC_AREA_OFFSET, llvm::TargetSubtargetInfo::getInstrInfo(), llvm::TargetMachine::getIntrinsicInfo(), getMachineOpcode(), llvm::Intrinsic::getName(), getOpcode(), getOperand(), llvm::SelectionDAG::getSubtarget(), llvm::SelectionDAG::getTarget(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::TargetLowering::getTargetNodeName(), llvm::ISD::GLOBAL_OFFSET_TABLE, llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ISD::HANDLENODE, llvm::ISD::INIT_TRAMPOLINE, llvm::ISD::INLINEASM, llvm::ISD::INSERT_SUBVECTOR, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, isMachineOpcode(), llvm::ISD::JumpTable, llvm::ISD::LIFETIME_END, llvm::ISD::LIFETIME_START, llvm_unreachable, llvm::ISD::LOAD, llvm::ISD::LOCAL_RECOVER, llvm::ISD::MCSymbol, llvm::ISD::MDNODE_SDNODE, llvm::ISD::MERGE_VALUES, llvm::ISD::MGATHER, llvm::ISD::MLOAD, llvm::ISD::MSCATTER, llvm::ISD::MSTORE, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, Name, llvm::None, llvm::Intrinsic::num_intrinsics, llvm::ISD::OR, llvm::ISD::PCMARKER, llvm::ISD::PREFETCH, llvm::ISD::READ_REGISTER, llvm::ISD::READCYCLECOUNTER, llvm::ISD::Register, llvm::ISD::RegisterMask, llvm::ISD::RETURNADDR, llvm::ISD::ROTL, llvm::ISD::ROTR, llvm::ISD::SADDO, llvm::ISD::SADDSAT, llvm::ISD::SCALAR_TO_VECTOR, llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::ISD::SETCCCARRY, llvm::ISD::SETEQ, llvm::ISD::SETFALSE, llvm::ISD::SETFALSE2, llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETLE, llvm::ISD::SETLT, llvm::ISD::SETNE, llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::ISD::SETONE, llvm::ISD::SETTRUE, llvm::ISD::SETTRUE2, llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETULE, llvm::ISD::SETULT, llvm::ISD::SETUNE, llvm::ISD::SETUO, llvm::ISD::SHL, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SIGN_EXTEND_VECTOR_INREG, llvm::ISD::SINT_TO_FP, llvm::ISD::SMAX, llvm::ISD::SMIN, llvm::ISD::SMUL_LOHI, llvm::ISD::SMULFIX, llvm::ISD::SMULO, llvm::ISD::SPONENTRY, llvm::ISD::SRA, llvm::ISD::SRA_PARTS, llvm::ISD::SRCVALUE, llvm::ISD::SREM, llvm::ISD::SRL, llvm::ISD::SRL_PARTS, llvm::ISD::SSUBO, llvm::ISD::SSUBSAT, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::STORE, llvm::ISD::STRICT_FADD, llvm::ISD::STRICT_FCEIL, llvm::ISD::STRICT_FCOS, llvm::ISD::STRICT_FDIV, llvm::ISD::STRICT_FEXP, llvm::ISD::STRICT_FEXP2, llvm::ISD::STRICT_FFLOOR, llvm::ISD::STRICT_FLOG, llvm::ISD::STRICT_FLOG10, llvm::ISD::STRICT_FLOG2, llvm::ISD::STRICT_FMA, llvm::ISD::STRICT_FMAXNUM, llvm::ISD::STRICT_FMINNUM, llvm::ISD::STRICT_FMUL, llvm::ISD::STRICT_FNEARBYINT, llvm::ISD::STRICT_FPOW, llvm::ISD::STRICT_FPOWI, llvm::ISD::STRICT_FREM, llvm::ISD::STRICT_FRINT, llvm::ISD::STRICT_FROUND, llvm::ISD::STRICT_FSIN, llvm::ISD::STRICT_FSQRT, llvm::ISD::STRICT_FSUB, llvm::ISD::STRICT_FTRUNC, llvm::ISD::SUB, llvm::ISD::SUBC, llvm::ISD::SUBCARRY, llvm::ISD::SUBE, llvm::ISD::TargetBlockAddress, llvm::ISD::TargetConstant, llvm::ISD::TargetConstantFP, llvm::ISD::TargetConstantPool, llvm::ISD::TargetExternalSymbol, llvm::ISD::TargetFrameIndex, llvm::ISD::TargetGlobalAddress, llvm::ISD::TargetGlobalTLSAddress, llvm::ISD::TargetIndex, llvm::ISD::TargetJumpTable, TII, llvm::ISD::TokenFactor, llvm::ISD::TRAP, llvm::ISD::TRUNCATE, llvm::ISD::UADDO, llvm::ISD::UADDSAT, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::ISD::UMAX, llvm::ISD::UMIN, llvm::ISD::UMUL_LOHI, llvm::ISD::UMULO, llvm::ISD::UNDEF, llvm::ISD::UREM, llvm::ISD::USUBO, llvm::ISD::USUBSAT, llvm::utostr(), llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, llvm::ISD::VALUETYPE, llvm::ISD::VASTART, llvm::ISD::VECREDUCE_ADD, llvm::ISD::VECREDUCE_AND, llvm::ISD::VECREDUCE_FADD, llvm::ISD::VECREDUCE_FMAX, llvm::ISD::VECREDUCE_FMIN, llvm::ISD::VECREDUCE_FMUL, llvm::ISD::VECREDUCE_MUL, llvm::ISD::VECREDUCE_OR, llvm::ISD::VECREDUCE_SMAX, llvm::ISD::VECREDUCE_SMIN, llvm::ISD::VECREDUCE_STRICT_FADD, llvm::ISD::VECREDUCE_STRICT_FMUL, llvm::ISD::VECREDUCE_UMAX, llvm::ISD::VECREDUCE_UMIN, llvm::ISD::VECREDUCE_XOR, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, llvm::ISD::WRITE_REGISTER, llvm::ISD::XOR, llvm::ISD::ZERO_EXTEND, and llvm::ISD::ZERO_EXTEND_VECTOR_INREG.

◆ getSDVTList()

Definition at line 1049 of file SelectionDAGNodes.h.

References llvm::MipsISD::Ret.

◆ getSimpleValueType()

Return the type of a specified result as a simple type.

Definition at line 973 of file SelectionDAGNodes.h.

Referenced by llvm::ScheduleDAGSDNodes::RegDefIter::Advance(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), CalcNodeSethiUllmanNumber(), canClobberPhysRegDefs(), CheckForPhysRegDependency(), checkV64LaneV128(), combineADC(), combineAndnp(), combineANDXORWithAllOnesIntoANDNP(), combineBasicSADPattern(), combineCompareEqual(), combineExtractSubvector(), combineInsertSubvector(), combineMOVMSK(), combineOrCmpEqZeroToCtlzSrl(), combineSBB(), combineShuffleToAddSubOrFMAddSub(), combineShuffleToFMAddSub(), combineVectorCompare(), ExpandBVWithShuffles(), getDivRemArgList(), getHopForBuildVector(), getIntOperandFromRegisterString(), getPhysicalRegisterVT(), getPromotedVectorElementType(), isAddSubOrSubAdd(), isCalleeLoad(), isHopBuildVector(), isOperandOf(), isSinCosLibcallAvailable(), isSplatZeroExtended(), isStackPtrRelative(), LowerADDSUBCARRY(), lowerAtomicArith(), lowerAtomicArithWithLOCK(), LowerAVXExtend(), lowerBuildVectorAsBroadcast(), lowerBuildVectorToBitOp(), LowerEXTEND_VECTOR_INREG(), LowerFPOWI(), LowerSIGN_EXTEND(), LowerSIGN_EXTEND_Mask(), lowerToAddSubOrFMAddSub(), LowerToHorizontalOp(), lowerUINT_TO_FP_vXi32(), lowerX86FPLogicOp(), LowerZERO_EXTEND_Mask(), mayUseP9Setb(), performAddSubLongCombine(), llvm::SparcTargetLowering::PerformBITCASTCombine(), performFDivCombine(), performFpToIntCombine(), PerformVCVTCombine(), PerformVDIVCombine(), pickOpcodeForVT(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::ResourcePriorityQueue::scheduledNode(), ShrinkLoadReplaceStoreWithStore(), tryCombineShiftImm(), and useSinCos().

◆ getValueSizeInBits()

Returns MVT::getSizeInBits(getValueType(ResNo)).

Definition at line 978 of file SelectionDAGNodes.h.

Referenced by generateEquivalentSub(), llvm::isAllOnesOrAllOnesSplat(), llvm::isOneOrOneSplat(), isSlicingProfitable(), and numVectorEltsOrZero().

◆ getValueType()

Return the type of a specified result.

Definition at line 967 of file SelectionDAGNodes.h.

References assert().

Referenced by AddCombineBUILD_VECTORToVPADDL(), AddCombineToVPADD(), AddCombineVUZPToVPADDL(), AddGlue(), llvm::MipsSETargetLowering::addMSAFloatType(), AddNodeIDCustom(), addShuffleForVecExtend(), adjustForSubtraction(), adjustLoadValueTypeImpl(), llvm::AMDGPUTargetLowering::allUsesHaveSourceMods(), llvm::SelectionDAG::areNonVolatileConsecutiveLoads(), BuildExactSDIV(), llvm::ScheduleDAGSDNodes::BuildSchedGraph(), llvm::TargetLowering::BuildSDIV(), llvm::PPCTargetLowering::BuildSDIVPow2(), llvm::TargetLowering::BuildSDIVPow2(), llvm::TargetLowering::BuildUDIV(), calculateByteProvider(), CanCombineFCOPYSIGN_EXTEND_ROUND(), canFoldInAddressingMode(), canLowerToLDG(), checkV64LaneV128(), CollectOpsToWiden(), combineAcrossLanesIntrinsic(), combineADC(), combineAdd(), combineAddOrSubToADCOrSBB(), combineADDToADDZE(), combineAddToSUBUS(), combineAnd(), combineAndMaskToShift(), CombineANDShift(), CombineBaseUpdate(), combineBEXTR(), combineBitcast(), combineBitcastvxi1(), combineBVOfConsecutiveLoads(), combineBVOfVecSExt(), combineCastedMaskArithmetic(), combineCCMask(), combineCMov(), combineConcatVectorOfExtracts(), combineConcatVectorOfScalars(), combineExtractSubvector(), combineExtractVectorElt(), combineExtractWithShuffle(), combineExtSetcc(), combineFaddFsub(), combineFAndFNotToFAndn(), combineFMA(), combineFMADDSUB(), combineFMinFMax(), combineFMinNumFMaxNum(), combineFneg(), combineHorizontalMinMaxResult(), combineHorizontalPredicateResult(), combineIncDecVector(), combineLoad(), combineLogicBlendIntoPBLENDV(), combineLoopMAddPattern(), combineLoopSADPattern(), combineMaskedLoad(), combineMaskedLoadConstantMask(), combineMinNumMaxNum(), combineMOVMSK(), combineMul(), combineMulToPMADDWD(), combineMulToPMULDQ(), combineOr(), combineOrCmpEqZeroToCtlzSrl(), combineParity(), combinePMULDQ(), combineScalarToVector(), combineSelect(), combineSelectAndUse(), combineSelectOfTwoConstants(), combineSetCC(), combineSext(), combineSextInRegCmov(), combineShuffle(), combineShuffleOfConcatUndef(), combineShuffleOfScalars(), combineShuffleOfSplat(), combineShuffleToVectorExtend(), combineSignExtendInReg(), combineSIntToFP(), combineSub(), combineSubToSubus(), combineToExtendBoolVectorInReg(), combineToExtendCMOV(), combineToExtendVectorInReg(), combineTruncate(), combineTruncatedArithmetic(), combineTruncationShuffle(), combineUIntToFP(), combineVectorCompareAndMaskUnaryOp(), combineVectorInsert(), combineVectorPack(), combineVectorShiftImm(), combineVectorShiftVar(), combineVectorSignBitsTruncation(), combineVectorSizedSetCCEquality(), combineVectorTruncation(), combineVectorTruncationWithPACKSS(), combineVectorTruncationWithPACKUS(), CombineVLDDUP(), CombineVMOVDRRCandidateWithVecOp(), combineVSelectToBLENDV(), combineX86INT_TO_FP(), combineXor(), combineZext(), ConvertCarryFlagToBooleanCarry(), convertIntLogicToFPLogic(), ConvertSelectToConcatVector(), createLoadLR(), doNotCSE(), EltsFromConsecutiveLoads(), llvm::InstrEmitter::EmitDbgLabel(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), Expand64BitShift(), llvm::TargetLowering::expandABS(), ExpandBITCAST(), ExpandBVWithShuffles(), expandf64Toi32(), llvm::TargetLowering::expandMUL(), ExpandREAD_REGISTER(), llvm::TargetLowering::expandUnalignedLoad(), llvm::PPCTargetLowering::expandVSXLoadForLE(), ExtendUsesToFormExtLoad(), findUser(), foldBitcastedFPLogic(), llvm::SelectionDAG::FoldConstantArithmetic(), foldExtendedSignBitTest(), foldFPToIntToFP(), FoldIntToFPToInt(), foldVectorXorShiftIntoCmp(), foldXorTruncShiftIntoCmp(), fp16SrcZerosHighBits(), generateEquivalentSub(), getAArch64XALUOOp(), getARMIndexedAddressParts(), llvm::SelectionDAG::getCommutedVectorShuffle(), getConstantValue(), getContiguousRangeOfSetBits(), getDivRemArgList(), llvm::HexagonTargetLowering::GetDynamicTLSAddr(), getExpandedMinMaxOps(), GetFPLibCall(), getFPTernOp(), getIPMConversion(), getLoadExtOrTrunc(), getMad64_32(), llvm::SelectionDAG::getMaskedGather(), llvm::SelectionDAG::getMaskedScatter(), getMOVL(), getOneTrueElt(), getPermuteMask(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), getPromotedVectorElementType(), GetPromotionOpcode(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::AVRTargetLowering::getSetCCResultType(), getShiftAmountTyForConstant(), getSplatConstantFP(), getT2IndexedAddressParts(), getTestBitOperand(), GetTLSADDR(), llvm::SDValue::getValueType(), hasNormalLoadOperand(), hasOnlySelectUsers(), haveEfficientBuildVectorPattern(), isADDADDMUL(), isAddSubOrSubAdd(), isAllConstantBuildVector(), isAnyConstantBuildVector(), isBitfieldExtractOp(), isBitfieldExtractOpFromAnd(), isBitfieldExtractOpFromSExtInReg(), isBitfieldExtractOpFromShr(), isBooleanFlip(), isBSwapHWordElement(), llvm::ISD::isBuildVectorAllOnes(), llvm::ISD::isBuildVectorAllZeros(), isCalleeLoad(), isClampZeroToOne(), isConditionalZeroOrAllOnes(), llvm::BuildVectorSDNode::isConstantSplat(), llvm::ISD::isConstantSplatVector(), llvm::TargetLowering::isConstFalseVal(), llvm::isConstOrConstSplat(), isConstOrDemandedConstSplat(), llvm::TargetLowering::isConstTrueVal(), isContractable(), llvm::AArch64TargetLowering::isDesirableToCommuteWithShift(), isExtendedBUILD_VECTOR(), llvm::TargetLowering::isExtendedTrueVal(), isFloatingPointZero(), isFNEG(), isFPExtLoad(), isHorizontalBinOpPart(), isInt32Immediate(), isInt64Immediate(), llvm::isIntS16Immediate(), llvm::SelectionDAGISel::IsLegalToFold(), isMemOPCandidate(), isOpcWithIntImmediate(), isPerfectIncrement(), llvm::PPC::isQVALIGNIShuffleMask(), isSETCCorConvertedSETCC(), isSeveralBitsExtractOpFromShr(), isSlicingProfitable(), llvm::PPC::isSplatShuffleMask(), isTargetConstant(), isTruncateOf(), isVMerge(), llvm::PPC::isVSLDOIShuffleMask(), IsVUZPShuffleNode(), isWordAligned(), isXXBRShuffleMaskHelper(), llvm::PPC::isXXPERMDIShuffleMask(), llvm::PPC::isXXSLDWIShuffleMask(), LowerADDSUBCARRY(), llvm::X86TargetLowering::LowerAsmOperandForConstraint(), LowerCTPOP(), LowerCTTZ(), lowerDSPIntr(), LowerDYNAMIC_STACKALLOC(), LowerEXTRACT_VECTOR_ELT_SSE4(), lowerFCMPIntrinsic(), lowerICMPIntrinsic(), LowerINTRINSIC_W_CHAIN(), lowerMSABinaryBitImmIntr(), lowerMSABitClear(), lowerMSABitClearImm(), lowerMSACopyIntr(), lowerMSALoadIntr(), lowerMSASplatImm(), lowerMSASplatZExt(), lowerMSAStoreIntr(), llvm::LanaiTargetLowering::LowerMUL(), llvm::SystemZTargetLowering::LowerOperationWrapper(), LowerShift(), llvm::MipsTargetLowering::lowerSTORE(), LowerToTLSExecModel(), LowerToTLSLocalDynamicModel(), LowerXOR(), maskMatters(), mayTailCallThisCC(), mayUseP9Setb(), minMaxOpcToMin3Max3Opc(), narrowExtractedVectorBinOp(), narrowExtractedVectorLoad(), NarrowVector(), numVectorEltsOrZero(), partitionShuffleOfConcats(), performADDCombine(), performANDCombine(), PerformANDCombine(), PerformARMBUILD_VECTORCombine(), llvm::AMDGPUTargetLowering::performAssertSZExtCombine(), PerformBFICombine(), performBitcastCombine(), llvm::ARMTargetLowering::PerformBRCONDCombine(), PerformBUILD_VECTORCombine(), llvm::ARMTargetLowering::PerformCMOVCombine(), performConcatVectorsCombine(), performCONDCombine(), llvm::R600TargetLowering::PerformDAGCombine(), llvm::RISCVTargetLowering::PerformDAGCombine(), llvm::AMDGPUTargetLowering::PerformDAGCombine(), llvm::ARMTargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PerformDAGCombine(), llvm::PPCTargetLowering::PerformDAGCombine(), performDivRemCombine(), performExtendCombine(), PerformExtendCombine(), llvm::AMDGPUTargetLowering::performFAbsCombine(), llvm::AMDGPUTargetLowering::performFNegCombine(), performFpToIntCombine(), PerformInsertEltCombine(), performIntegerAbsCombine(), performIntrinsicCombine(), PerformIntrinsicCombine(), performIntToFpCombine(), PerformLOADCombine(), performMADD_MSUBCombine(), llvm::AMDGPUTargetLowering::performMulCombine(), performMULCombine(), performMulCombine(), PerformMULCombine(), llvm::AMDGPUTargetLowering::performMulhsCombine(), llvm::AMDGPUTargetLowering::performMulhuCombine(), performNEONPostLDSTCombine(), performNVCASTCombine(), performORCombine(), PerformORCombine(), PerformORCombineToBFI(), performPostLD1Combine(), llvm::AMDGPUTargetLowering::performRcpCombine(), PerformREMCombine(), llvm::AMDGPUTargetLowering::performSelectCombine(), performSelectCombine(), performSetccAddFolding(), performSETCCCombine(), PerformSETCCCombine(), PerformShiftCombine(), llvm::AMDGPUTargetLowering::performShlCombine(), performSHLCombine(), llvm::AMDGPUTargetLowering::performSraCombine(), performSRACombine(), llvm::AMDGPUTargetLowering::performSrlCombine(), performSRLCombine(), performSUBCombine(), llvm::AMDGPUTargetLowering::performTruncateCombine(), PerformVCVTCombine(), PerformVDIVCombine(), PerformVDUPCombine(), PerformVDUPLANECombine(), PerformVECTOR_SHUFFLECombine(), performVectorCompareAndMaskUnaryOpCombine(), PerformVMOVDRRCombine(), PerformVMOVRRDCombine(), PerformVMULCombine(), performVSELECTCombine(), performVSelectCombine(), performXORCombine(), performXorCombine(), PerformXORCombine(), pickOpcodeForVT(), print_types(), promoteExtBeforeAdd(), PromoteMaskArithmetic(), recoverFramePointer(), reduceBuildVecToShuffleWithZero(), reduceMaskedLoadToScalarLoad(), RemoveUnusedGlue(), ReorganizeVector(), llvm::SelectionDAG::ReplaceAllUsesWith(), ReplaceBITCASTResults(), ReplaceCMP_SWAP_128Results(), ReplaceCMP_SWAP_64Results(), ReplaceINTRINSIC_W_CHAIN(), ReplaceLoadVector(), llvm::R600TargetLowering::ReplaceNodeResults(), llvm::AVRTargetLowering::ReplaceNodeResults(), llvm::HexagonTargetLowering::ReplaceNodeResults(), llvm::SparcTargetLowering::ReplaceNodeResults(), llvm::SITargetLowering::ReplaceNodeResults(), llvm::PPCTargetLowering::ReplaceNodeResults(), llvm::X86TargetLowering::ReplaceNodeResults(), ReplaceReductionResults(), replaceShuffleOfInsert(), resolveBuildVector(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), scalarizeExtractedBinop(), llvm::TargetLowering::scalarizeVectorLoad(), llvm::PPCTargetLowering::SelectAddressRegImm(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::HexagonDAGToDAGISel::SelectConstant(), llvm::HexagonDAGToDAGISel::SelectConstantFP(), llvm::HexagonDAGToDAGISel::SelectD2P(), selectI64Imm(), llvm::HexagonDAGToDAGISel::SelectIndexedLoad(), llvm::AVRDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWOChain(), llvm::HexagonDAGToDAGISel::SelectP2D(), llvm::HexagonDAGToDAGISel::SelectQ2V(), llvm::HvxSelector::selectRor(), llvm::HexagonDAGToDAGISel::SelectSHL(), llvm::HvxSelector::selectShuffle(), llvm::HexagonDAGToDAGISel::SelectV2Q(), llvm::HexagonDAGToDAGISel::SelectVAlign(), llvm::HvxSelector::selectVAlign(), llvm::AMDGPUTargetLowering::shouldReduceLoadWidth(), llvm::X86InstrInfo::shouldScheduleLoadsNear(), ShrinkLoadReplaceStoreWithStore(), simplifyDivRem(), skipExtensionForVectorMULL(), SkipExtensionForVMULL(), SplitVSETCC(), stripModuloOnShift(), truncateVecElts(), tryBitfieldInsertOpFromOr(), tryBitfieldInsertOpFromOrAndImm(), tryBuildVectorByteMask(), tryBuildVectorShuffle(), tryCombineFixedPointConvert(), tryCombineLongOpWithDup(), tryCombineShiftImm(), tryCombineToBSL(), tryCombineToEXTR(), tryFoldToZero(), tryLowerToSLI(), TryMULWIDECombine(), tryToFoldExtendOfConstant(), llvm::X86InstrInfo::unfoldMemoryOperand(), llvm::SelectionDAG::UnrollVectorOp(), useSinCos(), vectorEltWillFoldAway(), VerifySDNode(), visitFMinMax(), WinDBZCheckDenominator(), and XFormVExtractWithShuffleIntoLoad().

◆ getVTList()

|

inline |

Definition at line 932 of file SelectionDAGNodes.h.

References X.

Referenced by AddNodeIDNode(), combineAddOrSubToADCOrSBB(), combineBrCond(), ConvertSelectToConcatVector(), llvm::createR600ISelDag(), emitIntrinsicWithCC(), findUser(), getAsCarry(), getCCResult(), getConstantValue(), getContiguousRangeOfSetBits(), getFPTernOp(), getMad64_32(), isBooleanFlip(), isOpcWithIntImmediate(), isStackPtrRelative(), llvm::HexagonTargetLowering::LowerAddSubCarry(), LowerADDSUBCARRY(), LowerINTRINSIC_W_CHAIN(), LowerXALUO(), parseTexFail(), PeepholePPC64ZExtGather(), PerformAddcSubcCombine(), PerformAddeSubeCombine(), performANDCombine(), llvm::R600TargetLowering::PerformDAGCombine(), performSRACombine(), pickOpcodeForVT(), llvm::R600TargetLowering::ReplaceNodeResults(), llvm::HexagonDAGToDAGISel::SelectAddSubCarry(), simplifyDivRem(), simplifyI24(), tryFoldToZero(), and VerifySDNode().

◆ hasAnyUseOfValue()

Return true if there are any use of the indicated value.

hasAnyUseOfValue - Return true if there are any use of the indicated value.

This method ignores uses of other values defined by this operation.

Definition at line 8735 of file SelectionDAG.cpp.

References assert(), E, getNumValues(), use_begin(), and use_end().

Referenced by AddCombineTo64bitMLAL(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::ScheduleDAGSDNodes::RegDefIter::Advance(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), CalcNodeSethiUllmanNumber(), canClobberPhysRegDefs(), checkBoolTestSetCCCombine(), combineSetCCAtomicArith(), llvm::InstrEmitter::EmitDbgLabel(), getAsCarry(), isBooleanFlip(), isCalleeLoad(), isTruncateOf(), lowerAtomicArith(), llvm::SelectionDAG::makeEquivalentMemoryOrdering(), numVectorEltsOrZero(), performDivRemCombine(), RemoveUnusedGlue(), llvm::SelectionDAG::ReplaceAllUsesWith(), replaceShuffleOfInsert(), simplifyDivRem(), tryFoldToZero(), and llvm::SDValue::use_empty().

◆ hasNUsesOfValue()

Return true if there are exactly NUSES uses of the indicated value.

hasNUsesOfValue - Return true if there are exactly NUSES uses of the indicated value.

This method ignores uses of other values defined by this operation.

Definition at line 8717 of file SelectionDAG.cpp.

References assert(), E, getNumValues(), use_begin(), and use_end().

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), calculateByteProvider(), combineStore(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), getAArch64Cmp(), getCmp(), llvm::SDValue::hasOneUse(), isFMAddSubOrFMSubAdd(), isFusableLoadOpStorePattern(), lowerAddSubToHorizontalOp(), LowerInterruptReturn(), Passv64i1ArgInRegs(), performBRCONDCombine(), llvm::AArch64TargetLowering::PerformDAGCombine(), llvm::PPCTargetLowering::PerformDAGCombine(), scalarizeExtractedBinop(), and XFormVExtractWithShuffleIntoLoad().

◆ hasOneUse()

|

inline |

Return true if there is exactly one use of this node.

Definition at line 706 of file SelectionDAGNodes.h.