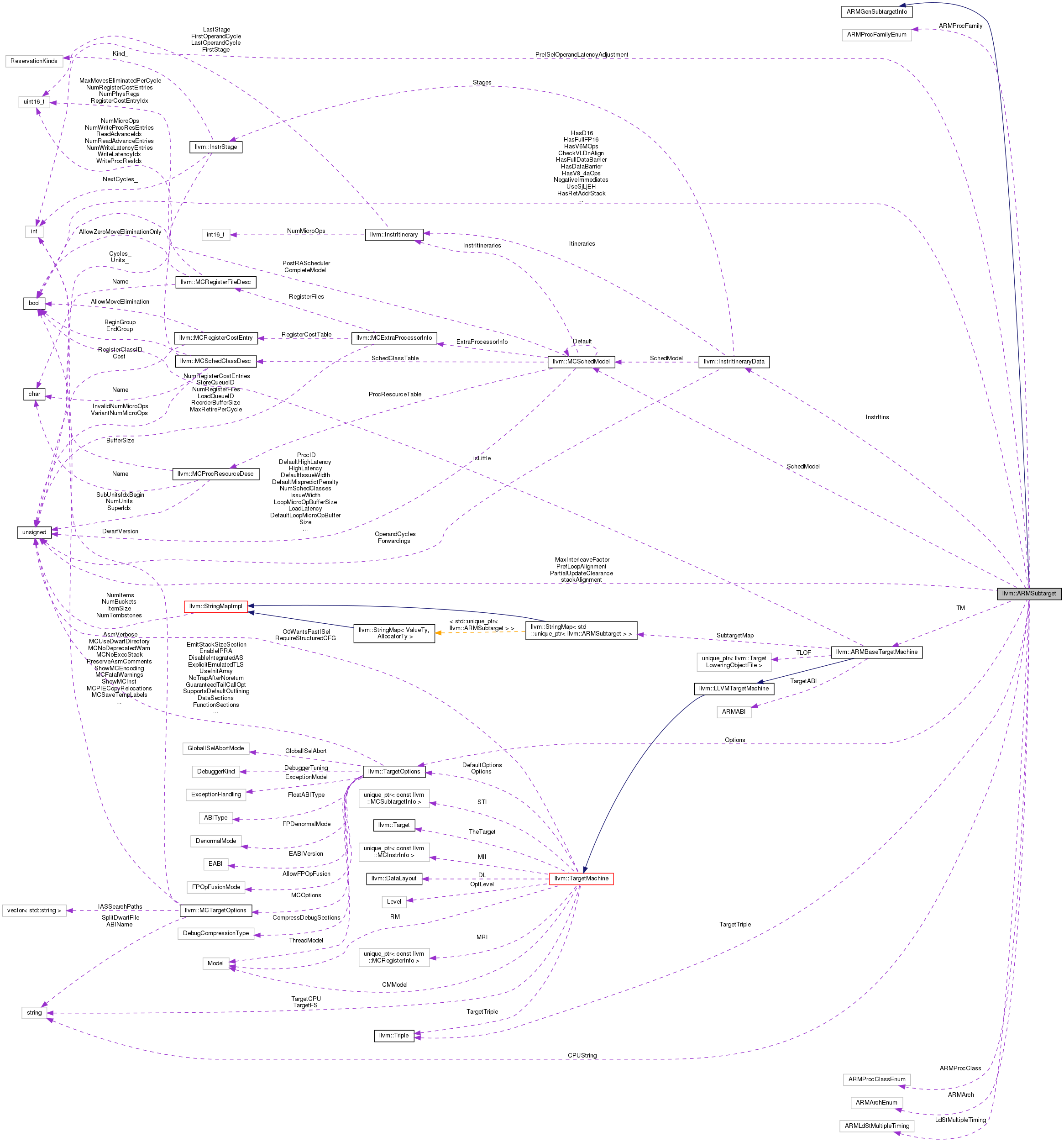

#include "Target/ARM/ARMSubtarget.h"

Public Types | |

| enum | ARMLdStMultipleTiming { DoubleIssue, DoubleIssueCheckUnalignedAccess, SingleIssue, SingleIssuePlusExtras } |

| What kind of timing do load multiple/store multiple instructions have. More... | |

Protected Types | |

| enum | ARMProcFamilyEnum { Others, CortexA12, CortexA15, CortexA17, CortexA32, CortexA35, CortexA5, CortexA53, CortexA55, CortexA57, CortexA7, CortexA72, CortexA73, CortexA75, CortexA8, CortexA9, CortexM3, CortexR4, CortexR4F, CortexR5, CortexR52, CortexR7, Exynos, Krait, Kryo, Swift } |

| enum | ARMProcClassEnum { None, AClass, MClass, RClass } |

| enum | ARMArchEnum { ARMv2, ARMv2a, ARMv3, ARMv3m, ARMv4, ARMv4t, ARMv5, ARMv5t, ARMv5te, ARMv5tej, ARMv6, ARMv6k, ARMv6kz, ARMv6m, ARMv6sm, ARMv6t2, ARMv7a, ARMv7em, ARMv7m, ARMv7r, ARMv7ve, ARMv81a, ARMv82a, ARMv83a, ARMv84a, ARMv85a, ARMv8a, ARMv8mBaseline, ARMv8mMainline, ARMv8r } |

Protected Attributes | |

| ARMProcFamilyEnum | ARMProcFamily = Others |

| ARMProcFamily - ARM processor family: Cortex-A8, Cortex-A9, and others. More... | |

| ARMProcClassEnum | ARMProcClass = None |

| ARMProcClass - ARM processor class: None, AClass, RClass or MClass. More... | |

| ARMArchEnum | ARMArch = ARMv4t |

| ARMArch - ARM architecture. More... | |

| bool | HasV4TOps = false |

| HasV4TOps, HasV5TOps, HasV5TEOps, HasV6Ops, HasV6MOps, HasV6KOps, HasV6T2Ops, HasV7Ops, HasV8Ops - Specify whether target support specific ARM ISA variants. More... | |

| bool | HasV5TOps = false |

| bool | HasV5TEOps = false |

| bool | HasV6Ops = false |

| bool | HasV6MOps = false |

| bool | HasV6KOps = false |

| bool | HasV6T2Ops = false |

| bool | HasV7Ops = false |

| bool | HasV8Ops = false |

| bool | HasV8_1aOps = false |

| bool | HasV8_2aOps = false |

| bool | HasV8_3aOps = false |

| bool | HasV8_4aOps = false |

| bool | HasV8_5aOps = false |

| bool | HasV8MBaselineOps = false |

| bool | HasV8MMainlineOps = false |

| bool | HasVFPv2 = false |

| HasVFPv2, HasVFPv3, HasVFPv4, HasFPARMv8, HasNEON - Specify what floating point ISAs are supported. More... | |

| bool | HasVFPv3 = false |

| bool | HasVFPv4 = false |

| bool | HasFPARMv8 = false |

| bool | HasNEON = false |

| bool | HasDotProd = false |

| HasDotProd - True if the ARMv8.2A dot product instructions are supported. More... | |

| bool | UseNEONForSinglePrecisionFP = false |

| UseNEONForSinglePrecisionFP - if the NEONFP attribute has been specified. More... | |

| bool | UseMulOps = false |

| UseMulOps - True if non-microcoded fused integer multiply-add and multiply-subtract instructions should be used. More... | |

| bool | SlowFPVMLx = false |

| SlowFPVMLx - If the VFP2 / NEON instructions are available, indicates whether the FP VML[AS] instructions are slow (if so, don't use them). More... | |

| bool | HasVMLxForwarding = false |

| HasVMLxForwarding - If true, NEON has special multiplier accumulator forwarding to allow mul + mla being issued back to back. More... | |

| bool | SlowFPBrcc = false |

| SlowFPBrcc - True if floating point compare + branch is slow. More... | |

| bool | InThumbMode = false |

| InThumbMode - True if compiling for Thumb, false for ARM. More... | |

| bool | UseSoftFloat = false |

| UseSoftFloat - True if we're using software floating point features. More... | |

| bool | UseMISched = false |

| UseMISched - True if MachineScheduler should be used for this subtarget. More... | |

| bool | DisablePostRAScheduler = false |

| DisablePostRAScheduler - False if scheduling should happen again after register allocation. More... | |

| bool | UseAA = false |

| UseAA - True if using AA during codegen (DAGCombine, MISched, etc) More... | |

| bool | HasThumb2 = false |

| HasThumb2 - True if Thumb2 instructions are supported. More... | |

| bool | NoARM = false |

| NoARM - True if subtarget does not support ARM mode execution. More... | |

| bool | ReserveR9 = false |

| ReserveR9 - True if R9 is not available as a general purpose register. More... | |

| bool | NoMovt = false |

| NoMovt - True if MOVT / MOVW pairs are not used for materialization of 32-bit imms (including global addresses). More... | |

| bool | SupportsTailCall = false |

| SupportsTailCall - True if the OS supports tail call. More... | |

| bool | HasFP16 = false |

| HasFP16 - True if subtarget supports half-precision FP conversions. More... | |

| bool | HasFullFP16 = false |

| HasFullFP16 - True if subtarget supports half-precision FP operations. More... | |

| bool | HasFP16FML = false |

| HasFP16FML - True if subtarget supports half-precision FP fml operations. More... | |

| bool | HasD16 = false |

| HasD16 - True if subtarget is limited to 16 double precision FP registers for VFPv3. More... | |

| bool | HasHardwareDivideInThumb = false |

| HasHardwareDivide - True if subtarget supports [su]div in Thumb mode. More... | |

| bool | HasHardwareDivideInARM = false |

| HasHardwareDivideInARM - True if subtarget supports [su]div in ARM mode. More... | |

| bool | HasDataBarrier = false |

| HasDataBarrier - True if the subtarget supports DMB / DSB data barrier instructions. More... | |

| bool | HasFullDataBarrier = false |

| HasFullDataBarrier - True if the subtarget supports DFB data barrier instruction. More... | |

| bool | HasV7Clrex = false |

| HasV7Clrex - True if the subtarget supports CLREX instructions. More... | |

| bool | HasAcquireRelease = false |

| HasAcquireRelease - True if the subtarget supports v8 atomics (LDA/LDAEX etc) instructions. More... | |

| bool | Pref32BitThumb = false |

| Pref32BitThumb - If true, codegen would prefer 32-bit Thumb instructions over 16-bit ones. More... | |

| bool | AvoidCPSRPartialUpdate = false |

| AvoidCPSRPartialUpdate - If true, codegen would avoid using instructions that partially update CPSR and add false dependency on the previous CPSR setting instruction. More... | |

| bool | CheapPredicableCPSRDef = false |

| CheapPredicableCPSRDef - If true, disable +1 predication cost for instructions updating CPSR. More... | |

| bool | AvoidMOVsShifterOperand = false |

| AvoidMOVsShifterOperand - If true, codegen should avoid using flag setting movs with shifter operand (i.e. More... | |

| bool | HasRetAddrStack = false |

| HasRetAddrStack - Some processors perform return stack prediction. More... | |

| bool | HasBranchPredictor = true |

| HasBranchPredictor - True if the subtarget has a branch predictor. More... | |

| bool | HasMPExtension = false |

| HasMPExtension - True if the subtarget supports Multiprocessing extension (ARMv7 only). More... | |

| bool | HasVirtualization = false |

| HasVirtualization - True if the subtarget supports the Virtualization extension. More... | |

| bool | FPOnlySP = false |

| FPOnlySP - If true, the floating point unit only supports single precision. More... | |

| bool | HasPerfMon = false |

| If true, the processor supports the Performance Monitor Extensions. More... | |

| bool | HasTrustZone = false |

| HasTrustZone - if true, processor supports TrustZone security extensions. More... | |

| bool | Has8MSecExt = false |

| Has8MSecExt - if true, processor supports ARMv8-M Security Extensions. More... | |

| bool | HasSHA2 = false |

| HasSHA2 - if true, processor supports SHA1 and SHA256. More... | |

| bool | HasAES = false |

| HasAES - if true, processor supports AES. More... | |

| bool | HasCrypto = false |

| HasCrypto - if true, processor supports Cryptography extensions. More... | |

| bool | HasCRC = false |

| HasCRC - if true, processor supports CRC instructions. More... | |

| bool | HasRAS = false |

| HasRAS - if true, the processor supports RAS extensions. More... | |

| bool | HasZeroCycleZeroing = false |

| If true, the instructions "vmov.i32 d0, #0" and "vmov.i32 q0, #0" are particularly effective at zeroing a VFP register. More... | |

| bool | HasFPAO = false |

| HasFPAO - if true, processor does positive address offset computation faster. More... | |

| bool | HasFuseAES = false |

| HasFuseAES - if true, processor executes back to back AES instruction pairs faster. More... | |

| bool | HasFuseLiterals = false |

| HasFuseLiterals - if true, processor executes back to back bottom and top halves of literal generation faster. More... | |

| bool | IsProfitableToUnpredicate = false |

| If true, if conversion may decide to leave some instructions unpredicated. More... | |

| bool | HasSlowVGETLNi32 = false |

| If true, VMOV will be favored over VGETLNi32. More... | |

| bool | HasSlowVDUP32 = false |

| If true, VMOV will be favored over VDUP. More... | |

| bool | PreferVMOVSR = false |

| If true, VMOVSR will be favored over VMOVDRR. More... | |

| bool | PreferISHST = false |

| If true, ISHST barriers will be used for Release semantics. More... | |

| bool | SlowOddRegister = false |

| If true, a VLDM/VSTM starting with an odd register number is considered to take more microops than single VLDRS/VSTRS. More... | |

| bool | SlowLoadDSubregister = false |

| If true, loading into a D subregister will be penalized. More... | |

| bool | UseWideStrideVFP = false |

| If true, use a wider stride when allocating VFP registers. More... | |

| bool | HasMuxedUnits = false |

| If true, the AGU and NEON/FPU units are multiplexed. More... | |

| bool | DontWidenVMOVS = false |

| If true, VMOVS will never be widened to VMOVD. More... | |

| bool | SplatVFPToNeon = false |

| If true, splat a register between VFP and NEON instructions. More... | |

| bool | ExpandMLx = false |

| If true, run the MLx expansion pass. More... | |

| bool | HasVMLxHazards = false |

| If true, VFP/NEON VMLA/VMLS have special RAW hazards. More... | |

| bool | ReadTPHard = false |

| bool | UseNEONForFPMovs = false |

| If true, VMOVRS, VMOVSR and VMOVS will be converted from VFP to NEON. More... | |

| bool | CheckVLDnAlign = false |

| If true, VLDn instructions take an extra cycle for unaligned accesses. More... | |

| bool | NonpipelinedVFP = false |

| If true, VFP instructions are not pipelined. More... | |

| bool | StrictAlign = false |

| StrictAlign - If true, the subtarget disallows unaligned memory accesses for some types. More... | |

| bool | RestrictIT = false |

| RestrictIT - If true, the subtarget disallows generation of deprecated IT blocks to conform to ARMv8 rule. More... | |

| bool | HasDSP = false |

| HasDSP - If true, the subtarget supports the DSP (saturating arith and such) instructions. More... | |

| bool | UseNaClTrap = false |

| NaCl TRAP instruction is generated instead of the regular TRAP. More... | |

| bool | GenLongCalls = false |

| Generate calls via indirect call instructions. More... | |

| bool | GenExecuteOnly = false |

| Generate code that does not contain data access to code sections. More... | |

| bool | UnsafeFPMath = false |

| Target machine allowed unsafe FP math (such as use of NEON fp) More... | |

| bool | UseSjLjEH = false |

| UseSjLjEH - If true, the target uses SjLj exception handling (e.g. iOS). More... | |

| bool | HasSB = false |

| Has speculation barrier. More... | |

| bool | NegativeImmediates = true |

| Implicitly convert an instruction to a different one if its immediates cannot be encoded. More... | |

| unsigned | stackAlignment = 4 |

| stackAlignment - The minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function. More... | |

| std::string | CPUString |

| CPUString - String name of used CPU. More... | |

| unsigned | MaxInterleaveFactor = 1 |

| unsigned | PartialUpdateClearance = 0 |

| Clearance before partial register updates (in number of instructions) More... | |

| ARMLdStMultipleTiming | LdStMultipleTiming = SingleIssue |

| What kind of timing do load multiple/store multiple have (double issue, single issue etc). More... | |

| int | PreISelOperandLatencyAdjustment = 2 |

| The adjustment that we need to apply to get the operand latency from the operand cycle returned by the itinerary data for pre-ISel operands. More... | |

| unsigned | PrefLoopAlignment = 0 |

| What alignment is preferred for loop bodies, in log2(bytes). More... | |

| bool | IsLittle |

| IsLittle - The target is Little Endian. More... | |

| Triple | TargetTriple |

| TargetTriple - What processor and OS we're targeting. More... | |

| MCSchedModel | SchedModel |

| SchedModel - Processor specific instruction costs. More... | |

| InstrItineraryData | InstrItins |

| Selected instruction itineraries (one entry per itinerary class.) More... | |

| const TargetOptions & | Options |

| Options passed via command line that could influence the target. More... | |

| const ARMBaseTargetMachine & | TM |

Detailed Description

Definition at line 45 of file ARMSubtarget.h.

Member Enumeration Documentation

◆ ARMArchEnum

|

protected |

Definition at line 83 of file ARMSubtarget.h.

◆ ARMLdStMultipleTiming

What kind of timing do load multiple/store multiple instructions have.

Definition at line 118 of file ARMSubtarget.h.

◆ ARMProcClassEnum

|

protected |

| Enumerator | |

|---|---|

| None | |

| AClass | |

| MClass | |

| RClass | |

Definition at line 76 of file ARMSubtarget.h.

◆ ARMProcFamilyEnum

|

protected |

Definition at line 47 of file ARMSubtarget.h.

Constructor & Destructor Documentation

◆ ARMSubtarget()

| ARMSubtarget::ARMSubtarget | ( | const Triple & | TT, |

| const std::string & | CPU, | ||

| const std::string & | FS, | ||

| const ARMBaseTargetMachine & | TM, | ||

| bool | IsLittle | ||

| ) |

This constructor initializes the data members to match that of the specified triple.

Definition at line 94 of file ARMSubtarget.cpp.

References llvm::createARMInstructionSelector(), getRegisterInfo(), and getTargetLowering().

Member Function Documentation

◆ allowPositionIndependentMovt()

|

inline |

Allow movt+movw for PIC global address calculation.

ELF does not have GOT relocations for movt+movw. ROPI does not use GOT.

Definition at line 814 of file ARMSubtarget.h.

References isROPI(), and isTargetELF().

◆ allowsUnalignedMem()

|

inline |

Definition at line 745 of file ARMSubtarget.h.

References StrictAlign.

Referenced by llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses().

◆ avoidCPSRPartialUpdate()

|

inline |

Definition at line 622 of file ARMSubtarget.h.

References AvoidCPSRPartialUpdate.

Referenced by isHighLatencyCPSR().

◆ avoidMOVsShifterOperand()

|

inline |

Definition at line 624 of file ARMSubtarget.h.

References AvoidMOVsShifterOperand.

Referenced by VerifyLowRegs().

◆ cheapPredicableCPSRDef()

|

inline |

Definition at line 623 of file ARMSubtarget.h.

References CheapPredicableCPSRDef.

◆ checkVLDnAccessAlignment()

|

inline |

Definition at line 619 of file ARMSubtarget.h.

References CheckVLDnAlign.

Referenced by adjustDefLatency().

◆ computeIssueWidth()

| void llvm::ARMSubtarget::computeIssueWidth | ( | ) |

Referenced by getRegisterInfo().

◆ disablePostRAScheduler()

|

inline |

Definition at line 710 of file ARMSubtarget.h.

References DisablePostRAScheduler.

Referenced by enablePostRAScheduler().

◆ dontWidenVMOVS()

|

inline |

Definition at line 616 of file ARMSubtarget.h.

References DontWidenVMOVS.

◆ enableAtomicExpand()

|

override |

Definition at line 375 of file ARMSubtarget.cpp.

References hasAnyDataBarrier().

Referenced by useAA().

◆ enableMachineScheduler()

|

override |

Returns true if machine scheduler should be enabled.

Definition at line 361 of file ARMSubtarget.cpp.

References useMachineScheduler().

Referenced by isLittle().

◆ enablePostRAScheduler()

|

override |

True for some subtargets at > -O0.

Definition at line 368 of file ARMSubtarget.cpp.

References disablePostRAScheduler(), and isThumb1Only().

Referenced by isLittle().

◆ expandMLx()

|

inline |

Definition at line 610 of file ARMSubtarget.h.

References ExpandMLx.

Referenced by isFpMulInstruction().

◆ genExecuteOnly()

|

inline |

Definition at line 633 of file ARMSubtarget.h.

References GenExecuteOnly.

Referenced by llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::ARMAsmPrinter::EmitInstruction(), emitThumbRegPlusImmInReg(), isExecuteOnlyFunction(), isNEONModifiedImm(), llvm::ARMTargetLowering::isReadOnly(), isXRaySupported(), llvm::ARMAsmPrinter::lowerOperand(), LowerWRITE_REGISTER(), llvm::ARMAsmPrinter::printOperand(), and useMovt().

◆ genLongCalls()

|

inline |

Definition at line 632 of file ARMSubtarget.h.

References GenLongCalls.

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn().

◆ getCallLowering()

|

override |

Definition at line 123 of file ARMSubtarget.cpp.

Referenced by getRegisterInfo().

◆ getCPUString()

|

inline |

Definition at line 749 of file ARMSubtarget.h.

References CPUString.

◆ getFrameLowering()

|

inlineoverride |

Definition at line 499 of file ARMSubtarget.h.

Referenced by llvm::ThumbRegisterInfo::eliminateFrameIndex(), and llvm::ARMFrameLowering::emitPrologue().

◆ getInstrInfo()

|

inlineoverride |

Definition at line 491 of file ARMSubtarget.h.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::Thumb1FrameLowering::emitEpilogue(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), emitPostSt(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), emitThumb1LoadConstPool(), findTemporariesForLR(), llvm::ARMTargetLowering::getExceptionSelectorRegister(), llvm::ARMTargetLowering::getSchedulingPreference(), isCopy(), llvm::LowerARMMachineInstrToMCInst(), MatchingStackOffset(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::ThumbRegisterInfo::resolveFrameIndex(), llvm::Thumb1FrameLowering::restoreCalleeSavedRegisters(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::Thumb1FrameLowering::spillCalleeSavedRegisters(), and UpdateCPSRUse().

◆ getInstrItineraryData()

|

inlineoverride |

getInstrItins - Return the instruction itineraries based on subtarget selection.

Definition at line 770 of file ARMSubtarget.h.

References InstrItins.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ getInstructionSelector()

|

override |

Definition at line 127 of file ARMSubtarget.cpp.

Referenced by getRegisterInfo().

◆ getLdStMultipleTiming()

|

inline |

Definition at line 783 of file ARMSubtarget.h.

References LdStMultipleTiming.

◆ getLegalizerInfo()

|

override |

Definition at line 131 of file ARMSubtarget.cpp.

Referenced by getRegisterInfo().

◆ getMaxInlineSizeThreshold()

|

inline |

getMaxInlineSizeThreshold - Returns the maximum memset / memcpy size that still makes it profitable to inline the call.

Definition at line 475 of file ARMSubtarget.h.

References initializeSubtargetDependencies(), and ParseSubtargetFeatures().

Referenced by llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemcpy().

◆ getMaxInterleaveFactor()

|

inline |

Definition at line 779 of file ARMSubtarget.h.

References MaxInterleaveFactor.

Referenced by llvm::ARMTTIImpl::getMaxInterleaveFactor().

◆ getMispredictionPenalty()

| unsigned ARMSubtarget::getMispredictionPenalty | ( | ) | const |

Definition at line 357 of file ARMSubtarget.cpp.

References llvm::MCSchedModel::MispredictPenalty, and SchedModel.

Referenced by isLittle().

◆ getPartialUpdateClearance()

|

inline |

Definition at line 781 of file ARMSubtarget.h.

References PartialUpdateClearance.

◆ getPrefLoopAlignment()

|

inline |

Definition at line 818 of file ARMSubtarget.h.

References PrefLoopAlignment.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ getPreISelOperandLatencyAdjustment()

|

inline |

Definition at line 787 of file ARMSubtarget.h.

References isGVIndirectSymbol(), isGVInGOT(), PreISelOperandLatencyAdjustment, and useFastISel().

◆ getRegBankInfo()

|

override |

Definition at line 135 of file ARMSubtarget.cpp.

Referenced by getRegisterInfo().

◆ getRegisterInfo()

|

inlineoverride |

Definition at line 503 of file ARMSubtarget.h.

References computeIssueWidth(), getCallLowering(), getInstructionSelector(), getLegalizerInfo(), and getRegBankInfo().

Referenced by ARMSubtarget(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::Thumb1InstrInfo::copyPhysReg(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::emitEpilogue(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), findTemporariesForLR(), llvm::ARMTargetLowering::getExceptionSelectorRegister(), isCopy(), LowerInterruptReturn(), MatchingStackOffset(), and llvm::ARMFrameLowering::ResolveFrameIndexReference().

◆ getReturnOpcode()

|

inline |

Returns the correct return opcode for the current feature set.

Use BX if available to allow mixing thumb/arm code, but fall back to plain mov pc,lr on ARMv4.

Definition at line 803 of file ARMSubtarget.h.

References hasV4TOps(), and isThumb().

Referenced by llvm::ARMFrameLowering::adjustForSegmentedStacks(), and llvm::ARMCallLowering::lowerReturn().

◆ getSelectionDAGInfo()

|

inlineoverride |

Definition at line 487 of file ARMSubtarget.h.

◆ getStackAlignment()

|

inline |

getStackAlignment - Returns the minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function for this subtarget.

Definition at line 777 of file ARMSubtarget.h.

References stackAlignment.

◆ getTargetLowering()

|

inlineoverride |

Definition at line 495 of file ARMSubtarget.h.

Referenced by ARMSubtarget(), llvm::ARMSelectionDAGInfo::EmitSpecializedLibcall(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), llvm::ARMBaseRegisterInfo::getCallPreservedMask(), and InsertLDR_STR().

◆ getTargetTriple()

Definition at line 645 of file ARMSubtarget.h.

References TargetTriple.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::isReadOnly(), isXRaySupported(), and LowerFPOWI().

◆ has8MSecExt()

|

inline |

Definition at line 602 of file ARMSubtarget.h.

References Has8MSecExt.

◆ hasAcquireRelease()

|

inline |

Definition at line 589 of file ARMSubtarget.h.

References HasAcquireRelease.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ hasAES()

|

inline |

Definition at line 573 of file ARMSubtarget.h.

References HasAES.

◆ hasAnyDataBarrier()

|

inline |

Definition at line 591 of file ARMSubtarget.h.

References hasV6Ops(), and isThumb().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and enableAtomicExpand().

◆ hasARMOps()

|

inline |

Definition at line 565 of file ARMSubtarget.h.

References NoARM.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and isXRaySupported().

◆ hasBranchPredictor()

|

inline |

Definition at line 626 of file ARMSubtarget.h.

References HasBranchPredictor.

Referenced by llvm::ARMTTIImpl::getUnrollingPreferences().

◆ hasCRC()

|

inline |

Definition at line 576 of file ARMSubtarget.h.

References HasCRC.

◆ hasCrypto()

|

inline |

Definition at line 574 of file ARMSubtarget.h.

References HasCrypto.

◆ hasD16()

|

inline |

Definition at line 636 of file ARMSubtarget.h.

References HasD16.

Referenced by llvm::ARMBaseRegisterInfo::getReservedRegs().

◆ hasDataBarrier()

|

inline |

Definition at line 586 of file ARMSubtarget.h.

References HasDataBarrier.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), LowerATOMIC_FENCE(), and llvm::ARMTargetLowering::makeDMB().

◆ hasDivideInARMMode()

|

inline |

Definition at line 585 of file ARMSubtarget.h.

References HasHardwareDivideInARM.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), getDivRemArgList(), and LowerADDSUBCARRY().

◆ hasDivideInThumbMode()

|

inline |

Definition at line 584 of file ARMSubtarget.h.

References HasHardwareDivideInThumb.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), getDivRemArgList(), and LowerADDSUBCARRY().

◆ hasDotProd()

|

inline |

Definition at line 575 of file ARMSubtarget.h.

References HasDotProd.

◆ hasDSP()

|

inline |

Definition at line 628 of file ARMSubtarget.h.

References HasDSP.

Referenced by AddCombineTo64bitMLAL(), AddCombineTo64BitSMLAL16(), AddCombineTo64bitUMAAL(), llvm::ARMTargetLowering::ARMTargetLowering(), getContiguousRangeOfSetBits(), PerformORCombineToBFI(), PerformORCombineToSMULWBT(), and PerformUMLALCombine().

◆ hasFP16()

|

inline |

Definition at line 635 of file ARMSubtarget.h.

References HasFP16.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ hasFP16FML()

|

inline |

Definition at line 638 of file ARMSubtarget.h.

References HasFP16FML.

◆ hasFPAO()

|

inline |

Definition at line 604 of file ARMSubtarget.h.

References HasFPAO.

Referenced by llvm::ARMTargetLowering::getScalingFactorCost().

◆ hasFPARMv8()

|

inline |

Definition at line 570 of file ARMSubtarget.h.

References HasFPARMv8.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), getARClassRegisterMask(), and isLowerSaturatingConditional().

◆ hasFullDataBarrier()

|

inline |

Definition at line 587 of file ARMSubtarget.h.

References HasFullDataBarrier.

◆ hasFullFP16()

|

inline |

Definition at line 637 of file ARMSubtarget.h.

References HasFullFP16.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), ExpandBITCAST(), llvm::ARMTargetLowering::isFNegFree(), llvm::ARMTargetLowering::isFPImmLegal(), and LowerInterruptReturn().

◆ hasFuseAES()

|

inline |

Definition at line 640 of file ARMSubtarget.h.

References HasFuseAES.

Referenced by hasFusion(), and llvm::shouldScheduleAdjacent().

◆ hasFuseLiterals()

|

inline |

Definition at line 641 of file ARMSubtarget.h.

References HasFuseLiterals.

Referenced by hasFusion(), and llvm::shouldScheduleAdjacent().

◆ hasFusion()

|

inline |

Return true if the CPU supports any kind of instruction fusion.

Definition at line 643 of file ARMSubtarget.h.

References hasFuseAES(), and hasFuseLiterals().

Referenced by llvm::ARMBETargetMachine::ARMBETargetMachine().

◆ hasMPExtension()

|

inline |

Definition at line 627 of file ARMSubtarget.h.

References HasMPExtension.

Referenced by LowerPREFETCH().

◆ hasMuxedUnits()

|

inline |

Definition at line 615 of file ARMSubtarget.h.

References HasMuxedUnits.

Referenced by llvm::ARMHazardRecognizer::getHazardType().

◆ hasNEON()

|

inline |

Definition at line 571 of file ARMSubtarget.h.

References HasNEON.

Referenced by AddCombineBUILD_VECTORToVPADDL(), llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::canCombineStoreAndExtract(), emitPostSt(), llvm::ARMTTIImpl::getArithmeticInstrCost(), llvm::ARMTTIImpl::getCastInstrCost(), llvm::ARMTTIImpl::getCmpSelInstrCost(), llvm::ARMTTIImpl::getNumberOfRegisters(), llvm::ARMTargetLowering::getOptimalMemOpType(), llvm::ARMTargetLowering::getRegClassFor(), llvm::ARMTTIImpl::getRegisterBitWidth(), isNEONModifiedImm(), LowerCTPOP(), LowerCTTZ(), llvm::ARMTargetLowering::lowerInterleavedLoad(), llvm::ARMTargetLowering::lowerInterleavedStore(), LowerShift(), LowerVectorINT_TO_FP(), llvm::ARMTargetLowering::LowerXConstraint(), PerformExtendCombine(), PerformORCombine(), PerformShiftCombine(), PerformVCVTCombine(), PerformVDIVCombine(), and useNEONForSinglePrecisionFP().

◆ hasPerfMon()

|

inline |

Definition at line 600 of file ARMSubtarget.h.

References HasPerfMon.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ hasRAS()

|

inline |

Definition at line 577 of file ARMSubtarget.h.

References HasRAS.

◆ hasRetAddrStack()

|

inline |

Definition at line 625 of file ARMSubtarget.h.

References HasRetAddrStack.

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn().

◆ hasSB()

|

inline |

Definition at line 631 of file ARMSubtarget.h.

References HasSB.

◆ hasSHA2()

|

inline |

Definition at line 572 of file ARMSubtarget.h.

References HasSHA2.

◆ hasSlowLoadDSubregister()

|

inline |

Definition at line 613 of file ARMSubtarget.h.

References SlowLoadDSubregister.

Referenced by llvm::ARMTTIImpl::getVectorInstrCost().

◆ hasSlowOddRegister()

|

inline |

Definition at line 612 of file ARMSubtarget.h.

References SlowOddRegister.

◆ hasSlowVDUP32()

|

inline |

Definition at line 607 of file ARMSubtarget.h.

References HasSlowVDUP32.

◆ hasSlowVGETLNi32()

|

inline |

Definition at line 606 of file ARMSubtarget.h.

References HasSlowVGETLNi32.

◆ hasThumb2()

|

inline |

Definition at line 715 of file ARMSubtarget.h.

References HasThumb2.

Referenced by getContiguousRangeOfSetBits(), isXRaySupported(), and PerformORCombineToSMULWBT().

◆ hasTrustZone()

|

inline |

Definition at line 601 of file ARMSubtarget.h.

References HasTrustZone.

◆ hasV4TOps()

|

inline |

Definition at line 533 of file ARMSubtarget.h.

References HasV4TOps.

Referenced by llvm::ARMAsmPrinter::EmitInstruction(), getReturnOpcode(), and llvm::ARMCallLowering::lowerFormalArguments().

◆ hasV5TEOps()

|

inline |

Definition at line 535 of file ARMSubtarget.h.

References HasV5TEOps.

Referenced by AddCombineTo64BitSMLAL16(), and LowerPREFETCH().

◆ hasV5TOps()

|

inline |

Definition at line 534 of file ARMSubtarget.h.

References HasV5TOps.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMAsmPrinter::EmitInstruction(), findTemporariesForLR(), llvm::ARMCallLowering::lowerFormalArguments(), llvm::ARMTargetLowering::PerformCMOVCombine(), llvm::ARMFrameLowering::ResolveFrameIndexReference(), and llvm::Thumb1FrameLowering::restoreCalleeSavedRegisters().

◆ hasV6KOps()

|

inline |

Definition at line 538 of file ARMSubtarget.h.

References HasV6KOps.

◆ hasV6MOps()

|

inline |

Definition at line 537 of file ARMSubtarget.h.

References HasV6MOps.

◆ hasV6Ops()

|

inline |

Definition at line 536 of file ARMSubtarget.h.

References HasV6Ops.

Referenced by AddCombineTo64bitMLAL(), AddCombineTo64bitUMAAL(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::Thumb1InstrInfo::copyPhysReg(), llvm::ARMTargetLowering::ExpandInlineAsm(), getContiguousRangeOfSetBits(), hasAnyDataBarrier(), isLowerSaturatingConditional(), isXRaySupported(), LowerATOMIC_FENCE(), llvm::ARMTargetLowering::makeDMB(), PerformORCombineToSMULWBT(), PerformShiftCombine(), PerformUMLALCombine(), llvm::ARMTargetLowering::shouldAlignPointerArgs(), and useFastISel().

◆ hasV6T2Ops()

|

inline |

Definition at line 539 of file ARMSubtarget.h.

References HasV6T2Ops.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), emitAligningInstructions(), getContiguousRangeOfSetBits(), llvm::ARMTTIImpl::getIntImmCost(), llvm::ARMTargetLowering::isCheapToSpeculateCtlz(), llvm::ARMTargetLowering::isCheapToSpeculateCttz(), isPerfectIncrement(), isXRaySupported(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerCTTZ(), llvm::ARMTargetLowering::PerformCMOVCombine(), PerformORCombineToBFI(), and llvm::ARMTargetLowering::ReplaceNodeResults().

◆ hasV7Clrex()

|

inline |

Definition at line 588 of file ARMSubtarget.h.

References HasV7Clrex.

◆ hasV7Ops()

|

inline |

Definition at line 540 of file ARMSubtarget.h.

References HasV7Ops.

Referenced by llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses(), emitAligningInstructions(), llvm::ARMTargetLowering::emitAtomicCmpXchgNoStoreLLBalance(), and LowerPREFETCH().

◆ hasV8_1aOps()

|

inline |

Definition at line 542 of file ARMSubtarget.h.

References HasV8_1aOps.

◆ hasV8_2aOps()

|

inline |

Definition at line 543 of file ARMSubtarget.h.

References HasV8_2aOps.

◆ hasV8_3aOps()

|

inline |

Definition at line 544 of file ARMSubtarget.h.

References HasV8_3aOps.

◆ hasV8_4aOps()

|

inline |

Definition at line 545 of file ARMSubtarget.h.

References HasV8_4aOps.

◆ hasV8_5aOps()

|

inline |

Definition at line 546 of file ARMSubtarget.h.

References HasV8_5aOps.

◆ hasV8MBaselineOps()

|

inline |

Definition at line 547 of file ARMSubtarget.h.

References HasV8MBaselineOps.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), expandf64Toi32(), getContiguousRangeOfSetBits(), isXRaySupported(), llvm::ARMTargetLowering::shouldExpandAtomicCmpXchgInIR(), llvm::ARMTargetLowering::shouldExpandAtomicRMWInIR(), and useMovt().

◆ hasV8MMainlineOps()

|

inline |

Definition at line 548 of file ARMSubtarget.h.

References HasV8MMainlineOps.

◆ hasV8Ops()

|

inline |

Definition at line 541 of file ARMSubtarget.h.

References HasV8Ops.

Referenced by isXRaySupported().

◆ hasVFP2()

|

inline |

Definition at line 567 of file ARMSubtarget.h.

References HasVFPv2.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer(), FPCCToARMCC(), getARClassRegisterMask(), llvm::ARMBaseRegisterInfo::getSjLjDispatchPreservedMask(), isLegalAddressImmediate(), isLegalT2AddressImmediate(), llvm::ARMTargetLowering::LowerXConstraint(), selectMergeValues(), and selectUnmergeValues().

◆ hasVFP3()

|

inline |

Definition at line 568 of file ARMSubtarget.h.

References HasVFPv3.

Referenced by llvm::ARMBaseRegisterInfo::getReservedRegs(), llvm::ARMTargetLowering::isFPImmLegal(), and isNEONModifiedImm().

◆ hasVFP4()

|

inline |

Definition at line 569 of file ARMSubtarget.h.

References HasVFPv4.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), and llvm::ARMTargetLowering::ARMTargetLowering().

◆ hasVirtualization()

|

inline |

Definition at line 578 of file ARMSubtarget.h.

References HasVirtualization.

◆ hasVMLxForwarding()

|

inline |

Definition at line 597 of file ARMSubtarget.h.

References HasVMLxForwarding.

Referenced by PerformVMULCombine().

◆ hasVMLxHazards()

|

inline |

Definition at line 611 of file ARMSubtarget.h.

References HasVMLxHazards.

◆ hasZeroCycleZeroing()

|

inline |

Definition at line 603 of file ARMSubtarget.h.

References HasZeroCycleZeroing.

◆ initializeSubtargetDependencies()

| ARMSubtarget & ARMSubtarget::initializeSubtargetDependencies | ( | StringRef | CPU, |

| StringRef | FS | ||

| ) |

initializeSubtargetDependencies - Initializes using a CPU and feature string so that we can use initializer lists for subtarget initialization.

Definition at line 78 of file ARMSubtarget.cpp.

References isThumb1Only().

Referenced by getMaxInlineSizeThreshold().

◆ isAAPCS16_ABI()

| bool ARMSubtarget::isAAPCS16_ABI | ( | ) | const |

Definition at line 324 of file ARMSubtarget.cpp.

References llvm::ARMBaseTargetMachine::ARM_ABI_AAPCS16, llvm::ARMBaseTargetMachine::ARM_ABI_UNKNOWN, assert(), llvm::ARMBaseTargetMachine::TargetABI, and TM.

Referenced by isTargetAndroid(), and isXRaySupported().

◆ isAAPCS_ABI()

| bool ARMSubtarget::isAAPCS_ABI | ( | ) | const |

Definition at line 319 of file ARMSubtarget.cpp.

References llvm::ARMBaseTargetMachine::ARM_ABI_AAPCS, llvm::ARMBaseTargetMachine::ARM_ABI_AAPCS16, llvm::ARMBaseTargetMachine::ARM_ABI_UNKNOWN, assert(), llvm::ARMBaseTargetMachine::TargetABI, and TM.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), FPCCToARMCC(), isTargetAndroid(), and isXRaySupported().

◆ isAClass()

|

inline |

Definition at line 718 of file ARMSubtarget.h.

References AClass.

◆ isAPCS_ABI()

| bool ARMSubtarget::isAPCS_ABI | ( | ) | const |

Definition at line 315 of file ARMSubtarget.cpp.

References llvm::ARMBaseTargetMachine::ARM_ABI_APCS, llvm::ARMBaseTargetMachine::ARM_ABI_UNKNOWN, assert(), llvm::ARMBaseTargetMachine::TargetABI, and TM.

Referenced by isTargetAndroid(), and LowerADDSUBCARRY().

◆ isCortexA15()

|

inline |

◆ isCortexA5()

|

inline |

These functions are obsolete, please consider adding subtarget features or properties instead of calling them.

Definition at line 553 of file ARMSubtarget.h.

References CortexA5.

◆ isCortexA7()

|

inline |

Definition at line 554 of file ARMSubtarget.h.

References CortexA7.

Referenced by adjustDefLatency().

◆ isCortexA8()

|

inline |

Definition at line 555 of file ARMSubtarget.h.

References CortexA8.

Referenced by adjustDefLatency().

◆ isCortexA9()

|

inline |

◆ isCortexM3()

|

inline |

Definition at line 559 of file ARMSubtarget.h.

References CortexM3.

◆ isCortexR5()

|

inline |

Definition at line 561 of file ARMSubtarget.h.

References CortexR5.

◆ isFPBrccSlow()

|

inline |

Definition at line 598 of file ARMSubtarget.h.

References SlowFPBrcc.

Referenced by canChangeToInt().

◆ isFPOnlySP()

|

inline |

Definition at line 599 of file ARMSubtarget.h.

References FPOnlySP.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), checkVSELConstraints(), expandf64Toi32(), getDivRemArgList(), isFloatingPointZero(), llvm::ARMTargetLowering::isFPImmLegal(), isLowerSaturatingConditional(), isNEONModifiedImm(), LowerVectorFP_TO_INT(), LowerVectorINT_TO_FP(), and PerformVMOVRRDCombine().

◆ isGVIndirectSymbol()

| bool ARMSubtarget::isGVIndirectSymbol | ( | const GlobalValue * | GV | ) | const |

True if the GV will be accessed via an indirect symbol.

Definition at line 338 of file ARMSubtarget.cpp.

References llvm::GlobalValue::getParent(), llvm::GlobalValue::hasCommonLinkage(), llvm::GlobalValue::isDeclarationForLinker(), llvm::TargetMachine::isPositionIndependent(), isTargetMachO(), llvm::TargetMachine::shouldAssumeDSOLocal(), and TM.

Referenced by getModifierVariantKind(), getPreISelOperandLatencyAdjustment(), llvm::ARMInstrInfo::getUnindexedOpcode(), and llvm::ARMTargetLowering::isReadOnly().

◆ isGVInGOT()

| bool ARMSubtarget::isGVInGOT | ( | const GlobalValue * | GV | ) | const |

Returns the constant pool modifier needed to access the GV.

Definition at line 352 of file ARMSubtarget.cpp.

References llvm::GlobalValue::getParent(), llvm::TargetMachine::isPositionIndependent(), isTargetELF(), llvm::TargetMachine::shouldAssumeDSOLocal(), and TM.

Referenced by getPreISelOperandLatencyAdjustment().

◆ isKrait()

|

inline |

◆ isLikeA9()

|

inline |

Definition at line 560 of file ARMSubtarget.h.

References isCortexA15(), isCortexA9(), and isKrait().

Referenced by adjustDefLatency(), and isFpMulInstruction().

◆ isLittle()

|

inline |

Definition at line 751 of file ARMSubtarget.h.

References enableMachineScheduler(), enablePostRAScheduler(), getMispredictionPenalty(), and IsLittle.

Referenced by llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMTargetLowering::emitLoadLinked(), llvm::ARMTargetLowering::emitStoreConditional(), isNEONModifiedImm(), LowerInterruptReturn(), and LowerVASTART().

◆ isMClass()

|

inline |

Definition at line 716 of file ARMSubtarget.h.

References MClass.

Referenced by llvm::ARMTargetLowering::alignLoopsWithOptSize(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMBaseInstrInfo::copyFromCPSR(), llvm::ARMBaseInstrInfo::copyToCPSR(), getARClassRegisterMask(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), llvm::ARMTTIImpl::getUnrollingPreferences(), LowerATOMIC_FENCE(), LowerInterruptReturn(), llvm::ARMTargetLowering::makeDMB(), llvm::ARMTargetLowering::shouldAlignPointerArgs(), llvm::ARMTargetLowering::shouldExpandAtomicLoadInIR(), llvm::ARMTargetLowering::shouldExpandAtomicRMWInIR(), and llvm::ARMTargetLowering::shouldExpandAtomicStoreInIR().

◆ isProfitableToUnpredicate()

|

inline |

Definition at line 605 of file ARMSubtarget.h.

References IsProfitableToUnpredicate.

◆ isR9Reserved()

|

inline |

Definition at line 721 of file ARMSubtarget.h.

References HasV6Ops, and isTargetMachO().

Referenced by llvm::ARMBaseRegisterInfo::getRegPressureLimit(), and llvm::ARMBaseRegisterInfo::getReservedRegs().

◆ isRClass()

|

inline |

Definition at line 717 of file ARMSubtarget.h.

References RClass.

◆ isReadTPHard()

|

inline |

Definition at line 719 of file ARMSubtarget.h.

References ReadTPHard.

◆ isROPI()

| bool ARMSubtarget::isROPI | ( | ) | const |

Definition at line 329 of file ARMSubtarget.cpp.

References llvm::TargetMachine::getRelocationModel(), llvm::Reloc::ROPI, llvm::Reloc::ROPI_RWPI, and TM.

Referenced by allowPositionIndependentMovt(), llvm::ARMAsmPrinter::EmitJumpTableAddrs(), expandf64Toi32(), llvm::ARMTargetLowering::getJumpTableEncoding(), llvm::ARMTargetLowering::isReadOnly(), isTargetAndroid(), promoteToConstantPool(), llvm::ARMTargetLowering::ReplaceNodeResults(), and llvm::ARMTTIImpl::shouldBuildLookupTablesForConstant().

◆ isRWPI()

| bool ARMSubtarget::isRWPI | ( | ) | const |

Definition at line 333 of file ARMSubtarget.cpp.

References llvm::TargetMachine::getRelocationModel(), llvm::Reloc::ROPI_RWPI, llvm::Reloc::RWPI, and TM.

Referenced by llvm::ARMTargetLowering::isReadOnly(), isTargetAndroid(), isXRaySupported(), llvm::ARMTargetLowering::ReplaceNodeResults(), and llvm::ARMTTIImpl::shouldBuildLookupTablesForConstant().

◆ isSwift()

|

inline |

Definition at line 558 of file ARMSubtarget.h.

References Swift.

Referenced by adjustDefLatency(), and isFpMulInstruction().

◆ isTargetAEABI()

|

inline |

Definition at line 667 of file ARMSubtarget.h.

References llvm::Triple::EABI, llvm::Triple::EABIHF, llvm::Triple::getEnvironment(), isTargetDarwin(), and isTargetWindows().

Referenced by AEABI(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMAsmPrinter::EmitEndOfAsmFile(), and getDivRemArgList().

◆ isTargetAndroid()

|

inline |

Definition at line 698 of file ARMSubtarget.h.

References isAAPCS16_ABI(), isAAPCS_ABI(), llvm::Triple::isAndroid(), isAPCS_ABI(), isROPI(), isRWPI(), and isXRaySupported().

Referenced by llvm::ARMFrameLowering::adjustForSegmentedStacks(), llvm::ARMTargetLowering::ARMTargetLowering(), getDivRemArgList(), and isTargetEHABICompatible().

◆ isTargetCOFF()

|

inline |

Definition at line 656 of file ARMSubtarget.h.

References llvm::Triple::isOSBinFormatCOFF().

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn(), getModifierVariantKind(), and llvm::ARMAsmPrinter::runOnMachineFunction().

◆ isTargetDarwin()

|

inline |

Definition at line 647 of file ARMSubtarget.h.

References llvm::Triple::isOSDarwin().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), llvm::ARMBaseRegisterInfo::getCallPreservedMask(), llvm::ARMTargetLowering::getJumpTableEncoding(), llvm::ARMBaseRegisterInfo::getThisReturnPreservedMask(), llvm::ARMBaseRegisterInfo::getTLSCallPreservedMask(), llvm::ARMTTIImpl::isFPVectorizationPotentiallyUnsafe(), isTargetAEABI(), isTargetEHABICompatible(), isTargetGNUAEABI(), isTargetMuslAEABI(), isXRaySupported(), LowerADDSUBCARRY(), and useR7AsFramePointer().

◆ isTargetEHABICompatible()

|

inline |

Definition at line 685 of file ARMSubtarget.h.

References llvm::Triple::EABI, llvm::Triple::EABIHF, llvm::Triple::getEnvironment(), llvm::Triple::GNUEABI, llvm::Triple::GNUEABIHF, isTargetAndroid(), isTargetDarwin(), isTargetHardFloat(), isTargetWindows(), llvm::Triple::MuslEABI, and llvm::Triple::MuslEABIHF.

Referenced by llvm::ARMAsmPrinter::EmitInstruction().

◆ isTargetELF()

|

inline |

Definition at line 657 of file ARMSubtarget.h.

References llvm::Triple::isOSBinFormatELF().

Referenced by allowPositionIndependentMovt(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::ARMAsmPrinter::EmitXXStructor(), llvm::ARMTargetLowering::getJumpTableEncoding(), getModifierVariantKind(), and isGVInGOT().

◆ isTargetGNUAEABI()

|

inline |

Definition at line 672 of file ARMSubtarget.h.

References llvm::Triple::getEnvironment(), llvm::Triple::GNUEABI, llvm::Triple::GNUEABIHF, isTargetDarwin(), and isTargetWindows().

Referenced by AEABI(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMAsmPrinter::EmitEndOfAsmFile(), and getDivRemArgList().

◆ isTargetHardFloat()

| bool ARMSubtarget::isTargetHardFloat | ( | ) | const |

Definition at line 313 of file ARMSubtarget.cpp.

References llvm::ARMBaseTargetMachine::isTargetHardFloat(), and TM.

Referenced by isTargetEHABICompatible(), and LowerInterruptReturn().

◆ isTargetIOS()

|

inline |

Definition at line 648 of file ARMSubtarget.h.

References llvm::Triple::isiOS().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), and isXRaySupported().

◆ isTargetLinux()

|

inline |

Definition at line 651 of file ARMSubtarget.h.

References llvm::Triple::isOSLinux().

Referenced by llvm::ARMFrameLowering::adjustForSegmentedStacks(), and useFastISel().

◆ isTargetMachO()

|

inline |

Definition at line 658 of file ARMSubtarget.h.

References llvm::Triple::isOSBinFormatMachO().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitMachineConstantPoolValue(), getModifierVariantKind(), isGVIndirectSymbol(), isR9Reserved(), isXRaySupported(), useFastISel(), and llvm::ARMTargetLowering::useLoadStackGuardNode().

◆ isTargetMuslAEABI()

|

inline |

Definition at line 677 of file ARMSubtarget.h.

References llvm::Triple::getEnvironment(), isTargetDarwin(), isTargetWindows(), llvm::Triple::MuslEABI, and llvm::Triple::MuslEABIHF.

Referenced by AEABI(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMAsmPrinter::EmitEndOfAsmFile(), and getDivRemArgList().

◆ isTargetNaCl()

|

inline |

Definition at line 652 of file ARMSubtarget.h.

References llvm::Triple::isOSNaCl().

Referenced by isXRaySupported(), and useFastISel().

◆ isTargetNetBSD()

|

inline |

Definition at line 653 of file ARMSubtarget.h.

References llvm::Triple::isOSNetBSD().

◆ isTargetWatchABI()

|

inline |

Definition at line 650 of file ARMSubtarget.h.

References llvm::Triple::isWatchABI().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), isXRaySupported(), and useStride4VFPs().

◆ isTargetWatchOS()

|

inline |

Definition at line 649 of file ARMSubtarget.h.

References llvm::Triple::isWatchOS().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering().

◆ isTargetWindows()

|

inline |

Definition at line 654 of file ARMSubtarget.h.

References llvm::Triple::isOSWindows().

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::ARMAsmPrinter::EmitInstruction(), emitPostSt(), llvm::ARMFrameLowering::emitPrologue(), getDivRemArgList(), llvm::ARMTargetLowering::getJumpTableEncoding(), getModifierVariantKind(), llvm::ARMTargetLowering::isReadOnly(), isTargetAEABI(), isTargetEHABICompatible(), isTargetGNUAEABI(), isTargetMuslAEABI(), isXRaySupported(), llvm::ARMTargetLowering::LowerOperation(), llvm::ARMTargetLowering::ReplaceNodeResults(), useMovt(), and useR7AsFramePointer().

◆ isThumb()

|

inline |

Definition at line 712 of file ARMSubtarget.h.

References InThumbMode.

Referenced by AddCombineTo64BitSMLAL16(), llvm::ARMFrameLowering::adjustForSegmentedStacks(), llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ARMBaseInstrInfo::copyFromCPSR(), llvm::ARMBaseInstrInfo::copyToCPSR(), emitPostSt(), expandf64Toi32(), getContiguousRangeOfSetBits(), getDivRemArgList(), llvm::ARMTTIImpl::getIntImmCost(), llvm::ARMTargetLowering::getJumpTableEncoding(), llvm::ARMTargetLowering::getRegForInlineAsmConstraint(), getReturnOpcode(), llvm::ARMTargetLowering::getSingleConstraintMatchWeight(), hasAnyDataBarrier(), llvm::ARMTargetLowering::isDesirableToCommuteWithShift(), llvm::ARMTargetLowering::isLegalAddImmediate(), llvm::ARMTargetLowering::isLegalICmpImmediate(), isLowerSaturatingConditional(), isPerfectIncrement(), llvm::ARMTargetLowering::isReadOnly(), isXRaySupported(), LowerADDSUBCARRY(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerATOMIC_FENCE(), llvm::ARMCallLowering::lowerFormalArguments(), LowerPREFETCH(), llvm::ARMTargetLowering::makeDMB(), llvm::ARMTargetLowering::PerformCMOVToBFICombine(), PerformORCombineToSMULWBT(), PerformSHLSimplify(), llvm::ARMTargetLowering::ReplaceNodeResults(), selectUnmergeValues(), llvm::ARMTargetLowering::shouldExpandAtomicCmpXchgInIR(), llvm::ARMTargetLowering::shouldExpandAtomicRMWInIR(), useFastISel(), and useR7AsFramePointer().

◆ isThumb1Only()

|

inline |

Definition at line 713 of file ARMSubtarget.h.

References HasThumb2.

Referenced by llvm::ARMFrameLowering::adjustForSegmentedStacks(), llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::CCAssignFnForReturn(), llvm::ThumbRegisterInfo::eliminateFrameIndex(), llvm::ARMAsmPrinter::EmitJumpTableTBInst(), llvm::ThumbRegisterInfo::emitLoadConstPool(), emitPostSt(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemcpy(), enablePostRAScheduler(), Expand64BitShift(), expandf64Toi32(), FPCCToARMCC(), getContiguousRangeOfSetBits(), llvm::ThumbRegisterInfo::getLargestLegalSuperClass(), llvm::ARMTTIImpl::getNumberOfRegisters(), llvm::ThumbRegisterInfo::getPointerRegClass(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPreIndexedAddressParts(), llvm::ARMTargetLowering::getRegForInlineAsmConstraint(), llvm::ARMBaseRegisterInfo::getSjLjDispatchPreservedMask(), initializeSubtargetDependencies(), llvm::ARMTargetLowering::isDesirableToCommuteWithShift(), isLegalAddressImmediate(), llvm::ARMTargetLowering::isLegalAddressingMode(), isPerfectIncrement(), IsSingleInstrConstant(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerInterruptReturn(), LowerPREFETCH(), MatchingStackOffset(), PerformAddcSubcCombine(), PerformADDECombine(), PerformAddeSubeCombine(), PerformANDCombine(), llvm::ARMTargetLowering::PerformCMOVCombine(), PerformMULCombine(), PerformORCombine(), PerformORCombineToBFI(), PerformSHLSimplify(), PerformXORCombine(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::ThumbRegisterInfo::resolveFrameIndex(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::ARMTargetLowering::shouldFoldShiftPairToMask(), splitFramePushPop(), UpdateCPSRUse(), and useFastISel().

◆ isThumb2()

|

inline |

Definition at line 714 of file ARMSubtarget.h.

References HasThumb2.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), emitPostSt(), expandf64Toi32(), getARClassRegisterMask(), getContiguousRangeOfSetBits(), llvm::ARMTTIImpl::getIntImmCost(), llvm::ARMTargetLowering::getPostIndexedAddressParts(), llvm::ARMTargetLowering::getPreIndexedAddressParts(), llvm::ARMTTIImpl::getUnrollingPreferences(), isCopy(), llvm::ARMTargetLowering::isLegalAddImmediate(), isLegalAddressImmediate(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalICmpImmediate(), isLowerSaturatingConditional(), isPerfectIncrement(), llvm::ARMTargetLowering::LowerAsmOperandForConstraint(), LowerPREFETCH(), and llvm::ARMTargetLowering::ReplaceNodeResults().

◆ isXRaySupported()

|

override |

Definition at line 139 of file ARMSubtarget.cpp.

References ARMProcFamily, assert(), llvm::tgtok::Bits, CortexA12, CortexA15, CortexA17, CortexA32, CortexA35, CortexA5, CortexA53, CortexA55, CortexA57, CortexA7, CortexA72, CortexA73, CortexA75, CortexA8, CortexA9, CortexM3, CortexR4, CortexR4F, CortexR5, CortexR52, CortexR7, CPUString, DefaultIT, DoubleIssue, DoubleIssueCheckUnalignedAccess, llvm::StringRef::empty(), llvm::TargetOptions::ExceptionModel, Exynos, genExecuteOnly(), llvm::Triple::getArchName(), llvm::MCAsmInfo::getExceptionHandlingType(), llvm::TargetMachine::getMCAsmInfo(), getTargetTriple(), hasARMOps(), hasThumb2(), hasV6Ops(), hasV6T2Ops(), hasV8MBaselineOps(), hasV8Ops(), InstrItins, isAAPCS16_ABI(), isAAPCS_ABI(), isRWPI(), isTargetDarwin(), isTargetIOS(), isTargetMachO(), isTargetNaCl(), isTargetWatchABI(), isTargetWindows(), isThumb(), IT, Krait, Kryo, LdStMultipleTiming, MaxInterleaveFactor, NoARM, NoMovt, llvm::None, NoRestrictedIT, Options, Others, llvm::ARM::parseArch(), llvm::ARM_MC::ParseARMTriple(), ParseSubtargetFeatures(), PartialUpdateClearance, PrefLoopAlignment, PreISelOperandLatencyAdjustment, ReserveR9, RestrictedIT, RestrictIT, SchedModel, SingleIssuePlusExtras, llvm::SjLj, stackAlignment, SupportsTailCall, Swift, TargetTriple, TM, llvm::TargetOptions::UnsafeFPMath, UseNEONForSinglePrecisionFP, and UseSjLjEH.

Referenced by isTargetAndroid().

◆ nonpipelinedVFP()

|

inline |

Definition at line 620 of file ARMSubtarget.h.

References NonpipelinedVFP.

◆ ParseSubtargetFeatures()

ParseSubtargetFeatures - Parses features string setting specified subtarget options.

Definition of function is auto generated by tblgen.

Referenced by getMaxInlineSizeThreshold(), and isXRaySupported().

◆ preferISHSTBarriers()

|

inline |

Definition at line 609 of file ARMSubtarget.h.

References PreferISHST.

Referenced by llvm::ARMTargetLowering::emitLeadingFence(), and LowerATOMIC_FENCE().

◆ prefers32BitThumb()

|

inline |

Definition at line 621 of file ARMSubtarget.h.

References Pref32BitThumb.

Referenced by UpdateCPSRUse().

◆ preferVMOVSR()

|

inline |

Definition at line 608 of file ARMSubtarget.h.

References PreferVMOVSR.

◆ restrictIT()

|

inline |

Definition at line 747 of file ARMSubtarget.h.

References RestrictIT.

Referenced by isCopy(), and llvm::ARMBaseInstrInfo::isPredicable().

◆ splitFramePushPop()

|

inline |

Returns true if the frame setup is split into two separate pushes (first r0-r7,lr then r8-r11), principally so that the frame pointer is adjacent to lr.

This is always required on Thumb1-only targets, as the push and pop instructions can't access the high registers.

Definition at line 733 of file ARMSubtarget.h.

References llvm::TargetOptions::DisableFramePointerElim(), llvm::MachineFunction::getTarget(), isThumb1Only(), llvm::TargetMachine::Options, useMovt(), useR7AsFramePointer(), and useStride4VFPs().

Referenced by llvm::ARMFrameLowering::determineCalleeSaves(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::ARMBaseRegisterInfo::getCalleeSavedRegs(), and llvm::ARMFrameLowering::ResolveFrameIndexReference().

◆ supportsTailCall()

|

inline |

Definition at line 743 of file ARMSubtarget.h.

References SupportsTailCall.

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn(), LowerInterruptReturn(), and MatchingStackOffset().

◆ useAA()

|

inlineoverride |

Enable use of alias analysis during code generation (during MI scheduling, DAGCombine, etc.).

Definition at line 763 of file ARMSubtarget.h.

References enableAtomicExpand(), and UseAA.

◆ useFastISel()

| bool ARMSubtarget::useFastISel | ( | ) | const |

True if fast-isel is used.

Definition at line 393 of file ARMSubtarget.cpp.

References llvm::TargetOptions::EnableFastISel, ForceFastISel, hasV6Ops(), isTargetLinux(), isTargetMachO(), isTargetNaCl(), isThumb(), isThumb1Only(), llvm::TargetMachine::Options, and TM.

Referenced by llvm::ARM::createFastISel(), and getPreISelOperandLatencyAdjustment().

◆ useFPVMLx()

|

inline |

Definition at line 596 of file ARMSubtarget.h.

References SlowFPVMLx.

◆ useMachineScheduler()

|

inline |

Definition at line 709 of file ARMSubtarget.h.

References UseMISched.

Referenced by enableMachineScheduler().

◆ useMovt()

| bool ARMSubtarget::useMovt | ( | const MachineFunction & | MF | ) | const |

Definition at line 385 of file ARMSubtarget.cpp.

References genExecuteOnly(), llvm::MachineFunction::getFunction(), hasV8MBaselineOps(), isTargetWindows(), NoMovt, and llvm::Function::optForMinSize().

Referenced by emitPostSt(), llvm::ARMInstrInfo::getUnindexedOpcode(), llvm::ARMTargetLowering::isReadOnly(), and splitFramePushPop().

◆ useMulOps()

|

inline |

Definition at line 595 of file ARMSubtarget.h.

References UseMulOps.

Referenced by AddCombineTo64bitMLAL().

◆ useNaClTrap()

|

inline |

Definition at line 629 of file ARMSubtarget.h.

References UseNaClTrap.

Referenced by llvm::ARMTargetLowering::ReplaceNodeResults().

◆ useNEONForFPMovs()

|

inline |

Definition at line 618 of file ARMSubtarget.h.

References UseNEONForFPMovs.

◆ useNEONForSinglePrecisionFP()

|

inline |

Definition at line 580 of file ARMSubtarget.h.

References hasNEON(), and UseNEONForSinglePrecisionFP.

Referenced by llvm::ARMTargetLowering::findRepresentativeClass(), and isNEONModifiedImm().

◆ useR7AsFramePointer()

|

inline |

Definition at line 725 of file ARMSubtarget.h.

References isTargetDarwin(), isTargetWindows(), and isThumb().

Referenced by llvm::ARMAsmPrinter::EmitInstruction(), findTemporariesForLR(), getFramePointerReg(), and splitFramePushPop().

◆ useSjLjEH()

|

inline |

Definition at line 630 of file ARMSubtarget.h.

References UseSjLjEH.

Referenced by llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMTargetLowering::getExceptionPointerRegister(), and llvm::ARMTargetLowering::getExceptionSelectorRegister().

◆ useSoftFloat()

|

inline |

Definition at line 711 of file ARMSubtarget.h.

References UseSoftFloat.

Referenced by llvm::ARMLegalizerInfo::ARMLegalizerInfo(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::ARMBaseRegisterInfo::getSjLjDispatchPreservedMask(), and llvm::ARMTargetLowering::useSoftFloat().

◆ useSplatVFPToNeon()

|

inline |

Definition at line 617 of file ARMSubtarget.h.

References SplatVFPToNeon.

◆ useStride4VFPs()

| bool ARMSubtarget::useStride4VFPs | ( | const MachineFunction & | MF | ) | const |

Definition at line 377 of file ARMSubtarget.cpp.

References llvm::MachineFunction::getFunction(), isTargetWatchABI(), llvm::Function::optForMinSize(), and useWideStrideVFP().

Referenced by splitFramePushPop().

◆ useWideStrideVFP()

|

inline |

Definition at line 614 of file ARMSubtarget.h.

References UseWideStrideVFP.

Referenced by useStride4VFPs().

Member Data Documentation

◆ ARMArch

|

protected |

ARMArch - ARM architecture.

Definition at line 139 of file ARMSubtarget.h.

◆ ARMProcClass

|

protected |

ARMProcClass - ARM processor class: None, AClass, RClass or MClass.

Definition at line 136 of file ARMSubtarget.h.

◆ ARMProcFamily

|

protected |

ARMProcFamily - ARM processor family: Cortex-A8, Cortex-A9, and others.

Definition at line 133 of file ARMSubtarget.h.

Referenced by isXRaySupported().

◆ AvoidCPSRPartialUpdate

AvoidCPSRPartialUpdate - If true, codegen would avoid using instructions that partially update CPSR and add false dependency on the previous CPSR setting instruction.

Definition at line 267 of file ARMSubtarget.h.

Referenced by avoidCPSRPartialUpdate().

◆ AvoidMOVsShifterOperand

AvoidMOVsShifterOperand - If true, codegen should avoid using flag setting movs with shifter operand (i.e.

asr, lsl, lsr).

Definition at line 275 of file ARMSubtarget.h.

Referenced by avoidMOVsShifterOperand().

◆ CheapPredicableCPSRDef

CheapPredicableCPSRDef - If true, disable +1 predication cost for instructions updating CPSR.

Enabled for Cortex-A57.

Definition at line 271 of file ARMSubtarget.h.

Referenced by cheapPredicableCPSRDef().

◆ CheckVLDnAlign

If true, VLDn instructions take an extra cycle for unaligned accesses.

Definition at line 386 of file ARMSubtarget.h.

Referenced by checkVLDnAccessAlignment().

◆ CPUString

|

protected |

CPUString - String name of used CPU.

Definition at line 431 of file ARMSubtarget.h.

Referenced by getCPUString(), and isXRaySupported().

◆ DisablePostRAScheduler

DisablePostRAScheduler - False if scheduling should happen again after register allocation.

Definition at line 203 of file ARMSubtarget.h.

Referenced by disablePostRAScheduler().

◆ DontWidenVMOVS

If true, VMOVS will never be widened to VMOVD.

Definition at line 368 of file ARMSubtarget.h.

Referenced by dontWidenVMOVS().

◆ ExpandMLx

If true, run the MLx expansion pass.

Definition at line 374 of file ARMSubtarget.h.

Referenced by expandMLx().

◆ FPOnlySP

FPOnlySP - If true, the floating point unit only supports single precision.

Definition at line 296 of file ARMSubtarget.h.

Referenced by isFPOnlySP().

◆ GenExecuteOnly

Generate code that does not contain data access to code sections.

Definition at line 411 of file ARMSubtarget.h.

Referenced by genExecuteOnly().

◆ GenLongCalls

Generate calls via indirect call instructions.

Definition at line 408 of file ARMSubtarget.h.

Referenced by genLongCalls().

◆ Has8MSecExt

Has8MSecExt - if true, processor supports ARMv8-M Security Extensions.

Definition at line 307 of file ARMSubtarget.h.

Referenced by has8MSecExt().

◆ HasAcquireRelease

HasAcquireRelease - True if the subtarget supports v8 atomics (LDA/LDAEX etc) instructions.

Definition at line 258 of file ARMSubtarget.h.

Referenced by hasAcquireRelease().

◆ HasAES

HasAES - if true, processor supports AES.

Definition at line 313 of file ARMSubtarget.h.

Referenced by hasAES().

◆ HasBranchPredictor

HasBranchPredictor - True if the subtarget has a branch predictor.

Having a branch predictor or not changes the expected cost of taking a branch which affects the choice of whether to use predicated instructions.

Definition at line 284 of file ARMSubtarget.h.

Referenced by hasBranchPredictor().

◆ HasCRC

HasCRC - if true, processor supports CRC instructions.

Definition at line 319 of file ARMSubtarget.h.

Referenced by hasCRC().

◆ HasCrypto

HasCrypto - if true, processor supports Cryptography extensions.

Definition at line 316 of file ARMSubtarget.h.

Referenced by hasCrypto().

◆ HasD16

HasD16 - True if subtarget is limited to 16 double precision FP registers for VFPv3.

Definition at line 237 of file ARMSubtarget.h.

Referenced by hasD16().

◆ HasDataBarrier

HasDataBarrier - True if the subtarget supports DMB / DSB data barrier instructions.

Definition at line 247 of file ARMSubtarget.h.

Referenced by hasDataBarrier().

◆ HasDotProd

HasDotProd - True if the ARMv8.2A dot product instructions are supported.

Definition at line 170 of file ARMSubtarget.h.

Referenced by hasDotProd().

◆ HasDSP

HasDSP - If true, the subtarget supports the DSP (saturating arith and such) instructions.

Definition at line 402 of file ARMSubtarget.h.

Referenced by hasDSP().

◆ HasFP16

HasFP16 - True if subtarget supports half-precision FP conversions.

Definition at line 227 of file ARMSubtarget.h.

Referenced by hasFP16().

◆ HasFP16FML

HasFP16FML - True if subtarget supports half-precision FP fml operations.

Definition at line 233 of file ARMSubtarget.h.

Referenced by hasFP16FML().

◆ HasFPAO

HasFPAO - if true, processor does positive address offset computation faster.

Definition at line 329 of file ARMSubtarget.h.

Referenced by hasFPAO().

◆ HasFPARMv8

Definition at line 166 of file ARMSubtarget.h.

Referenced by hasFPARMv8().

◆ HasFullDataBarrier

HasFullDataBarrier - True if the subtarget supports DFB data barrier instruction.

Definition at line 251 of file ARMSubtarget.h.

Referenced by hasFullDataBarrier().

◆ HasFullFP16

HasFullFP16 - True if subtarget supports half-precision FP operations.

Definition at line 230 of file ARMSubtarget.h.

Referenced by hasFullFP16().

◆ HasFuseAES

HasFuseAES - if true, processor executes back to back AES instruction pairs faster.

Definition at line 333 of file ARMSubtarget.h.

Referenced by hasFuseAES().

◆ HasFuseLiterals

HasFuseLiterals - if true, processor executes back to back bottom and top halves of literal generation faster.

Definition at line 337 of file ARMSubtarget.h.

Referenced by hasFuseLiterals().

◆ HasHardwareDivideInARM

HasHardwareDivideInARM - True if subtarget supports [su]div in ARM mode.

Definition at line 243 of file ARMSubtarget.h.

Referenced by hasDivideInARMMode().

◆ HasHardwareDivideInThumb

HasHardwareDivide - True if subtarget supports [su]div in Thumb mode.

Definition at line 240 of file ARMSubtarget.h.

Referenced by hasDivideInThumbMode().

◆ HasMPExtension

HasMPExtension - True if the subtarget supports Multiprocessing extension (ARMv7 only).

Definition at line 288 of file ARMSubtarget.h.

Referenced by hasMPExtension().

◆ HasMuxedUnits

If true, the AGU and NEON/FPU units are multiplexed.

Definition at line 365 of file ARMSubtarget.h.

Referenced by hasMuxedUnits().

◆ HasNEON

Definition at line 167 of file ARMSubtarget.h.

Referenced by hasNEON().

◆ HasPerfMon

If true, the processor supports the Performance Monitor Extensions.

These include a generic cycle-counter as well as more fine-grained (often implementation-specific) events.

Definition at line 301 of file ARMSubtarget.h.

Referenced by hasPerfMon().

◆ HasRAS

HasRAS - if true, the processor supports RAS extensions.

Definition at line 322 of file ARMSubtarget.h.

Referenced by hasRAS().

◆ HasRetAddrStack

HasRetAddrStack - Some processors perform return stack prediction.

CodeGen should avoid issue "normal" call instructions to callees which do not return.

Definition at line 279 of file ARMSubtarget.h.

Referenced by hasRetAddrStack().

◆ HasSB

◆ HasSHA2

HasSHA2 - if true, processor supports SHA1 and SHA256.

Definition at line 310 of file ARMSubtarget.h.

Referenced by hasSHA2().

◆ HasSlowVDUP32

If true, VMOV will be favored over VDUP.

Definition at line 346 of file ARMSubtarget.h.

Referenced by hasSlowVDUP32().

◆ HasSlowVGETLNi32

If true, VMOV will be favored over VGETLNi32.

Definition at line 343 of file ARMSubtarget.h.

Referenced by hasSlowVGETLNi32().

◆ HasThumb2

HasThumb2 - True if Thumb2 instructions are supported.

Definition at line 209 of file ARMSubtarget.h.

Referenced by hasThumb2(), isThumb1Only(), and isThumb2().

◆ HasTrustZone

HasTrustZone - if true, processor supports TrustZone security extensions.

Definition at line 304 of file ARMSubtarget.h.

Referenced by hasTrustZone().

◆ HasV4TOps

HasV4TOps, HasV5TOps, HasV5TEOps, HasV6Ops, HasV6MOps, HasV6KOps, HasV6T2Ops, HasV7Ops, HasV8Ops - Specify whether target support specific ARM ISA variants.

Definition at line 144 of file ARMSubtarget.h.

Referenced by hasV4TOps().

◆ HasV5TEOps

Definition at line 146 of file ARMSubtarget.h.

Referenced by hasV5TEOps().

◆ HasV5TOps

Definition at line 145 of file ARMSubtarget.h.

Referenced by hasV5TOps().

◆ HasV6KOps

Definition at line 149 of file ARMSubtarget.h.

Referenced by hasV6KOps().

◆ HasV6MOps

Definition at line 148 of file ARMSubtarget.h.

Referenced by hasV6MOps().

◆ HasV6Ops

Definition at line 147 of file ARMSubtarget.h.

Referenced by hasV6Ops(), and isR9Reserved().

◆ HasV6T2Ops

Definition at line 150 of file ARMSubtarget.h.

Referenced by hasV6T2Ops().

◆ HasV7Clrex

HasV7Clrex - True if the subtarget supports CLREX instructions.

Definition at line 254 of file ARMSubtarget.h.

Referenced by hasV7Clrex().

◆ HasV7Ops

Definition at line 151 of file ARMSubtarget.h.

Referenced by hasV7Ops().

◆ HasV8_1aOps

Definition at line 153 of file ARMSubtarget.h.

Referenced by hasV8_1aOps().

◆ HasV8_2aOps

Definition at line 154 of file ARMSubtarget.h.

Referenced by hasV8_2aOps().

◆ HasV8_3aOps

Definition at line 155 of file ARMSubtarget.h.

Referenced by hasV8_3aOps().

◆ HasV8_4aOps

Definition at line 156 of file ARMSubtarget.h.

Referenced by hasV8_4aOps().

◆ HasV8_5aOps

Definition at line 157 of file ARMSubtarget.h.

Referenced by hasV8_5aOps().

◆ HasV8MBaselineOps

Definition at line 158 of file ARMSubtarget.h.

Referenced by hasV8MBaselineOps().

◆ HasV8MMainlineOps

Definition at line 159 of file ARMSubtarget.h.

Referenced by hasV8MMainlineOps().

◆ HasV8Ops

Definition at line 152 of file ARMSubtarget.h.

Referenced by hasV8Ops().

◆ HasVFPv2

HasVFPv2, HasVFPv3, HasVFPv4, HasFPARMv8, HasNEON - Specify what floating point ISAs are supported.

Definition at line 163 of file ARMSubtarget.h.

Referenced by hasVFP2().

◆ HasVFPv3

Definition at line 164 of file ARMSubtarget.h.

Referenced by hasVFP3().

◆ HasVFPv4

Definition at line 165 of file ARMSubtarget.h.

Referenced by hasVFP4().

◆ HasVirtualization

HasVirtualization - True if the subtarget supports the Virtualization extension.

Definition at line 292 of file ARMSubtarget.h.

Referenced by hasVirtualization().

◆ HasVMLxForwarding

HasVMLxForwarding - If true, NEON has special multiplier accumulator forwarding to allow mul + mla being issued back to back.

Definition at line 187 of file ARMSubtarget.h.

Referenced by hasVMLxForwarding().

◆ HasVMLxHazards

If true, VFP/NEON VMLA/VMLS have special RAW hazards.

Definition at line 377 of file ARMSubtarget.h.

Referenced by hasVMLxHazards().

◆ HasZeroCycleZeroing

If true, the instructions "vmov.i32 d0, #0" and "vmov.i32 q0, #0" are particularly effective at zeroing a VFP register.

Definition at line 326 of file ARMSubtarget.h.

Referenced by hasZeroCycleZeroing().

◆ InstrItins

|

protected |

Selected instruction itineraries (one entry per itinerary class.)

Definition at line 459 of file ARMSubtarget.h.

Referenced by getInstrItineraryData(), and isXRaySupported().

◆ InThumbMode

InThumbMode - True if compiling for Thumb, false for ARM.

Definition at line 193 of file ARMSubtarget.h.

Referenced by isThumb().

◆ IsLittle

|

protected |

IsLittle - The target is Little Endian.

Definition at line 450 of file ARMSubtarget.h.

Referenced by isLittle().

◆ IsProfitableToUnpredicate

If true, if conversion may decide to leave some instructions unpredicated.

Definition at line 340 of file ARMSubtarget.h.

Referenced by isProfitableToUnpredicate().

◆ LdStMultipleTiming

|

protected |

What kind of timing do load multiple/store multiple have (double issue, single issue etc).

Definition at line 440 of file ARMSubtarget.h.

Referenced by getLdStMultipleTiming(), and isXRaySupported().

◆ MaxInterleaveFactor

|

protected |

Definition at line 433 of file ARMSubtarget.h.

Referenced by getMaxInterleaveFactor(), and isXRaySupported().

◆ NegativeImmediates

Implicitly convert an instruction to a different one if its immediates cannot be encoded.

For example, ADD r0, r1, #FFFFFFFF -> SUB r0, r1, #1.

Definition at line 424 of file ARMSubtarget.h.

◆ NoARM

NoARM - True if subtarget does not support ARM mode execution.

Definition at line 212 of file ARMSubtarget.h.

Referenced by hasARMOps(), and isXRaySupported().

◆ NoMovt

NoMovt - True if MOVT / MOVW pairs are not used for materialization of 32-bit imms (including global addresses).

Definition at line 219 of file ARMSubtarget.h.

Referenced by isXRaySupported(), and useMovt().

◆ NonpipelinedVFP

If true, VFP instructions are not pipelined.

Definition at line 389 of file ARMSubtarget.h.

Referenced by nonpipelinedVFP().

◆ Options

|

protected |

Options passed via command line that could influence the target.

Definition at line 462 of file ARMSubtarget.h.

Referenced by isXRaySupported().

◆ PartialUpdateClearance

|

protected |

Clearance before partial register updates (in number of instructions)

Definition at line 436 of file ARMSubtarget.h.

Referenced by getPartialUpdateClearance(), and isXRaySupported().

◆ Pref32BitThumb

Pref32BitThumb - If true, codegen would prefer 32-bit Thumb instructions over 16-bit ones.

Definition at line 262 of file ARMSubtarget.h.

Referenced by prefers32BitThumb().

◆ PreferISHST

If true, ISHST barriers will be used for Release semantics.

Definition at line 352 of file ARMSubtarget.h.

Referenced by preferISHSTBarriers().

◆ PreferVMOVSR

If true, VMOVSR will be favored over VMOVDRR.

Definition at line 349 of file ARMSubtarget.h.

Referenced by preferVMOVSR().

◆ PrefLoopAlignment

|

protected |

What alignment is preferred for loop bodies, in log2(bytes).