|

| | ARMInstrInfo (const ARMSubtarget &STI) |

| |

| void | getNoop (MCInst &NopInst) const override |

| | Return the noop instruction to use for a noop. More...

|

| |

| unsigned | getUnindexedOpcode (unsigned Opc) const override |

| |

| const ARMRegisterInfo & | getRegisterInfo () const override |

| | getRegisterInfo - TargetInstrInfo is a superset of MRegister info. More...

|

| |

| bool | hasNOP () const |

| |

| MachineInstr * | convertToThreeAddress (MachineFunction::iterator &MFI, MachineInstr &MI, LiveVariables *LV) const override |

| |

| const ARMSubtarget & | getSubtarget () const |

| |

| ScheduleHazardRecognizer * | CreateTargetHazardRecognizer (const TargetSubtargetInfo *STI, const ScheduleDAG *DAG) const override |

| |

| ScheduleHazardRecognizer * | CreateTargetPostRAHazardRecognizer (const InstrItineraryData *II, const ScheduleDAG *DAG) const override |

| |

| bool | analyzeBranch (MachineBasicBlock &MBB, MachineBasicBlock *&TBB, MachineBasicBlock *&FBB, SmallVectorImpl< MachineOperand > &Cond, bool AllowModify=false) const override |

| |

| unsigned | removeBranch (MachineBasicBlock &MBB, int *BytesRemoved=nullptr) const override |

| |

| unsigned | insertBranch (MachineBasicBlock &MBB, MachineBasicBlock *TBB, MachineBasicBlock *FBB, ArrayRef< MachineOperand > Cond, const DebugLoc &DL, int *BytesAdded=nullptr) const override |

| |

| bool | reverseBranchCondition (SmallVectorImpl< MachineOperand > &Cond) const override |

| |

| bool | isPredicated (const MachineInstr &MI) const override |

| |

| ARMCC::CondCodes | getPredicate (const MachineInstr &MI) const |

| |

| bool | PredicateInstruction (MachineInstr &MI, ArrayRef< MachineOperand > Pred) const override |

| |

| bool | SubsumesPredicate (ArrayRef< MachineOperand > Pred1, ArrayRef< MachineOperand > Pred2) const override |

| |

| bool | DefinesPredicate (MachineInstr &MI, std::vector< MachineOperand > &Pred) const override |

| |

| bool | isPredicable (const MachineInstr &MI) const override |

| | isPredicable - Return true if the specified instruction can be predicated. More...

|

| |

| bool | isAddrMode3OpImm (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isAddrMode3OpMinusReg (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isLdstScaledReg (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isLdstScaledRegNotPlusLsl2 (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isLdstSoMinusReg (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isAm2ScaledReg (const MachineInstr &MI, unsigned Op) const |

| |

| bool | isLDMBaseRegInList (const MachineInstr &MI) const |

| |

| unsigned | getLDMVariableDefsSize (const MachineInstr &MI) const |

| |

| unsigned | getInstSizeInBytes (const MachineInstr &MI) const override |

| | GetInstSize - Returns the size of the specified MachineInstr. More...

|

| |

| unsigned | isLoadFromStackSlot (const MachineInstr &MI, int &FrameIndex) const override |

| |

| unsigned | isStoreToStackSlot (const MachineInstr &MI, int &FrameIndex) const override |

| |

| unsigned | isLoadFromStackSlotPostFE (const MachineInstr &MI, int &FrameIndex) const override |

| |

| unsigned | isStoreToStackSlotPostFE (const MachineInstr &MI, int &FrameIndex) const override |

| |

| void | copyToCPSR (MachineBasicBlock &MBB, MachineBasicBlock::iterator I, unsigned SrcReg, bool KillSrc, const ARMSubtarget &Subtarget) const |

| |

| void | copyFromCPSR (MachineBasicBlock &MBB, MachineBasicBlock::iterator I, unsigned DestReg, bool KillSrc, const ARMSubtarget &Subtarget) const |

| |

| void | copyPhysReg (MachineBasicBlock &MBB, MachineBasicBlock::iterator I, const DebugLoc &DL, unsigned DestReg, unsigned SrcReg, bool KillSrc) const override |

| |

| void | storeRegToStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MBBI, unsigned SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| |

| void | loadRegFromStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MBBI, unsigned DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| |

| bool | expandPostRAPseudo (MachineInstr &MI) const override |

| |

| bool | shouldSink (const MachineInstr &MI) const override |

| |

| void | reMaterialize (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned DestReg, unsigned SubIdx, const MachineInstr &Orig, const TargetRegisterInfo &TRI) const override |

| |

| MachineInstr & | duplicate (MachineBasicBlock &MBB, MachineBasicBlock::iterator InsertBefore, const MachineInstr &Orig) const override |

| |

| const MachineInstrBuilder & | AddDReg (MachineInstrBuilder &MIB, unsigned Reg, unsigned SubIdx, unsigned State, const TargetRegisterInfo *TRI) const |

| |

| bool | produceSameValue (const MachineInstr &MI0, const MachineInstr &MI1, const MachineRegisterInfo *MRI) const override |

| |

| bool | areLoadsFromSameBasePtr (SDNode *Load1, SDNode *Load2, int64_t &Offset1, int64_t &Offset2) const override |

| | areLoadsFromSameBasePtr - This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address. More...

|

| |

| bool | shouldScheduleLoadsNear (SDNode *Load1, SDNode *Load2, int64_t Offset1, int64_t Offset2, unsigned NumLoads) const override |

| | shouldScheduleLoadsNear - This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled togther. More...

|

| |

| bool | isSchedulingBoundary (const MachineInstr &MI, const MachineBasicBlock *MBB, const MachineFunction &MF) const override |

| |

| bool | isProfitableToIfCvt (MachineBasicBlock &MBB, unsigned NumCycles, unsigned ExtraPredCycles, BranchProbability Probability) const override |

| |

| bool | isProfitableToIfCvt (MachineBasicBlock &TMBB, unsigned NumT, unsigned ExtraT, MachineBasicBlock &FMBB, unsigned NumF, unsigned ExtraF, BranchProbability Probability) const override |

| |

| bool | isProfitableToDupForIfCvt (MachineBasicBlock &MBB, unsigned NumCycles, BranchProbability Probability) const override |

| |

| bool | isProfitableToUnpredicate (MachineBasicBlock &TMBB, MachineBasicBlock &FMBB) const override |

| |

| bool | analyzeCompare (const MachineInstr &MI, unsigned &SrcReg, unsigned &SrcReg2, int &CmpMask, int &CmpValue) const override |

| | analyzeCompare - For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue. More...

|

| |

| bool | optimizeCompareInstr (MachineInstr &CmpInstr, unsigned SrcReg, unsigned SrcReg2, int CmpMask, int CmpValue, const MachineRegisterInfo *MRI) const override |

| | optimizeCompareInstr - Convert the instruction to set the zero flag so that we can remove a "comparison with zero"; Remove a redundant CMP instruction if the flags can be updated in the same way by an earlier instruction such as SUB. More...

|

| |

| bool | analyzeSelect (const MachineInstr &MI, SmallVectorImpl< MachineOperand > &Cond, unsigned &TrueOp, unsigned &FalseOp, bool &Optimizable) const override |

| |

| MachineInstr * | optimizeSelect (MachineInstr &MI, SmallPtrSetImpl< MachineInstr *> &SeenMIs, bool) const override |

| |

| bool | FoldImmediate (MachineInstr &UseMI, MachineInstr &DefMI, unsigned Reg, MachineRegisterInfo *MRI) const override |

| | FoldImmediate - 'Reg' is known to be defined by a move immediate instruction, try to fold the immediate into the use instruction. More...

|

| |

| unsigned | getNumMicroOps (const InstrItineraryData *ItinData, const MachineInstr &MI) const override |

| |

| int | getOperandLatency (const InstrItineraryData *ItinData, const MachineInstr &DefMI, unsigned DefIdx, const MachineInstr &UseMI, unsigned UseIdx) const override |

| |

| int | getOperandLatency (const InstrItineraryData *ItinData, SDNode *DefNode, unsigned DefIdx, SDNode *UseNode, unsigned UseIdx) const override |

| |

| std::pair< uint16_t, uint16_t > | getExecutionDomain (const MachineInstr &MI) const override |

| | VFP/NEON execution domains. More...

|

| |

| void | setExecutionDomain (MachineInstr &MI, unsigned Domain) const override |

| |

| unsigned | getPartialRegUpdateClearance (const MachineInstr &, unsigned, const TargetRegisterInfo *) const override |

| |

| void | breakPartialRegDependency (MachineInstr &, unsigned, const TargetRegisterInfo *TRI) const override |

| |

| unsigned | getNumLDMAddresses (const MachineInstr &MI) const |

| | Get the number of addresses by LDM or VLDM or zero for unknown. More...

|

| |

| std::pair< unsigned, unsigned > | decomposeMachineOperandsTargetFlags (unsigned TF) const override |

| |

| ArrayRef< std::pair< unsigned, const char * > > | getSerializableDirectMachineOperandTargetFlags () const override |

| |

| ArrayRef< std::pair< unsigned, const char * > > | getSerializableBitmaskMachineOperandTargetFlags () const override |

| |

| bool | isFpMLxInstruction (unsigned Opcode) const |

| | isFpMLxInstruction - Return true if the specified opcode is a fp MLA / MLS instruction. More...

|

| |

| bool | isFpMLxInstruction (unsigned Opcode, unsigned &MulOpc, unsigned &AddSubOpc, bool &NegAcc, bool &HasLane) const |

| | isFpMLxInstruction - This version also returns the multiply opcode and the addition / subtraction opcode to expand to. More...

|

| |

| bool | canCauseFpMLxStall (unsigned Opcode) const |

| | canCauseFpMLxStall - Return true if an instruction of the specified opcode will cause stalls when scheduled after (within 4-cycle window) a fp MLA / MLS instruction. More...

|

| |

| bool | isSwiftFastImmShift (const MachineInstr *MI) const |

| | Returns true if the instruction has a shift by immediate that can be executed in one cycle less. More...

|

| |

| unsigned | getFramePred (const MachineInstr &MI) const |

| | Returns predicate register associated with the given frame instruction. More...

|

| |

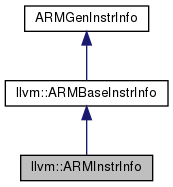

Definition at line 23 of file ARMInstrInfo.h.

Static Public Member Functions inherited from llvm::ARMBaseInstrInfo

Static Public Member Functions inherited from llvm::ARMBaseInstrInfo Protected Member Functions inherited from llvm::ARMBaseInstrInfo

Protected Member Functions inherited from llvm::ARMBaseInstrInfo 1.8.13

1.8.13