#include "Target/ARM/Thumb2InstrInfo.h"

Additional Inherited Members | |

Static Public Member Functions inherited from llvm::ARMBaseInstrInfo Static Public Member Functions inherited from llvm::ARMBaseInstrInfo | |

| static bool | isCPSRDefined (const MachineInstr &MI) |

Protected Member Functions inherited from llvm::ARMBaseInstrInfo Protected Member Functions inherited from llvm::ARMBaseInstrInfo | |

| ARMBaseInstrInfo (const ARMSubtarget &STI) | |

| void | expandLoadStackGuardBase (MachineBasicBlock::iterator MI, unsigned LoadImmOpc, unsigned LoadOpc) const |

| bool | getRegSequenceLikeInputs (const MachineInstr &MI, unsigned DefIdx, SmallVectorImpl< RegSubRegPairAndIdx > &InputRegs) const override |

Build the equivalent inputs of a REG_SEQUENCE for the given MI and DefIdx. More... | |

| bool | getExtractSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPairAndIdx &InputReg) const override |

Build the equivalent inputs of a EXTRACT_SUBREG for the given MI and DefIdx. More... | |

| bool | getInsertSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPair &BaseReg, RegSubRegPairAndIdx &InsertedReg) const override |

Build the equivalent inputs of a INSERT_SUBREG for the given MI and DefIdx. More... | |

| MachineInstr * | commuteInstructionImpl (MachineInstr &MI, bool NewMI, unsigned OpIdx1, unsigned OpIdx2) const override |

| Commutes the operands in the given instruction. More... | |

| bool | isCopyInstrImpl (const MachineInstr &MI, const MachineOperand *&Source, const MachineOperand *&Destination) const override |

| If the specific machine instruction is a instruction that moves/copies value from one register to another register return true along with machine operand and machine operand. More... | |

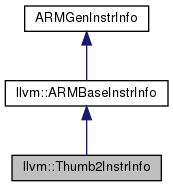

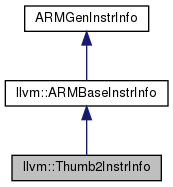

Detailed Description

Definition at line 24 of file Thumb2InstrInfo.h.

Constructor & Destructor Documentation

◆ Thumb2InstrInfo()

|

explicit |

Definition at line 42 of file Thumb2InstrInfo.cpp.

Member Function Documentation

◆ copyPhysReg()

|

override |

Definition at line 122 of file Thumb2InstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), contains(), llvm::ARMBaseInstrInfo::copyPhysReg(), llvm::getKillRegState(), llvm::predOps(), and storeRegToStackSlot().

◆ getNoop()

|

override |

Return the noop instruction to use for a noop.

Definition at line 46 of file Thumb2InstrInfo.cpp.

References llvm::MCInst::addOperand(), llvm::ARMCC::AL, llvm::MCOperand::createImm(), llvm::MCOperand::createReg(), and llvm::MCInst::setOpcode().

◆ getRegisterInfo()

|

inlineoverridevirtual |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info.

As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Implements llvm::ARMBaseInstrInfo.

Definition at line 62 of file Thumb2InstrInfo.h.

References llvm::getITInstrPredicate(), and MI.

◆ getUnindexedOpcode()

Implements llvm::ARMBaseInstrInfo.

Definition at line 53 of file Thumb2InstrInfo.cpp.

◆ isLegalToSplitMBBAt()

|

override |

Definition at line 110 of file Thumb2InstrInfo.cpp.

References llvm::ARMCC::AL, llvm::MachineBasicBlock::end(), and llvm::getITInstrPredicate().

◆ loadRegFromStackSlot()

|

override |

Definition at line 179 of file Thumb2InstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::ARMBaseInstrInfo::AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::RegState::DefineNoRead, llvm::MachineBasicBlock::end(), llvm::ARMBaseInstrInfo::expandLoadStackGuardBase(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getTarget(), llvm::RegState::ImplicitDefine, llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::TargetMachine::isPositionIndependent(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::ARMBaseInstrInfo::loadRegFromStackSlot(), MI, llvm::MachineMemOperand::MOLoad, MRI, and llvm::predOps().

Referenced by storeRegToStackSlot().

◆ ReplaceTailWithBranchTo()

|

override |

Definition at line 59 of file Thumb2InstrInfo.cpp.

References llvm::ARMCC::AL, llvm::MachineBasicBlock::begin(), E, llvm::MachineFunction::getInfo(), llvm::getInstrPredicate(), llvm::MachineBasicBlock::getParent(), llvm::ARMFunctionInfo::hasITBlocks(), llvm::BitmaskEnumDetail::Mask(), and llvm::TargetInstrInfo::ReplaceTailWithBranchTo().

◆ storeRegToStackSlot()

|

override |

Definition at line 136 of file Thumb2InstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::ARMBaseInstrInfo::AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::MachineBasicBlock::end(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::getKillRegState(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterInfo::isVirtualRegister(), loadRegFromStackSlot(), llvm::MachineMemOperand::MOStore, MRI, llvm::predOps(), and llvm::ARMBaseInstrInfo::storeRegToStackSlot().

Referenced by copyPhysReg().

The documentation for this class was generated from the following files:

- lib/Target/ARM/Thumb2InstrInfo.h

- lib/Target/ARM/Thumb2InstrInfo.cpp

1.8.13

1.8.13