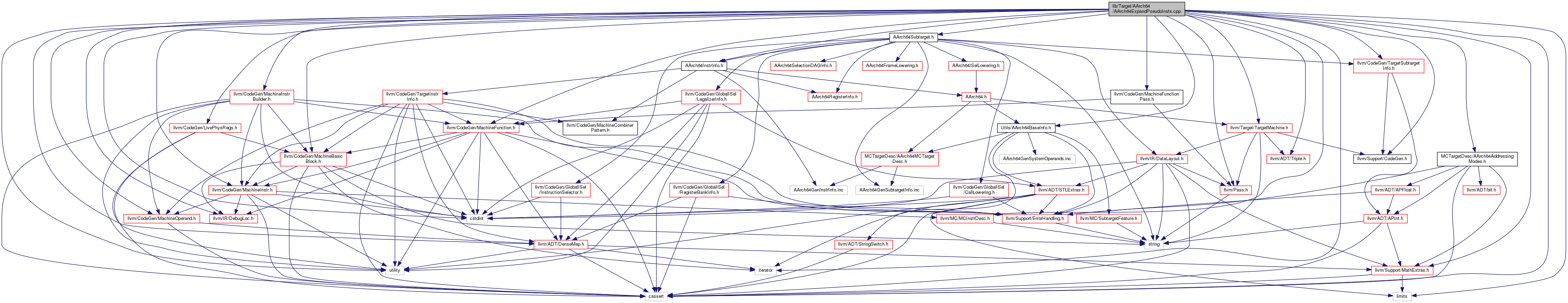

#include "AArch64InstrInfo.h"#include "AArch64Subtarget.h"#include "MCTargetDesc/AArch64AddressingModes.h"#include "Utils/AArch64BaseInfo.h"#include "llvm/ADT/DenseMap.h"#include "llvm/ADT/Triple.h"#include "llvm/CodeGen/LivePhysRegs.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/TargetSubtargetInfo.h"#include "llvm/IR/DebugLoc.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/Pass.h"#include "llvm/Support/CodeGen.h"#include "llvm/Support/MathExtras.h"#include "llvm/Target/TargetMachine.h"#include <cassert>#include <cstdint>#include <iterator>#include <limits>#include <utility>

Go to the source code of this file.

Macros | |

| #define | AARCH64_EXPAND_PSEUDO_NAME "AArch64 pseudo instruction expansion pass" |

Functions | |

| INITIALIZE_PASS (AArch64ExpandPseudo, "aarch64-expand-pseudo", AARCH64_EXPAND_PSEUDO_NAME, false, false) static void transferImpOps(MachineInstr &OldMI | |

| Transfer implicit operands on the pseudo instruction to the instructions created from the expansion. More... | |

| for (unsigned i=Desc.getNumOperands(), e=OldMI.getNumOperands();i !=e;++i) | |

| static uint64_t | getChunk (uint64_t Imm, unsigned ChunkIdx) |

| Helper function which extracts the specified 16-bit chunk from a 64-bit value. More... | |

| static bool | canUseOrr (uint64_t Chunk, uint64_t &Encoding) |

| Check whether the given 16-bit chunk replicated to full 64-bit width can be materialized with an ORR instruction. More... | |

| static bool | tryToreplicateChunks (uint64_t UImm, MachineInstr &MI, MachineBasicBlock &MBB, MachineBasicBlock::iterator &MBBI, const AArch64InstrInfo *TII) |

| Check for identical 16-bit chunks within the constant and if so materialize them with a single ORR instruction. More... | |

| static bool | isStartChunk (uint64_t Chunk) |

| Check whether this chunk matches the pattern '1...0...'. More... | |

| static bool | isEndChunk (uint64_t Chunk) |

| Check whether this chunk matches the pattern '0...1...' This pattern ends a contiguous sequence of ones if we look at the bits from the LSB towards the MSB. More... | |

| static uint64_t | updateImm (uint64_t Imm, unsigned Idx, bool Clear) |

| Clear or set all bits in the chunk at the given index. More... | |

| static bool | trySequenceOfOnes (uint64_t UImm, MachineInstr &MI, MachineBasicBlock &MBB, MachineBasicBlock::iterator &MBBI, const AArch64InstrInfo *TII) |

| Check whether the constant contains a sequence of contiguous ones, which might be interrupted by one or two chunks. More... | |

Variables | |

| MachineInstrBuilder & | UseMI |

| MachineInstrBuilder MachineInstrBuilder & | DefMI |

Macro Definition Documentation

◆ AARCH64_EXPAND_PSEUDO_NAME

| #define AARCH64_EXPAND_PSEUDO_NAME "AArch64 pseudo instruction expansion pass" |

Definition at line 45 of file AArch64ExpandPseudoInsts.cpp.

Function Documentation

◆ canUseOrr()

|

static |

Check whether the given 16-bit chunk replicated to full 64-bit width can be materialized with an ORR instruction.

Definition at line 117 of file AArch64ExpandPseudoInsts.cpp.

References llvm::AArch64_AM::processLogicalImmediate().

◆ for()

| for | ( | unsigned | i = Desc.getNumOperands(), |

| e | = OldMI.getNumOperands(); i != e; ++i |

||

| ) |

Definition at line 96 of file AArch64ExpandPseudoInsts.cpp.

References llvm::MachineInstrBuilder::add(), assert(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), and UseMI.

Referenced by analyzeGlobalAux(), llvm::DwarfDebug::beginModule(), CalcNodeSethiUllmanNumber(), checkDyldCommand(), checkDylibCommand(), checkRpathCommand(), checkSubCommand(), collectBitParts(), llvm::AppleAcceleratorTable::dump(), llvm::BitTracker::RegisterCell::extract(), llvm::sampleprof::FunctionSamples::findFunctionSamplesAt(), firstch(), freeset(), freezeset(), getLayoutSuccessorProbThreshold(), llvm::TargetLowering::getMultipleConstraintMatchWeight(), getUnderlyingArgReg(), llvm::MCCodePadder::handleInstructionEnd(), INITIALIZE_PASS(), llvm::InsertPointAnalysis::InsertPointAnalysis(), isLoadConditional(), isProfitableChain(), mayUsePostIncMode(), nch(), llvm::BitVector::operator &=(), llvm::operator<<(), and llvm::UnrollLoop().

◆ getChunk()

|

static |

Helper function which extracts the specified 16-bit chunk from a 64-bit value.

Definition at line 109 of file AArch64ExpandPseudoInsts.cpp.

References assert().

Referenced by trySequenceOfOnes(), and tryToreplicateChunks().

◆ INITIALIZE_PASS()

| INITIALIZE_PASS | ( | AArch64ExpandPseudo | , |

| "aarch64-expand-pseudo" | , | ||

| AARCH64_EXPAND_PSEUDO_NAME | , | ||

| false | , | ||

| false | |||

| ) | & |

Transfer implicit operands on the pseudo instruction to the instructions created from the expansion.

◆ isEndChunk()

|

static |

Check whether this chunk matches the pattern '0...1...' This pattern ends a contiguous sequence of ones if we look at the bits from the LSB towards the MSB.

Definition at line 230 of file AArch64ExpandPseudoInsts.cpp.

References llvm::isMask_64(), and llvm::max().

Referenced by trySequenceOfOnes().

◆ isStartChunk()

|

static |

Check whether this chunk matches the pattern '1...0...'.

This pattern starts a contiguous sequence of ones if we look at the bits from the LSB towards the MSB.

Definition at line 220 of file AArch64ExpandPseudoInsts.cpp.

References llvm::isMask_64(), and llvm::max().

Referenced by trySequenceOfOnes().

◆ trySequenceOfOnes()

|

static |

Check whether the constant contains a sequence of contiguous ones, which might be interrupted by one or two chunks.

If so, materialize the sequence of contiguous ones with an ORR instruction. Materialize the chunks which are either interrupting the sequence or outside of the sequence with a MOVK instruction.

Assuming S is a chunk which starts the sequence (1...0...), E is a chunk which ends the sequence (0...1...). Then we are looking for constants which contain at least one S and E chunk. E.g. |E|A|B|S|, |A|E|B|S| or |A|B|E|S|.

We are also looking for constants like |S|A|B|E| where the contiguous sequence of ones wraps around the MSB into the LSB.

Definition at line 264 of file AArch64ExpandPseudoInsts.cpp.

References llvm::ARM_AM::add, llvm::MachineInstrBuilder::addConstantPoolIndex(), llvm::MachineInstrBuilder::addExternalSymbol(), llvm::MachineInstrBuilder::addGlobalAddress(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineInstrBuilder::addUse(), llvm::AArch64ISD::ADRP, assert(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::computeAndAddLiveIns(), llvm::countLeadingZeros(), llvm::countTrailingZeros(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::RegState::Define, E, llvm::MachineBasicBlock::end(), llvm::AArch64CC::EQ, llvm::MachineInstr::eraseFromParent(), llvm::AArch64_AM::getArithExtendImm(), llvm::MachineBasicBlock::getBasicBlock(), getChunk(), llvm::TargetMachine::getCodeModel(), llvm::getDeadRegState(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getGlobal(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::getKillRegState(), llvm::MachineOperand::getOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::AArch64_AM::getShifterImm(), llvm::MachineFunction::getSubtarget(), llvm::MachineOperand::getSymbolName(), llvm::MachineFunction::getTarget(), llvm::MachineOperand::getTargetFlags(), llvm::TargetMachine::getTargetTriple(), llvm::X86II::Imm16, llvm::RegState::Implicit, llvm::MachineFunction::insert(), llvm::MachineOperand::isCPI(), llvm::MachineOperand::isDead(), isEndChunk(), llvm::MachineOperand::isGlobal(), llvm::Triple::isOSFuchsia(), isStartChunk(), llvm::MachineOperand::isSymbol(), llvm::MachineOperand::isUndef(), llvm::CodeModel::Kernel, llvm::RegState::Kill, llvm::AArch64ISD::LOADgot, llvm::AArch64_AM::LSL, llvm::BitmaskEnumDetail::Mask(), MI, llvm::AArch64II::MO_NC, llvm::AArch64II::MO_PAGE, llvm::AArch64II::MO_PAGEOFF, Modified, llvm::AArch64CC::NE, llvm::AArch64_AM::processLogicalImmediate(), llvm::ARCISD::RET, std::swap(), TII, llvm::CodeModel::Tiny, tryToreplicateChunks(), llvm::RegState::Undef, updateImm(), llvm::AArch64_AM::UXTB, and llvm::AArch64_AM::UXTH.

◆ tryToreplicateChunks()

|

static |

Check for identical 16-bit chunks within the constant and if so materialize them with a single ORR instruction.

The remaining one or two 16-bit chunks will be materialized with MOVK instructions.

This allows us to materialize constants like |A|B|A|A| or |A|B|C|A| (order of the chunks doesn't matter), assuming |A|A|A|A| can be materialized with an ORR instruction.

Definition at line 130 of file AArch64ExpandPseudoInsts.cpp.

References getChunk().

Referenced by trySequenceOfOnes().

◆ updateImm()

Clear or set all bits in the chunk at the given index.

Definition at line 238 of file AArch64ExpandPseudoInsts.cpp.

References llvm::BitmaskEnumDetail::Mask().

Referenced by trySequenceOfOnes().

Variable Documentation

◆ DefMI

Definition at line 94 of file AArch64ExpandPseudoInsts.cpp.

Referenced by addSegmentsWithValNo(), allPhiOperandsUndefined(), canFoldIntoCSel(), llvm::LiveRangeEdit::checkRematerializable(), llvm::SIInstrInfo::commuteOpcode(), llvm::ScheduleDAGMILive::computeCyclicCriticalPath(), llvm::PPCInstrInfo::convertToImmediateForm(), llvm::LiveRangeEdit::create(), llvm::createSIWholeQuadModePass(), llvm::createX86OptimizeLEAs(), CriticalPathStep(), definesFullReg(), llvm::SplitEditor::dump(), llvm::LiveRangeEdit::eraseVirtReg(), getDepthOfOptCmov(), llvm::ARMHazardRecognizer::getHazardType(), llvm::MachineTraceMetrics::Trace::getInstrCycles(), llvm::AArch64RegisterBankInfo::getInstrMapping(), llvm::getOpcodeDef(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::TargetSchedModel::getResourceBufferSize(), getSingleDef(), getUnderlyingObjects(), hoistAndMergeSGPRInits(), INITIALIZE_PASS(), isCrossCopy(), isFullCopyOf(), isKilled(), llvm::ARMBaseInstrInfo::isProfitableToDupForIfCvt(), llvm::X86InstrInfo::isSubregFoldable(), isVirtualRegisterOperand(), llvm::TargetInstrInfo::isZeroCost(), llvm::AArch64InstrInfo::optimizeCondBranch(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), pushDepHeight(), regIsPICBase(), removeCopies(), llvm::PPCInstrInfo::replaceInstrWithLI(), scavengeVReg(), swapMIOperands(), llvm::TailDuplicator::tailDuplicateAndUpdate(), llvm::CombinerHelper::tryCombineCopy(), llvm::LegalizationArtifactCombiner::tryCombineInstruction(), llvm::LegalizationArtifactCombiner::tryFoldImplicitDef(), updatePHIs(), updatePhysDepsDownwards(), usedAsAddr(), and llvm::MachineTraceMetrics::Ensemble::verify().

◆ UseMI

| MachineInstrBuilder& UseMI |

Definition at line 93 of file AArch64ExpandPseudoInsts.cpp.

Referenced by addSegmentsWithValNo(), llvm::SIInstrInfo::commuteOpcode(), computeBranchTargetAndInversion(), CriticalPathStep(), llvm::LiveRangeEdit::eraseVirtReg(), llvm::SMSchedule::finalizeSchedule(), findOnlyInterestingUse(), llvm::ARMBaseInstrInfo::FoldImmediate(), for(), llvm::MachineTraceMetrics::Trace::getInstrCycles(), llvm::AArch64RegisterBankInfo::getInstrMapping(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::RegScavenger::getRegsAvailable(), llvm::TargetSchedModel::getResourceBufferSize(), getUnderlyingObjects(), INITIALIZE_PASS(), isCallerPreservedOrConstPhysReg(), isCopyFeedingInvariantStore(), isCrossCopy(), isDefLiveOut(), isEFLAGSLive(), isFullCopyOf(), llvm::ARMBaseInstrInfo::isProfitableToDupForIfCvt(), llvm::PPCInstrInfo::isSameClassPhysRegCopy(), llvm::X86InstrInfo::isSubregFoldable(), isUseSafeToFold(), isVirtualRegisterOperand(), llvm::TargetInstrInfo::isZeroCost(), llvm::MachineRegisterInfo::markUsesInDebugValueAsUndef(), llvm::SIInstrInfo::moveToVALU(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::SIInstrInfo::readlaneVGPRToSGPR(), regOverlapsSet(), removePhis(), llvm::MachineSSAUpdater::RewriteUse(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::RegScavenger::scavengeRegister(), llvm::RegScavenger::scavengeRegisterBackwards(), llvm::LiveIntervals::shrinkToUses(), llvm::TailDuplicator::tailDuplicateAndUpdate(), tryChangeVGPRtoSGPRinCopy(), llvm::CombinerHelper::tryCombineCopy(), llvm::CombinerHelper::tryCombineExtendingLoads(), llvm::MachineTraceMetrics::Ensemble::updateDepth(), updatePhysDepsDownwards(), and usedAsAddr().

1.8.13

1.8.13