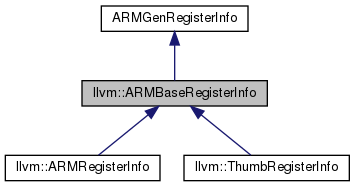

#include "Target/ARM/ARMBaseRegisterInfo.h"

Protected Member Functions | |

| ARMBaseRegisterInfo () | |

| unsigned | getOpcode (int Op) const |

Protected Attributes | |

| unsigned | BasePtr = ARM::R6 |

| BasePtr - ARM physical register used as a base ptr in complex stack frames. More... | |

Detailed Description

Definition at line 98 of file ARMBaseRegisterInfo.h.

Constructor & Destructor Documentation

◆ ARMBaseRegisterInfo()

|

explicitprotected |

Definition at line 58 of file ARMBaseRegisterInfo.cpp.

Member Function Documentation

◆ cannotEliminateFrame()

| bool ARMBaseRegisterInfo::cannotEliminateFrame | ( | const MachineFunction & | MF | ) | const |

Definition at line 420 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineFrameInfo::adjustsStack(), llvm::TargetOptions::DisableFramePointerElim(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getTarget(), llvm::MachineFrameInfo::hasVarSizedObjects(), llvm::MachineFrameInfo::isFrameAddressTaken(), and llvm::TargetMachine::Options.

Referenced by canRealignStack(), and llvm::ARMFrameLowering::determineCalleeSaves().

◆ canRealignStack()

|

override |

Definition at line 398 of file ARMBaseRegisterInfo.cpp.

References BasePtr, cannotEliminateFrame(), llvm::TargetRegisterInfo::canRealignStack(), llvm::MachineRegisterInfo::canReserveReg(), getFramePointerReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), llvm::ARMFrameLowering::hasReservedCallFrame(), and MRI.

Referenced by needsFrameBaseReg().

◆ eliminateFrameIndex()

|

override |

Definition at line 731 of file ARMBaseRegisterInfo.cpp.

References llvm::ARMII::AddrMode4, llvm::ARMII::AddrMode6, llvm::ARMII::AddrModeMask, llvm::ARMCC::AL, assert(), llvm::MachineOperand::ChangeToRegister(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::emitARMRegPlusImmediate(), llvm::emitT2RegPlusImmediate(), llvm::MachineInstr::findFirstPredOperandIdx(), llvm::ISD::FrameIndex, llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineFunction::getFrameInfo(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineFunction::getInfo(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), llvm::ARMFrameLowering::hasReservedCallFrame(), llvm::MachineFrameInfo::hasVarSizedObjects(), llvm::MachineInstr::isDebugValue(), llvm::RegScavenger::isScavengingFrameIndex(), llvm::ARMFunctionInfo::isThumb1OnlyFunction(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::ARMFunctionInfo::isThumbFunction(), MI, llvm::ARMFrameLowering::ResolveFrameIndexReference(), llvm::rewriteARMFrameIndex(), llvm::rewriteT2FrameIndex(), TII, and llvm::MCInstrDesc::TSFlags.

Referenced by llvm::ThumbRegisterInfo::eliminateFrameIndex().

◆ emitLoadConstPool()

|

virtual |

emitLoadConstPool - Emits a load from constpool to materialize the specified immediate.

Reimplemented in llvm::ThumbRegisterInfo.

Definition at line 440 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), C, llvm::MCInstrInfo::get(), llvm::ConstantInt::get(), llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstantPoolIndex(), llvm::Function::getContext(), llvm::getDefRegState(), llvm::MachineFunction::getFunction(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::Type::getInt32Ty(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getSubtarget(), llvm::predOps(), requiresRegisterScavenging(), llvm::MachineInstrBuilder::setMIFlags(), and TII.

Referenced by emitThumbRegPlusImmInReg().

◆ getBaseRegister()

|

inline |

Definition at line 178 of file ARMBaseRegisterInfo.h.

References llvm::ARMCC::AL, MI, llvm::MachineInstr::NoFlags, Reg, and SubReg.

Referenced by llvm::ARMFrameLowering::determineCalleeSaves(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), and llvm::ARMFrameLowering::ResolveFrameIndexReference().

◆ getCalleeSavedRegs()

|

override |

Code Generation virtual methods...

Definition at line 66 of file ARMBaseRegisterInfo.cpp.

References llvm::CallingConv::CXX_FAST_TLS, F(), llvm::Function::getAttributes(), llvm::Function::getCallingConv(), llvm::Function::getFnAttribute(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), llvm::MachineFunction::getSubtarget(), llvm::ARMSubtarget::getTargetLowering(), llvm::Attribute::getValueAsString(), llvm::CallingConv::GHC, llvm::AttributeList::hasAttrSomewhere(), llvm::Function::hasFnAttribute(), llvm::ARMSubtarget::isMClass(), llvm::ARMFunctionInfo::isSplitCSR(), llvm::ARMSubtarget::isTargetDarwin(), llvm::ARMSubtarget::splitFramePushPop(), llvm::ARMTargetLowering::supportSwiftError(), and llvm::Attribute::SwiftError.

Referenced by llvm::ARMFrameLowering::determineCalleeSaves(), and llvm::ARMTargetLowering::ReplaceNodeResults().

◆ getCalleeSavedRegsViaCopy()

| const MCPhysReg * ARMBaseRegisterInfo::getCalleeSavedRegsViaCopy | ( | const MachineFunction * | MF | ) | const |

Definition at line 111 of file ARMBaseRegisterInfo.cpp.

References assert(), llvm::CallingConv::CXX_FAST_TLS, llvm::Function::getCallingConv(), llvm::MachineFunction::getFunction(), and llvm::MachineFunction::getInfo().

Referenced by llvm::ARMTargetLowering::getExceptionSelectorRegister(), and LowerInterruptReturn().

◆ getCallPreservedMask()

|

override |

Definition at line 121 of file ARMBaseRegisterInfo.cpp.

References llvm::CallingConv::CXX_FAST_TLS, llvm::Function::getAttributes(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getSubtarget(), llvm::ARMSubtarget::getTargetLowering(), llvm::CallingConv::GHC, llvm::AttributeList::hasAttrSomewhere(), llvm::ARMSubtarget::isTargetDarwin(), llvm::ARMTargetLowering::supportSwiftError(), and llvm::Attribute::SwiftError.

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn(), and MatchingStackOffset().

◆ getCrossCopyRegClass()

|

override |

Definition at line 245 of file ARMBaseRegisterInfo.cpp.

◆ getFrameIndexInstrOffset()

|

override |

Definition at line 480 of file ARMBaseRegisterInfo.cpp.

References llvm::ARMII::AddrMode2, llvm::ARMII::AddrMode3, llvm::ARMII::AddrMode5, llvm::ARMII::AddrMode_i12, llvm::ARMII::AddrModeMask, llvm::ARMII::AddrModeT1_s, llvm::ARMII::AddrModeT2_i12, llvm::ARMII::AddrModeT2_i8, llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM3Offset(), llvm::ARM_AM::getAM3Op(), llvm::ARM_AM::getAM5Offset(), llvm::ARM_AM::getAM5Op(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), llvm_unreachable, needsFrameBaseReg(), llvm::ARM_AM::sub, and llvm::MCInstrDesc::TSFlags.

Referenced by isFrameOffsetLegal(), and requiresVirtualBaseRegisters().

◆ getFrameRegister()

|

override |

Definition at line 429 of file ARMBaseRegisterInfo.cpp.

References getFramePointerReg(), and llvm::MachineFunction::getSubtarget().

Referenced by addExclusiveRegPair(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), getComparePred(), LowerVectorINT_TO_FP(), needsFrameBaseReg(), llvm::ARMFrameLowering::ResolveFrameIndexReference(), llvm::Thumb1FrameLowering::restoreCalleeSavedRegisters(), and llvm::Thumb1FrameLowering::spillCalleeSavedRegisters().

◆ getLargestLegalSuperClass()

|

override |

Definition at line 218 of file ARMBaseRegisterInfo.cpp.

References llvm::TargetRegisterClass::getID(), llvm::TargetRegisterClass::getSuperClasses(), and I.

Referenced by llvm::ThumbRegisterInfo::getLargestLegalSuperClass().

◆ getNoPreservedMask()

Definition at line 139 of file ARMBaseRegisterInfo.cpp.

◆ getOpcode()

|

protected |

◆ getPointerRegClass()

|

override |

Definition at line 239 of file ARMBaseRegisterInfo.cpp.

Referenced by llvm::ThumbRegisterInfo::getPointerRegClass().

◆ getRegAllocationHints()

|

override |

Definition at line 289 of file ARMBaseRegisterInfo.cpp.

References getPairedGPR(), llvm::VirtRegMap::getPhys(), llvm::MachineRegisterInfo::getRegAllocationHint(), llvm::TargetRegisterInfo::getRegAllocationHints(), llvm::MachineFunction::getRegInfo(), llvm::VirtRegMap::hasPhys(), llvm::is_contained(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineRegisterInfo::isReserved(), MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), Reg, llvm::ARMRI::RegPairEven, and llvm::ARMRI::RegPairOdd.

◆ getRegPressureLimit()

|

override |

◆ getReservedRegs()

|

override |

Definition at line 179 of file ARMBaseRegisterInfo.cpp.

References assert(), BasePtr, getFramePointerReg(), llvm::MachineFunction::getSubtarget(), hasBasePointer(), llvm::ARMSubtarget::hasD16(), llvm::ARMSubtarget::hasVFP3(), isAsmClobberable(), llvm::ARMSubtarget::isR9Reserved(), Reg, SI, and llvm::BitVector::test().

Referenced by getThisReturnPreservedMask(), and isAsmClobberable().

◆ getSjLjDispatchPreservedMask()

| const uint32_t * ARMBaseRegisterInfo::getSjLjDispatchPreservedMask | ( | const MachineFunction & | MF | ) | const |

Definition at line 151 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineFunction::getSubtarget(), llvm::ARMSubtarget::hasVFP2(), llvm::ARMSubtarget::isThumb1Only(), and llvm::ARMSubtarget::useSoftFloat().

Referenced by llvm::ARMTargetLowering::ReplaceNodeResults().

◆ getThisReturnPreservedMask()

| const uint32_t * ARMBaseRegisterInfo::getThisReturnPreservedMask | ( | const MachineFunction & | MF, |

| CallingConv::ID | CC | ||

| ) | const |

getThisReturnPreservedMask - Returns a call preserved mask specific to the case that 'returned' is on an i32 first argument if the calling convention is one that can (partially) model this attribute with a preserved mask (i.e.

it is a calling convention that uses the same register for the first i32 argument and an i32 return value)

Should return NULL in the case that the calling convention does not have this property

Definition at line 160 of file ARMBaseRegisterInfo.cpp.

References getReservedRegs(), llvm::MachineFunction::getSubtarget(), llvm::CallingConv::GHC, and llvm::ARMSubtarget::isTargetDarwin().

Referenced by llvm::ARMTargetLowering::CCAssignFnForReturn().

◆ getTLSCallPreservedMask()

| const uint32_t * ARMBaseRegisterInfo::getTLSCallPreservedMask | ( | const MachineFunction & | MF | ) | const |

Definition at line 144 of file ARMBaseRegisterInfo.cpp.

References assert(), llvm::MachineFunction::getSubtarget(), and llvm::ARMSubtarget::isTargetDarwin().

◆ hasBasePointer()

| bool ARMBaseRegisterInfo::hasBasePointer | ( | const MachineFunction & | MF | ) | const |

Definition at line 367 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::MachineFrameInfo::getLocalFrameSize(), llvm::MachineFrameInfo::hasVarSizedObjects(), llvm::ARMFunctionInfo::isThumb2Function(), and llvm::ARMFunctionInfo::isThumbFunction().

Referenced by addExclusiveRegPair(), llvm::ARMFrameLowering::determineCalleeSaves(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), getReservedRegs(), and llvm::ARMFrameLowering::ResolveFrameIndexReference().

◆ isAsmClobberable()

|

override |

Definition at line 213 of file ARMBaseRegisterInfo.cpp.

References getReservedRegs(), and llvm::BitVector::test().

Referenced by getReservedRegs().

◆ isFrameOffsetLegal()

|

override |

Definition at line 665 of file ARMBaseRegisterInfo.cpp.

References llvm::ARMII::AddrMode2, llvm::ARMII::AddrMode3, llvm::ARMII::AddrMode4, llvm::ARMII::AddrMode5, llvm::ARMII::AddrMode6, llvm::ARMII::AddrMode_i12, llvm::ARMII::AddrModeMask, llvm::ARMII::AddrModeT1_s, llvm::ARMII::AddrModeT2_i12, llvm::ARMII::AddrModeT2_i8, assert(), llvm::MachineInstr::getDesc(), getFrameIndexInstrOffset(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::isFI(), llvm_unreachable, llvm::BitmaskEnumDetail::Mask(), and llvm::MCInstrDesc::TSFlags.

Referenced by needsFrameBaseReg().

◆ isLowRegister()

◆ materializeFrameBaseRegister()

|

override |

materializeFrameBaseRegister - Insert defining instruction(s) for BaseReg to be a pointer to FrameIdx at the beginning of the basic block.

Definition at line 612 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::ARMCC::AL, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::condCodeOp(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::MachineBasicBlock::end(), llvm::MCInstrInfo::get(), llvm::MachineFunction::getInfo(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineBasicBlock::getParent(), llvm::TargetInstrInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), llvm::MipsISD::Ins, llvm::ARMFunctionInfo::isThumb1OnlyFunction(), llvm::ARMFunctionInfo::isThumbFunction(), MRI, llvm::predOps(), and TII.

Referenced by needsFrameBaseReg().

◆ needsFrameBaseReg()

|

override |

needsFrameBaseReg - Returns true if the instruction's frame index reference would be better served by a base register other than FP or SP.

Used by LocalStackFrameAllocation to determine which frame index references it should create new base registers for.

Definition at line 531 of file ARMBaseRegisterInfo.cpp.

References assert(), canRealignStack(), llvm::MachineFunction::getFrameInfo(), getFrameRegister(), llvm::MachineFunction::getInfo(), llvm::MachineFrameInfo::getLocalFrameMaxAlign(), llvm::MachineFrameInfo::getLocalFrameSize(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::TargetFrameLowering::getStackAlignment(), llvm::ARMFrameLowering::hasFP(), llvm::MachineFrameInfo::hasVarSizedObjects(), llvm::MachineOperand::isFI(), isFrameOffsetLegal(), llvm::ARMFunctionInfo::isThumb1OnlyFunction(), llvm::ARMFunctionInfo::isThumbFunction(), and materializeFrameBaseRegister().

Referenced by getFrameIndexInstrOffset().

◆ requiresFrameIndexScavenging()

|

override |

Definition at line 470 of file ARMBaseRegisterInfo.cpp.

References requiresVirtualBaseRegisters().

Referenced by trackLivenessAfterRegAlloc().

◆ requiresRegisterScavenging()

|

override |

Code Generation virtual methods...

Definition at line 460 of file ARMBaseRegisterInfo.cpp.

References trackLivenessAfterRegAlloc().

Referenced by emitLoadConstPool().

◆ requiresVirtualBaseRegisters()

|

override |

Definition at line 475 of file ARMBaseRegisterInfo.cpp.

References getFrameIndexInstrOffset().

Referenced by requiresFrameIndexScavenging().

◆ resolveFrameIndex()

|

override |

Definition at line 637 of file ARMBaseRegisterInfo.cpp.

References assert(), llvm::MachineFunction::getInfo(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineFunction::getSubtarget(), llvm::MachineOperand::isFI(), llvm::ARMFunctionInfo::isThumb1OnlyFunction(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::ARMFunctionInfo::isThumbFunction(), llvm::rewriteARMFrameIndex(), llvm::rewriteT2FrameIndex(), and TII.

Referenced by llvm::ThumbRegisterInfo::resolveFrameIndex().

◆ shouldCoalesce()

|

override |

SrcRC and DstRC will be morphed into NewRC if this returns true.

Definition at line 807 of file ARMBaseRegisterInfo.cpp.

References llvm::dbgs(), llvm::ARMFunctionInfo::getCoalescedWeight(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::TargetRegisterInfo::getRegClassWeight(), llvm::MachineRegisterInfo::getTargetRegisterInfo(), LLVM_DEBUG, and MRI.

◆ trackLivenessAfterRegAlloc()

|

override |

Definition at line 465 of file ARMBaseRegisterInfo.cpp.

References requiresFrameIndexScavenging().

Referenced by requiresRegisterScavenging().

◆ updateRegAllocHint()

|

override |

Definition at line 343 of file ARMBaseRegisterInfo.cpp.

References llvm::MachineRegisterInfo::getRegAllocationHint(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterInfo::isVirtualRegister(), MRI, llvm::ARMRI::RegPairEven, llvm::ARMRI::RegPairOdd, and llvm::MachineRegisterInfo::setRegAllocationHint().

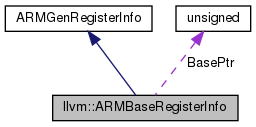

Member Data Documentation

◆ BasePtr

BasePtr - ARM physical register used as a base ptr in complex stack frames.

I.e., when we need a 3rd base, not just SP and FP, due to variable size stack objects.

Definition at line 103 of file ARMBaseRegisterInfo.h.

Referenced by canRealignStack(), and getReservedRegs().

The documentation for this class was generated from the following files:

- lib/Target/ARM/ARMBaseRegisterInfo.h

- lib/Target/ARM/ARMBaseRegisterInfo.cpp

1.8.13

1.8.13