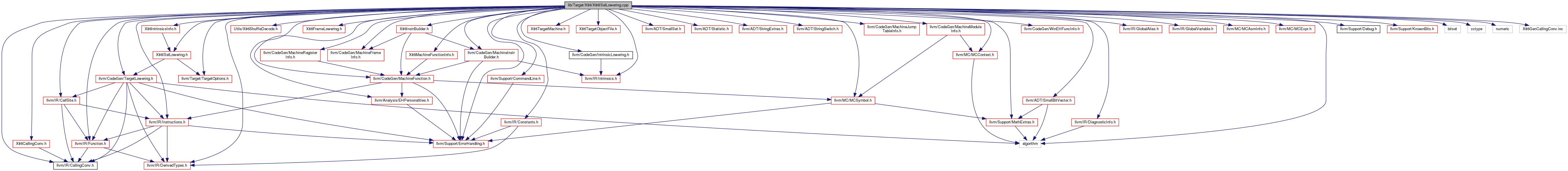

#include "X86ISelLowering.h"#include "Utils/X86ShuffleDecode.h"#include "X86CallingConv.h"#include "X86FrameLowering.h"#include "X86InstrBuilder.h"#include "X86IntrinsicsInfo.h"#include "X86MachineFunctionInfo.h"#include "X86TargetMachine.h"#include "X86TargetObjectFile.h"#include "llvm/ADT/SmallBitVector.h"#include "llvm/ADT/SmallSet.h"#include "llvm/ADT/Statistic.h"#include "llvm/ADT/StringExtras.h"#include "llvm/ADT/StringSwitch.h"#include "llvm/Analysis/EHPersonalities.h"#include "llvm/CodeGen/IntrinsicLowering.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineJumpTableInfo.h"#include "llvm/CodeGen/MachineModuleInfo.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/TargetLowering.h"#include "llvm/CodeGen/WinEHFuncInfo.h"#include "llvm/IR/CallSite.h"#include "llvm/IR/CallingConv.h"#include "llvm/IR/Constants.h"#include "llvm/IR/DerivedTypes.h"#include "llvm/IR/DiagnosticInfo.h"#include "llvm/IR/Function.h"#include "llvm/IR/GlobalAlias.h"#include "llvm/IR/GlobalVariable.h"#include "llvm/IR/Instructions.h"#include "llvm/IR/Intrinsics.h"#include "llvm/MC/MCAsmInfo.h"#include "llvm/MC/MCContext.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCSymbol.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/KnownBits.h"#include "llvm/Support/MathExtras.h"#include "llvm/Target/TargetOptions.h"#include <algorithm>#include <bitset>#include <cctype>#include <numeric>#include "X86GenCallingConv.inc"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "x86-isel" |

Enumerations | |

| enum | StructReturnType { NotStructReturn, RegStructReturn, StackStructReturn } |

| CallIsStructReturn - Determines whether a call uses struct return semantics. More... | |

| enum | ShrinkMode { MULS8, MULU8, MULS16, MULU16 } |

| Different mul shrinking modes. More... | |

Functions | |

| STATISTIC (NumTailCalls, "Number of tail calls") | |

| static void | errorUnsupported (SelectionDAG &DAG, const SDLoc &dl, const char *Msg) |

| Call this when the user attempts to do something unsupported, like returning a double without SSE2 enabled on x86_64. More... | |

| static void | getMaxByValAlign (Type *Ty, unsigned &MaxAlign) |

| Helper for getByValTypeAlignment to determine the desired ByVal argument alignment. More... | |

| static bool | hasStackGuardSlotTLS (const Triple &TargetTriple) |

| static Constant * | SegmentOffset (IRBuilder<> &IRB, unsigned Offset, unsigned AddressSpace) |

| static SDValue | lowerMasksToReg (const SDValue &ValArg, const EVT &ValLoc, const SDLoc &Dl, SelectionDAG &DAG) |

| Lowers masks values (v*i1) to the local register values. More... | |

| static void | Passv64i1ArgInRegs (const SDLoc &Dl, SelectionDAG &DAG, SDValue Chain, SDValue &Arg, SmallVector< std::pair< unsigned, SDValue >, 8 > &RegsToPass, CCValAssign &VA, CCValAssign &NextVA, const X86Subtarget &Subtarget) |

| Breaks v64i1 value into two registers and adds the new node to the DAG. More... | |

| static SDValue | getv64i1Argument (CCValAssign &VA, CCValAssign &NextVA, SDValue &Root, SelectionDAG &DAG, const SDLoc &Dl, const X86Subtarget &Subtarget, SDValue *InFlag=nullptr) |

| Reads two 32 bit registers and creates a 64 bit mask value. More... | |

| static SDValue | lowerRegToMasks (const SDValue &ValArg, const EVT &ValVT, const EVT &ValLoc, const SDLoc &Dl, SelectionDAG &DAG) |

| The function will lower a register of various sizes (8/16/32/64) to a mask value of the expected size (v8i1/v16i1/v32i1/v64i1) More... | |

| static StructReturnType | callIsStructReturn (ArrayRef< ISD::OutputArg > Outs, bool IsMCU) |

| static StructReturnType | argsAreStructReturn (ArrayRef< ISD::InputArg > Ins, bool IsMCU) |

| Determines whether a function uses struct return semantics. More... | |

| static SDValue | CreateCopyOfByValArgument (SDValue Src, SDValue Dst, SDValue Chain, ISD::ArgFlagsTy Flags, SelectionDAG &DAG, const SDLoc &dl) |

| Make a copy of an aggregate at address specified by "Src" to address "Dst" with size and alignment information specified by the specific parameter attribute. More... | |

| static bool | canGuaranteeTCO (CallingConv::ID CC) |

| Return true if the calling convention is one that we can guarantee TCO for. More... | |

| static bool | mayTailCallThisCC (CallingConv::ID CC) |

| Return true if we might ever do TCO for calls with this calling convention. More... | |

| static bool | shouldGuaranteeTCO (CallingConv::ID CC, bool GuaranteedTailCallOpt) |

| Return true if the function is being made into a tailcall target by changing its ABI. More... | |

| static ArrayRef< MCPhysReg > | get64BitArgumentGPRs (CallingConv::ID CallConv, const X86Subtarget &Subtarget) |

| static ArrayRef< MCPhysReg > | get64BitArgumentXMMs (MachineFunction &MF, CallingConv::ID CallConv, const X86Subtarget &Subtarget) |

| static bool | isSortedByValueNo (ArrayRef< CCValAssign > ArgLocs) |

| static SDValue | EmitTailCallStoreRetAddr (SelectionDAG &DAG, MachineFunction &MF, SDValue Chain, SDValue RetAddrFrIdx, EVT PtrVT, unsigned SlotSize, int FPDiff, const SDLoc &dl) |

| Emit a store of the return address if tail call optimization is performed and it is required (FPDiff!=0). More... | |

| static SDValue | getMOVL (SelectionDAG &DAG, const SDLoc &dl, MVT VT, SDValue V1, SDValue V2) |

| Returns a vector_shuffle mask for an movs{s|d}, movd operation of specified width. More... | |

| static bool | MatchingStackOffset (SDValue Arg, unsigned Offset, ISD::ArgFlagsTy Flags, MachineFrameInfo &MFI, const MachineRegisterInfo *MRI, const X86InstrInfo *TII, const CCValAssign &VA) |

| Return true if the given stack call argument is already available in the same position (relatively) of the caller's incoming argument stack. More... | |

| static bool | MayFoldLoad (SDValue Op) |

| static bool | MayFoldIntoStore (SDValue Op) |

| static bool | MayFoldIntoZeroExtend (SDValue Op) |

| static bool | isTargetShuffle (unsigned Opcode) |

| static bool | isTargetShuffleVariableMask (unsigned Opcode) |

| static bool | isX86CCUnsigned (unsigned X86CC) |

| Return true if the condition is an unsigned comparison operation. More... | |

| static X86::CondCode | TranslateIntegerX86CC (ISD::CondCode SetCCOpcode) |

| static X86::CondCode | TranslateX86CC (ISD::CondCode SetCCOpcode, const SDLoc &DL, bool isFP, SDValue &LHS, SDValue &RHS, SelectionDAG &DAG) |

| Do a one-to-one translation of a ISD::CondCode to the X86-specific condition code, returning the condition code and the LHS/RHS of the comparison to make. More... | |

| static bool | hasFPCMov (unsigned X86CC) |

| Is there a floating point cmov for the specific X86 condition code? Current x86 isa includes the following FP cmov instructions: fcmovb, fcomvbe, fcomve, fcmovu, fcmovae, fcmova, fcmovne, fcmovnu. More... | |

| static bool | isUndefOrEqual (int Val, int CmpVal) |

| Val is the undef sentinel value or equal to the specified value. More... | |

| static bool | isUndefOrZero (int Val) |

| Val is either the undef or zero sentinel value. More... | |

| static bool | isUndefInRange (ArrayRef< int > Mask, unsigned Pos, unsigned Size) |

| Return true if every element in Mask, beginning from position Pos and ending in Pos+Size is the undef sentinel value. More... | |

| static bool | isInRange (int Val, int Low, int Hi) |

| Return true if Val falls within the specified range (L, H]. More... | |

| static bool | isAnyInRange (ArrayRef< int > Mask, int Low, int Hi) |

| Return true if the value of any element in Mask falls within the specified range (L, H]. More... | |

| static bool | isUndefOrInRange (int Val, int Low, int Hi) |

| Return true if Val is undef or if its value falls within the specified range (L, H]. More... | |

| static bool | isUndefOrInRange (ArrayRef< int > Mask, int Low, int Hi) |

| Return true if every element in Mask is undef or if its value falls within the specified range (L, H]. More... | |

| static bool | isUndefOrZeroOrInRange (int Val, int Low, int Hi) |

| Return true if Val is undef, zero or if its value falls within the specified range (L, H]. More... | |

| static bool | isUndefOrZeroOrInRange (ArrayRef< int > Mask, int Low, int Hi) |

| Return true if every element in Mask is undef, zero or if its value falls within the specified range (L, H]. More... | |

| static bool | isSequentialOrUndefInRange (ArrayRef< int > Mask, unsigned Pos, unsigned Size, int Low, int Step=1) |

| Return true if every element in Mask, beginning from position Pos and ending in Pos + Size, falls within the specified sequence (Low, Low + Step, ..., Low + (Size - 1) * Step) or is undef. More... | |

| static bool | isSequentialOrUndefOrZeroInRange (ArrayRef< int > Mask, unsigned Pos, unsigned Size, int Low) |

| Return true if every element in Mask, beginning from position Pos and ending in Pos+Size, falls within the specified sequential range (Low, Low+Size], or is undef or is zero. More... | |

| static bool | isUndefOrZeroInRange (ArrayRef< int > Mask, unsigned Pos, unsigned Size) |

| Return true if every element in Mask, beginning from position Pos and ending in Pos+Size is undef or is zero. More... | |

| static bool | canWidenShuffleElements (ArrayRef< int > Mask, SmallVectorImpl< int > &WidenedMask) |

| Helper function to test whether a shuffle mask could be simplified by widening the elements being shuffled. More... | |

| static bool | canWidenShuffleElements (ArrayRef< int > Mask, const APInt &Zeroable, SmallVectorImpl< int > &WidenedMask) |

| static bool | canWidenShuffleElements (ArrayRef< int > Mask) |

| static SDValue | getConstVector (ArrayRef< int > Values, MVT VT, SelectionDAG &DAG, const SDLoc &dl, bool IsMask=false) |

| static SDValue | getConstVector (ArrayRef< APInt > Bits, APInt &Undefs, MVT VT, SelectionDAG &DAG, const SDLoc &dl) |

| static SDValue | getZeroVector (MVT VT, const X86Subtarget &Subtarget, SelectionDAG &DAG, const SDLoc &dl) |

| Returns a vector of specified type with all zero elements. More... | |

| static SDValue | extractSubVector (SDValue Vec, unsigned IdxVal, SelectionDAG &DAG, const SDLoc &dl, unsigned vectorWidth) |

| static SDValue | extract128BitVector (SDValue Vec, unsigned IdxVal, SelectionDAG &DAG, const SDLoc &dl) |

| Generate a DAG to grab 128-bits from a vector > 128 bits. More... | |

| static SDValue | extract256BitVector (SDValue Vec, unsigned IdxVal, SelectionDAG &DAG, const SDLoc &dl) |

| Generate a DAG to grab 256-bits from a 512-bit vector. More... | |

| static SDValue | insertSubVector (SDValue Result, SDValue Vec, unsigned IdxVal, SelectionDAG &DAG, const SDLoc &dl, unsigned vectorWidth) |

| static SDValue | insert128BitVector (SDValue Result, SDValue Vec, unsigned IdxVal, SelectionDAG &DAG, const SDLoc &dl) |

| Generate a DAG to put 128-bits into a vector > 128 bits. More... | |

| static SDValue | widenSubVector (MVT VT, SDValue Vec, bool ZeroNewElements, const X86Subtarget &Subtarget, SelectionDAG &DAG, const SDLoc &dl) |

| Widen a vector to a larger size with the same scalar type, with the new elements either zero or undef. More... | |

| template<typename F > | |

| SDValue | SplitOpsAndApply (SelectionDAG &DAG, const X86Subtarget &Subtarget, const SDLoc &DL, EVT VT, ArrayRef< SDValue > Ops, F Builder, bool CheckBWI=true) |

| static bool | isMaskedZeroUpperBitsvXi1 (unsigned int Opcode) |

| static SDValue | insert1BitVector (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Insert i1-subvector to i1-vector. More... | |

| static SDValue | concatSubVectors (SDValue V1, SDValue V2, EVT VT, unsigned NumElems, SelectionDAG &DAG, const SDLoc &dl, unsigned VectorWidth) |

| static SDValue | getOnesVector (EVT VT, SelectionDAG &DAG, const SDLoc &dl) |

| Returns a vector of specified type with all bits set. More... | |

| static SDValue | getExtendInVec (bool Signed, const SDLoc &DL, EVT VT, SDValue In, SelectionDAG &DAG) |

| static SDValue | getUnpackl (SelectionDAG &DAG, const SDLoc &dl, MVT VT, SDValue V1, SDValue V2) |

| Returns a vector_shuffle node for an unpackl operation. More... | |

| static SDValue | getUnpackh (SelectionDAG &DAG, const SDLoc &dl, MVT VT, SDValue V1, SDValue V2) |

| Returns a vector_shuffle node for an unpackh operation. More... | |

| static SDValue | getShuffleVectorZeroOrUndef (SDValue V2, int Idx, bool IsZero, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Return a vector_shuffle of the specified vector of zero or undef vector. More... | |

| static SDValue | peekThroughEXTRACT_SUBVECTORs (SDValue V) |

| static const Constant * | getTargetConstantFromNode (SDValue Op) |

| static bool | getTargetConstantBitsFromNode (SDValue Op, unsigned EltSizeInBits, APInt &UndefElts, SmallVectorImpl< APInt > &EltBits, bool AllowWholeUndefs=true, bool AllowPartialUndefs=true) |

| static bool | isConstantSplat (SDValue Op, APInt &SplatVal) |

| static bool | getTargetShuffleMaskIndices (SDValue MaskNode, unsigned MaskEltSizeInBits, SmallVectorImpl< uint64_t > &RawMask, APInt &UndefElts) |

| static void | createPackShuffleMask (MVT VT, SmallVectorImpl< int > &Mask, bool Unary) |

| Create a shuffle mask that matches the PACKSS/PACKUS truncation. More... | |

| static void | getPackDemandedElts (EVT VT, const APInt &DemandedElts, APInt &DemandedLHS, APInt &DemandedRHS) |

| static bool | getTargetShuffleMask (SDNode *N, MVT VT, bool AllowSentinelZero, SmallVectorImpl< SDValue > &Ops, SmallVectorImpl< int > &Mask, bool &IsUnary) |

| Calculates the shuffle mask corresponding to the target-specific opcode. More... | |

| static bool | setTargetShuffleZeroElements (SDValue N, SmallVectorImpl< int > &Mask, SmallVectorImpl< SDValue > &Ops) |

| Check a target shuffle mask's inputs to see if we can set any values to SM_SentinelZero - this is for elements that are known to be zero (not just zeroable) from their inputs. More... | |

| static bool | resolveTargetShuffleInputs (SDValue Op, SmallVectorImpl< SDValue > &Inputs, SmallVectorImpl< int > &Mask, const SelectionDAG &DAG) |

| Calls setTargetShuffleZeroElements to resolve a target shuffle mask's inputs and set the SM_SentinelUndef and SM_SentinelZero values. More... | |

| static bool | getFauxShuffleMask (SDValue N, SmallVectorImpl< int > &Mask, SmallVectorImpl< SDValue > &Ops, const SelectionDAG &DAG) |

| static void | resolveTargetShuffleInputsAndMask (SmallVectorImpl< SDValue > &Inputs, SmallVectorImpl< int > &Mask) |

| Removes unused shuffle source inputs and adjusts the shuffle mask accordingly. More... | |

| static SDValue | getShuffleScalarElt (SDNode *N, unsigned Index, SelectionDAG &DAG, unsigned Depth) |

| Returns the scalar element that will make up the ith element of the result of the vector shuffle. More... | |

| static SDValue | LowerBuildVectorAsInsert (SDValue Op, unsigned NonZeros, unsigned NumNonZero, unsigned NumZero, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerBuildVectorv16i8 (SDValue Op, unsigned NonZeros, unsigned NumNonZero, unsigned NumZero, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Custom lower build_vector of v16i8. More... | |

| static SDValue | LowerBuildVectorv8i16 (SDValue Op, unsigned NonZeros, unsigned NumNonZero, unsigned NumZero, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Custom lower build_vector of v8i16. More... | |

| static SDValue | LowerBuildVectorv4x32 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Custom lower build_vector of v4i32 or v4f32. More... | |

| static SDValue | getVShift (bool isLeft, EVT VT, SDValue SrcOp, unsigned NumBits, SelectionDAG &DAG, const TargetLowering &TLI, const SDLoc &dl) |

| Return a vector logical shift node. More... | |

| static SDValue | LowerAsSplatVectorLoad (SDValue SrcOp, MVT VT, const SDLoc &dl, SelectionDAG &DAG) |

| static SDValue | EltsFromConsecutiveLoads (EVT VT, ArrayRef< SDValue > Elts, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, bool isAfterLegalize) |

| Given the initializing elements 'Elts' of a vector of type 'VT', see if the elements can be replaced by a single large load which has the same value as a build_vector or insert_subvector whose loaded operands are 'Elts'. More... | |

| static Constant * | getConstantVector (MVT VT, const APInt &SplatValue, unsigned SplatBitSize, LLVMContext &C) |

| static bool | isUseOfShuffle (SDNode *N) |

| static SDValue | isSplatZeroExtended (const BuildVectorSDNode *Op, unsigned &NumElt, MVT &EltType) |

| static SDValue | lowerBuildVectorAsBroadcast (BuildVectorSDNode *BVOp, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Attempt to use the vbroadcast instruction to generate a splat value from a splat BUILD_VECTOR which uses: a. More... | |

| static int | getUnderlyingExtractedFromVec (SDValue &ExtractedFromVec, SDValue ExtIdx) |

| For an EXTRACT_VECTOR_ELT with a constant index return the real underlying vector and index. More... | |

| static SDValue | buildFromShuffleMostly (SDValue Op, SelectionDAG &DAG) |

| static SDValue | ConvertI1VectorToInteger (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerBUILD_VECTORvXi1 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static bool | isHorizontalBinOpPart (const BuildVectorSDNode *N, unsigned Opcode, SelectionDAG &DAG, unsigned BaseIdx, unsigned LastIdx, SDValue &V0, SDValue &V1) |

| This is a helper function of LowerToHorizontalOp(). More... | |

| static SDValue | ExpandHorizontalBinOp (const SDValue &V0, const SDValue &V1, const SDLoc &DL, SelectionDAG &DAG, unsigned X86Opcode, bool Mode, bool isUndefLO, bool isUndefHI) |

| Emit a sequence of two 128-bit horizontal add/sub followed by a concat_vector. More... | |

| static bool | isAddSubOrSubAdd (const BuildVectorSDNode *BV, const X86Subtarget &Subtarget, SelectionDAG &DAG, SDValue &Opnd0, SDValue &Opnd1, unsigned &NumExtracts, bool &IsSubAdd) |

Returns true iff BV builds a vector with the result equivalent to the result of ADDSUB/SUBADD operation. More... | |

| static bool | isFMAddSubOrFMSubAdd (const X86Subtarget &Subtarget, SelectionDAG &DAG, SDValue &Opnd0, SDValue &Opnd1, SDValue &Opnd2, unsigned ExpectedUses) |

Returns true if is possible to fold MUL and an idiom that has already been recognized as ADDSUB/SUBADD(Opnd0, Opnd1) into FMADDSUB/FMSUBADD(x, y, Opnd1). More... | |

| static SDValue | lowerToAddSubOrFMAddSub (const BuildVectorSDNode *BV, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to fold a build_vector that performs an 'addsub' or 'fmaddsub' or 'fsubadd' operation accordingly to X86ISD::ADDSUB or X86ISD::FMADDSUB or X86ISD::FMSUBADD node. More... | |

| static bool | isHopBuildVector (const BuildVectorSDNode *BV, SelectionDAG &DAG, unsigned &HOpcode, SDValue &V0, SDValue &V1) |

| static SDValue | getHopForBuildVector (const BuildVectorSDNode *BV, SelectionDAG &DAG, unsigned HOpcode, SDValue V0, SDValue V1) |

| static SDValue | LowerToHorizontalOp (const BuildVectorSDNode *BV, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower BUILD_VECTOR to a horizontal add/sub operation if possible. More... | |

| static SDValue | lowerBuildVectorToBitOp (BuildVectorSDNode *Op, SelectionDAG &DAG) |

| If a BUILD_VECTOR's source elements all apply the same bit operation and one of their operands is constant, lower to a pair of BUILD_VECTOR and just apply the bit to the vectors. More... | |

| static SDValue | materializeVectorConstant (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Create a vector constant without a load. More... | |

| static SDValue | createVariablePermute (MVT VT, SDValue SrcVec, SDValue IndicesVec, SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Look for opportunities to create a VPERMV/VPERMILPV/PSHUFB variable permute from a vector of source values and a vector of extraction indices. More... | |

| static SDValue | LowerBUILD_VECTORAsVariablePermute (SDValue V, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerAVXCONCAT_VECTORS (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static bool | isExpandWithZeros (const SDValue &Op) |

| static SDValue | isTypePromotionOfi1ZeroUpBits (SDValue Op) |

| static SDValue | LowerCONCAT_VECTORSvXi1 (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerCONCAT_VECTORS (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static bool | isNoopShuffleMask (ArrayRef< int > Mask) |

| Tiny helper function to identify a no-op mask. More... | |

| static bool | is128BitLaneCrossingShuffleMask (MVT VT, ArrayRef< int > Mask) |

| Test whether there are elements crossing 128-bit lanes in this shuffle mask. More... | |

| static bool | isRepeatedShuffleMask (unsigned LaneSizeInBits, MVT VT, ArrayRef< int > Mask, SmallVectorImpl< int > &RepeatedMask) |

| Test whether a shuffle mask is equivalent within each sub-lane. More... | |

| static bool | is128BitLaneRepeatedShuffleMask (MVT VT, ArrayRef< int > Mask, SmallVectorImpl< int > &RepeatedMask) |

| Test whether a shuffle mask is equivalent within each 128-bit lane. More... | |

| static bool | is128BitLaneRepeatedShuffleMask (MVT VT, ArrayRef< int > Mask) |

| static bool | is256BitLaneRepeatedShuffleMask (MVT VT, ArrayRef< int > Mask, SmallVectorImpl< int > &RepeatedMask) |

| Test whether a shuffle mask is equivalent within each 256-bit lane. More... | |

| static bool | isRepeatedTargetShuffleMask (unsigned LaneSizeInBits, MVT VT, ArrayRef< int > Mask, SmallVectorImpl< int > &RepeatedMask) |

| Test whether a target shuffle mask is equivalent within each sub-lane. More... | |

| static bool | isShuffleEquivalent (SDValue V1, SDValue V2, ArrayRef< int > Mask, ArrayRef< int > ExpectedMask) |

| Checks whether a shuffle mask is equivalent to an explicit list of arguments. More... | |

| static bool | isTargetShuffleEquivalent (ArrayRef< int > Mask, ArrayRef< int > ExpectedMask) |

| Checks whether a target shuffle mask is equivalent to an explicit pattern. More... | |

| static SmallVector< int, 64 > | createTargetShuffleMask (ArrayRef< int > Mask, const APInt &Zeroable) |

| static bool | createShuffleMaskFromVSELECT (SmallVectorImpl< int > &Mask, SDValue Cond) |

| static bool | isUnpackWdShuffleMask (ArrayRef< int > Mask, MVT VT) |

| static unsigned | getV4X86ShuffleImm (ArrayRef< int > Mask) |

| Get a 4-lane 8-bit shuffle immediate for a mask. More... | |

| static SDValue | getV4X86ShuffleImm8ForMask (ArrayRef< int > Mask, const SDLoc &DL, SelectionDAG &DAG) |

| static APInt | computeZeroableShuffleElements (ArrayRef< int > Mask, SDValue V1, SDValue V2) |

| Compute whether each element of a shuffle is zeroable. More... | |

| static bool | isNonZeroElementsInOrder (const APInt &Zeroable, ArrayRef< int > Mask, const EVT &VectorType, bool &IsZeroSideLeft) |

| static SDValue | lowerVectorShuffleWithPSHUFB (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a shuffle with a single PSHUFB of V1 or V2. More... | |

| static SDValue | getMaskNode (SDValue Mask, MVT MaskVT, const X86Subtarget &Subtarget, SelectionDAG &DAG, const SDLoc &dl) |

Return Mask with the necessary casting or extending for Mask according to MaskVT when lowering masking intrinsics. More... | |

| static SDValue | lowerVectorShuffleToEXPAND (const SDLoc &DL, MVT VT, const APInt &Zeroable, ArrayRef< int > Mask, SDValue &V1, SDValue &V2, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static bool | matchVectorShuffleWithUNPCK (MVT VT, SDValue &V1, SDValue &V2, unsigned &UnpackOpcode, bool IsUnary, ArrayRef< int > TargetMask, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerVectorShuffleWithUNPCK (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, SelectionDAG &DAG) |

| static bool | matchVectorShuffleAsVPMOV (ArrayRef< int > Mask, bool SwappedOps, int Delta) |

| static SDValue | lowerVectorShuffleWithVPMOV (const SDLoc &DL, ArrayRef< int > Mask, MVT VT, SDValue V1, SDValue V2, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static bool | matchVectorShuffleWithPACK (MVT VT, MVT &SrcVT, SDValue &V1, SDValue &V2, unsigned &PackOpcode, ArrayRef< int > TargetMask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerVectorShuffleWithPACK (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerVectorShuffleAsBitMask (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, SelectionDAG &DAG) |

| Try to emit a bitmask instruction for a shuffle. More... | |

| static SDValue | lowerVectorShuffleAsBitBlend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG) |

| Try to emit a blend instruction for a shuffle using bit math. More... | |

| static SDValue | getVectorMaskingNode (SDValue Op, SDValue Mask, SDValue PreservedSrc, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

Return (and Op, Mask) for compare instructions or (vselect Mask, Op, PreservedSrc) for others along with the necessary casting or extending for Mask when lowering masking intrinsics. More... | |

| static bool | matchVectorShuffleAsBlend (SDValue V1, SDValue V2, MutableArrayRef< int > TargetMask, bool &ForceV1Zero, bool &ForceV2Zero, uint64_t &BlendMask) |

| static uint64_t | scaleVectorShuffleBlendMask (uint64_t BlendMask, int Size, int Scale) |

| static SDValue | lowerVectorShuffleAsBlend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Original, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to emit a blend instruction for a shuffle. More... | |

| static SDValue | lowerVectorShuffleAsBlendAndPermute (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG, bool ImmBlends=false) |

| Try to lower as a blend of elements from two inputs followed by a single-input permutation. More... | |

| static SDValue | lowerVectorShuffleAsUNPCKAndPermute (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG) |

| Try to lower as an unpack of elements from two inputs followed by a single-input permutation. More... | |

| static SDValue | lowerVectorShuffleAsByteRotateAndPermute (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Helper to form a PALIGNR-based rotate+permute, merging 2 inputs and then permuting the elements of the result in place. More... | |

| static SDValue | lowerVectorShuffleAsDecomposedShuffleBlend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Generic routine to decompose a shuffle and blend into independent blends and permutes. More... | |

| static int | matchVectorShuffleAsRotate (SDValue &V1, SDValue &V2, ArrayRef< int > Mask) |

| Try to lower a vector shuffle as a rotation. More... | |

| static int | matchVectorShuffleAsByteRotate (MVT VT, SDValue &V1, SDValue &V2, ArrayRef< int > Mask) |

| Try to lower a vector shuffle as a byte rotation. More... | |

| static SDValue | lowerVectorShuffleAsByteRotate (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | lowerVectorShuffleAsRotate (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a vector shuffle as a dword/qword rotation. More... | |

| static int | matchVectorShuffleAsShift (MVT &ShiftVT, unsigned &Opcode, unsigned ScalarSizeInBits, ArrayRef< int > Mask, int MaskOffset, const APInt &Zeroable, const X86Subtarget &Subtarget) |

| Try to lower a vector shuffle as a bit shift (shifts in zeros). More... | |

| static SDValue | lowerVectorShuffleAsShift (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static bool | matchVectorShuffleAsEXTRQ (MVT VT, SDValue &V1, SDValue &V2, ArrayRef< int > Mask, uint64_t &BitLen, uint64_t &BitIdx, const APInt &Zeroable) |

| static bool | matchVectorShuffleAsINSERTQ (MVT VT, SDValue &V1, SDValue &V2, ArrayRef< int > Mask, uint64_t &BitLen, uint64_t &BitIdx) |

| static SDValue | lowerVectorShuffleWithSSE4A (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, SelectionDAG &DAG) |

| Try to lower a vector shuffle using SSE4a EXTRQ/INSERTQ. More... | |

| static SDValue | lowerVectorShuffleAsSpecificZeroOrAnyExtend (const SDLoc &DL, MVT VT, int Scale, int Offset, bool AnyExt, SDValue InputV, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower a vector shuffle as a zero or any extension. More... | |

| static SDValue | lowerVectorShuffleAsZeroOrAnyExtend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a vector shuffle as a zero extension on any microarch. More... | |

| static SDValue | getScalarValueForVectorElement (SDValue V, int Idx, SelectionDAG &DAG) |

| Try to get a scalar value for a specific element of a vector. More... | |

| static bool | isShuffleFoldableLoad (SDValue V) |

| Helper to test for a load that can be folded with x86 shuffles. More... | |

| static SDValue | lowerVectorShuffleAsElementInsertion (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower insertion of a single element into a zero vector. More... | |

| static SDValue | lowerVectorShuffleAsTruncBroadcast (const SDLoc &DL, MVT VT, SDValue V0, int BroadcastIdx, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

Try to lower broadcast of a single - truncated - integer element, coming from a scalar_to_vector/build_vector node V0 with larger elements. More... | |

| static SDValue | lowerVectorShuffleAsBroadcast (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower broadcast of a single element. More... | |

| static bool | matchVectorShuffleAsInsertPS (SDValue &V1, SDValue &V2, unsigned &InsertPSMask, const APInt &Zeroable, ArrayRef< int > Mask, SelectionDAG &DAG) |

| static SDValue | lowerVectorShuffleAsInsertPS (const SDLoc &DL, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, SelectionDAG &DAG) |

| static SDValue | lowerVectorShuffleAsPermuteAndUnpack (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a shuffle as a permute of the inputs followed by an UNPCK instruction. More... | |

| static SDValue | lowerV2F64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 2-lane 64-bit floating point shuffles. More... | |

| static SDValue | lowerV2I64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 2-lane 64-bit integer shuffles. More... | |

| static bool | isSingleSHUFPSMask (ArrayRef< int > Mask) |

| Test whether this can be lowered with a single SHUFPS instruction. More... | |

| static SDValue | lowerVectorShuffleWithSHUFPS (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, SelectionDAG &DAG) |

| Lower a vector shuffle using the SHUFPS instruction. More... | |

| static SDValue | lowerV4F32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower 4-lane 32-bit floating point shuffles. More... | |

| static SDValue | lowerV4I32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower 4-lane i32 vector shuffles. More... | |

| static SDValue | lowerV8I16GeneralSingleInputVectorShuffle (const SDLoc &DL, MVT VT, SDValue V, MutableArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lowering of single-input v8i16 shuffles is the cornerstone of SSE2 shuffle lowering, and the most complex part. More... | |

| static SDValue | lowerVectorShuffleAsBlendOfPSHUFBs (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, SelectionDAG &DAG, bool &V1InUse, bool &V2InUse) |

| Helper to form a PSHUFB-based shuffle+blend, opportunistically avoiding the blend if only one input is used. More... | |

| static SDValue | lowerV8I16VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Generic lowering of 8-lane i16 shuffles. More... | |

| static int | canLowerByDroppingEvenElements (ArrayRef< int > Mask, bool IsSingleInput) |

| Check whether a compaction lowering can be done by dropping even elements and compute how many times even elements must be dropped. More... | |

| static SDValue | lowerVectorShuffleWithPERMV (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, SelectionDAG &DAG) |

| static SDValue | lowerV16I8VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Generic lowering of v16i8 shuffles. More... | |

| static SDValue | lower128BitVectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, MVT VT, SDValue V1, SDValue V2, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Dispatching routine to lower various 128-bit x86 vector shuffles. More... | |

| static SDValue | splitAndLowerVectorShuffle (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG) |

| Generic routine to split vector shuffle into half-sized shuffles. More... | |

| static SDValue | lowerVectorShuffleAsSplitOrBlend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Either split a vector in halves or decompose the shuffles and the blend. More... | |

| static SDValue | lowerVectorShuffleAsLanePermuteAndPermute (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Lower a vector shuffle crossing multiple 128-bit lanes as a lane permutation followed by a per-lane permutation. More... | |

| static SDValue | lowerVectorShuffleAsLanePermuteAndBlend (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Lower a vector shuffle crossing multiple 128-bit lanes as a permutation and blend of those lanes. More... | |

| static SDValue | lowerV2X128VectorShuffle (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering 2-lane 128-bit shuffles. More... | |

| static SDValue | lowerVectorShuffleByMerging128BitLanes (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower a vector shuffle by first fixing the 128-bit lanes and then shuffling each lane. More... | |

| static SDValue | lowerVectorShuffleWithUndefHalf (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Lower shuffles where an entire half of a 256 or 512-bit vector is UNDEF. More... | |

| static bool | isShuffleMaskInputInPlace (int Input, ArrayRef< int > Mask) |

| Test whether the specified input (0 or 1) is in-place blended by the given mask. More... | |

| static SDValue | lowerShuffleAsRepeatedMaskAndLanePermute (const SDLoc &DL, MVT VT, SDValue V1, SDValue V2, ArrayRef< int > Mask, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle case where shuffle sources are coming from the same 128-bit lane and every lane can be represented as the same repeating mask - allowing us to shuffle the sources with the repeating shuffle and then permute the result to the destination lanes. More... | |

| static bool | matchVectorShuffleWithSHUFPD (MVT VT, SDValue &V1, SDValue &V2, unsigned &ShuffleImm, ArrayRef< int > Mask) |

| static SDValue | lowerVectorShuffleWithSHUFPD (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, SDValue V1, SDValue V2, SelectionDAG &DAG) |

| static SDValue | lowerV4F64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 4-lane 64-bit floating point shuffles. More... | |

| static SDValue | lowerV4I64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 4-lane 64-bit integer shuffles. More... | |

| static SDValue | lowerV8F32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 8-lane 32-bit floating point shuffles. More... | |

| static SDValue | lowerV8I32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 8-lane 32-bit integer shuffles. More... | |

| static SDValue | lowerV16I16VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 16-lane 16-bit integer shuffles. More... | |

| static SDValue | lowerV32I8VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 32-lane 8-bit integer shuffles. More... | |

| static SDValue | lower256BitVectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, MVT VT, SDValue V1, SDValue V2, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| High-level routine to lower various 256-bit x86 vector shuffles. More... | |

| static SDValue | lowerV4X128VectorShuffle (const SDLoc &DL, MVT VT, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a vector shuffle as a 128-bit shuffles. More... | |

| static SDValue | lowerV8F64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 8-lane 64-bit floating point shuffles. More... | |

| static SDValue | lowerV16F32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 16-lane 32-bit floating point shuffles. More... | |

| static SDValue | lowerV8I64VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 8-lane 64-bit integer shuffles. More... | |

| static SDValue | lowerV16I32VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 16-lane 32-bit integer shuffles. More... | |

| static SDValue | lowerV32I16VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 32-lane 16-bit integer shuffles. More... | |

| static SDValue | lowerV64I8VectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, const APInt &Zeroable, SDValue V1, SDValue V2, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle lowering of 64-lane 8-bit integer shuffles. More... | |

| static SDValue | lower512BitVectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, MVT VT, SDValue V1, SDValue V2, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| High-level routine to lower various 512-bit x86 vector shuffles. More... | |

| static int | match1BitShuffleAsKSHIFT (unsigned &Opcode, ArrayRef< int > Mask, int MaskOffset, const APInt &Zeroable) |

| static SDValue | lower1BitVectorShuffle (const SDLoc &DL, ArrayRef< int > Mask, MVT VT, SDValue V1, SDValue V2, const APInt &Zeroable, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static bool | canonicalizeShuffleMaskWithCommute (ArrayRef< int > Mask) |

| Helper function that returns true if the shuffle mask should be commuted to improve canonicalization. More... | |

| static SDValue | lowerVectorShuffle (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Top-level lowering for x86 vector shuffles. More... | |

| static SDValue | lowerVSELECTtoVectorShuffle (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to lower a VSELECT instruction to a vector shuffle. More... | |

| static SDValue | LowerEXTRACT_VECTOR_ELT_SSE4 (SDValue Op, SelectionDAG &DAG) |

| static SDValue | ExtractBitFromMaskVector (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Extract one bit from mask vector, like v16i1 or v8i1. More... | |

| static SDValue | InsertBitToMaskVector (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Insert one bit to mask vector, like v16i1 or v8i1. More... | |

| static SDValue | LowerSCALAR_TO_VECTOR (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerINSERT_SUBVECTOR (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerEXTRACT_SUBVECTOR (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | GetTLSADDR (SelectionDAG &DAG, SDValue Chain, GlobalAddressSDNode *GA, SDValue *InFlag, const EVT PtrVT, unsigned ReturnReg, unsigned char OperandFlags, bool LocalDynamic=false) |

| static SDValue | LowerToTLSGeneralDynamicModel32 (GlobalAddressSDNode *GA, SelectionDAG &DAG, const EVT PtrVT) |

| static SDValue | LowerToTLSGeneralDynamicModel64 (GlobalAddressSDNode *GA, SelectionDAG &DAG, const EVT PtrVT) |

| static SDValue | LowerToTLSLocalDynamicModel (GlobalAddressSDNode *GA, SelectionDAG &DAG, const EVT PtrVT, bool is64Bit) |

| static SDValue | LowerToTLSExecModel (GlobalAddressSDNode *GA, SelectionDAG &DAG, const EVT PtrVT, TLSModel::Model model, bool is64Bit, bool isPIC) |

| static SDValue | LowerShiftParts (SDValue Op, SelectionDAG &DAG) |

| Lower SRA_PARTS and friends, which return two i32 values and take a 2 x i32 value to shift plus a shift amount. More... | |

| static SDValue | LowerFunnelShift (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerI64IntToFP_AVX512DQ (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerUINT_TO_FP_i64 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| 64-bit unsigned integer to double expansion. More... | |

| static SDValue | LowerUINT_TO_FP_i32 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| 32-bit unsigned integer to float expansion. More... | |

| static SDValue | lowerUINT_TO_FP_v2i32 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget, const SDLoc &DL) |

| static SDValue | lowerUINT_TO_FP_vXi32 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerUINT_TO_FP_vec (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerAVXExtend (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | SplitAndExtendv16i1 (unsigned ExtOpc, MVT VT, SDValue In, const SDLoc &dl, SelectionDAG &DAG) |

| static SDValue | LowerZERO_EXTEND_Mask (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerZERO_EXTEND (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | truncateVectorWithPACK (unsigned Opcode, EVT DstVT, SDValue In, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Helper to recursively truncate vector elements in half with PACKSS/PACKUS. More... | |

| static SDValue | LowerTruncateVecI1 (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerFP_EXTEND (SDValue Op, SelectionDAG &DAG) |

| static bool | shouldUseHorizontalOp (bool IsSingleSource, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Horizontal vector math instructions may be slower than normal math with shuffles. More... | |

| static SDValue | lowerAddSubToHorizontalOp (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Depending on uarch and/or optimizing for size, we might prefer to use a vector operation in place of the typical scalar operation. More... | |

| static SDValue | lowerFaddFsub (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Depending on uarch and/or optimizing for size, we might prefer to use a vector operation in place of the typical scalar operation. More... | |

| static SDValue | LowerFABSorFNEG (SDValue Op, SelectionDAG &DAG) |

| The only differences between FABS and FNEG are the mask and the logic op. More... | |

| static SDValue | LowerFCOPYSIGN (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerFGETSIGN (SDValue Op, SelectionDAG &DAG) |

| static SDValue | getSETCC (X86::CondCode Cond, SDValue EFLAGS, const SDLoc &dl, SelectionDAG &DAG) |

| Helper for creating a X86ISD::SETCC node. More... | |

| static SDValue | LowerVectorAllZeroTest (SDValue Op, ISD::CondCode CC, const X86Subtarget &Subtarget, SelectionDAG &DAG, SDValue &X86CC) |

| static bool | hasNonFlagsUse (SDValue Op) |

return true if Op has a use that doesn't just read flags. More... | |

| static SDValue | EmitTest (SDValue Op, unsigned X86CC, const SDLoc &dl, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Emit nodes that will be selected as "test Op0,Op0", or something equivalent. More... | |

| static SDValue | LowerAndToBT (SDValue And, ISD::CondCode CC, const SDLoc &dl, SelectionDAG &DAG, SDValue &X86CC) |

| Result of 'and' is compared against zero. More... | |

| static unsigned | translateX86FSETCC (ISD::CondCode SetCCOpcode, SDValue &Op0, SDValue &Op1) |

| Turns an ISD::CondCode into a value suitable for SSE floating-point mask CMPs. More... | |

| static SDValue | Lower256IntVSETCC (SDValue Op, SelectionDAG &DAG) |

| Break a VSETCC 256-bit integer VSETCC into two new 128 ones and then concatenate the result back. More... | |

| static SDValue | LowerIntVSETCC_AVX512 (SDValue Op, SelectionDAG &DAG) |

| static SDValue | decrementVectorConstant (SDValue V, SelectionDAG &DAG) |

| Given a simple buildvector constant, return a new vector constant with each element decremented. More... | |

| static SDValue | LowerVSETCCWithSUBUS (SDValue Op0, SDValue Op1, MVT VT, ISD::CondCode Cond, const SDLoc &dl, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| As another special case, use PSUBUS[BW] when it's profitable. More... | |

| static SDValue | LowerVSETCC (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | EmitKORTEST (SDValue Op0, SDValue Op1, ISD::CondCode CC, const SDLoc &dl, SelectionDAG &DAG, const X86Subtarget &Subtarget, SDValue &X86CC) |

| static std::pair< SDValue, SDValue > | getX86XALUOOp (X86::CondCode &Cond, SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerXALUO (SDValue Op, SelectionDAG &DAG) |

| static bool | isX86LogicalCmp (SDValue Op) |

| Return true if opcode is a X86 logical comparison. More... | |

| static bool | isTruncWithZeroHighBitsInput (SDValue V, SelectionDAG &DAG) |

| static SDValue | LowerSIGN_EXTEND_Mask (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerANY_EXTEND (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerEXTEND_VECTOR_INREG (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerSIGN_EXTEND (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerStore (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerLoad (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static bool | isAndOrOfSetCCs (SDValue Op, unsigned &Opc) |

| Return true if node is an ISD::AND or ISD::OR of two X86ISD::SETCC nodes each of which has no other use apart from the AND / OR. More... | |

| static bool | isXor1OfSetCC (SDValue Op) |

| Return true if node is an ISD::XOR of a X86ISD::SETCC and 1 and that the SETCC node has a single use. More... | |

| static SDValue | LowerVACOPY (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static unsigned | getTargetVShiftUniformOpcode (unsigned Opc, bool IsVariable) |

| static SDValue | getTargetVShiftByConstNode (unsigned Opc, const SDLoc &dl, MVT VT, SDValue SrcOp, uint64_t ShiftAmt, SelectionDAG &DAG) |

| Handle vector element shifts where the shift amount is a constant. More... | |

| static SDValue | getTargetVShiftNode (unsigned Opc, const SDLoc &dl, MVT VT, SDValue SrcOp, SDValue ShAmt, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Handle vector element shifts where the shift amount may or may not be a constant. More... | |

| static SDValue | getScalarMaskingNode (SDValue Op, SDValue Mask, SDValue PreservedSrc, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Creates an SDNode for a predicated scalar operation. More... | |

| static int | getSEHRegistrationNodeSize (const Function *Fn) |

| static SDValue | recoverFramePointer (SelectionDAG &DAG, const Function *Fn, SDValue EntryEBP) |

| When the MSVC runtime transfers control to us, either to an outlined function or when returning to a parent frame after catching an exception, we recover the parent frame pointer by doing arithmetic on the incoming EBP. More... | |

| static SDValue | getAVX2GatherNode (unsigned Opc, SDValue Op, SelectionDAG &DAG, SDValue Src, SDValue Mask, SDValue Base, SDValue Index, SDValue ScaleOp, SDValue Chain, const X86Subtarget &Subtarget) |

| static SDValue | getGatherNode (unsigned Opc, SDValue Op, SelectionDAG &DAG, SDValue Src, SDValue Mask, SDValue Base, SDValue Index, SDValue ScaleOp, SDValue Chain, const X86Subtarget &Subtarget) |

| static SDValue | getScatterNode (unsigned Opc, SDValue Op, SelectionDAG &DAG, SDValue Src, SDValue Mask, SDValue Base, SDValue Index, SDValue ScaleOp, SDValue Chain, const X86Subtarget &Subtarget) |

| static SDValue | getPrefetchNode (unsigned Opc, SDValue Op, SelectionDAG &DAG, SDValue Mask, SDValue Base, SDValue Index, SDValue ScaleOp, SDValue Chain, const X86Subtarget &Subtarget) |

| static void | getExtendedControlRegister (SDNode *N, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, SmallVectorImpl< SDValue > &Results) |

| Handles the lowering of builtin intrinsic that return the value of the extended control register. More... | |

| static void | getReadPerformanceCounter (SDNode *N, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, SmallVectorImpl< SDValue > &Results) |

| Handles the lowering of builtin intrinsics that read performance monitor counters (x86_rdpmc). More... | |

| static void | getReadTimeStampCounter (SDNode *N, const SDLoc &DL, unsigned Opcode, SelectionDAG &DAG, const X86Subtarget &Subtarget, SmallVectorImpl< SDValue > &Results) |

| Handles the lowering of builtin intrinsics that read the time stamp counter (x86_rdtsc and x86_rdtscp). More... | |

| static SDValue | LowerREADCYCLECOUNTER (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | MarkEHRegistrationNode (SDValue Op, SelectionDAG &DAG) |

| static SDValue | MarkEHGuard (SDValue Op, SelectionDAG &DAG) |

| static SDValue | EmitTruncSStore (bool SignedSat, SDValue Chain, const SDLoc &Dl, SDValue Val, SDValue Ptr, EVT MemVT, MachineMemOperand *MMO, SelectionDAG &DAG) |

| Emit Truncating Store with signed or unsigned saturation. More... | |

| static SDValue | EmitMaskedTruncSStore (bool SignedSat, SDValue Chain, const SDLoc &Dl, SDValue Val, SDValue Ptr, SDValue Mask, EVT MemVT, MachineMemOperand *MMO, SelectionDAG &DAG) |

| Emit Masked Truncating Store with signed or unsigned saturation. More... | |

| static SDValue | LowerINTRINSIC_W_CHAIN (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerADJUST_TRAMPOLINE (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerVectorIntUnary (SDValue Op, SelectionDAG &DAG) |

| static SDValue | Lower256IntUnary (SDValue Op, SelectionDAG &DAG) |

| static SDValue | Lower512IntUnary (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerVectorCTLZ_AVX512CDI (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Lower a vector CTLZ using native supported vector CTLZ instruction. More... | |

| static SDValue | LowerVectorCTLZInRegLUT (SDValue Op, const SDLoc &DL, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerVectorCTLZ (SDValue Op, const SDLoc &DL, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerCTLZ (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerCTTZ (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | split256IntArith (SDValue Op, SelectionDAG &DAG) |

| Break a 256-bit integer operation into two new 128-bit ones and then concatenate the result back. More... | |

| static SDValue | split512IntArith (SDValue Op, SelectionDAG &DAG) |

| Break a 512-bit integer operation into two new 256-bit ones and then concatenate the result back. More... | |

| static SDValue | lowerAddSub (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerADDSAT_SUBSAT (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerABS (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerMINMAX (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerMUL (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerMULH (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static bool | SupportedVectorShiftWithImm (MVT VT, const X86Subtarget &Subtarget, unsigned Opcode) |

| static bool | SupportedVectorShiftWithBaseAmnt (MVT VT, const X86Subtarget &Subtarget, unsigned Opcode) |

| static bool | SupportedVectorVarShift (MVT VT, const X86Subtarget &Subtarget, unsigned Opcode) |

| static SDValue | LowerScalarImmediateShift (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | IsSplatVector (SDValue V, int &SplatIdx, SelectionDAG &DAG) |

| static SDValue | GetSplatValue (SDValue V, const SDLoc &dl, SelectionDAG &DAG) |

| static SDValue | LowerScalarVariableShift (SDValue Op, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | convertShiftLeftToScale (SDValue Amt, const SDLoc &dl, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerShift (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerRotate (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerATOMIC_FENCE (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerCMP_SWAP (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | getPMOVMSKB (const SDLoc &DL, SDValue V, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | LowerBITCAST (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerHorizontalByteSum (SDValue V, MVT VT, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Compute the horizontal sum of bytes in V for the elements of VT. More... | |

| static SDValue | LowerVectorCTPOPInRegLUT (SDValue Op, const SDLoc &DL, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerVectorCTPOP (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerCTPOP (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerBITREVERSE_XOP (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerBITREVERSE (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | lowerAtomicArithWithLOCK (SDValue N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerAtomicArith (SDValue N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Lower atomic_load_ops into LOCK-prefixed operations. More... | |

| static SDValue | LowerATOMIC_STORE (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerADDSUBCARRY (SDValue Op, SelectionDAG &DAG) |

| static SDValue | LowerFSINCOS (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | ExtendToType (SDValue InOp, MVT NVT, SelectionDAG &DAG, bool FillWithZeroes=false) |

| Widen a vector input to a vector of NVT. More... | |

| static SDValue | LowerMSCATTER (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerMLOAD (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerMSTORE (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static SDValue | LowerMGATHER (SDValue Op, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| static MachineBasicBlock * | emitXBegin (MachineInstr &MI, MachineBasicBlock *MBB, const TargetInstrInfo *TII) |

| Utility function to emit xbegin specifying the start of an RTM region. More... | |

| static MachineBasicBlock * | emitWRPKRU (MachineInstr &MI, MachineBasicBlock *BB, const X86Subtarget &Subtarget) |

| static MachineBasicBlock * | emitRDPKRU (MachineInstr &MI, MachineBasicBlock *BB, const X86Subtarget &Subtarget) |

| static MachineBasicBlock * | emitMonitor (MachineInstr &MI, MachineBasicBlock *BB, const X86Subtarget &Subtarget, unsigned Opc) |

| static MachineBasicBlock * | emitClzero (MachineInstr *MI, MachineBasicBlock *BB, const X86Subtarget &Subtarget) |

| static bool | checkAndUpdateEFLAGSKill (MachineBasicBlock::iterator SelectItr, MachineBasicBlock *BB, const TargetRegisterInfo *TRI) |

| static bool | isCMOVPseudo (MachineInstr &MI) |

| static MachineInstrBuilder | createPHIsForCMOVsInSinkBB (MachineBasicBlock::iterator MIItBegin, MachineBasicBlock::iterator MIItEnd, MachineBasicBlock *TrueMBB, MachineBasicBlock *FalseMBB, MachineBasicBlock *SinkMBB) |

| static unsigned | getOpcodeForRetpoline (unsigned RPOpc) |

| static const char * | getRetpolineSymbol (const X86Subtarget &Subtarget, unsigned Reg) |

| static bool | matchUnaryVectorShuffle (MVT MaskVT, ArrayRef< int > Mask, bool AllowFloatDomain, bool AllowIntDomain, SDValue &V1, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, unsigned &Shuffle, MVT &SrcVT, MVT &DstVT) |

| static bool | matchUnaryPermuteVectorShuffle (MVT MaskVT, ArrayRef< int > Mask, const APInt &Zeroable, bool AllowFloatDomain, bool AllowIntDomain, const X86Subtarget &Subtarget, unsigned &Shuffle, MVT &ShuffleVT, unsigned &PermuteImm) |

| static bool | matchBinaryVectorShuffle (MVT MaskVT, ArrayRef< int > Mask, bool AllowFloatDomain, bool AllowIntDomain, SDValue &V1, SDValue &V2, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, unsigned &Shuffle, MVT &SrcVT, MVT &DstVT, bool IsUnary) |

| static bool | matchBinaryPermuteVectorShuffle (MVT MaskVT, ArrayRef< int > Mask, const APInt &Zeroable, bool AllowFloatDomain, bool AllowIntDomain, SDValue &V1, SDValue &V2, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget, unsigned &Shuffle, MVT &ShuffleVT, unsigned &PermuteImm) |

| static SDValue | combineX86ShuffleChain (ArrayRef< SDValue > Inputs, SDValue Root, ArrayRef< int > BaseMask, int Depth, bool HasVariableMask, bool AllowVariableMask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Combine an arbitrary chain of shuffles into a single instruction if possible. More... | |

| static SDValue | combineX86ShufflesConstants (ArrayRef< SDValue > Ops, ArrayRef< int > Mask, SDValue Root, bool HasVariableMask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineX86ShufflesRecursively (ArrayRef< SDValue > SrcOps, int SrcOpIndex, SDValue Root, ArrayRef< int > RootMask, ArrayRef< const SDNode *> SrcNodes, unsigned Depth, bool HasVariableMask, bool AllowVariableMask, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Fully generic combining of x86 shuffle instructions. More... | |

| static SmallVector< int, 4 > | getPSHUFShuffleMask (SDValue N) |

| Get the PSHUF-style mask from PSHUF node. More... | |

| static SDValue | combineRedundantDWordShuffle (SDValue N, MutableArrayRef< int > Mask, SelectionDAG &DAG) |

| Search for a combinable shuffle across a chain ending in pshufd. More... | |

| static SDValue | combineTargetShuffle (SDValue N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Try to combine x86 target specific shuffles. More... | |

| static bool | isAddSubOrSubAddMask (ArrayRef< int > Mask, bool &Op0Even) |

| Checks if the shuffle mask takes subsequent elements alternately from two vectors. More... | |

| static bool | isAddSubOrSubAdd (SDNode *N, const X86Subtarget &Subtarget, SelectionDAG &DAG, SDValue &Opnd0, SDValue &Opnd1, bool &IsSubAdd) |

Returns true iff the shuffle node N can be replaced with ADDSUB(SUBADD) operation. More... | |

| static SDValue | combineShuffleToFMAddSub (SDNode *N, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Combine shuffle of two fma nodes into FMAddSub or FMSubAdd. More... | |

| static SDValue | combineShuffleToAddSubOrFMAddSub (SDNode *N, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Try to combine a shuffle into a target-specific add-sub or mul-add-sub node. More... | |

| static SDValue | combineShuffleOfConcatUndef (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | foldShuffleOfHorizOp (SDNode *N) |

| Eliminate a redundant shuffle of a horizontal math op. More... | |

| static SDValue | combineShuffle (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | XFormVExtractWithShuffleIntoLoad (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI) |

| Check if a vector extract from a target-specific shuffle of a load can be folded into a single element load. More... | |

| static SDValue | combineBitcastvxi1 (SelectionDAG &DAG, SDValue BitCast, const X86Subtarget &Subtarget) |

| static SDValue | combinevXi1ConstantToInteger (SDValue Op, SelectionDAG &DAG) |

| static SDValue | combineCastedMaskArithmetic (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | createMMXBuildVector (SDValue N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineBitcast (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static bool | detectZextAbsDiff (const SDValue &Select, SDValue &Op0, SDValue &Op1) |

| static SDValue | createPSADBW (SelectionDAG &DAG, const SDValue &Zext0, const SDValue &Zext1, const SDLoc &DL, const X86Subtarget &Subtarget) |

| static SDValue | combineHorizontalMinMaxResult (SDNode *Extract, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineHorizontalPredicateResult (SDNode *Extract, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineBasicSADPattern (SDNode *Extract, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineExtractWithShuffle (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineExtractVectorElt (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Detect vector gather/scatter index generation and convert it from being a bunch of shuffles and extracts into a somewhat faster sequence. More... | |

| static SDValue | combineVSelectWithAllOnesOrZeros (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| If a vector select has an operand that is -1 or 0, try to simplify the select to a bitwise logic operation. More... | |

| static SDValue | combineSelectOfTwoConstants (SDNode *N, SelectionDAG &DAG) |

| static SDValue | combineVSelectToBLENDV (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| If this is a dynamic select (non-constant condition) and we can match this node with one of the variable blend instructions, restructure the condition so that blends can use the high (sign) bit of each element. More... | |

| static SDValue | combineSelect (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Do target-specific dag combines on SELECT and VSELECT nodes. More... | |

| static SDValue | combineSetCCAtomicArith (SDValue Cmp, X86::CondCode &CC, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Combine: (brcond/cmov/setcc .., (cmp (atomic_load_add x, 1), 0), COND_S) to: (brcond/cmov/setcc .., (LADD x, 1), COND_LE) i.e., reusing the EFLAGS produced by the LOCKed instruction. More... | |

| static SDValue | checkBoolTestSetCCCombine (SDValue Cmp, X86::CondCode &CC) |

| static bool | checkBoolTestAndOrSetCCCombine (SDValue Cond, X86::CondCode &CC0, X86::CondCode &CC1, SDValue &Flags, bool &isAnd) |

| Check whether Cond is an AND/OR of SETCCs off of the same EFLAGS. More... | |

| static SDValue | combineCarryThroughADD (SDValue EFLAGS) |

| static SDValue | combineSetCCEFLAGS (SDValue EFLAGS, X86::CondCode &CC, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

Optimize an EFLAGS definition used according to the condition code CC into a simpler EFLAGS value, potentially returning a new CC and replacing uses of chain values. More... | |

| static SDValue | combineCMov (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Optimize X86ISD::CMOV [LHS, RHS, CONDCODE (e.g. X86::COND_NE), CONDVAL]. More... | |

| static bool | canReduceVMulWidth (SDNode *N, SelectionDAG &DAG, ShrinkMode &Mode) |

| static SDValue | reduceVMULWidth (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| When the operands of vector mul are extended from smaller size values, like i8 and i16, the type of mul may be shrinked to generate more efficient code. More... | |

| static SDValue | combineMulSpecial (uint64_t MulAmt, SDNode *N, SelectionDAG &DAG, EVT VT, const SDLoc &DL) |

| static SDValue | combineMulToPMADDWD (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineMulToPMULDQ (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineMul (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Optimize a single multiply with constant into two operations in order to implement it with two cheaper instructions, e.g. More... | |

| static SDValue | combineShiftLeft (SDNode *N, SelectionDAG &DAG) |

| static SDValue | combineShiftRightArithmetic (SDNode *N, SelectionDAG &DAG) |

| static SDValue | combineShiftRightLogical (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI) |

| static SDValue | combineShift (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineVectorPack (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineVectorShiftVar (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineVectorShiftImm (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineVectorInsert (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineCompareEqual (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| Recognize the distinctive (AND (setcc ...) (setcc ..)) where both setccs reference the same FP CMP, and rewrite for CMPEQSS and friends. More... | |

| static SDValue | combineANDXORWithAllOnesIntoANDNP (SDNode *N, SelectionDAG &DAG) |

| Try to fold: (and (xor X, -1), Y) -> (andnp X, Y). More... | |

| static SDValue | PromoteMaskArithmetic (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | convertIntLogicToFPLogic (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| If both input operands of a logic op are being cast from floating point types, try to convert this into a floating point logic node to avoid unnecessary moves from SSE to integer registers. More... | |

| static SDValue | combineAndMaskToShift (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| If this is a zero/all-bits result that is bitwise-anded with a low bits mask. More... | |

| static SDValue | getIndexFromUnindexedLoad (LoadSDNode *Ld) |

| static bool | hasBZHI (const X86Subtarget &Subtarget, MVT VT) |

| static SDValue | combineAndLoadToBZHI (SDNode *Node, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineParity (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | combineAnd (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static bool | matchLogicBlend (SDNode *N, SDValue &X, SDValue &Y, SDValue &Mask) |

| static SDValue | combineLogicBlendIntoPBLENDV (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | lowerX86CmpEqZeroToCtlzSrl (SDValue Op, EVT ExtTy, SelectionDAG &DAG) |

| static SDValue | combineOrCmpEqZeroToCtlzSrl (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineOr (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | foldXorTruncShiftIntoCmp (SDNode *N, SelectionDAG &DAG) |

| Try to turn tests against the signbit in the form of: XOR(TRUNCATE(SRL(X, size(X)-1)), 1) into: SETGT(X, -1) More... | |

| static SDValue | foldVectorXorShiftIntoCmp (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Turn vector tests of the signbit in the form of: xor (sra X, elt_size(X)-1), -1 into: pcmpgt X, -1. More... | |

| static bool | isSATValidOnAVX512Subtarget (EVT SrcVT, EVT DstVT, const X86Subtarget &Subtarget) |

Check if truncation with saturation form type SrcVT to DstVT is valid for the given Subtarget. More... | |

| static SDValue | detectUSatPattern (SDValue In, EVT VT, SelectionDAG &DAG, const SDLoc &DL) |

| Detect patterns of truncation with unsigned saturation: More... | |

| static SDValue | detectSSatPattern (SDValue In, EVT VT, bool MatchPackUS=false) |

| Detect patterns of truncation with signed saturation: (truncate (smin ((smax (x, signed_min_of_dest_type)), signed_max_of_dest_type)) to dest_type) or: (truncate (smax ((smin (x, signed_max_of_dest_type)), signed_min_of_dest_type)) to dest_type). More... | |

| static SDValue | detectAVX512SSatPattern (SDValue In, EVT VT, const X86Subtarget &Subtarget, const TargetLowering &TLI) |

| Detect a pattern of truncation with signed saturation. More... | |

| static SDValue | detectAVX512USatPattern (SDValue In, EVT VT, SelectionDAG &DAG, const SDLoc &DL, const X86Subtarget &Subtarget, const TargetLowering &TLI) |

| Detect a pattern of truncation with saturation: (truncate (umin (x, unsigned_max_of_dest_type)) to dest_type). More... | |

| static SDValue | combineTruncateWithSat (SDValue In, EVT VT, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | detectAVGPattern (SDValue In, EVT VT, SelectionDAG &DAG, const X86Subtarget &Subtarget, const SDLoc &DL) |

| This function detects the AVG pattern between vectors of unsigned i8/i16, which is c = (a + b + 1) / 2, and replace this operation with the efficient X86ISD::AVG instruction. More... | |

| static SDValue | combineLoad (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static int | getOneTrueElt (SDValue V) |

| If V is a build vector of boolean constants and exactly one of those constants is true, return the operand index of that true element. More... | |

| static bool | getParamsForOneTrueMaskedElt (MaskedLoadStoreSDNode *MaskedOp, SelectionDAG &DAG, SDValue &Addr, SDValue &Index, unsigned &Alignment) |

| Given a masked memory load/store operation, return true if it has one mask bit set. More... | |

| static SDValue | reduceMaskedLoadToScalarLoad (MaskedLoadSDNode *ML, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI) |

| If exactly one element of the mask is set for a non-extending masked load, it is a scalar load and vector insert. More... | |

| static SDValue | combineMaskedLoadConstantMask (MaskedLoadSDNode *ML, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI) |

| static SDValue | combineMaskedLoad (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | reduceMaskedStoreToScalarStore (MaskedStoreSDNode *MS, SelectionDAG &DAG) |

| If exactly one element of the mask is set for a non-truncating masked store, it is a vector extract and scalar store. More... | |

| static SDValue | combineMaskedStore (SDNode *N, SelectionDAG &DAG, TargetLowering::DAGCombinerInfo &DCI, const X86Subtarget &Subtarget) |

| static SDValue | combineStore (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static bool | isHorizontalBinOp (SDValue &LHS, SDValue &RHS, bool IsCommutative) |

| Return 'true' if this vector operation is "horizontal" and return the operands for the horizontal operation in LHS and RHS. More... | |

| static SDValue | combineFaddFsub (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| Do target-specific dag combines on floating-point adds/subs. More... | |

| static SDValue | combineTruncatedArithmetic (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget, const SDLoc &DL) |

| Attempt to pre-truncate inputs to arithmetic ops if it will simplify the codegen. More... | |

| static SDValue | combineVectorTruncationWithPACKUS (SDNode *N, const SDLoc &DL, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Truncate using ISD::AND mask and X86ISD::PACKUS. More... | |

| static SDValue | combineVectorTruncationWithPACKSS (SDNode *N, const SDLoc &DL, const X86Subtarget &Subtarget, SelectionDAG &DAG) |

| Truncate a group of v4i32 into v8i16 using X86ISD::PACKSS. More... | |

| static SDValue | combineVectorTruncation (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| This function transforms truncation from vXi32/vXi64 to vXi8/vXi16 into X86ISD::PACKUS/X86ISD::PACKSS operations. More... | |

| static SDValue | combineVectorSignBitsTruncation (SDNode *N, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| This function transforms vector truncation of 'extended sign-bits' or 'extended zero-bits' values. More... | |

| static SDValue | combinePMULH (SDValue Src, EVT VT, const SDLoc &DL, SelectionDAG &DAG, const X86Subtarget &Subtarget) |

| static SDValue | detectPMADDUBSW (SDValue In, EVT VT, SelectionDAG &DAG, const X86Subtarget &Subtarget, const SDLoc &DL) |

| static SDValue | combineTruncate (SDNode *N, SelectionDAG &DAG, const X86Subtarget &Subtarget) |