#include "Target/X86/X86Subtarget.h"

Public Types | |

| enum | X86ProcFamilyEnum { Others, IntelAtom, IntelSLM, IntelGLM, IntelGLP, IntelTRM } |

Protected Types | |

| enum | X86SSEEnum { NoSSE, SSE1, SSE2, SSE3, SSSE3, SSE41, SSE42, AVX, AVX2, AVX512F } |

| enum | X863DNowEnum { NoThreeDNow, MMX, ThreeDNow, ThreeDNowA } |

Protected Attributes | |

| X86ProcFamilyEnum | X86ProcFamily = Others |

| X86 processor family: Intel Atom, and others. More... | |

| PICStyles::Style | PICStyle |

| Which PIC style to use. More... | |

| const TargetMachine & | TM |

| X86SSEEnum | X86SSELevel = NoSSE |

| SSE1, SSE2, SSE3, SSSE3, SSE41, SSE42, or none supported. More... | |

| X863DNowEnum | X863DNowLevel = NoThreeDNow |

| MMX, 3DNow, 3DNow Athlon, or none supported. More... | |

| bool | HasX87 = false |

| True if the processor supports X87 instructions. More... | |

| bool | HasNOPL = false |

| True if this processor has NOPL instruction (generally pentium pro+). More... | |

| bool | HasCMov = false |

| True if this processor has conditional move instructions (generally pentium pro+). More... | |

| bool | HasX86_64 = false |

| True if the processor supports X86-64 instructions. More... | |

| bool | HasPOPCNT = false |

| True if the processor supports POPCNT. More... | |

| bool | HasSSE4A = false |

| True if the processor supports SSE4A instructions. More... | |

| bool | HasAES = false |

| Target has AES instructions. More... | |

| bool | HasVAES = false |

| bool | HasFXSR = false |

| Target has FXSAVE/FXRESTOR instructions. More... | |

| bool | HasXSAVE = false |

| Target has XSAVE instructions. More... | |

| bool | HasXSAVEOPT = false |

| Target has XSAVEOPT instructions. More... | |

| bool | HasXSAVEC = false |

| Target has XSAVEC instructions. More... | |

| bool | HasXSAVES = false |

| Target has XSAVES instructions. More... | |

| bool | HasPCLMUL = false |

| Target has carry-less multiplication. More... | |

| bool | HasVPCLMULQDQ = false |

| bool | HasGFNI = false |

| Target has Galois Field Arithmetic instructions. More... | |

| bool | HasFMA = false |

| Target has 3-operand fused multiply-add. More... | |

| bool | HasFMA4 = false |

| Target has 4-operand fused multiply-add. More... | |

| bool | HasXOP = false |

| Target has XOP instructions. More... | |

| bool | HasTBM = false |

| Target has TBM instructions. More... | |

| bool | HasLWP = false |

| Target has LWP instructions. More... | |

| bool | HasMOVBE = false |

| True if the processor has the MOVBE instruction. More... | |

| bool | HasRDRAND = false |

| True if the processor has the RDRAND instruction. More... | |

| bool | HasF16C = false |

| Processor has 16-bit floating point conversion instructions. More... | |

| bool | HasFSGSBase = false |

| Processor has FS/GS base insturctions. More... | |

| bool | HasLZCNT = false |

| Processor has LZCNT instruction. More... | |

| bool | HasBMI = false |

| Processor has BMI1 instructions. More... | |

| bool | HasBMI2 = false |

| Processor has BMI2 instructions. More... | |

| bool | HasVBMI = false |

| Processor has VBMI instructions. More... | |

| bool | HasVBMI2 = false |

| Processor has VBMI2 instructions. More... | |

| bool | HasIFMA = false |

| Processor has Integer Fused Multiply Add. More... | |

| bool | HasRTM = false |

| Processor has RTM instructions. More... | |

| bool | HasADX = false |

| Processor has ADX instructions. More... | |

| bool | HasSHA = false |

| Processor has SHA instructions. More... | |

| bool | HasPRFCHW = false |

| Processor has PRFCHW instructions. More... | |

| bool | HasRDSEED = false |

| Processor has RDSEED instructions. More... | |

| bool | HasLAHFSAHF = false |

| Processor has LAHF/SAHF instructions. More... | |

| bool | HasMWAITX = false |

| Processor has MONITORX/MWAITX instructions. More... | |

| bool | HasCLZERO = false |

| Processor has Cache Line Zero instruction. More... | |

| bool | HasCLDEMOTE = false |

| Processor has Cache Line Demote instruction. More... | |

| bool | HasMOVDIRI = false |

| Processor has MOVDIRI instruction (direct store integer). More... | |

| bool | HasMOVDIR64B = false |

| Processor has MOVDIR64B instruction (direct store 64 bytes). More... | |

| bool | HasPTWRITE = false |

| Processor has ptwrite instruction. More... | |

| bool | HasPREFETCHWT1 = false |

| Processor has Prefetch with intent to Write instruction. More... | |

| bool | IsSHLDSlow = false |

| True if SHLD instructions are slow. More... | |

| bool | IsPMULLDSlow = false |

| True if the PMULLD instruction is slow compared to PMULLW/PMULHW and. More... | |

| bool | IsPMADDWDSlow = false |

| True if the PMADDWD instruction is slow compared to PMULLD. More... | |

| bool | IsUAMem16Slow = false |

| True if unaligned memory accesses of 16-bytes are slow. More... | |

| bool | IsUAMem32Slow = false |

| True if unaligned memory accesses of 32-bytes are slow. More... | |

| bool | HasSSEUnalignedMem = false |

| True if SSE operations can have unaligned memory operands. More... | |

| bool | HasCmpxchg16b = false |

| True if this processor has the CMPXCHG16B instruction; this is true for most x86-64 chips, but not the first AMD chips. More... | |

| bool | UseLeaForSP = false |

| True if the LEA instruction should be used for adjusting the stack pointer. More... | |

| bool | HasPOPCNTFalseDeps = false |

| True if POPCNT instruction has a false dependency on the destination register. More... | |

| bool | HasLZCNTFalseDeps = false |

| True if LZCNT/TZCNT instructions have a false dependency on the destination register. More... | |

| bool | HasFastVariableShuffle = false |

| True if its preferable to combine to a single shuffle using a variable mask over multiple fixed shuffles. More... | |

| bool | HasFastPartialYMMorZMMWrite = false |

| True if there is no performance penalty to writing only the lower parts of a YMM or ZMM register without clearing the upper part. More... | |

| bool | HasFast11ByteNOP = false |

| True if there is no performance penalty for writing NOPs with up to 11 bytes. More... | |

| bool | HasFast15ByteNOP = false |

| True if there is no performance penalty for writing NOPs with up to 15 bytes. More... | |

| bool | HasFastGather = false |

| True if gather is reasonably fast. More... | |

| bool | HasFastScalarFSQRT = false |

| True if hardware SQRTSS instruction is at least as fast (latency) as RSQRTSS followed by a Newton-Raphson iteration. More... | |

| bool | HasFastVectorFSQRT = false |

| True if hardware SQRTPS/VSQRTPS instructions are at least as fast (throughput) as RSQRTPS/VRSQRTPS followed by a Newton-Raphson iteration. More... | |

| bool | HasSlowDivide32 = false |

| True if 8-bit divisions are significantly faster than 32-bit divisions and should be used when possible. More... | |

| bool | HasSlowDivide64 = false |

| True if 32-bit divides are significantly faster than 64-bit divisions and should be used when possible. More... | |

| bool | HasFastLZCNT = false |

| True if LZCNT instruction is fast. More... | |

| bool | HasFastSHLDRotate = false |

| True if SHLD based rotate is fast. More... | |

| bool | HasMacroFusion = false |

| True if the processor supports macrofusion. More... | |

| bool | HasERMSB = false |

| True if the processor has enhanced REP MOVSB/STOSB. More... | |

| bool | PadShortFunctions = false |

| True if the short functions should be padded to prevent a stall when returning too early. More... | |

| bool | SlowTwoMemOps = false |

| True if two memory operand instructions should use a temporary register instead. More... | |

| bool | LEAUsesAG = false |

| True if the LEA instruction inputs have to be ready at address generation (AG) time. More... | |

| bool | SlowLEA = false |

| True if the LEA instruction with certain arguments is slow. More... | |

| bool | Slow3OpsLEA = false |

| True if the LEA instruction has all three source operands: base, index, and offset or if the LEA instruction uses base and index registers where the base is EBP, RBP,or R13. More... | |

| bool | SlowIncDec = false |

| True if INC and DEC instructions are slow when writing to flags. More... | |

| bool | HasPFI = false |

| Processor has AVX-512 PreFetch Instructions. More... | |

| bool | HasERI = false |

| Processor has AVX-512 Exponential and Reciprocal Instructions. More... | |

| bool | HasCDI = false |

| Processor has AVX-512 Conflict Detection Instructions. More... | |

| bool | HasVPOPCNTDQ = false |

| Processor has AVX-512 population count Instructions. More... | |

| bool | HasDQI = false |

| Processor has AVX-512 Doubleword and Quadword instructions. More... | |

| bool | HasBWI = false |

| Processor has AVX-512 Byte and Word instructions. More... | |

| bool | HasVLX = false |

| Processor has AVX-512 Vector Length eXtenstions. More... | |

| bool | HasPKU = false |

| Processor has PKU extenstions. More... | |

| bool | HasVNNI = false |

| Processor has AVX-512 Vector Neural Network Instructions. More... | |

| bool | HasBITALG = false |

| Processor has AVX-512 Bit Algorithms instructions. More... | |

| bool | HasMPX = false |

| Processor supports MPX - Memory Protection Extensions. More... | |

| bool | HasSHSTK = false |

| Processor supports CET SHSTK - Control-Flow Enforcement Technology using Shadow Stack. More... | |

| bool | HasINVPCID = false |

| Processor supports Invalidate Process-Context Identifier. More... | |

| bool | HasSGX = false |

| Processor has Software Guard Extensions. More... | |

| bool | HasCLFLUSHOPT = false |

| Processor supports Flush Cache Line instruction. More... | |

| bool | HasCLWB = false |

| Processor supports Cache Line Write Back instruction. More... | |

| bool | HasWBNOINVD = false |

| Processor supports Write Back No Invalidate instruction. More... | |

| bool | HasRDPID = false |

| Processor support RDPID instruction. More... | |

| bool | HasWAITPKG = false |

| Processor supports WaitPKG instructions. More... | |

| bool | HasPCONFIG = false |

| Processor supports PCONFIG instruction. More... | |

| bool | HasFastBEXTR = false |

| Processor has a single uop BEXTR implementation. More... | |

| bool | HasFastHorizontalOps = false |

| Try harder to combine to horizontal vector ops if they are fast. More... | |

| bool | UseRetpolineIndirectCalls = false |

| Use a retpoline thunk rather than indirect calls to block speculative execution. More... | |

| bool | UseRetpolineIndirectBranches = false |

| Use a retpoline thunk or remove any indirect branch to block speculative execution. More... | |

| bool | DeprecatedUseRetpoline = false |

Deprecated flag, query UseRetpolineIndirectCalls and UseRetpolineIndirectBranches instead. More... | |

| bool | UseRetpolineExternalThunk = false |

| When using a retpoline thunk, call an externally provided thunk rather than emitting one inside the compiler. More... | |

| bool | UseSoftFloat = false |

| Use software floating point for code generation. More... | |

| unsigned | stackAlignment = 4 |

| The minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function. More... | |

| unsigned | MaxInlineSizeThreshold = 128 |

| Max. More... | |

| bool | Prefer256Bit = false |

| Indicates target prefers 256 bit instructions. More... | |

| bool | ThreewayBranchProfitable = false |

| Threeway branch is profitable in this subtarget. More... | |

| Triple | TargetTriple |

| What processor and OS we're targeting. More... | |

| std::unique_ptr< CallLowering > | CallLoweringInfo |

| GlobalISel related APIs. More... | |

| std::unique_ptr< LegalizerInfo > | Legalizer |

| std::unique_ptr< RegisterBankInfo > | RegBankInfo |

| std::unique_ptr< InstructionSelector > | InstSelector |

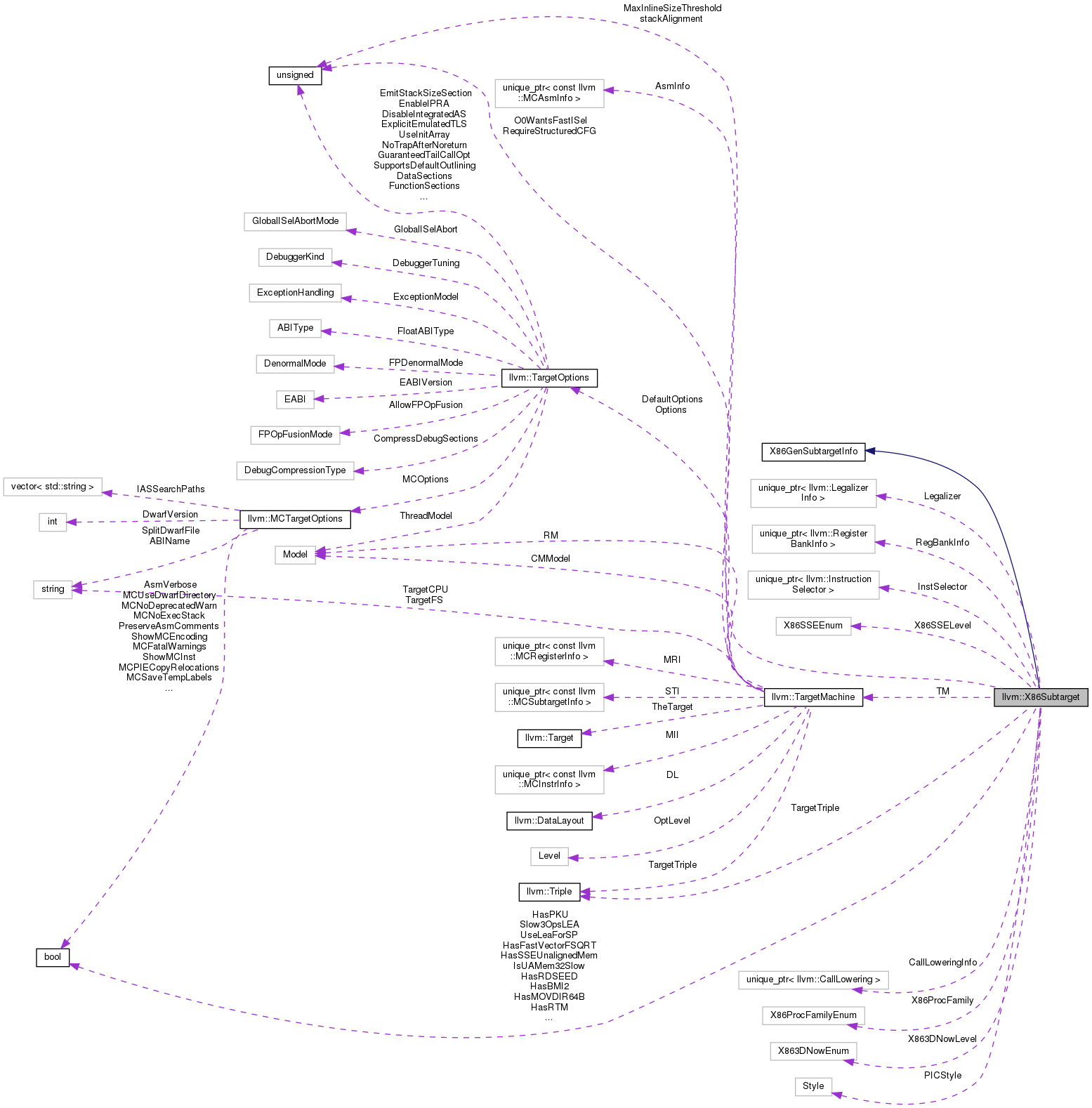

Detailed Description

Definition at line 53 of file X86Subtarget.h.

Member Enumeration Documentation

◆ X863DNowEnum

|

protected |

| Enumerator | |

|---|---|

| NoThreeDNow | |

| MMX | |

| ThreeDNow | |

| ThreeDNowA | |

Definition at line 71 of file X86Subtarget.h.

◆ X86ProcFamilyEnum

| Enumerator | |

|---|---|

| Others | |

| IntelAtom | |

| IntelSLM | |

| IntelGLM | |

| IntelGLP | |

| IntelTRM | |

Definition at line 57 of file X86Subtarget.h.

◆ X86SSEEnum

|

protected |

| Enumerator | |

|---|---|

| NoSSE | |

| SSE1 | |

| SSE2 | |

| SSE3 | |

| SSSE3 | |

| SSE41 | |

| SSE42 | |

| AVX | |

| AVX2 | |

| AVX512F | |

Definition at line 67 of file X86Subtarget.h.

Constructor & Destructor Documentation

◆ X86Subtarget()

| X86Subtarget::X86Subtarget | ( | const Triple & | TT, |

| StringRef | CPU, | ||

| StringRef | FS, | ||

| const X86TargetMachine & | TM, | ||

| unsigned | StackAlignOverride, | ||

| unsigned | PreferVectorWidthOverride, | ||

| unsigned | RequiredVectorWidth | ||

| ) |

This constructor initializes the data members to match that of the specified triple.

Definition at line 314 of file X86Subtarget.cpp.

References CallLoweringInfo, llvm::createX86InstructionSelector(), getRegisterInfo(), getTargetLowering(), llvm::PICStyles::GOT, InstSelector, is64Bit(), isPositionIndependent(), isTargetCOFF(), isTargetDarwin(), isTargetELF(), llvm::PICStyles::None, RegBankInfo, llvm::PICStyles::RIPRel, setPICStyle(), and llvm::PICStyles::StubPIC.

Member Function Documentation

◆ canExtendTo512BW()

|

inline |

Definition at line 688 of file X86Subtarget.h.

Referenced by lower1BitVectorShuffle(), LowerMUL(), LowerMULH(), LowerScalarVariableShift(), and LowerShift().

◆ canExtendTo512DQ()

|

inline |

Definition at line 685 of file X86Subtarget.h.

Referenced by lower1BitVectorShuffle(), LowerScalarVariableShift(), LowerShift(), LowerSIGN_EXTEND_Mask(), LowerTruncateVecI1(), LowerVectorCTLZ(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTPOP(), and LowerZERO_EXTEND_Mask().

◆ classifyBlockAddressReference()

Classify a blockaddress reference for the current subtarget according to how we should reference it in a non-pcrel context.

Definition at line 58 of file X86Subtarget.cpp.

References classifyLocalReference().

Referenced by getRetpolineSymbol(), and LowerEXTRACT_SUBVECTOR().

◆ classifyGlobalFunctionReference() [1/2]

| unsigned char X86Subtarget::classifyGlobalFunctionReference | ( | const GlobalValue * | GV, |

| const Module & | M | ||

| ) | const |

Classify a global function reference for the current subtarget.

Definition at line 174 of file X86Subtarget.cpp.

References assert(), F(), llvm::Function::getCallingConv(), llvm::Module::getRtLibUseGOT(), llvm::GlobalValue::hasDLLImportStorageClass(), llvm::Function::hasFnAttribute(), is64Bit(), isTargetCOFF(), isTargetELF(), llvm::X86II::MO_DLLIMPORT, llvm::X86II::MO_GOTPCREL, llvm::X86II::MO_NO_FLAG, llvm::X86II::MO_PLT, llvm::Attribute::NonLazyBind, llvm::TargetMachine::shouldAssumeDSOLocal(), TM, and llvm::CallingConv::X86_RegCall.

Referenced by classifyGlobalFunctionReference(), and getMOVL().

◆ classifyGlobalFunctionReference() [2/2]

| unsigned char X86Subtarget::classifyGlobalFunctionReference | ( | const GlobalValue * | GV | ) | const |

Definition at line 169 of file X86Subtarget.cpp.

References classifyGlobalFunctionReference(), and llvm::GlobalValue::getParent().

◆ classifyGlobalReference() [1/2]

| unsigned char X86Subtarget::classifyGlobalReference | ( | const GlobalValue * | GV, |

| const Module & | M | ||

| ) | const |

Definition at line 122 of file X86Subtarget.cpp.

References classifyLocalReference(), llvm::GlobalValue::getAbsoluteSymbolRange(), llvm::TargetMachine::getCodeModel(), llvm::GlobalValue::hasDLLImportStorageClass(), is64Bit(), isPositionIndependent(), isTargetCOFF(), isTargetDarwin(), isTargetELF(), llvm::CodeModel::Large, llvm::X86II::MO_ABS8, llvm::X86II::MO_COFFSTUB, llvm::X86II::MO_DARWIN_NONLAZY, llvm::X86II::MO_DARWIN_NONLAZY_PIC_BASE, llvm::X86II::MO_DLLIMPORT, llvm::X86II::MO_GOT, llvm::X86II::MO_GOTPCREL, llvm::X86II::MO_NO_FLAG, llvm::TargetMachine::shouldAssumeDSOLocal(), and TM.

Referenced by classifyGlobalReference(), llvm::X86TargetLowering::isLegalAddressingMode(), llvm::X86TargetLowering::LowerAsmOperandForConstraint(), and LowerEXTRACT_SUBVECTOR().

◆ classifyGlobalReference() [2/2]

| unsigned char X86Subtarget::classifyGlobalReference | ( | const GlobalValue * | GV | ) | const |

Classify a global variable reference for the current subtarget according to how we should reference it in a non-pcrel context.

Definition at line 65 of file X86Subtarget.cpp.

References classifyGlobalReference(), and llvm::GlobalValue::getParent().

◆ classifyLocalReference()

| unsigned char X86Subtarget::classifyLocalReference | ( | const GlobalValue * | GV | ) | const |

Classify a global variable reference for the current subtarget according to how we should reference it in a non-pcrel context.

Definition at line 70 of file X86Subtarget.cpp.

References llvm::TargetMachine::getCodeModel(), llvm::GlobalValue::hasCommonLinkage(), is64Bit(), llvm::GlobalValue::isDeclarationForLinker(), isPositionIndependent(), isTargetCOFF(), isTargetDarwin(), isTargetELF(), llvm::CodeModel::Kernel, llvm::CodeModel::Large, llvm_unreachable, llvm::CodeModel::Medium, llvm::X86II::MO_DARWIN_NONLAZY_PIC_BASE, llvm::X86II::MO_GOTOFF, llvm::X86II::MO_NO_FLAG, llvm::X86II::MO_PIC_BASE_OFFSET, llvm::CodeModel::Small, llvm::CodeModel::Tiny, and TM.

Referenced by classifyBlockAddressReference(), classifyGlobalReference(), and LowerEXTRACT_SUBVECTOR().

◆ enableAdvancedRASplitCost()

|

inlineoverride |

Definition at line 846 of file X86Subtarget.h.

◆ enableEarlyIfConversion()

|

override |

Definition at line 367 of file X86Subtarget.cpp.

References hasCMov(), and X86EarlyIfConv.

◆ enableIndirectBrExpand()

|

inlineoverride |

If we are using retpolines, we need to expand indirectbr to avoid it lowering to an actual indirect jump.

Definition at line 830 of file X86Subtarget.h.

◆ enableMachineScheduler()

|

inlineoverride |

Enable the MachineScheduler pass for all X86 subtargets.

Definition at line 835 of file X86Subtarget.h.

◆ getAntiDepBreakMode()

|

inlineoverride |

Definition at line 842 of file X86Subtarget.h.

◆ getCallLowering()

|

override |

Methods used by Global ISel.

Definition at line 351 of file X86Subtarget.cpp.

References CallLoweringInfo.

◆ getFrameLowering()

|

inlineoverride |

Definition at line 483 of file X86Subtarget.h.

Referenced by ExpandMOVImmSExti8(), getMOVL(), llvm::X86TargetLowering::getRegisterByName(), isSortedByValueNo(), and LowerADJUST_TRAMPOLINE().

◆ getGatherOverhead()

|

inline |

Definition at line 621 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getUserCost().

◆ getInstrInfo()

|

inlineoverride |

Definition at line 481 of file X86Subtarget.h.

Referenced by callHasRegMask(), createPHIsForCMOVsInSinkBB(), llvm::createX86FixupLEAs(), llvm::createX86IndirectBranchTrackingPass(), emitClzero(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), emitMonitor(), emitRDPKRU(), emitWRPKRU(), findUncondBrI(), getRetpolineSymbol(), llvm::X86InstrInfo::getSerializableDirectMachineOperandTargetFlags(), llvm::X86FrameLowering::inlineStackProbe(), llvm::X86TargetLowering::isIntDivCheap(), llvm::X86CallLowering::lowerCall(), MatchingStackOffset(), llvm::X86TargetLowering::needsFixedCatchObjects(), llvm::X86AsmPrinter::runOnMachineFunction(), and llvm::X86LegalizerInfo::X86LegalizerInfo().

◆ getInstructionSelector()

|

override |

Definition at line 355 of file X86Subtarget.cpp.

References InstSelector.

◆ getLegalizerInfo()

|

override |

Definition at line 359 of file X86Subtarget.cpp.

◆ getMaxInlineSizeThreshold()

|

inline |

Returns the maximum memset / memcpy size that still makes it profitable to inline the call.

Definition at line 502 of file X86Subtarget.h.

◆ getPICStyle()

|

inline |

Definition at line 546 of file X86Subtarget.h.

◆ getPreferVectorWidth()

|

inline |

Definition at line 678 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getRegisterBitWidth().

◆ getProcFamily()

|

inline |

Definition at line 704 of file X86Subtarget.h.

◆ getRegBankInfo()

|

override |

Definition at line 363 of file X86Subtarget.cpp.

References RegBankInfo.

◆ getRegisterInfo()

|

inlineoverride |

Definition at line 491 of file X86Subtarget.h.

Referenced by createPHIsForCMOVsInSinkBB(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), expandXorFP(), getLoadStoreRegOpcode(), getMOVL(), llvm::X86TargetLowering::getRegisterByName(), getRetpolineSymbol(), llvm::X86TargetLowering::getReturnAddressFrameIndex(), llvm::X86TargetLowering::isIntDivCheap(), LowerADJUST_TRAMPOLINE(), llvm::X86CallLowering::lowerCall(), LowerINTRINSIC_W_CHAIN(), lowerRegToMasks(), MatchingStackOffset(), llvm::X86TargetLowering::needsFixedCatchObjects(), Passv64i1ArgInRegs(), recoverFramePointer(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::X86AsmPrinter::runOnMachineFunction(), X86Subtarget(), and llvm::X86TargetLowering::X86TargetLowering().

◆ getRequiredVectorWidth()

|

inline |

Definition at line 679 of file X86Subtarget.h.

◆ getScatterOverhead()

|

inline |

Definition at line 622 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getUserCost().

◆ getSelectionDAGInfo()

|

inlineoverride |

Definition at line 487 of file X86Subtarget.h.

◆ getStackAlignment()

|

inline |

Returns the minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function for this subtarget.

Definition at line 498 of file X86Subtarget.h.

◆ getTargetLowering()

|

inlineoverride |

Definition at line 477 of file X86Subtarget.h.

Referenced by combineInsertSubvector(), combineOrCmpEqZeroToCtlzSrl(), combineSIntToFP(), llvm::X86FrameLowering::emitPrologue(), llvm::X86RegisterInfo::getCalleeSavedRegs(), llvm::X86RegisterInfo::getCallPreservedMask(), llvm::X86FrameLowering::inlineStackProbe(), llvm::X86TargetLowering::isDesirableToCombineBuildVectorToShuffleTruncate(), and X86Subtarget().

◆ getTargetTriple()

Definition at line 721 of file X86Subtarget.h.

Referenced by computeBytesPoppedByCalleeForSRet(), llvm::X86TargetLowering::getIRStackGuard(), getMOVL(), llvm::X86TargetLowering::getSafeStackPointerLocation(), llvm::X86TargetLowering::getSDagStackGuard(), llvm::X86TargetLowering::getSSPStackGuardCheck(), llvm::X86TargetLowering::insertSSPDeclarations(), isSortedByValueNo(), Passv64i1ArgInRegs(), and llvm::X86TargetLowering::useStackGuardXorFP().

◆ has3DNow()

|

inline |

Definition at line 566 of file X86Subtarget.h.

References llvm::X86II::ThreeDNow.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ has3DNowA()

|

inline |

Definition at line 567 of file X86Subtarget.h.

◆ hasADX()

|

inline |

Definition at line 598 of file X86Subtarget.h.

◆ hasAES()

|

inline |

Definition at line 569 of file X86Subtarget.h.

◆ hasAnyFMA()

|

inline |

Definition at line 583 of file X86Subtarget.h.

Referenced by combineFMA(), combineFneg(), combineShuffleToFMAddSub(), isFMAddSubOrFMSubAdd(), llvm::X86TargetLowering::isFMAFasterThanFMulAndFAdd(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasAVX()

|

inline |

Definition at line 560 of file X86Subtarget.h.

Referenced by callHasRegMask(), combineBasicSADPattern(), combineBitcastvxi1(), combineExtractSubvector(), combineFaddFsub(), combineFMinNumFMaxNum(), combineHorizontalPredicateResult(), combineLoopSADPattern(), combineSubToSubus(), combineToExtendVectorInReg(), combineX86ShuffleChain(), CopyToFromAsymmetricReg(), createVariablePermute(), emitClzero(), EmitTest(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getArithmeticReductionCost(), llvm::X86RegisterInfo::getCalleeSavedRegs(), llvm::X86RegisterInfo::getCallPreservedMask(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), getLoadStoreRegOpcode(), llvm::X86TTIImpl::getMaxInterleaveFactor(), llvm::X86TTIImpl::getMinMaxReductionCost(), llvm::X86TargetLowering::getOptimalMemOpType(), llvm::X86TTIImpl::getRegisterBitWidth(), llvm::X86TTIImpl::getShuffleCost(), llvm::X86TargetLowering::getSingleConstraintMatchWeight(), InsertBitToMaskVector(), llvm::X86TTIImpl::isLegalMaskedLoad(), isSortedByValueNo(), isTruncWithZeroHighBitsInput(), LowerANY_EXTEND(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerEXTEND_VECTOR_INREG(), LowerShift(), LowerToHorizontalOp(), LowerTruncateVecI1(), lowerV2F64VectorShuffle(), lowerV4F32VectorShuffle(), lowerVectorShuffleAsBroadcast(), LowerVSETCC(), LowerVSETCCWithSUBUS(), LowerZERO_EXTEND(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), llvm::X86TargetLowering::reduceSelectOfFPConstantLoads(), X86ChooseCmpOpcode(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasAVX2()

|

inline |

Definition at line 561 of file X86Subtarget.h.

Referenced by combineExtractSubvector(), combineHorizontalPredicateResult(), combineShuffleOfConcatUndef(), combineVectorSizedSetCCEquality(), combineVectorTruncation(), combineVSelectToBLENDV(), combineX86ShuffleChain(), convertShiftLeftToScale(), createVariablePermute(), llvm::X86TTIImpl::enableMemCmpExpansion(), foldVectorXorShiftIntoCmp(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getInterleavedMemoryOpCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TTIImpl::getMinMaxReductionCost(), llvm::X86TTIImpl::getShuffleCost(), InsertBitToMaskVector(), llvm::X86TargetLowering::isDesirableToCombineBuildVectorToShuffleTruncate(), llvm::X86TTIImpl::isLegalMaskedGather(), isLegalToCallImmediateAddr(), llvm::X86TargetLowering::isVectorClearMaskLegal(), llvm::X86TargetLowering::isVectorShiftByScalarCheap(), lower256BitVectorShuffle(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerMGATHER(), LowerRotate(), lowerShuffleAsRepeatedMaskAndLanePermute(), LowerToHorizontalOp(), lowerV16I16VectorShuffle(), lowerV2X128VectorShuffle(), lowerV32I8VectorShuffle(), lowerV4F64VectorShuffle(), lowerV4I64VectorShuffle(), lowerV8F32VectorShuffle(), lowerV8I32VectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsLanePermuteAndBlend(), lowerVectorShuffleAsTruncBroadcast(), lowerVectorShuffleWithPSHUFB(), lowerVectorShuffleWithUndefHalf(), lowerVSELECTtoVectorShuffle(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), SplitOpsAndApply(), and llvm::X86LegalizerInfo::X86LegalizerInfo().

◆ hasAVX512()

|

inline |

Definition at line 562 of file X86Subtarget.h.

Referenced by combineBitcast(), combineBitcastvxi1(), combineCastedMaskArithmetic(), combineCompareEqual(), combineExtSetcc(), combineGatherScatter(), combineMaskedLoad(), combineSelect(), combineSetCC(), combineStore(), combineToExtendBoolVectorInReg(), combineTruncateWithSat(), combineVectorPack(), combineVectorSignBitsTruncation(), combineVSelectWithAllOnesOrZeros(), combineX86ShuffleChain(), llvm::X86TargetLowering::convertSelectOfConstantsToMath(), convertShiftLeftToScale(), CopyToFromAsymmetricReg(), createVariablePermute(), EmitKORTEST(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86RegisterInfo::getCalleeSavedRegs(), llvm::X86RegisterInfo::getCallPreservedMask(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getGatherScatterOpCost(), llvm::X86TTIImpl::getInterleavedMemoryOpCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86RegisterInfo::getLargestLegalSuperClass(), getLoadStoreRegOpcode(), llvm::X86TTIImpl::getMaskedMemoryOpCost(), llvm::X86TTIImpl::getMinMaxReductionCost(), llvm::X86TTIImpl::getNumberOfRegisters(), llvm::X86TargetLowering::getNumRegistersForCallingConv(), llvm::X86TargetLowering::getPreferredVectorAction(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TTIImpl::getRegisterBitWidth(), llvm::X86TargetLowering::getRegisterTypeForCallingConv(), llvm::X86RegisterInfo::getReservedRegs(), llvm::X86TargetLowering::getSetCCResultType(), llvm::X86TTIImpl::getShuffleCost(), llvm::X86TargetLowering::getSingleConstraintMatchWeight(), llvm::X86TTIImpl::getUserCost(), llvm::X86TTIImpl::isLegalMaskedGather(), llvm::X86TTIImpl::isLegalMaskedScatter(), isLegalToCallImmediateAddr(), llvm::X86TargetLowering::isLoadBitCastBeneficial(), isSATValidOnAVX512Subtarget(), isSortedByValueNo(), isTruncWithZeroHighBitsInput(), lower1BitVectorShuffle(), lower512BitVectorShuffle(), LowerBITCAST(), LowerBUILD_VECTORAsVariablePermute(), LowerEXTEND_VECTOR_INREG(), LowerLoad(), LowerMGATHER(), LowerMLOAD(), LowerMSCATTER(), LowerMSTORE(), LowerMULH(), LowerRotate(), LowerShift(), LowerStore(), LowerTruncateVecI1(), lowerUINT_TO_FP_v2i32(), lowerUINT_TO_FP_vec(), lowerV8F32VectorShuffle(), lowerV8I32VectorShuffle(), LowerVSETCC(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), llvm::X86TargetLowering::ReplaceNodeResults(), SupportedVectorShiftWithImm(), SupportedVectorVarShift(), X86ChooseCmpOpcode(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasBITALG()

|

inline |

Definition at line 660 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasBMI()

|

inline |

Definition at line 592 of file X86Subtarget.h.

Referenced by foldMaskedShiftToBEXTR(), llvm::X86TargetLowering::hasAndNotCompare(), llvm::X86TargetLowering::isCheapToSpeculateCttz(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasBMI2()

|

inline |

Definition at line 593 of file X86Subtarget.h.

Referenced by hasBZHI().

◆ hasBWI()

|

inline |

Definition at line 656 of file X86Subtarget.h.

Referenced by llvm::X86FrameLowering::assignCalleeSavedSpillSlots(), combineBitcastvxi1(), combineSelect(), combineSetCC(), combineX86ShuffleChain(), CopyToFromAsymmetricReg(), createVariablePermute(), EmitKORTEST(), ExtractBitFromMaskVector(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getInterleavedMemoryOpCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), getLoadStoreRegOpcode(), getMaskNode(), llvm::X86TargetLowering::getNumRegistersForCallingConv(), llvm::X86TargetLowering::getPreferredVectorAction(), llvm::X86TargetLowering::getRegisterTypeForCallingConv(), llvm::X86TargetLowering::getSetCCResultType(), llvm::X86TTIImpl::getShuffleCost(), getv64i1Argument(), getZeroVector(), llvm::X86TTIImpl::isLegalMaskedLoad(), isSATValidOnAVX512Subtarget(), isTruncWithZeroHighBitsInput(), llvm::X86TargetLowering::isVectorShiftByScalarCheap(), lower1BitVectorShuffle(), LowerBITCAST(), LowerLoad(), LowerMLOAD(), LowerMSTORE(), LowerMULH(), LowerShift(), LowerSIGN_EXTEND_Mask(), LowerTruncateVecI1(), lowerV16I16VectorShuffle(), lowerV16I32VectorShuffle(), lowerV32I16VectorShuffle(), lowerV64I8VectorShuffle(), LowerVectorCTLZ(), LowerVectorCTPOP(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleWithPSHUFB(), lowerVectorShuffleWithVPMOV(), LowerVSETCC(), LowerZERO_EXTEND_Mask(), matchBinaryVectorShuffle(), matchVectorShuffleAsShift(), Passv64i1ArgInRegs(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), SupportedVectorShiftWithImm(), SupportedVectorVarShift(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasCDI()

|

inline |

Definition at line 651 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getIntrinsicInstrCost(), lowerBuildVectorAsBroadcast(), LowerVectorCTLZ(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasCLDEMOTE()

|

inline |

Definition at line 612 of file X86Subtarget.h.

◆ hasCLFLUSHOPT()

|

inline |

Definition at line 663 of file X86Subtarget.h.

◆ hasCLWB()

|

inline |

Definition at line 664 of file X86Subtarget.h.

◆ hasCLZERO()

|

inline |

Definition at line 611 of file X86Subtarget.h.

◆ hasCMov()

|

inline |

Definition at line 553 of file X86Subtarget.h.

References is64Bit().

Referenced by EmitTest(), enableEarlyIfConversion(), isTruncWithZeroHighBitsInput(), llvm::X86TargetLowering::shouldUseStrictFP_TO_INT(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasCmpxchg16b()

|

inline |

Definition at line 624 of file X86Subtarget.h.

Referenced by LowerRotate(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasDQI()

|

inline |

Definition at line 655 of file X86Subtarget.h.

Referenced by combineSIntToFP(), EmitKORTEST(), ExtractBitFromMaskVector(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getCastInstrCost(), insert1BitVector(), llvm::X86TargetLowering::isLoadBitCastBeneficial(), lower1BitVectorShuffle(), LowerEXTRACT_SUBVECTOR(), LowerI64IntToFP_AVX512DQ(), LowerLoad(), LowerMUL(), LowerSIGN_EXTEND_Mask(), LowerStore(), LowerTruncateVecI1(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasERI()

|

inline |

Definition at line 654 of file X86Subtarget.h.

◆ hasERMSB()

|

inline |

Definition at line 642 of file X86Subtarget.h.

◆ hasF16C()

|

inline |

Definition at line 589 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasFastBEXTR()

|

inline |

Definition at line 639 of file X86Subtarget.h.

Referenced by foldMaskedShiftToBEXTR().

◆ hasFastGather()

|

inline |

Definition at line 634 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::isLegalMaskedGather(), and isLegalToCallImmediateAddr().

◆ hasFastHorizontalOps()

|

inline |

Definition at line 640 of file X86Subtarget.h.

Referenced by shouldUseHorizontalOp().

◆ hasFastLZCNT()

|

inline |

Definition at line 637 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::isCtlzFast().

◆ hasFastPartialYMMorZMMWrite()

|

inline |

Definition at line 631 of file X86Subtarget.h.

Referenced by callHasRegMask().

◆ hasFastScalarFSQRT()

|

inline |

Definition at line 635 of file X86Subtarget.h.

Referenced by EmitTest().

◆ hasFastSHLDRotate()

|

inline |

Definition at line 638 of file X86Subtarget.h.

◆ hasFastVariableShuffle()

|

inline |

Definition at line 628 of file X86Subtarget.h.

Referenced by combineX86ShuffleChain().

◆ hasFastVectorFSQRT()

|

inline |

Definition at line 636 of file X86Subtarget.h.

Referenced by EmitTest().

◆ hasFMA()

|

inline |

Definition at line 581 of file X86Subtarget.h.

◆ hasFMA4()

|

inline |

Definition at line 582 of file X86Subtarget.h.

◆ hasFSGSBase()

|

inline |

Definition at line 590 of file X86Subtarget.h.

◆ hasFXSR()

|

inline |

Definition at line 571 of file X86Subtarget.h.

◆ hasGFNI()

|

inline |

Definition at line 578 of file X86Subtarget.h.

◆ hasIFMA()

|

inline |

Definition at line 596 of file X86Subtarget.h.

◆ hasInt256()

|

inline |

Definition at line 563 of file X86Subtarget.h.

Referenced by combineLoad(), combineLogicBlendIntoPBLENDV(), combineSignExtendInReg(), convertShiftLeftToScale(), EltsFromConsecutiveLoads(), getPMOVMSKB(), LowerABS(), LowerAVXExtend(), LowerBITREVERSE(), lowerBuildVectorAsBroadcast(), LowerCTTZ(), LowerEXTEND_VECTOR_INREG(), LowerLoad(), LowerMUL(), LowerMULH(), LowerScalarImmediateShift(), LowerShift(), LowerSIGN_EXTEND(), LowerTruncateVecI1(), LowerVectorCTLZ(), LowerVectorCTPOP(), LowerVSETCC(), matchBinaryVectorShuffle(), matchUnaryVectorShuffle(), materializeVectorConstant(), SupportedVectorShiftWithImm(), SupportedVectorVarShift(), truncateVectorWithPACK(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasINVPCID()

|

inline |

Definition at line 671 of file X86Subtarget.h.

◆ hasLAHFSAHF()

|

inline |

Definition at line 609 of file X86Subtarget.h.

Referenced by EmitTest().

◆ hasLWP()

|

inline |

Definition at line 586 of file X86Subtarget.h.

◆ hasLZCNT()

|

inline |

Definition at line 591 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::isCheapToSpeculateCtlz(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasLZCNTFalseDeps()

|

inline |

Definition at line 627 of file X86Subtarget.h.

Referenced by hasPartialRegUpdate().

◆ hasMacroFusion()

|

inline |

Definition at line 641 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::canMacroFuseCmp(), and shouldScheduleAdjacent().

◆ hasMFence()

|

inline |

Use mfence if we have SSE2 or we're on x86-64 (even if we asked for no-sse2).

There isn't any reason to disable it if the target processor supports it.

Definition at line 719 of file X86Subtarget.h.

References is64Bit().

Referenced by LowerATOMIC_FENCE(), and LowerRotate().

◆ hasMMX()

|

inline |

Definition at line 565 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TargetLowering::getSingleConstraintMatchWeight(), LowerBITCAST(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasMOVBE()

|

inline |

Definition at line 587 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasMOVDIR64B()

|

inline |

Definition at line 614 of file X86Subtarget.h.

◆ hasMOVDIRI()

|

inline |

Definition at line 613 of file X86Subtarget.h.

◆ hasMPX()

|

inline |

Definition at line 661 of file X86Subtarget.h.

◆ hasMWAITX()

|

inline |

Definition at line 610 of file X86Subtarget.h.

◆ hasNOPL()

|

inline |

Definition at line 550 of file X86Subtarget.h.

◆ hasPCLMUL()

|

inline |

Definition at line 576 of file X86Subtarget.h.

◆ hasPCONFIG()

|

inline |

Definition at line 668 of file X86Subtarget.h.

◆ hasPFI()

|

inline |

Definition at line 653 of file X86Subtarget.h.

◆ hasPKU()

|

inline |

Definition at line 658 of file X86Subtarget.h.

◆ hasPOPCNT()

|

inline |

Definition at line 568 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getPopcntSupport(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasPOPCNTFalseDeps()

|

inline |

Definition at line 626 of file X86Subtarget.h.

Referenced by hasPartialRegUpdate().

◆ hasPREFETCHWT1()

|

inline |

Definition at line 601 of file X86Subtarget.h.

◆ hasPRFCHW()

|

inline |

Definition at line 600 of file X86Subtarget.h.

◆ hasPTWRITE()

|

inline |

Definition at line 615 of file X86Subtarget.h.

◆ hasRDPID()

|

inline |

Definition at line 666 of file X86Subtarget.h.

◆ hasRDRAND()

|

inline |

Definition at line 588 of file X86Subtarget.h.

◆ hasRDSEED()

|

inline |

Definition at line 608 of file X86Subtarget.h.

◆ hasRTM()

|

inline |

Definition at line 597 of file X86Subtarget.h.

◆ hasSGX()

|

inline |

Definition at line 669 of file X86Subtarget.h.

◆ hasSHA()

|

inline |

Definition at line 599 of file X86Subtarget.h.

◆ hasSHSTK()

|

inline |

Definition at line 662 of file X86Subtarget.h.

◆ hasSlowDivide32()

|

inline |

Definition at line 643 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasSlowDivide64()

|

inline |

Definition at line 644 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSE1()

|

inline |

Definition at line 554 of file X86Subtarget.h.

Referenced by combineAnd(), combineBitcast(), combineFAndFNotToFAndn(), combineFMinNumFMaxNum(), combineOr(), combineSelect(), combineSetCC(), combineXor(), convertIntLogicToFPLogic(), createMMXBuildVector(), EmitTest(), get64BitArgumentXMMs(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TargetLowering::getByValTypeAlignment(), llvm::X86RegisterInfo::getCalleeSavedRegs(), llvm::X86RegisterInfo::getCallPreservedMask(), llvm::X86TTIImpl::getIntrinsicInstrCost(), getMOVL(), llvm::X86TTIImpl::getNumberOfRegisters(), llvm::X86TargetLowering::getOptimalMemOpType(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TTIImpl::getRegisterBitWidth(), llvm::X86TTIImpl::getShuffleCost(), llvm::X86TargetLowering::getSingleConstraintMatchWeight(), llvm::X86TargetLowering::hasAndNot(), isSortedByValueNo(), isTruncWithZeroHighBitsInput(), lowerRegToMasks(), llvm::X86TargetLowering::LowerXConstraint(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), Passv64i1ArgInRegs(), X86ChooseCmpOpcode(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSE2()

|

inline |

Definition at line 555 of file X86Subtarget.h.

Referenced by combineAddToSUBUS(), combineAnd(), combineBasicSADPattern(), combineBitcast(), combineBitcastvxi1(), combineCompareEqual(), combineExtractWithShuffle(), combineFAndFNotToFAndn(), combineFMinNumFMaxNum(), combineHorizontalPredicateResult(), combineLogicBlendIntoPBLENDV(), combineLoopMAddPattern(), combineLoopSADPattern(), combineMulToPMADDWD(), combineMulToPMULDQ(), combineOr(), combinePMULH(), combineSelect(), combineSetCC(), combineStore(), combineSubToSubus(), combineToExtendBoolVectorInReg(), combineToExtendVectorInReg(), combineVectorSignBitsTruncation(), combineVectorSizedSetCCEquality(), combineVectorTruncation(), combineX86ShuffleChain(), combineXor(), llvm::X86InstrInfo::commuteInstructionImpl(), convertIntLogicToFPLogic(), detectAVGPattern(), EmitTest(), llvm::X86TTIImpl::enableMemCmpExpansion(), llvm::X86InstrInfo::findCommutedOpIndices(), foldVectorXorShiftIntoCmp(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TargetLowering::getOptimalMemOpType(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TTIImpl::getShuffleCost(), llvm::X86TargetLowering::getSingleConstraintMatchWeight(), getZeroVector(), llvm::X86TargetLowering::hasAndNot(), InsertBitToMaskVector(), isSortedByValueNo(), isTruncWithZeroHighBitsInput(), LowerBITCAST(), LowerBuildVectorAsInsert(), LowerEXTEND_VECTOR_INREG(), LowerLoad(), LowerMUL(), LowerMULH(), LowerShift(), lowerV4F32VectorShuffle(), LowerVSETCC(), LowerVSETCCWithSUBUS(), lowerX86FPLogicOp(), llvm::X86TargetLowering::LowerXConstraint(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchPMADDWD(), matchPMADDWD_2(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), materializeVectorConstant(), Passv64i1ArgInRegs(), reduceVMULWidth(), llvm::X86TargetLowering::ReplaceNodeResults(), SplitOpsAndApply(), SupportedVectorShiftWithImm(), truncateVectorWithPACK(), X86ChooseCmpOpcode(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSE3()

|

inline |

Definition at line 556 of file X86Subtarget.h.

Referenced by combineFaddFsub(), isAddSubOrSubAdd(), lowerAddSubToHorizontalOp(), LowerBuildVectorv4x32(), LowerToHorizontalOp(), LowerUINT_TO_FP_i64(), lowerV4F32VectorShuffle(), lowerVectorShuffleAsBroadcast(), matchUnaryVectorShuffle(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSE41()

|

inline |

Definition at line 558 of file X86Subtarget.h.

Referenced by combineExtractWithShuffle(), combineHorizontalMinMaxResult(), combineLogicBlendIntoPBLENDV(), combineMulToPMADDWD(), combineMulToPMULDQ(), combineShuffle(), combineToExtendVectorInReg(), combineTruncateWithSat(), combineVectorSignBitsTruncation(), combineVectorTruncation(), combineVSelectToBLENDV(), llvm::X86InstrInfo::commuteInstructionImpl(), convertShiftLeftToScale(), createVariablePermute(), ExtractBitFromMaskVector(), llvm::X86InstrInfo::findCommutedOpIndices(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getCastInstrCost(), llvm::X86TTIImpl::getShuffleCost(), getTargetVShiftNode(), InsertBitToMaskVector(), LowerABS(), LowerBUILD_VECTORAsVariablePermute(), LowerBuildVectorAsInsert(), LowerBuildVectorv16i8(), LowerBuildVectorv4x32(), LowerBuildVectorv8i16(), LowerMUL(), LowerMULH(), LowerRotate(), LowerShift(), LowerTruncateVecI1(), lowerUINT_TO_FP_vXi32(), lowerV16I8VectorShuffle(), lowerV2F64VectorShuffle(), lowerV2I64VectorShuffle(), lowerV4F32VectorShuffle(), lowerV4I32VectorShuffle(), lowerV8I16VectorShuffle(), LowerVectorAllZeroTest(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVSELECTtoVectorShuffle(), LowerVSETCC(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryVectorShuffle(), matchVectorShuffleWithPACK(), matchVectorShuffleWithUNPCK(), reduceVMULWidth(), llvm::X86TargetLowering::ReplaceNodeResults(), truncateVectorWithPACK(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSE42()

|

inline |

Definition at line 559 of file X86Subtarget.h.

Referenced by foldVectorXorShiftIntoCmp(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getArithmeticReductionCost(), llvm::X86TTIImpl::getCmpSelInstrCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TTIImpl::getMinMaxReductionCost(), isLegalToCallImmediateAddr(), LowerScalarImmediateShift(), and LowerVSETCC().

◆ hasSSE4A()

|

inline |

Definition at line 564 of file X86Subtarget.h.

Referenced by combineX86ShuffleChain(), isLegalToCallImmediateAddr(), lowerV16I8VectorShuffle(), lowerV8I16VectorShuffle(), and lowerVectorShuffleAsSpecificZeroOrAnyExtend().

◆ hasSSEPrefetch()

|

inline |

Definition at line 602 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::X86TargetLowering().

◆ hasSSEUnalignedMem()

|

inline |

Definition at line 623 of file X86Subtarget.h.

◆ hasSSSE3()

|

inline |

Definition at line 557 of file X86Subtarget.h.

Referenced by combineAdd(), combineSub(), combineSubToSubus(), combineVectorTruncation(), combineX86ShuffleChain(), createVariablePermute(), detectPMADDUBSW(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TTIImpl::getShuffleCost(), lowerAddSubToHorizontalOp(), LowerBITREVERSE(), LowerToHorizontalOp(), lowerV16I8VectorShuffle(), lowerV2I64VectorShuffle(), lowerV4I32VectorShuffle(), lowerV8I16VectorShuffle(), LowerVectorCTLZ(), LowerVectorCTPOP(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleWithPSHUFB(), matchBinaryPermuteVectorShuffle(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasTBM()

|

inline |

Definition at line 585 of file X86Subtarget.h.

Referenced by foldMaskedShiftToBEXTR().

◆ hasVAES()

|

inline |

Definition at line 570 of file X86Subtarget.h.

◆ hasVBMI()

|

inline |

Definition at line 594 of file X86Subtarget.h.

Referenced by combineX86ShuffleChain(), createVariablePermute(), llvm::X86TTIImpl::getShuffleCost(), lowerV16I8VectorShuffle(), lowerV32I8VectorShuffle(), and lowerV64I8VectorShuffle().

◆ hasVBMI2()

|

inline |

Definition at line 595 of file X86Subtarget.h.

Referenced by LowerFunnelShift(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasVLX()

|

inline |

Definition at line 657 of file X86Subtarget.h.

Referenced by combineHorizontalPredicateResult(), combineVectorPack(), combineX86ShuffleChain(), createVariablePermute(), llvm::X86TTIImpl::getGatherScatterOpCost(), llvm::X86RegisterInfo::getLargestLegalSuperClass(), getLoadStoreRegOpcode(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TargetLowering::getSetCCResultType(), isLegalMaskCompare(), isSATValidOnAVX512Subtarget(), isSortedByValueNo(), lower1BitVectorShuffle(), lowerBuildVectorAsBroadcast(), LowerI64IntToFP_AVX512DQ(), LowerMGATHER(), LowerMLOAD(), LowerMSCATTER(), LowerMSTORE(), LowerShift(), LowerSIGN_EXTEND_Mask(), LowerTruncateVecI1(), lowerV16I16VectorShuffle(), lowerV16I8VectorShuffle(), lowerV2I64VectorShuffle(), lowerV2X128VectorShuffle(), lowerV32I8VectorShuffle(), lowerV4F64VectorShuffle(), lowerV4I32VectorShuffle(), lowerV4I64VectorShuffle(), lowerV8F32VectorShuffle(), lowerV8I32VectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsRotate(), lowerVectorShuffleWithVPMOV(), LowerZERO_EXTEND_Mask(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::X86LegalizerInfo::X86LegalizerInfo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasVNNI()

|

inline |

Definition at line 659 of file X86Subtarget.h.

◆ hasVPCLMULQDQ()

|

inline |

Definition at line 577 of file X86Subtarget.h.

◆ hasVPOPCNTDQ()

|

inline |

Definition at line 652 of file X86Subtarget.h.

Referenced by LowerVectorCTPOP(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasWAITPKG()

|

inline |

Definition at line 667 of file X86Subtarget.h.

◆ hasWBNOINVD()

|

inline |

Definition at line 665 of file X86Subtarget.h.

◆ hasX87()

|

inline |

Definition at line 549 of file X86Subtarget.h.

Referenced by combineSIntToFP(), llvm::X86TargetLowering::getOptimalMemOpType(), lowerRegToMasks(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasXOP()

|

inline |

Definition at line 584 of file X86Subtarget.h.

Referenced by combineX86ShuffleChain(), createVariablePermute(), llvm::X86TTIImpl::getArithmeticInstrCost(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TTIImpl::getShuffleCost(), llvm::X86TargetLowering::isVectorShiftByScalarCheap(), LowerBITREVERSE(), LowerBuildVectorv4x32(), LowerRotate(), LowerScalarImmediateShift(), LowerScalarVariableShift(), LowerShift(), LowerVSETCC(), and llvm::X86TargetLowering::X86TargetLowering().

◆ hasXSAVE()

|

inline |

Definition at line 572 of file X86Subtarget.h.

◆ hasXSAVEC()

|

inline |

Definition at line 574 of file X86Subtarget.h.

◆ hasXSAVEOPT()

|

inline |

Definition at line 573 of file X86Subtarget.h.

◆ hasXSAVES()

|

inline |

Definition at line 575 of file X86Subtarget.h.

◆ is16Bit()

|

inline |

Definition at line 530 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::getRegForInlineAsmConstraint().

◆ is32Bit()

|

inline |

Definition at line 526 of file X86Subtarget.h.

Referenced by createPHIsForCMOVsInSinkBB(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), getMaskNode(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), getv64i1Argument(), lowerBuildVectorAsBroadcast(), Passv64i1ArgInRegs(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), llvm::X86FrameLowering::restoreWin32EHStackPointers(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), and llvm::X86TargetLowering::X86TargetLowering().

◆ is64Bit()

|

inline |

Is this x86_64? (disregarding specific ABI / programming model)

Definition at line 522 of file X86Subtarget.h.

Referenced by llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::X86TargetLowering::canMergeStoresTo(), classifyGlobalFunctionReference(), classifyGlobalReference(), llvm::X86InstrInfo::classifyLEAReg(), classifyLocalReference(), combineAnd(), combineCompareEqual(), combineSIntToFP(), combineStore(), computeBytesPoppedByCalleeForSRet(), llvm::X86InstrInfo::convertToThreeAddress(), createPHIsForCMOVsInSinkBB(), llvm::createX86IndirectBranchTrackingPass(), emitClzero(), emitMonitor(), EmitNops(), llvm::X86TargetLowering::emitStackGuardXorFP(), llvm::X86TTIImpl::enableMemCmpExpansion(), ExpandMOVImmSExti8(), llvm::X86TargetLowering::findRepresentativeClass(), get64BitArgumentGPRs(), get64BitArgumentXMMs(), llvm::X86TargetLowering::getByValTypeAlignment(), getExtendedControlRegister(), llvm::X86TTIImpl::getIntrinsicInstrCost(), llvm::X86TargetLowering::getIRStackGuard(), getLoadStoreRegOpcode(), getMOVL(), llvm::X86TTIImpl::getNumberOfRegisters(), llvm::X86TargetLowering::getOptimalMemOpType(), llvm::X86TargetLowering::getPICJumpTableRelocBase(), getReadPerformanceCounter(), getReadTimeStampCounter(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::X86TTIImpl::getRegisterBitWidth(), getRetOpcode(), getRetpolineSymbol(), llvm::X86TargetLowering::getSafeStackPointerLocation(), llvm::X86InstrInfo::getSerializableDirectMachineOperandTargetFlags(), llvm::X86TargetLowering::getStackProbeSymbolName(), hasBZHI(), llvm::X86FrameLowering::inlineStackProbe(), llvm::X86InstrInfo::isCoalescableExtInstr(), llvm::X86TargetLowering::isIntDivCheap(), llvm::X86TargetLowering::isLegalAddressingMode(), isSortedByValueNo(), isTruncWithZeroHighBitsInput(), llvm::X86TargetLowering::isZExtFree(), LowerADJUST_TRAMPOLINE(), llvm::X86TargetLowering::LowerAsmOperandForConstraint(), LowerBITCAST(), LowerBUILD_VECTORAsVariablePermute(), LowerBUILD_VECTORvXi1(), llvm::X86CallLowering::lowerCall(), LowerCMP_SWAP(), LowerFSINCOS(), LowerI64IntToFP_AVX512DQ(), lowerRegToMasks(), LowerRotate(), LowerStore(), LowerToTLSExecModel(), lowerUINT_TO_FP_vec(), LowerVACOPY(), llvm::X86TargetLowering::markLibCallAttributes(), MatchingStackOffset(), llvm::X86TargetLowering::needsFixedCatchObjects(), Passv64i1ArgInRegs(), llvm::X86TargetLowering::preferShiftsToClearExtremeBits(), printAsmMRegister(), llvm::X86FrameLowering::processFunctionBeforeFrameFinalized(), recoverFramePointer(), removeRedundantBlockingStores(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), shouldGuaranteeTCO(), SimplifyShortMoveForm(), llvm::X86FrameLowering::spillCalleeSavedRegisters(), llvm::X86TargetLowering::supportSwiftError(), llvm::X86TargetLowering::useLoadStackGuardNode(), llvm::X86FrameLowering::X86FrameLowering(), llvm::X86LegalizerInfo::X86LegalizerInfo(), X86Subtarget(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isAtom()

|

inline |

TODO: to be removed later and replaced with suitable properties.

Definition at line 707 of file X86Subtarget.h.

Referenced by EmitTest(), llvm::X86TTIImpl::enableInterleavedAccessVectorization(), llvm::X86TTIImpl::getMaxInterleaveFactor(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isCallingConvWin64()

|

inline |

Definition at line 784 of file X86Subtarget.h.

References llvm::CallingConv::C, llvm::CallingConv::Fast, llvm::CallingConv::Intel_OCL_BI, llvm::CallingConv::Swift, llvm::CallingConv::Win64, llvm::CallingConv::X86_64_SysV, llvm::CallingConv::X86_FastCall, llvm::CallingConv::X86_StdCall, llvm::CallingConv::X86_ThisCall, and llvm::CallingConv::X86_VectorCall.

Referenced by emitClzero(), llvm::X86FrameLowering::emitPrologue(), get64BitArgumentGPRs(), get64BitArgumentXMMs(), getMOVL(), isSortedByValueNo(), llvm::X86CallLowering::lowerCall(), LowerVACOPY(), and MatchingStackOffset().

◆ isGLM()

|

inline |

Definition at line 709 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getArithmeticInstrCost(), and llvm::X86TTIImpl::getIntrinsicInstrCost().

◆ isLegalToCallImmediateAddr()

| bool X86Subtarget::isLegalToCallImmediateAddr | ( | ) | const |

Return true if the subtarget allows calls to immediate address.

Definition at line 214 of file X86Subtarget.cpp.

References llvm::dbgs(), llvm::TargetMachine::getRelocationModel(), hasAVX2(), hasAVX512(), hasFastGather(), hasSSE42(), hasSSE4A(), HasX86_64, isTargetDarwin(), isTargetELF(), isTargetKFreeBSD(), isTargetLinux(), isTargetSolaris(), isTargetWin32(), IsUAMem16Slow, LLVM_DEBUG, llvm_unreachable, ParseSubtargetFeatures(), Prefer256Bit, llvm::report_fatal_error(), stackAlignment, llvm::Reloc::Static, TM, X863DNowLevel, and X86SSELevel.

◆ isOSWindows()

|

inline |

Definition at line 769 of file X86Subtarget.h.

References llvm::Triple::isOSWindows().

Referenced by llvm::X86TargetLowering::getStackProbeSymbolName(), llvm::X86FrameLowering::inlineStackProbe(), isXor1OfSetCC(), llvm::X86FrameLowering::restoreCalleeSavedRegisters(), and llvm::X86FrameLowering::spillCalleeSavedRegisters().

◆ isPICStyleGOT()

|

inline |

Definition at line 775 of file X86Subtarget.h.

References llvm::PICStyles::GOT.

Referenced by llvm::X86TargetLowering::getJumpTableEncoding(), getMOVL(), llvm::X86InstrInfo::getSerializableDirectMachineOperandTargetFlags(), llvm::X86TargetLowering::LowerAsmOperandForConstraint(), and llvm::X86TargetLowering::LowerCustomJumpTableEntry().

◆ isPICStyleRIPRel()

|

inline |

Definition at line 776 of file X86Subtarget.h.

References llvm::PICStyles::RIPRel.

Referenced by llvm::X86TargetLowering::getPICJumpTableRelocBaseExpr(), LowerEXTRACT_SUBVECTOR(), LowerToTLSExecModel(), and llvm::X86AsmPrinter::PrintAsmOperand().

◆ isPICStyleStubPIC()

|

inline |

Definition at line 778 of file X86Subtarget.h.

References llvm::PICStyles::StubPIC.

Referenced by llvm::X86TargetLowering::LowerAsmOperandForConstraint().

◆ isPMADDWDSlow()

|

inline |

Definition at line 618 of file X86Subtarget.h.

Referenced by combineMulToPMADDWD().

◆ isPMULLDSlow()

|

inline |

Definition at line 617 of file X86Subtarget.h.

Referenced by reduceVMULWidth().

◆ isPositionIndependent()

|

inline |

Definition at line 782 of file X86Subtarget.h.

References llvm::TargetMachine::isPositionIndependent().

Referenced by classifyGlobalReference(), classifyLocalReference(), and X86Subtarget().

◆ isSHLDSlow()

|

inline |

Definition at line 616 of file X86Subtarget.h.

Referenced by combineOr(), and LowerFunnelShift().

◆ isSLM()

|

inline |

Definition at line 708 of file X86Subtarget.h.

Referenced by llvm::X86TTIImpl::getArithmeticInstrCost(), and llvm::X86TTIImpl::getIntrinsicInstrCost().

◆ isTarget64BitILP32()

|

inline |

Is this x86_64 with the ILP32 programming model (x32 ABI)?

Definition at line 535 of file X86Subtarget.h.

References llvm::Triple::getEnvironment(), llvm::Triple::GNUX32, and llvm::Triple::isOSNaCl().

Referenced by llvm::X86FrameLowering::determineCalleeSaves(), llvm::X86FrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitPrologue(), getLeaOP(), getMOVL(), llvm::X86RegisterInfo::getPtrSizedFrameRegister(), and Passv64i1ArgInRegs().

◆ isTarget64BitLP64()

|

inline |

Is this x86_64 with the LP64 programming model (standard AMD64, no x32)?

Definition at line 541 of file X86Subtarget.h.

References llvm::Triple::getEnvironment(), llvm::Triple::GNUX32, and llvm::Triple::isOSNaCl().

Referenced by createPHIsForCMOVsInSinkBB(), llvm::X86TargetLowering::getExceptionPointerRegister(), llvm::X86TargetLowering::getExceptionSelectorRegister(), llvm::X86RegisterInfo::getPointerRegClass(), getRetpolineSymbol(), llvm::X86TargetLowering::reduceSelectOfFPConstantLoads(), and llvm::X86FrameLowering::X86FrameLowering().

◆ isTargetAndroid()

|

inline |

Definition at line 736 of file X86Subtarget.h.

References llvm::Triple::isAndroid().

Referenced by llvm::X86TargetLowering::getSafeStackPointerLocation().

◆ isTargetCOFF()

|

inline |

Definition at line 730 of file X86Subtarget.h.

References llvm::Triple::isOSBinFormatCOFF().

Referenced by classifyGlobalFunctionReference(), classifyGlobalReference(), classifyLocalReference(), llvm::X86AsmPrinter::runOnMachineFunction(), and X86Subtarget().

◆ isTargetCygMing()

|

inline |

Definition at line 767 of file X86Subtarget.h.

References llvm::Triple::isOSCygMing().

Referenced by llvm::X86TargetLowering::getStackProbeSymbolName(), isSortedByValueNo(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetDarwin()

|

inline |

Definition at line 723 of file X86Subtarget.h.

References llvm::Triple::isOSDarwin().

Referenced by llvm::X86FrameLowering::adjustForSegmentedStacks(), classifyGlobalReference(), classifyLocalReference(), createPHIsForCMOVsInSinkBB(), isLegalToCallImmediateAddr(), LowerFSINCOS(), LowerToTLSExecModel(), X86Subtarget(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetDragonFly()

|

inline |

Definition at line 725 of file X86Subtarget.h.

References llvm::Triple::isOSDragonFly().

Referenced by llvm::X86FrameLowering::adjustForSegmentedStacks().

◆ isTargetELF()

|

inline |

Definition at line 729 of file X86Subtarget.h.

References llvm::Triple::isOSBinFormatELF().

Referenced by classifyGlobalFunctionReference(), classifyGlobalReference(), classifyLocalReference(), isLegalToCallImmediateAddr(), LowerToTLSExecModel(), X86Subtarget(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetFreeBSD()

|

inline |

Definition at line 724 of file X86Subtarget.h.

References llvm::Triple::isOSFreeBSD().

Referenced by llvm::X86FrameLowering::adjustForSegmentedStacks().

◆ isTargetFuchsia()

|

inline |

Definition at line 741 of file X86Subtarget.h.

References llvm::Triple::isOSFuchsia().

Referenced by llvm::X86TargetLowering::getIRStackGuard(), and llvm::X86TargetLowering::getSafeStackPointerLocation().

◆ isTargetGlibc()

|

inline |

Definition at line 735 of file X86Subtarget.h.

References llvm::Triple::isOSGlibc().

◆ isTargetKFreeBSD()

|

inline |

Definition at line 734 of file X86Subtarget.h.

References llvm::Triple::isOSKFreeBSD().

Referenced by isLegalToCallImmediateAddr().

◆ isTargetKnownWindowsMSVC()

|

inline |

Definition at line 747 of file X86Subtarget.h.

References llvm::Triple::isKnownWindowsMSVCEnvironment().

Referenced by LowerToTLSExecModel(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetLinux()

|

inline |

Definition at line 733 of file X86Subtarget.h.

References llvm::Triple::isOSLinux().

Referenced by llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::X86FrameLowering::adjustForSegmentedStacks(), isLegalToCallImmediateAddr(), and llvm::X86CallLowering::lowerCall().

◆ isTargetMachO()

|

inline |

Definition at line 731 of file X86Subtarget.h.

References llvm::Triple::isOSBinFormatMachO().

Referenced by llvm::X86TargetLowering::getStackProbeSymbolName(), isXor1OfSetCC(), and llvm::X86TargetLowering::useLoadStackGuardNode().

◆ isTargetMCU()

|

inline |

Definition at line 740 of file X86Subtarget.h.

References llvm::Triple::isOSIAMCU().

Referenced by computeBytesPoppedByCalleeForSRet(), getMOVL(), and isSortedByValueNo().

◆ isTargetNaCl()

|

inline |

Definition at line 737 of file X86Subtarget.h.

References llvm::Triple::isOSNaCl().

◆ isTargetNaCl32()

|

inline |

Definition at line 738 of file X86Subtarget.h.

References is64Bit().

◆ isTargetNaCl64()

|

inline |

Definition at line 739 of file X86Subtarget.h.

References is64Bit().

Referenced by createPHIsForCMOVsInSinkBB(), getRetpolineSymbol(), and llvm::X86FrameLowering::X86FrameLowering().

◆ isTargetPS4()

|

inline |

Definition at line 727 of file X86Subtarget.h.

References llvm::Triple::isPS4CPU().

◆ isTargetSolaris()

|

inline |

Definition at line 726 of file X86Subtarget.h.

References llvm::Triple::isOSSolaris().

Referenced by isLegalToCallImmediateAddr().

◆ isTargetWin32()

|

inline |

◆ isTargetWin64()

|

inline |

Definition at line 771 of file X86Subtarget.h.

Referenced by llvm::X86FrameLowering::adjustForSegmentedStacks(), llvm::X86InstrInfo::canMakeTailCallConditional(), llvm::X86FrameLowering::canUseAsEpilogue(), llvm::X86FrameLowering::getFrameIndexReferencePreferSP(), llvm::X86FrameLowering::inlineStackProbe(), LowerMULH(), llvm::X86TargetLowering::needsFixedCatchObjects(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetWindowsCoreCLR()

|

inline |

Definition at line 751 of file X86Subtarget.h.

References llvm::Triple::isWindowsCoreCLREnvironment().

Referenced by llvm::X86FrameLowering::emitStackProbe(), and llvm::X86FrameLowering::inlineStackProbe().

◆ isTargetWindowsCygwin()

|

inline |

Definition at line 755 of file X86Subtarget.h.

References llvm::Triple::isWindowsCygwinEnvironment().

◆ isTargetWindowsGNU()

|

inline |

Definition at line 759 of file X86Subtarget.h.

References llvm::Triple::isWindowsGNUEnvironment().

Referenced by LowerToTLSExecModel(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetWindowsItanium()

|

inline |

Definition at line 763 of file X86Subtarget.h.

References llvm::Triple::isWindowsItaniumEnvironment().

Referenced by LowerToTLSExecModel(), and llvm::X86TargetLowering::X86TargetLowering().

◆ isTargetWindowsMSVC()

|

inline |

Definition at line 743 of file X86Subtarget.h.

References llvm::Triple::isWindowsMSVCEnvironment().

Referenced by llvm::X86FrameLowering::restoreWin32EHStackPointers().

◆ isUnalignedMem16Slow()

|

inline |

Definition at line 619 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::allowsMisalignedMemoryAccesses(), and llvm::X86TargetLowering::getOptimalMemOpType().

◆ isUnalignedMem32Slow()

|

inline |

Definition at line 620 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::allowsMisalignedMemoryAccesses(), and llvm::X86TTIImpl::getMemoryOpCost().

◆ isXRaySupported()

|

inlineoverride |

Definition at line 702 of file X86Subtarget.h.

References is64Bit().

◆ LEAusesAG()

|

inline |

Definition at line 647 of file X86Subtarget.h.

Referenced by llvm::createX86FixupLEAs().

◆ padShortFunctions()

|

inline |

Definition at line 645 of file X86Subtarget.h.

Referenced by llvm::createX86PadShortFunctions().

◆ ParseSubtargetFeatures()

ParseSubtargetFeatures - Parses features string setting specified subtarget options.

Definition of function is auto generated by tblgen.

Referenced by isLegalToCallImmediateAddr().

◆ setPICStyle()

|

inline |

Definition at line 547 of file X86Subtarget.h.

Referenced by X86Subtarget().

◆ slow3OpsLEA()

|

inline |

Definition at line 649 of file X86Subtarget.h.

Referenced by llvm::createX86FixupLEAs().

◆ slowIncDec()

|

inline |

Definition at line 650 of file X86Subtarget.h.

Referenced by llvm::createX86FixupLEAs().

◆ slowLEA()

|

inline |

Definition at line 648 of file X86Subtarget.h.

Referenced by combineMul(), and llvm::createX86FixupLEAs().

◆ slowTwoMemOps()

|

inline |

Definition at line 646 of file X86Subtarget.h.

◆ supportPrintSchedInfo()

|

inlineoverride |

Definition at line 838 of file X86Subtarget.h.

◆ threewayBranchProfitable()

|

inline |

Definition at line 670 of file X86Subtarget.h.

Referenced by findUncondBrI().

◆ useAVX512Regs()

|

inline |

Definition at line 694 of file X86Subtarget.h.

Referenced by combineToExtendVectorInReg(), combineVectorSizedSetCCEquality(), EmitTest(), SplitOpsAndApply(), and llvm::X86TargetLowering::X86TargetLowering().

◆ useBWIRegs()

|

inline |

Definition at line 698 of file X86Subtarget.h.

Referenced by combineBasicSADPattern(), combineLoopSADPattern(), combineSubToSubus(), SplitOpsAndApply(), and llvm::X86TargetLowering::X86TargetLowering().

◆ useLeaForSP()

|

inline |

Definition at line 625 of file X86Subtarget.h.

Referenced by llvm::X86FrameLowering::emitSPUpdate().

◆ useRetpolineExternalThunk()

|

inline |

Definition at line 676 of file X86Subtarget.h.

Referenced by getRetpolineSymbol().

◆ useRetpolineIndirectBranches()

|

inline |

Definition at line 673 of file X86Subtarget.h.

Referenced by llvm::X86TargetLowering::areJTsAllowed().

◆ useRetpolineIndirectCalls()

|

inline |

Definition at line 672 of file X86Subtarget.h.

Referenced by llvm::X86FrameLowering::adjustForSegmentedStacks(), EmitNops(), and llvm::X86FrameLowering::inlineStackProbe().

◆ useSoftFloat()

|

inline |

Definition at line 714 of file X86Subtarget.h.

Referenced by combineFMinNumFMaxNum(), combineSIntToFP(), combineStore(), get64BitArgumentXMMs(), isSortedByValueNo(), llvm::X86TargetLowering::useSoftFloat(), and llvm::X86TargetLowering::X86TargetLowering().

Member Data Documentation

◆ CallLoweringInfo

|

protected |

GlobalISel related APIs.

Definition at line 429 of file X86Subtarget.h.

Referenced by getCallLowering(), and X86Subtarget().

◆ DeprecatedUseRetpoline

Deprecated flag, query UseRetpolineIndirectCalls and UseRetpolineIndirectBranches instead.

Definition at line 401 of file X86Subtarget.h.

◆ HasADX

Processor has ADX instructions.

Definition at line 184 of file X86Subtarget.h.

◆ HasAES

Target has AES instructions.

Definition at line 110 of file X86Subtarget.h.

◆ HasBITALG

Processor has AVX-512 Bit Algorithms instructions.

Definition at line 352 of file X86Subtarget.h.

◆ HasBMI

Processor has BMI1 instructions.

Definition at line 166 of file X86Subtarget.h.

◆ HasBMI2

Processor has BMI2 instructions.

Definition at line 169 of file X86Subtarget.h.

◆ HasBWI

Processor has AVX-512 Byte and Word instructions.

Definition at line 340 of file X86Subtarget.h.

◆ HasCDI

Processor has AVX-512 Conflict Detection Instructions.

Definition at line 331 of file X86Subtarget.h.

◆ HasCLDEMOTE

Processor has Cache Line Demote instruction.

Definition at line 205 of file X86Subtarget.h.

◆ HasCLFLUSHOPT

Processor supports Flush Cache Line instruction.

Definition at line 368 of file X86Subtarget.h.

◆ HasCLWB

Processor supports Cache Line Write Back instruction.

Definition at line 371 of file X86Subtarget.h.

◆ HasCLZERO

Processor has Cache Line Zero instruction.

Definition at line 202 of file X86Subtarget.h.

◆ HasCMov

True if this processor has conditional move instructions (generally pentium pro+).

Definition at line 98 of file X86Subtarget.h.

◆ HasCmpxchg16b

True if this processor has the CMPXCHG16B instruction; this is true for most x86-64 chips, but not the first AMD chips.

Definition at line 241 of file X86Subtarget.h.

◆ HasDQI

Processor has AVX-512 Doubleword and Quadword instructions.

Definition at line 337 of file X86Subtarget.h.

◆ HasERI

Processor has AVX-512 Exponential and Reciprocal Instructions.

Definition at line 328 of file X86Subtarget.h.

◆ HasERMSB

True if the processor has enhanced REP MOVSB/STOSB.

Definition at line 299 of file X86Subtarget.h.

◆ HasF16C

Processor has 16-bit floating point conversion instructions.

Definition at line 157 of file X86Subtarget.h.

◆ HasFast11ByteNOP

True if there is no performance penalty for writing NOPs with up to 11 bytes.

Definition at line 263 of file X86Subtarget.h.

◆ HasFast15ByteNOP

True if there is no performance penalty for writing NOPs with up to 15 bytes.

Definition at line 267 of file X86Subtarget.h.

◆ HasFastBEXTR

Processor has a single uop BEXTR implementation.

Definition at line 386 of file X86Subtarget.h.

◆ HasFastGather

True if gather is reasonably fast.

This is true for Skylake client and all AVX-512 CPUs.

Definition at line 271 of file X86Subtarget.h.

◆ HasFastHorizontalOps

Try harder to combine to horizontal vector ops if they are fast.

Definition at line 389 of file X86Subtarget.h.

◆ HasFastLZCNT

True if LZCNT instruction is fast.

Definition at line 290 of file X86Subtarget.h.

◆ HasFastPartialYMMorZMMWrite

True if there is no performance penalty to writing only the lower parts of a YMM or ZMM register without clearing the upper part.

Definition at line 259 of file X86Subtarget.h.

◆ HasFastScalarFSQRT

True if hardware SQRTSS instruction is at least as fast (latency) as RSQRTSS followed by a Newton-Raphson iteration.

Definition at line 275 of file X86Subtarget.h.

◆ HasFastSHLDRotate

True if SHLD based rotate is fast.

Definition at line 293 of file X86Subtarget.h.

◆ HasFastVariableShuffle

True if its preferable to combine to a single shuffle using a variable mask over multiple fixed shuffles.

Definition at line 255 of file X86Subtarget.h.

◆ HasFastVectorFSQRT

True if hardware SQRTPS/VSQRTPS instructions are at least as fast (throughput) as RSQRTPS/VRSQRTPS followed by a Newton-Raphson iteration.

Definition at line 279 of file X86Subtarget.h.

◆ HasFMA

Target has 3-operand fused multiply-add.

Definition at line 136 of file X86Subtarget.h.

◆ HasFMA4

Target has 4-operand fused multiply-add.

Definition at line 139 of file X86Subtarget.h.

◆ HasFSGSBase

Processor has FS/GS base insturctions.

Definition at line 160 of file X86Subtarget.h.

◆ HasFXSR

Target has FXSAVE/FXRESTOR instructions.

Definition at line 114 of file X86Subtarget.h.

◆ HasGFNI

Target has Galois Field Arithmetic instructions.

Definition at line 133 of file X86Subtarget.h.

◆ HasIFMA

Processor has Integer Fused Multiply Add.

Definition at line 178 of file X86Subtarget.h.

◆ HasINVPCID

Processor supports Invalidate Process-Context Identifier.

Definition at line 362 of file X86Subtarget.h.

◆ HasLAHFSAHF

Processor has LAHF/SAHF instructions.

Definition at line 196 of file X86Subtarget.h.

◆ HasLWP

Target has LWP instructions.

Definition at line 148 of file X86Subtarget.h.

◆ HasLZCNT

Processor has LZCNT instruction.

Definition at line 163 of file X86Subtarget.h.

◆ HasLZCNTFalseDeps

True if LZCNT/TZCNT instructions have a false dependency on the destination register.

Definition at line 251 of file X86Subtarget.h.

◆ HasMacroFusion

True if the processor supports macrofusion.

Definition at line 296 of file X86Subtarget.h.

◆ HasMOVBE

True if the processor has the MOVBE instruction.

Definition at line 151 of file X86Subtarget.h.

◆ HasMOVDIR64B

Processor has MOVDIR64B instruction (direct store 64 bytes).

Definition at line 211 of file X86Subtarget.h.

◆ HasMOVDIRI