#include "llvm/Support/MachineValueType.h"

Classes | |

| class | ElementCount |

Public Member Functions | |

| constexpr | MVT ()=default |

| constexpr | MVT (SimpleValueType SVT) |

| bool | operator> (const MVT &S) const |

| bool | operator< (const MVT &S) const |

| bool | operator== (const MVT &S) const |

| bool | operator!= (const MVT &S) const |

| bool | operator>= (const MVT &S) const |

| bool | operator<= (const MVT &S) const |

| bool | isValid () const |

| Return true if this is a valid simple valuetype. More... | |

| bool | isFloatingPoint () const |

| Return true if this is a FP or a vector FP type. More... | |

| bool | isInteger () const |

| Return true if this is an integer or a vector integer type. More... | |

| bool | isScalarInteger () const |

| Return true if this is an integer, not including vectors. More... | |

| bool | isVector () const |

| Return true if this is a vector value type. More... | |

| bool | isScalableVector () const |

| Return true if this is a vector value type where the runtime length is machine dependent. More... | |

| bool | is16BitVector () const |

| Return true if this is a 16-bit vector type. More... | |

| bool | is32BitVector () const |

| Return true if this is a 32-bit vector type. More... | |

| bool | is64BitVector () const |

| Return true if this is a 64-bit vector type. More... | |

| bool | is128BitVector () const |

| Return true if this is a 128-bit vector type. More... | |

| bool | is256BitVector () const |

| Return true if this is a 256-bit vector type. More... | |

| bool | is512BitVector () const |

| Return true if this is a 512-bit vector type. More... | |

| bool | is1024BitVector () const |

| Return true if this is a 1024-bit vector type. More... | |

| bool | is2048BitVector () const |

| Return true if this is a 2048-bit vector type. More... | |

| bool | isOverloaded () const |

| Return true if this is an overloaded type for TableGen. More... | |

| bool | isPow2VectorType () const |

| Returns true if the given vector is a power of 2. More... | |

| MVT | getPow2VectorType () const |

| Widens the length of the given vector MVT up to the nearest power of 2 and returns that type. More... | |

| MVT | getScalarType () const |

| If this is a vector, return the element type, otherwise return this. More... | |

| MVT | getVectorElementType () const |

| unsigned | getVectorNumElements () const |

| MVT::ElementCount | getVectorElementCount () const |

| unsigned | getSizeInBits () const |

| unsigned | getScalarSizeInBits () const |

| unsigned | getStoreSize () const |

| Return the number of bytes overwritten by a store of the specified value type. More... | |

| unsigned | getStoreSizeInBits () const |

| Return the number of bits overwritten by a store of the specified value type. More... | |

| bool | bitsGT (MVT VT) const |

| Return true if this has more bits than VT. More... | |

| bool | bitsGE (MVT VT) const |

| Return true if this has no less bits than VT. More... | |

| bool | bitsLT (MVT VT) const |

| Return true if this has less bits than VT. More... | |

| bool | bitsLE (MVT VT) const |

| Return true if this has no more bits than VT. More... | |

Static Public Member Functions | |

| static MVT | getFloatingPointVT (unsigned BitWidth) |

| static MVT | getIntegerVT (unsigned BitWidth) |

| static MVT | getVectorVT (MVT VT, unsigned NumElements) |

| static MVT | getScalableVectorVT (MVT VT, unsigned NumElements) |

| static MVT | getVectorVT (MVT VT, unsigned NumElements, bool IsScalable) |

| static MVT | getVectorVT (MVT VT, MVT::ElementCount EC) |

| static MVT | getVT (Type *Ty, bool HandleUnknown=false) |

| Return the value type corresponding to the specified type. More... | |

| static mvt_range | all_valuetypes () |

| SimpleValueType Iteration. More... | |

| static mvt_range | integer_valuetypes () |

| static mvt_range | fp_valuetypes () |

| static mvt_range | vector_valuetypes () |

| static mvt_range | integer_vector_valuetypes () |

| static mvt_range | fp_vector_valuetypes () |

| static mvt_range | integer_scalable_vector_valuetypes () |

| static mvt_range | fp_scalable_vector_valuetypes () |

Public Attributes | |

| SimpleValueType | SimpleTy = INVALID_SIMPLE_VALUE_TYPE |

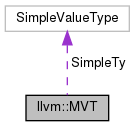

Detailed Description

Every type that is supported natively by some processor targeted by LLVM occurs here. This means that any legal value type can be represented by an MVT.

Definition at line 30 of file MachineValueType.h.

Member Enumeration Documentation

◆ SimpleValueType

| enum llvm::MVT::SimpleValueType : uint8_t |

Definition at line 32 of file MachineValueType.h.

Constructor & Destructor Documentation

◆ MVT() [1/2]

|

default |

Referenced by llvm::MVT::ElementCount::operator==().

◆ MVT() [2/2]

|

inline |

Definition at line 277 of file MachineValueType.h.

Member Function Documentation

◆ all_valuetypes()

|

inlinestatic |

SimpleValueType Iteration.

Definition at line 1013 of file MachineValueType.h.

References FIRST_VALUETYPE, and LAST_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), and llvm::TargetLoweringBase::initActions().

◆ bitsGE()

Return true if this has no less bits than VT.

Definition at line 777 of file MachineValueType.h.

References getSizeInBits().

Referenced by combineOrCmpEqZeroToCtlzSrl().

◆ bitsGT()

Return true if this has more bits than VT.

Definition at line 772 of file MachineValueType.h.

References getSizeInBits().

Referenced by LowerFCOPYSIGN(), and LowerScalarVariableShift().

◆ bitsLE()

Return true if this has no more bits than VT.

Definition at line 787 of file MachineValueType.h.

References getSizeInBits().

Referenced by getMaskNode(), llvm::SITargetLowering::getPreferredVectorAction(), and LowerScalarVariableShift().

◆ bitsLT()

Return true if this has less bits than VT.

Definition at line 782 of file MachineValueType.h.

References getSizeInBits().

Referenced by LowerFCOPYSIGN(), and LowerScalarVariableShift().

◆ fp_scalable_vector_valuetypes()

|

inlinestatic |

Definition at line 1049 of file MachineValueType.h.

References FIRST_FP_SCALABLE_VALUETYPE, and LAST_FP_SCALABLE_VALUETYPE.

◆ fp_valuetypes()

|

inlinestatic |

Definition at line 1022 of file MachineValueType.h.

References FIRST_FP_VALUETYPE, and LAST_FP_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), and llvm::SystemZTargetLowering::SystemZTargetLowering().

◆ fp_vector_valuetypes()

|

inlinestatic |

Definition at line 1038 of file MachineValueType.h.

References FIRST_FP_VECTOR_VALUETYPE, and LAST_FP_VECTOR_VALUETYPE.

Referenced by llvm::MipsTargetLowering::MipsTargetLowering(), and llvm::X86TargetLowering::X86TargetLowering().

◆ getFloatingPointVT()

Definition at line 791 of file MachineValueType.h.

References f128, f16, f32, f64, f80, and llvm_unreachable.

Referenced by combineHorizontalPredicateResult(), combineX86ShuffleChain(), combineX86ShufflesConstants(), EltsFromConsecutiveLoads(), llvm::EVT::getFloatingPointVT(), lower256BitVectorShuffle(), lowerBuildVectorAsBroadcast(), LowerInterruptReturn(), LowerVectorFP_TO_INT(), LowerVectorINT_TO_FP(), lowerVectorShuffle(), mayTailCallThisCC(), and PrepareCall().

◆ getIntegerVT()

Definition at line 808 of file MachineValueType.h.

References i1, i128, i16, i32, i64, i8, and INVALID_SIMPLE_VALUE_TYPE.

Referenced by buildVector(), llvm::EVT::changeTypeToInteger(), llvm::EVT::changeVectorElementTypeToInteger(), CombineBaseUpdate(), combineX86ShuffleChain(), combineX86ShufflesConstants(), llvm::ComputeSignatureVTs(), ConstantBuildVector(), ConvertI1VectorToInteger(), EltsFromConsecutiveLoads(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), ExtractBitFromMaskVector(), findUser(), llvm::EVT::getIntegerVT(), getPermuteNode(), llvm::TargetLoweringBase::getPointerTy(), GetRegistersForValue(), llvm::TargetLoweringBase::getScalarShiftAmountTy(), llvm::MipsTargetLowering::getTypeForExtReturn(), llvm::TargetLoweringBase::hasFastEqualityCompare(), llvm::X86TargetLowering::hasFastEqualityCompare(), hasOnlySelectUsers(), InsertBitToMaskVector(), isMulPowOf2(), isPromotedInstructionLegal(), isSplatZeroExtended(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBUILD_VECTORvXi1(), lowerBuildVectorAsBroadcast(), LowerCTPOP(), lowerFCOPYSIGN64(), llvm::HexagonTargetLowering::LowerSETCC(), LowerTruncateVecI1(), llvm::HexagonTargetLowering::LowerUnalignedLoad(), LowerVectorCTLZInRegLUT(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsPermuteAndUnpack(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleToEXPAND(), lowerVectorShuffleWithPERMV(), lowerVSELECTtoVectorShuffle(), lowerX86FPLogicOp(), matchBinaryPermuteVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), matchVectorShuffleAsShift(), matchVectorShuffleWithPACK(), mayTailCallThisCC(), memsetStore(), llvm::TargetLowering::ParseConstraints(), performExtendCombine(), llvm::X86TargetLowering::ReplaceNodeResults(), scaleVectorType(), llvm::HexagonTargetLowering::shouldExpandAtomicRMWInIR(), llvm::AArch64TargetLowering::shouldTransformSignedTruncationCheck(), llvm::X86TargetLowering::shouldTransformSignedTruncationCheck(), ShrinkLoadReplaceStoreWithStore(), skipExtensionForVectorMULL(), SkipExtensionForVMULL(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::HexagonDAGToDAGISel::StoreInstrForLoadIntrinsic(), llvm::SystemZTargetLowering::SystemZTargetLowering(), tryBuildVectorReplicate(), unpackFromMemLoc(), llvm::WebAssemblyTargetLowering::WebAssemblyTargetLowering(), and llvm::X86TargetLowering::X86TargetLowering().

◆ getPow2VectorType()

|

inline |

Widens the length of the given vector MVT up to the nearest power of 2 and returns that type.

Definition at line 402 of file MachineValueType.h.

References getVectorElementType(), getVectorNumElements(), getVectorVT(), isPow2VectorType(), and llvm::Log2_32_Ceil().

Referenced by llvm::TargetLoweringBase::computeRegisterProperties().

◆ getScalableVectorVT()

Definition at line 906 of file MachineValueType.h.

References f16, f32, f64, i1, i16, i32, i64, i8, INVALID_SIMPLE_VALUE_TYPE, nxv16f32, nxv16i1, nxv16i16, nxv16i32, nxv16i64, nxv16i8, nxv1f32, nxv1f64, nxv1i1, nxv1i16, nxv1i32, nxv1i64, nxv1i8, nxv2f16, nxv2f32, nxv2f64, nxv2i1, nxv2i16, nxv2i32, nxv2i64, nxv2i8, nxv32i1, nxv32i16, nxv32i32, nxv32i64, nxv32i8, nxv4f16, nxv4f32, nxv4f64, nxv4i1, nxv4i16, nxv4i32, nxv4i64, nxv4i8, nxv8f16, nxv8f32, nxv8f64, nxv8i1, nxv8i16, nxv8i32, nxv8i64, nxv8i8, and SimpleTy.

Referenced by getVectorVT().

◆ getScalarSizeInBits()

|

inline |

Definition at line 755 of file MachineValueType.h.

References getScalarType(), and getSizeInBits().

Referenced by combineAndnp(), combineInsertSubvector(), combineMOVMSK(), combineTargetShuffle(), combineX86ShuffleChain(), computeBytesPoppedByCalleeForSRet(), llvm::TargetLoweringBase::computeRegisterProperties(), createPackShuffleMask(), llvm::createUnpackShuffleMask(), createVariablePermute(), DecodePALIGNRMask(), llvm::PPCTargetLowering::expandVSXLoadForLE(), llvm::PPCTargetLowering::expandVSXStoreForLE(), getConstantVector(), getConstVector(), llvm::RegsForValue::getCopyFromRegs(), getFauxShuffleMask(), getMemCmpLoad(), llvm::SystemZTargetLowering::getPreferredVectorAction(), llvm::PPCTargetLowering::getPreferredVectorAction(), getPromotedVectorElementType(), getPSHUFShuffleMask(), getScalarValueForVectorElement(), getTargetShuffleMask(), getTargetVShiftNode(), is128BitLaneCrossingShuffleMask(), isRepeatedShuffleMask(), isRepeatedTargetShuffleMask(), isSplatZeroExtended(), lower256BitVectorShuffle(), LowerBITREVERSE_XOP(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerCTTZ(), LowerEXTEND_VECTOR_INREG(), LowerFABSorFNEG(), LowerFCOPYSIGN(), LowerLoad(), LowerMGATHER(), LowerMSCATTER(), LowerMSTORE(), LowerRotate(), LowerShift(), lowerShuffleAsRepeatedMaskAndLanePermute(), LowerTruncateVecI1(), lowerV4X128VectorShuffle(), LowerVectorCTLZInRegLUT(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBlendAndPermute(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsPermuteAndUnpack(), lowerVectorShuffleAsShift(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleAsZeroOrAnyExtend(), lowerVectorShuffleByMerging128BitLanes(), lowerVectorShuffleWithPERMV(), lowerVectorShuffleWithPSHUFB(), lowerVSELECTtoVectorShuffle(), LowerVSETCC(), lowerX86FPLogicOp(), LowerZERO_EXTEND_Mask(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryVectorShuffle(), matchVectorShuffleAsEXTRQ(), matchVectorShuffleAsINSERTQ(), matchVectorShuffleWithPACK(), matchVectorShuffleWithSHUFPD(), processShaderInputArgs(), scaleVectorType(), llvm::X86TargetLowering::SimplifyDemandedBitsForTargetNode(), SupportedVectorShiftWithImm(), and SupportedVectorVarShift().

◆ getScalarType()

|

inline |

If this is a vector, return the element type, otherwise return this.

Definition at line 412 of file MachineValueType.h.

References getVectorElementType(), and isVector().

Referenced by llvm::AMDGPUTargetLowering::analyzeFormalArgumentsCompute(), combineExtractSubvector(), combineVectorSignBitsTruncation(), createVariablePermute(), llvm::SITargetLowering::getPreferredVectorAction(), llvm::NVPTXTargetLowering::getPreferredVectorAction(), getScalarSizeInBits(), getTargetShuffleMask(), llvm::X86TargetLowering::isShuffleMaskLegal(), LowerADDSAT_SUBSAT(), lowerAddSub(), LowerBITREVERSE(), lowerBuildVectorAsBroadcast(), LowerMINMAX(), LowerMLOAD(), LowerMSTORE(), LowerMUL(), lowerRegToMasks(), llvm::AMDGPUTargetLowering::LowerSIGN_EXTEND_INREG(), LowerVectorCTPOP(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsRotate(), matchUnaryVectorShuffle(), parseTexFail(), pickOpcodeForVT(), shouldGuaranteeTCO(), tryCombineShiftImm(), useSinCos(), and widenSubVector().

◆ getSizeInBits()

|

inline |

Definition at line 624 of file MachineValueType.h.

References Any, ExceptRef, f128, f16, f32, f64, f80, fAny, i1, i128, i16, i32, i64, i8, iAny, iPTR, iPTRAny, llvm_unreachable, Metadata, nxv16f32, nxv16i1, nxv16i16, nxv16i32, nxv16i64, nxv16i8, nxv1f32, nxv1f64, nxv1i1, nxv1i16, nxv1i32, nxv1i64, nxv1i8, nxv2f16, nxv2f32, nxv2f64, nxv2i1, nxv2i16, nxv2i32, nxv2i64, nxv2i8, nxv32i1, nxv32i16, nxv32i32, nxv32i64, nxv32i8, nxv4f16, nxv4f32, nxv4f64, nxv4i1, nxv4i16, nxv4i32, nxv4i64, nxv4i8, nxv8f16, nxv8f32, nxv8f64, nxv8i1, nxv8i16, nxv8i32, nxv8i64, nxv8i8, Other, ppcf128, token, v1024i1, v128i1, v128i16, v128i8, v16f32, v16i1, v16i16, v16i32, v16i64, v16i8, v1f32, v1f64, v1i1, v1i128, v1i16, v1i32, v1i64, v1i8, v256i8, v2f16, v2f32, v2f64, v2i1, v2i16, v2i32, v2i64, v2i8, v32i1, v32i16, v32i32, v32i64, v32i8, v4f16, v4f32, v4f64, v4i1, v4i16, v4i32, v4i64, v4i8, v512i1, v64i1, v64i16, v64i32, v64i8, v8f16, v8f32, v8f64, v8i1, v8i16, v8i32, v8i64, v8i8, vAny, and x86mmx.

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), llvm::HexagonTargetLowering::allowsMisalignedMemoryAccesses(), AnalyzeReturnValues(), bitsGE(), bitsGT(), bitsLE(), bitsLT(), CallingConvSupported(), llvm::CC_ARM_AAPCS_Custom_Aggregate(), CC_Lanai32_VarArg(), CC_MipsO32_FP64(), CC_Sparc64_Full(), CC_Sparc64_Half(), llvm::CC_X86_32_VectorCall(), llvm::CC_X86_64_VectorCall(), llvm::AArch64TargetLowering::CCAssignFnForReturn(), llvm::EVT::changeVectorElementTypeToInteger(), CombineBaseUpdate(), combineBasicSADPattern(), combineInsertSubvector(), combineLoopSADPattern(), combineStore(), combineVectorSignBitsTruncation(), combineX86ShuffleChain(), combineX86ShufflesConstants(), combineX86ShufflesRecursively(), llvm::TargetLoweringBase::computeRegisterProperties(), convertShiftLeftToScale(), createPackShuffleMask(), createShuffleStride(), createVariablePermute(), DecodePALIGNRMask(), determineLocInfo(), EltsFromConsecutiveLoads(), EnsureStackAlignment(), llvm::TargetLowering::expandUnalignedStore(), ExtractBitFromMaskVector(), llvm::FastISel::fastEmit_ri_(), foldMaskAndShiftToScale(), foldMaskedShiftToBEXTR(), genShuffleBland(), getCompareCC(), getComparePred(), getCopyFromParts(), getCopyFromPartsVector(), getCopyToParts(), getCopyToPartsVector(), getEstimate(), getFauxShuffleMask(), getHopForBuildVector(), getMaskNode(), getMemCmpLoad(), getMOVL(), getOpenCLAlignment(), llvm::HvxSelector::getPairVT(), llvm::HexagonTargetLowering::getPreferredVectorAction(), getPromotedVectorElementType(), getPSHUFShuffleMask(), llvm::HexagonTargetLowering::getRegForInlineAsmConstraint(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), llvm::ARMTargetLowering::getRegForInlineAsmConstraint(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), GetRegistersForValue(), llvm::RegsForValue::getRegsAndSizes(), getScalarSizeInBits(), getScalarValueForVectorElement(), llvm::X86TargetLowering::getSetCCResultType(), getShiftAmountTyForConstant(), llvm::X86TTIImpl::getShuffleCost(), llvm::HvxSelector::getSingleVT(), llvm::EVT::getSizeInBits(), getStoreSize(), getTargetVShiftByConstNode(), getTargetVShiftNode(), llvm::HexagonSubtarget::getTypeAlignment(), llvm::AArch64TargetLowering::getVaListSizeInBits(), llvm::TargetLoweringBase::getVectorTypeBreakdown(), llvm::MipsTargetLowering::getVectorTypeBreakdownForCallingConv(), getVectorTypeBreakdownMVT(), getZeroVector(), group2Shuffle(), llvm::MipsCallLowering::MipsHandler::handle(), hasBZHI(), insert1BitVector(), InsertBitToMaskVector(), isBroadcastShuffle(), isHorizontalBinOp(), llvm::HexagonSubtarget::isHVXVectorType(), isMulPowOf2(), llvm::X86TargetLowering::isShuffleMaskLegal(), isSupportedType(), isTruncWithZeroHighBitsInput(), llvm::LLT::LLT(), LowerADJUST_TRAMPOLINE(), LowerAsSplatVectorLoad(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBITCAST(), LowerBITREVERSE_XOP(), llvm::HexagonTargetLowering::LowerBUILD_VECTOR(), LowerBUILD_VECTORAsVariablePermute(), LowerBUILD_VECTORvXi1(), lowerBuildVectorAsBroadcast(), LowerCallResult(), llvm::TargetLowering::LowerCallTo(), llvm::HexagonTargetLowering::LowerCONCAT_VECTORS(), LowerCTLZ(), LowerEXTEND_VECTOR_INREG(), LowerEXTRACT_VECTOR_ELT_SSE4(), lowerFCOPYSIGN64(), llvm::HexagonTargetLowering::LowerFormalArguments(), llvm::SparcTargetLowering::LowerFormalArguments_64(), LowerFPToInt(), LowerHorizontalByteSum(), LowerI64IntToFP_AVX512DQ(), LowerLoad(), LowerMGATHER(), LowerMLOAD(), LowerMSCATTER(), LowerMSTORE(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), LowerSCALAR_TO_VECTOR(), llvm::HexagonTargetLowering::LowerSETCC(), LowerShiftParts(), lowerShuffleAsRepeatedMaskAndLanePermute(), LowerSIGN_EXTEND_Mask(), llvm::LanaiTargetLowering::LowerSRL_PARTS(), LowerStore(), LowerTruncateVecI1(), LowerVASTART(), llvm::HexagonTargetLowering::LowerVECTOR_SHUFFLE(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTPOP(), LowerVectorIntUnary(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBlendOfPSHUFBs(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsLanePermuteAndPermute(), lowerVectorShuffleAsSplitOrBlend(), lowerVectorShuffleAsUNPCKAndPermute(), lowerVectorShuffleAsZeroOrAnyExtend(), lowerVectorShuffleWithPSHUFB(), lowerVSELECTtoVectorShuffle(), LowerVSETCC(), lowerX86FPLogicOp(), LowerZERO_EXTEND_Mask(), matchBinaryPermuteVectorShuffle(), MatchingStackOffset(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), mayTailCallThisCC(), llvm::TargetLowering::ParseConstraints(), performBitcastCombine(), performFDivCombine(), performFpToIntCombine(), PerformSTORECombine(), PerformVCVTCombine(), PerformVDIVCombine(), pickOpcodeForVT(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::HexagonDAGToDAGISel::SelectVAlign(), setGroupSize(), setTargetShuffleZeroElements(), llvm::HexagonTargetLowering::shouldExpandAtomicRMWInIR(), shouldGuaranteeTCO(), simplifyDivRem(), splitAndLowerVectorShuffle(), tryCombineShiftImm(), UnpackFromArgumentSlot(), VisitGlobalVariableForEmission(), widenSubVector(), llvm::X86CallLowering::X86CallLowering(), and X86ChooseCmpImmediateOpcode().

◆ getStoreSize()

|

inline |

Return the number of bytes overwritten by a store of the specified value type.

Definition at line 761 of file MachineValueType.h.

References getSizeInBits().

Referenced by CC_MipsO32(), CC_MipsO32_FP64(), combineStore(), computeBytesPoppedByCalleeForSRet(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), EnsureStackAlignment(), getCompareCC(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getInterleavedMemoryOpCost(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX2(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX512(), getRetpolineSymbol(), llvm::X86TTIImpl::getShuffleCost(), getStoreSizeInBits(), isSupportedType(), llvm::SITargetLowering::isTypeDesirableForOp(), llvm::SITargetLowering::LowerCall(), lowerCallResult(), tryToElideArgumentCopy(), and llvm::X86CallLowering::X86CallLowering().

◆ getStoreSizeInBits()

|

inline |

Return the number of bits overwritten by a store of the specified value type.

Definition at line 767 of file MachineValueType.h.

References getStoreSize().

Referenced by llvm::HexagonTargetLowering::LowerCall(), and llvm::HexagonTargetLowering::LowerFormalArguments().

◆ getVectorElementCount()

|

inline |

Definition at line 620 of file MachineValueType.h.

References getVectorNumElements(), and isScalableVector().

Referenced by llvm::EVT::getVectorElementCount().

◆ getVectorElementType()

|

inline |

Definition at line 416 of file MachineValueType.h.

References f16, f32, f64, i1, i128, i16, i32, i64, i8, llvm_unreachable, nxv16f32, nxv16i1, nxv16i16, nxv16i32, nxv16i64, nxv16i8, nxv1f32, nxv1f64, nxv1i1, nxv1i16, nxv1i32, nxv1i64, nxv1i8, nxv2f16, nxv2f32, nxv2f64, nxv2i1, nxv2i16, nxv2i32, nxv2i64, nxv2i8, nxv32i1, nxv32i16, nxv32i32, nxv32i64, nxv32i8, nxv4f16, nxv4f32, nxv4f64, nxv4i1, nxv4i16, nxv4i32, nxv4i64, nxv4i8, nxv8f16, nxv8f32, nxv8f64, nxv8i1, nxv8i16, nxv8i32, nxv8i64, nxv8i8, v1024i1, v128i1, v128i16, v128i8, v16f32, v16i1, v16i16, v16i32, v16i64, v16i8, v1f32, v1f64, v1i1, v1i128, v1i16, v1i32, v1i64, v1i8, v256i8, v2f16, v2f32, v2f64, v2i1, v2i16, v2i32, v2i64, v2i8, v32i1, v32i16, v32i32, v32i64, v32i8, v4f16, v4f32, v4f64, v4i1, v4i16, v4i32, v4i64, v4i8, v512i1, v64i1, v64i16, v64i32, v64i8, v8f16, v8f32, v8f64, v8i1, v8i16, v8i32, v8i64, and v8i8.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::HexagonTargetLowering::allowsMisalignedMemoryAccesses(), CallingConvSupported(), llvm::EVT::changeVectorElementTypeToInteger(), combineInsertSubvector(), combineMOVMSK(), combineRedundantDWordShuffle(), combineTargetShuffle(), llvm::TargetLoweringBase::computeRegisterProperties(), convertShiftLeftToScale(), decrementVectorConstant(), ExtendToType(), ExtractBitFromMaskVector(), getConstVector(), getPow2VectorType(), llvm::HexagonTargetLowering::getPreferredVectorAction(), llvm::X86TargetLowering::getPreferredVectorAction(), getScalarType(), getScalarValueForVectorElement(), llvm::X86TargetLowering::getSetCCResultType(), llvm::X86TTIImpl::getShuffleCost(), getShuffleScalarElt(), getTargetVShiftByConstNode(), getTargetVShiftNode(), getUnderlyingExtractedFromVec(), llvm::EVT::getVectorElementType(), getVectorTypeBreakdownMVT(), getZeroVector(), InsertBitToMaskVector(), llvm::HexagonSubtarget::isHVXVectorType(), isTruncWithZeroHighBitsInput(), isTypePromotionOfi1ZeroUpBits(), llvm::LLT::LLT(), Lower256IntVSETCC(), LowerANY_EXTEND(), LowerAVXCONCAT_VECTORS(), LowerAVXExtend(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBITCAST(), LowerBUILD_VECTORAsVariablePermute(), LowerBUILD_VECTORvXi1(), LowerBuildVectorv4x32(), llvm::HexagonTargetLowering::LowerCONCAT_VECTORS(), LowerCONCAT_VECTORS(), LowerCONCAT_VECTORSvXi1(), LowerEXTEND_VECTOR_INREG(), LowerEXTRACT_SUBVECTOR(), llvm::HexagonTargetLowering::LowerEXTRACT_VECTOR_ELT(), LowerHorizontalByteSum(), LowerINSERT_SUBVECTOR(), llvm::HexagonTargetLowering::LowerINSERT_VECTOR_ELT(), LowerIntVSETCC_AVX512(), LowerLoad(), LowerMGATHER(), LowerMSCATTER(), LowerSCALAR_TO_VECTOR(), LowerScalarVariableShift(), llvm::HexagonTargetLowering::LowerSETCC(), LowerSIGN_EXTEND(), LowerSIGN_EXTEND_Mask(), LowerStore(), LowerTruncateVecI1(), lowerV2X128VectorShuffle(), lowerV4X128VectorShuffle(), lowerV8I16GeneralSingleInputVectorShuffle(), llvm::HexagonTargetLowering::LowerVECTOR_SHUFFLE(), LowerVectorCTLZ(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTPOP(), LowerVectorCTPOPInRegLUT(), LowerVectorIntUnary(), lowerVectorShuffle(), lowerVectorShuffleAsBitBlend(), lowerVectorShuffleAsBitMask(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsTruncBroadcast(), lowerVectorShuffleWithUndefHalf(), lowerVectorShuffleWithVPMOV(), LowerVSETCC(), LowerVSETCCWithSUBUS(), LowerZERO_EXTEND(), LowerZERO_EXTEND_Mask(), performConcatVectorsCombine(), performFDivCombine(), performFpToIntCombine(), PerformVCVTCombine(), PerformVDIVCombine(), llvm::X86TargetLowering::ReplaceNodeResults(), scaleVectorType(), llvm::TargetLoweringBase::setJumpIsExpensive(), llvm::HexagonTargetLowering::shouldExpandAtomicRMWInIR(), split256IntArith(), split512IntArith(), splitAndLowerVectorShuffle(), tryExtendDUPToExtractHigh(), and UnrollVectorShift().

◆ getVectorNumElements()

|

inline |

Definition at line 518 of file MachineValueType.h.

References llvm_unreachable, nxv16f32, nxv16i1, nxv16i16, nxv16i32, nxv16i64, nxv16i8, nxv1f32, nxv1f64, nxv1i1, nxv1i16, nxv1i32, nxv1i64, nxv1i8, nxv2f16, nxv2f32, nxv2f64, nxv2i1, nxv2i16, nxv2i32, nxv2i64, nxv2i8, nxv32i1, nxv32i16, nxv32i32, nxv32i64, nxv32i8, nxv4f16, nxv4f32, nxv4f64, nxv4i1, nxv4i16, nxv4i32, nxv4i64, nxv4i8, nxv8f16, nxv8f32, nxv8f64, nxv8i1, nxv8i16, nxv8i32, nxv8i64, nxv8i8, v1024i1, v128i1, v128i16, v128i8, v16f32, v16i1, v16i16, v16i32, v16i64, v16i8, v1f32, v1f64, v1i1, v1i128, v1i16, v1i32, v1i64, v1i8, v256i8, v2f16, v2f32, v2f64, v2i1, v2i16, v2i32, v2i64, v2i8, v32i1, v32i16, v32i32, v32i64, v32i8, v4f16, v4f32, v4f64, v4i1, v4i16, v4i32, v4i64, v4i8, v512i1, v64i1, v64i16, v64i32, v64i8, v8f16, v8f32, v8f64, v8i1, v8i16, v8i32, v8i64, and v8i8.

Referenced by llvm::AMDGPUTargetLowering::analyzeFormalArgumentsCompute(), combineBasicSADPattern(), combineExtractSubvector(), combineHorizontalPredicateResult(), combineInsertSubvector(), combineMOVMSK(), combineTargetShuffle(), combineX86ShuffleChain(), llvm::TargetLoweringBase::computeRegisterProperties(), convertShiftLeftToScale(), createPackShuffleMask(), createShuffleStride(), llvm::createUnpackShuffleMask(), createVariablePermute(), DecodePALIGNRMask(), decrementVectorConstant(), ExpandHorizontalBinOp(), ExtendToType(), ExtractBitFromMaskVector(), genShuffleBland(), getConstVector(), getFauxShuffleMask(), getGatherNode(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX2(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX512(), getMemCmpLoad(), getMOVL(), getPow2VectorType(), llvm::HexagonTargetLowering::getPreferredVectorAction(), llvm::SITargetLowering::getPreferredVectorAction(), llvm::TargetLoweringBase::getPreferredVectorAction(), llvm::NVPTXTargetLowering::getPreferredVectorAction(), llvm::X86TargetLowering::getPreferredVectorAction(), getPrefetchNode(), getScatterNode(), llvm::X86TTIImpl::getShuffleCost(), getShuffleScalarElt(), getShuffleVectorZeroOrUndef(), getTargetShuffleMask(), llvm::X86TargetLowering::getTgtMemIntrinsic(), getUnderlyingExtractedFromVec(), getVectorElementCount(), getVectorMaskingNode(), llvm::EVT::getVectorNumElements(), getVectorTypeBreakdownMVT(), getZeroVector(), group2Shuffle(), insert1BitVector(), InsertBitToMaskVector(), isAddSubOrSubAdd(), isHopBuildVector(), isHorizontalBinOp(), llvm::HexagonSubtarget::isHVXVectorType(), isPow2VectorType(), llvm::LLT::LLT(), lower1BitVectorShuffle(), lower256BitVectorShuffle(), Lower256IntVSETCC(), LowerAsSplatVectorLoad(), LowerAVXCONCAT_VECTORS(), LowerAVXExtend(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBITCAST(), LowerBITREVERSE(), LowerBITREVERSE_XOP(), llvm::HexagonTargetLowering::LowerBUILD_VECTOR(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerBuildVectorAsInsert(), lowerBuildVectorToBitOp(), llvm::HexagonTargetLowering::LowerCONCAT_VECTORS(), LowerCONCAT_VECTORSvXi1(), LowerEXTEND_VECTOR_INREG(), LowerEXTRACT_SUBVECTOR(), LowerLoad(), LowerMGATHER(), LowerMSCATTER(), LowerMUL(), LowerMULH(), LowerRotate(), LowerSCALAR_TO_VECTOR(), LowerScalarImmediateShift(), LowerScalarVariableShift(), llvm::HexagonTargetLowering::LowerSETCC(), LowerShift(), lowerShuffleAsRepeatedMaskAndLanePermute(), LowerSIGN_EXTEND(), llvm::AMDGPUTargetLowering::LowerSIGN_EXTEND_INREG(), LowerSIGN_EXTEND_Mask(), LowerStore(), LowerToHorizontalOp(), LowerTruncateVecI1(), lowerV8I16GeneralSingleInputVectorShuffle(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTLZInRegLUT(), LowerVectorCTPOP(), LowerVectorCTPOPInRegLUT(), LowerVectorIntUnary(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsLanePermuteAndPermute(), lowerVectorShuffleAsShift(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleAsZeroOrAnyExtend(), lowerVectorShuffleToEXPAND(), lowerVectorShuffleWithPERMV(), lowerVectorShuffleWithUndefHalf(), lowerVectorShuffleWithVPMOV(), lowerVSELECTtoVectorShuffle(), LowerVSETCC(), LowerZERO_EXTEND_Mask(), matchUnaryVectorShuffle(), matchVectorShuffleAsEXTRQ(), matchVectorShuffleAsINSERTQ(), matchVectorShuffleWithPACK(), matchVectorShuffleWithSHUFPD(), matchVectorShuffleWithUNPCK(), parseTexFail(), performConcatVectorsCombine(), recoverFramePointer(), reduceVMULWidth(), llvm::X86TargetLowering::ReplaceNodeResults(), scaleVectorType(), setGroupSize(), llvm::TargetLoweringBase::setJumpIsExpensive(), setTargetShuffleZeroElements(), llvm::X86TargetLowering::SimplifyDemandedBitsForTargetNode(), llvm::X86TargetLowering::SimplifyDemandedVectorEltsForTargetNode(), split256IntArith(), split512IntArith(), splitAndLowerVectorShuffle(), and tryExtendDUPToExtractHigh().

◆ getVectorVT() [1/3]

Definition at line 827 of file MachineValueType.h.

References f16, f32, f64, i1, i128, i16, i32, i64, i8, INVALID_SIMPLE_VALUE_TYPE, SimpleTy, v1024i1, v128i1, v128i16, v128i8, v16f32, v16i1, v16i16, v16i32, v16i64, v16i8, v1f32, v1f64, v1i1, v1i128, v1i16, v1i32, v1i64, v1i8, v256i8, v2f16, v2f32, v2f64, v2i1, v2i16, v2i32, v2i64, v2i8, v32i1, v32i16, v32i32, v32i64, v32i8, v4f16, v4f32, v4f64, v4i1, v4i16, v4i32, v4i64, v4i8, v512i1, v64i1, v64i16, v64i32, v64i8, v8f16, v8f32, v8f64, v8i1, v8i16, v8i32, v8i64, and v8i8.

Referenced by AddCombineBUILD_VECTORToVPADDL(), buildVector(), llvm::EVT::changeVectorElementTypeToInteger(), CombineBaseUpdate(), combineBasicSADPattern(), combineHorizontalPredicateResult(), combineInsertSubvector(), combineLoopMAddPattern(), combineLoopSADPattern(), combineMOVMSK(), combineMulToPMADDWD(), combineTargetShuffle(), combineVSelectWithAllOnesOrZeros(), combineX86ShuffleChain(), combineX86ShufflesConstants(), createPSADBW(), createVariablePermute(), EltsFromConsecutiveLoads(), ExtractBitFromMaskVector(), findUser(), getConstVector(), getExpandedMinMaxOps(), getFPTernOp(), getGatherNode(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX512(), getMaskNode(), getOnesVector(), llvm::HvxSelector::getPairVT(), getPermuteNode(), getPow2VectorType(), getPrefetchNode(), getPromotedVectorElementType(), getScatterNode(), llvm::HvxSelector::getSingleVT(), getTargetVShiftNode(), llvm::X86TargetLowering::getTgtMemIntrinsic(), getVectorMaskingNode(), getVectorTypeBreakdownMVT(), llvm::EVT::getVectorVT(), getVectorVT(), getZeroVector(), group2Shuffle(), llvm::HexagonTargetLowering::HexagonTargetLowering(), InsertBitToMaskVector(), lower1BitVectorShuffle(), lower256BitVectorShuffle(), Lower256IntVSETCC(), LowerAVXCONCAT_VECTORS(), LowerAVXExtend(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBITCAST(), LowerBITREVERSE_XOP(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerCONCAT_VECTORSvXi1(), LowerCTPOP(), LowerEXTEND_VECTOR_INREG(), LowerHorizontalByteSum(), LowerI64IntToFP_AVX512DQ(), LowerINTRINSIC_W_CHAIN(), LowerMGATHER(), LowerMLOAD(), LowerMSCATTER(), LowerMSTORE(), LowerMUL(), LowerMULH(), LowerRotate(), LowerSCALAR_TO_VECTOR(), LowerScalarImmediateShift(), LowerScalarVariableShift(), llvm::HexagonTargetLowering::LowerSETCC(), LowerShift(), LowerSIGN_EXTEND(), LowerSIGN_EXTEND_Mask(), LowerStore(), LowerTruncateVecI1(), llvm::HexagonTargetLowering::LowerUnalignedLoad(), lowerV2X128VectorShuffle(), lowerV4X128VectorShuffle(), lowerV8I16GeneralSingleInputVectorShuffle(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTLZInRegLUT(), LowerVectorCTPOP(), LowerVectorFP_TO_INT(), LowerVectorINT_TO_FP(), LowerVectorIntUnary(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBlendOfPSHUFBs(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsPermuteAndUnpack(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleToEXPAND(), lowerVectorShuffleWithPERMV(), lowerVectorShuffleWithPSHUFB(), lowerVectorShuffleWithUndefHalf(), lowerVSELECTtoVectorShuffle(), lowerX86FPLogicOp(), LowerZERO_EXTEND_Mask(), matchBinaryPermuteVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), matchVectorShuffleAsShift(), matchVectorShuffleWithPACK(), mayTailCallThisCC(), memVTFromAggregate(), llvm::MipsTargetLowering::MipsTargetLowering(), NarrowVector(), performConcatVectorsCombine(), performExtendCombine(), recoverFramePointer(), reduceVMULWidth(), reorderSubVector(), llvm::X86TargetLowering::ReplaceNodeResults(), scaleVectorType(), llvm::TargetLoweringBase::setJumpIsExpensive(), llvm::HexagonTargetLowering::shouldExpandAtomicRMWInIR(), skipExtensionForVectorMULL(), SkipExtensionForVMULL(), split256IntArith(), split512IntArith(), splitAndLowerVectorShuffle(), tryBuildVectorReplicate(), tryExtendDUPToExtractHigh(), and WidenVector().

◆ getVectorVT() [2/3]

Definition at line 972 of file MachineValueType.h.

References getScalableVectorVT(), and getVectorVT().

◆ getVectorVT() [3/3]

|

inlinestatic |

Definition at line 978 of file MachineValueType.h.

References assert(), getScalableVectorVT(), getVectorVT(), getVT(), MAX_ALLOWED_VALUETYPE, llvm::MVT::ElementCount::Min, operator!=(), llvm::MVT::ElementCount::operator*(), and llvm::MVT::ElementCount::Scalable.

◆ getVT()

Return the value type corresponding to the specified type.

This returns all pointers as iPTR. If HandleUnknown is true, unknown types are returned as Other, otherwise they are invalid.

This returns all pointers as MVT::iPTR. If HandleUnknown is true, unknown types are returned as Other, otherwise they are invalid.

Definition at line 281 of file ValueTypes.cpp.

References llvm::Type::DoubleTyID, f128, f16, f32, f64, f80, llvm::Type::FloatTyID, llvm::Type::FP128TyID, getBitWidth(), llvm::SequentialType::getElementType(), llvm::EVT::getIntegerVT(), llvm::SequentialType::getNumElements(), llvm::Type::getTypeID(), llvm::EVT::getVectorVT(), llvm::Type::HalfTyID, llvm::Type::IntegerTyID, iPTR, isVoid, llvm_unreachable, Other, llvm::Type::PointerTyID, llvm::Type::PPC_FP128TyID, ppcf128, llvm::Type::VectorTyID, llvm::Type::VoidTyID, llvm::Type::X86_FP80TyID, llvm::Type::X86_MMXTyID, and x86mmx.

Referenced by concatSubVector(), getConvRTLibDesc(), llvm::EVT::getEVT(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX512(), llvm::RISCVTargetLowering::getTgtMemIntrinsic(), llvm::HexagonTargetLowering::getTgtMemIntrinsic(), llvm::SITargetLowering::getTgtMemIntrinsic(), llvm::AArch64TargetLowering::getTgtMemIntrinsic(), llvm::ARMTargetLowering::getTgtMemIntrinsic(), llvm::X86TargetLowering::getTgtMemIntrinsic(), getVectorVT(), llvm::CallLowering::handleAssignments(), memVTFromAggregate(), and llvm::TargetLowering::ParseConstraints().

◆ integer_scalable_vector_valuetypes()

|

inlinestatic |

Definition at line 1044 of file MachineValueType.h.

References FIRST_INTEGER_SCALABLE_VALUETYPE, and LAST_INTEGER_SCALABLE_VALUETYPE.

◆ integer_valuetypes()

|

inlinestatic |

Definition at line 1017 of file MachineValueType.h.

References FIRST_INTEGER_VALUETYPE, and LAST_INTEGER_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::AVRTargetLowering::AVRTargetLowering(), llvm::BPFTargetLowering::BPFTargetLowering(), combineStore(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::LanaiTargetLowering::LanaiTargetLowering(), LowerLoad(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), PerformSTORECombine(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::WebAssemblyTargetLowering::WebAssemblyTargetLowering(), llvm::X86TargetLowering::X86TargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

◆ integer_vector_valuetypes()

|

inlinestatic |

Definition at line 1032 of file MachineValueType.h.

References FIRST_INTEGER_VECTOR_VALUETYPE, and LAST_INTEGER_VECTOR_VALUETYPE.

Referenced by llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::WebAssemblyTargetLowering::WebAssemblyTargetLowering(), and llvm::X86TargetLowering::X86TargetLowering().

◆ is1024BitVector()

|

inline |

Return true if this is a 1024-bit vector type.

Definition at line 375 of file MachineValueType.h.

References v1024i1, v128i8, v16i64, v32i32, and v64i16.

Referenced by llvm::EVT::is1024BitVector().

◆ is128BitVector()

|

inline |

Return true if this is a 128-bit vector type.

Definition at line 351 of file MachineValueType.h.

References v128i1, v16i8, v1i128, v2f64, v2i64, v4f32, v4i32, v8f16, and v8i16.

Referenced by CallingConvSupported(), combineExtractSubvector(), combineVectorSignBitsTruncation(), combineX86ShuffleChain(), computeBytesPoppedByCalleeForSRet(), ExtractBitFromMaskVector(), getCompareCC(), getZeroVector(), InsertBitToMaskVector(), llvm::EVT::is128BitVector(), isHorizontalBinOp(), LowerBITREVERSE_XOP(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerBuildVectorv4x32(), LowerEXTEND_VECTOR_INREG(), LowerEXTRACT_VECTOR_ELT_SSE4(), LowerRotate(), LowerSCALAR_TO_VECTOR(), LowerTruncateVecI1(), LowerVectorCTPOP(), lowerVectorShuffle(), lowerVectorShuffleAsBlend(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsPermuteAndUnpack(), lowerVectorShuffleAsRotate(), lowerVectorShuffleAsSpecificZeroOrAnyExtend(), lowerVectorShuffleWithPSHUFB(), LowerVSETCC(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), matchVectorShuffleAsInsertPS(), performAddSubLongCombine(), llvm::X86TargetLowering::SimplifyDemandedVectorEltsForTargetNode(), SupportedVectorShiftWithImm(), and SupportedVectorVarShift().

◆ is16BitVector()

|

inline |

Return true if this is a 16-bit vector type.

Definition at line 330 of file MachineValueType.h.

References v16i1, v1i16, and v2i8.

Referenced by llvm::EVT::is16BitVector().

◆ is2048BitVector()

|

inline |

Return true if this is a 2048-bit vector type.

Definition at line 382 of file MachineValueType.h.

References v128i16, v256i8, v32i64, and v64i32.

Referenced by llvm::EVT::is2048BitVector().

◆ is256BitVector()

|

inline |

Return true if this is a 256-bit vector type.

Definition at line 360 of file MachineValueType.h.

References v16i16, v32i8, v4f64, v4i64, v8f32, and v8i32.

Referenced by llvm::CC_X86_VectorCallGetSSEs(), combineLogicBlendIntoPBLENDV(), combineVectorSignBitsTruncation(), combineX86ShuffleChain(), computeBytesPoppedByCalleeForSRet(), ExpandHorizontalBinOp(), ExtractBitFromMaskVector(), getZeroVector(), InsertBitToMaskVector(), llvm::EVT::is256BitVector(), isHopBuildVector(), isHorizontalBinOp(), Lower256IntUnary(), Lower256IntVSETCC(), LowerABS(), LowerADDSAT_SUBSAT(), lowerAddSub(), LowerAVXCONCAT_VECTORS(), LowerBITREVERSE(), LowerBITREVERSE_XOP(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerCONCAT_VECTORS(), LowerCTTZ(), LowerEXTEND_VECTOR_INREG(), LowerMINMAX(), LowerMUL(), LowerMULH(), LowerRotate(), LowerShift(), lowerShuffleAsRepeatedMaskAndLanePermute(), LowerToHorizontalOp(), LowerTruncateVecI1(), LowerVectorCTLZ(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTPOP(), lowerVectorShuffle(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleAsLanePermuteAndBlend(), lowerVectorShuffleAsRotate(), lowerVectorShuffleWithPSHUFB(), lowerVectorShuffleWithUndefHalf(), LowerVSETCC(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), split256IntArith(), SupportedVectorShiftWithImm(), and SupportedVectorVarShift().

◆ is32BitVector()

|

inline |

Return true if this is a 32-bit vector type.

Definition at line 336 of file MachineValueType.h.

References v1f32, v1i32, v2f16, v2i16, v32i1, and v4i8.

Referenced by llvm::EVT::is32BitVector().

◆ is512BitVector()

|

inline |

Return true if this is a 512-bit vector type.

Definition at line 367 of file MachineValueType.h.

References v16f32, v16i32, v32i16, v512i1, v64i8, v8f64, and v8i64.

Referenced by llvm::CC_X86_VectorCallGetSSEs(), combineShuffleToAddSubOrFMAddSub(), combineX86ShuffleChain(), computeBytesPoppedByCalleeForSRet(), ExtractBitFromMaskVector(), llvm::X86TargetLowering::getSetCCResultType(), getZeroVector(), InsertBitToMaskVector(), llvm::EVT::is512BitVector(), Lower512IntUnary(), LowerAVXCONCAT_VECTORS(), LowerBITREVERSE(), LowerBUILD_VECTORAsVariablePermute(), lowerBuildVectorAsBroadcast(), LowerCONCAT_VECTORS(), LowerEXTEND_VECTOR_INREG(), LowerMGATHER(), LowerMSCATTER(), LowerMSTORE(), LowerScalarImmediateShift(), LowerShift(), LowerSIGN_EXTEND_Mask(), lowerToAddSubOrFMAddSub(), lowerV4X128VectorShuffle(), LowerVectorCTLZ(), LowerVectorCTLZ_AVX512CDI(), LowerVectorCTPOP(), lowerVectorShuffle(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsByteRotate(), lowerVectorShuffleAsByteRotateAndPermute(), lowerVectorShuffleWithPSHUFB(), lowerVectorShuffleWithUndefHalf(), lowerVectorShuffleWithVPMOV(), LowerZERO_EXTEND_Mask(), matchBinaryPermuteVectorShuffle(), matchBinaryVectorShuffle(), matchUnaryPermuteVectorShuffle(), matchUnaryVectorShuffle(), split512IntArith(), and SupportedVectorShiftWithImm().

◆ is64BitVector()

|

inline |

Return true if this is a 64-bit vector type.

Definition at line 343 of file MachineValueType.h.

References v1f64, v1i64, v2f32, v2i32, v4f16, v4i16, v64i1, and v8i8.

Referenced by getCompareCC(), llvm::EVT::is64BitVector(), and tryExtendDUPToExtractHigh().

◆ isFloatingPoint()

|

inline |

Return true if this is a FP or a vector FP type.

Definition at line 293 of file MachineValueType.h.

References FIRST_FP_VALUETYPE, FIRST_FP_VECTOR_VALUETYPE, LAST_FP_VALUETYPE, and LAST_FP_VECTOR_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::AMDGPUTargetLowering::analyzeFormalArgumentsCompute(), CC_MipsO32(), llvm::CC_X86_32_VectorCall(), llvm::CC_X86_64_VectorCall(), combineMOVMSK(), combineX86ShuffleChain(), combineX86ShufflesConstants(), EltsFromConsecutiveLoads(), EmitKORTEST(), getCompareCC(), getConstantVector(), getCopyFromParts(), getCopyToParts(), llvm::TargetLoweringBase::getTypeToPromoteTo(), getVCmpInst(), isAddSubOrSubAdd(), llvm::EVT::isFloatingPoint(), isTruncWithZeroHighBitsInput(), lowerAddSubToHorizontalOp(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBUILD_VECTORAsVariablePermute(), lowerVectorShuffle(), lowerVectorShuffleAsBitMask(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsElementInsertion(), lowerVectorShuffleAsLanePermuteAndBlend(), lowerVectorShuffleAsPermuteAndUnpack(), LowerVSETCC(), matchBinaryPermuteVectorShuffle(), pickOpcodeForVT(), PrepareCall(), setTargetShuffleZeroElements(), and UnpackFromArgumentSlot().

◆ isInteger()

|

inline |

Return true if this is an integer or a vector integer type.

Definition at line 301 of file MachineValueType.h.

References FIRST_INTEGER_VALUETYPE, FIRST_INTEGER_VECTOR_VALUETYPE, LAST_INTEGER_VALUETYPE, and LAST_INTEGER_VECTOR_VALUETYPE.

Referenced by llvm::AMDGPUTargetLowering::analyzeFormalArgumentsCompute(), CC_MipsO32_FP64(), computeBytesPoppedByCalleeForSRet(), EmitKORTEST(), getCopyFromParts(), llvm::RegsForValue::getCopyFromRegs(), getCopyToParts(), getPromotedVectorElementType(), GetRegistersForValue(), getShuffleScalarElt(), llvm::TargetLoweringBase::getTypeToPromoteTo(), InsertBitToMaskVector(), llvm::EVT::isInteger(), isValueTypeInRegForCC(), lower256BitVectorShuffle(), Lower256IntUnary(), Lower512IntUnary(), LowerABS(), LowerADDSAT_SUBSAT(), lowerAddSub(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerFPToInt(), LowerLoad(), LowerSETCCCARRY(), LowerStore(), lowerVectorShuffleAsBitBlend(), lowerVectorShuffleAsBroadcast(), lowerVectorShuffleAsTruncBroadcast(), matchUnaryVectorShuffle(), llvm::TargetLowering::ParseConstraints(), llvm::X86TargetLowering::ReplaceNodeResults(), split256IntArith(), and split512IntArith().

◆ isOverloaded()

|

inline |

◆ isPow2VectorType()

|

inline |

Returns true if the given vector is a power of 2.

Definition at line 395 of file MachineValueType.h.

References getVectorNumElements().

Referenced by getPow2VectorType().

◆ isScalableVector()

|

inline |

Return true if this is a vector value type where the runtime length is machine dependent.

Definition at line 322 of file MachineValueType.h.

References FIRST_FP_SCALABLE_VALUETYPE, FIRST_INTEGER_SCALABLE_VALUETYPE, LAST_FP_SCALABLE_VALUETYPE, and LAST_INTEGER_SCALABLE_VALUETYPE.

Referenced by getVectorElementCount(), and llvm::EVT::isScalableVector().

◆ isScalarInteger()

|

inline |

Return true if this is an integer, not including vectors.

Definition at line 309 of file MachineValueType.h.

References FIRST_INTEGER_VALUETYPE, and LAST_INTEGER_VALUETYPE.

Referenced by hasBZHI(), llvm::EVT::isScalarInteger(), LowerBITCAST(), and llvm::HexagonTargetLowering::LowerSETCC().

◆ isValid()

|

inline |

Return true if this is a valid simple valuetype.

Definition at line 287 of file MachineValueType.h.

References FIRST_VALUETYPE, and LAST_VALUETYPE.

Referenced by llvm::TargetLoweringBase::getIndexedLoadAction(), llvm::TargetLoweringBase::getIndexedStoreAction(), llvm::LLT::LLT(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::TargetLoweringBase::setCondCodeAction(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setLoadExtAction(), and llvm::TargetLoweringBase::setTruncStoreAction().

◆ isVector()

|

inline |

Return true if this is a vector value type.

Definition at line 315 of file MachineValueType.h.

References FIRST_VECTOR_VALUETYPE, and LAST_VECTOR_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::PPCTargetLowering::allowsMisalignedMemoryAccesses(), llvm::AMDGPUTargetLowering::analyzeFormalArgumentsCompute(), CC_MipsO32_FP64(), llvm::CC_X86_32_VectorCall(), llvm::CC_X86_64_VectorCall(), combineAndnp(), combineX86ShufflesRecursively(), computeBytesPoppedByCalleeForSRet(), convertLocVTToValVT(), convertValVTToLocVT(), EmitKORTEST(), getCompareCC(), getComparePred(), getCopyFromParts(), getCopyToPartsVector(), llvm::X86TTIImpl::getInterleavedMemoryOpCostAVX2(), getMemCmpLoad(), getPromotedVectorElementType(), getScalarType(), getScalarValueForVectorElement(), llvm::X86TargetLowering::getSetCCResultType(), llvm::X86TTIImpl::getShuffleCost(), isCalleeLoad(), llvm::HexagonSubtarget::isHVXVectorType(), isMulPowOf2(), isSExtLoad(), isTruncWithZeroHighBitsInput(), isValueTypeInRegForCC(), llvm::EVT::isVector(), llvm::LLT::LLT(), LowerAVXExtend(), llvm::HexagonTargetLowering::LowerBITCAST(), LowerBITCAST(), LowerBITREVERSE_XOP(), LowerCTLZ(), LowerCTPOP(), LowerCTTZ(), LowerFABSorFNEG(), LowerFCOPYSIGN(), LowerFPToInt(), LowerFunnelShift(), LowerI64IntToFP_AVX512DQ(), LowerLoad(), lowerRegToMasks(), LowerRotate(), llvm::HexagonTargetLowering::LowerSETCC(), LowerShift(), LowerSIGN_EXTEND(), llvm::AMDGPUTargetLowering::LowerSIGN_EXTEND_INREG(), LowerStore(), LowerTruncateVecI1(), lowerUINT_TO_FP_vec(), lowerVectorShuffleAsBroadcast(), lowerX86FPLogicOp(), parseTexFail(), performConcatVectorsCombine(), pickOpcodeForVT(), processShaderInputArgs(), llvm::X86TargetLowering::ReplaceNodeResults(), llvm::HexagonTargetLowering::shouldExpandAtomicRMWInIR(), shouldGuaranteeTCO(), llvm::X86TargetLowering::SimplifyDemandedVectorEltsForTargetNode(), UnrollVectorShift(), and VerifyVectorType().

◆ operator!=()

Definition at line 282 of file MachineValueType.h.

References SimpleTy.

Referenced by getVectorVT().

◆ operator<()

Definition at line 280 of file MachineValueType.h.

References SimpleTy.

◆ operator<=()

Definition at line 284 of file MachineValueType.h.

References SimpleTy.

◆ operator==()

Definition at line 281 of file MachineValueType.h.

References SimpleTy.

◆ operator>()

Definition at line 279 of file MachineValueType.h.

References SimpleTy.

◆ operator>=()

Definition at line 283 of file MachineValueType.h.

References SimpleTy.

◆ vector_valuetypes()

|

inlinestatic |

Definition at line 1027 of file MachineValueType.h.

References FIRST_VECTOR_VALUETYPE, and LAST_VECTOR_VALUETYPE.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::WebAssemblyTargetLowering::WebAssemblyTargetLowering(), and llvm::X86TargetLowering::X86TargetLowering().

Member Data Documentation

◆ SimpleTy

| SimpleValueType llvm::MVT::SimpleTy = INVALID_SIMPLE_VALUE_TYPE |

Definition at line 239 of file MachineValueType.h.

Referenced by AddCombineBUILD_VECTORToVPADDL(), llvm::TargetLoweringBase::AddPromotedToType(), llvm::TargetLoweringBase::addRegisterClass(), allocateSGPRTuple(), allocateVGPRTuple(), llvm::MipsSETargetLowering::allowsMisalignedMemoryAccesses(), llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses(), AnalyzeReturnValues(), llvm::CC_ARM_AAPCS_Custom_Aggregate(), CC_Lanai32_VarArg(), CC_MipsO32_FP64(), llvm::EVT::changeVectorElementTypeToInteger(), checkV64LaneV128(), combineBitcastvxi1(), computeBytesPoppedByCalleeForSRet(), createVariablePermute(), llvm::SITargetLowering::denormalsEnabledForType(), EnsureStackAlignment(), llvm::SelectionDAG::EVTToAPFloatSemantics(), ExpandBVWithShuffles(), FindOptimalMemOpLowering(), llvm::ARMTargetLowering::findRepresentativeClass(), llvm::X86TargetLowering::findRepresentativeClass(), llvm::TargetLoweringBase::findRepresentativeClass(), foldVectorXorShiftIntoCmp(), getAL(), llvm::R600RegisterInfo::getCFGStructurizerRegClass(), getCompareCC(), getComparePred(), llvm::TargetLoweringBase::getCondCodeAction(), getContiguousRangeOfSetBits(), getDivRemArgList(), llvm::EVT::getEVTString(), getExtensionTo64Bits(), GetFPLibCall(), getImplicitScaleFactor(), llvm::TargetLoweringBase::getIndexedLoadAction(), llvm::TargetLoweringBase::getIndexedStoreAction(), llvm::EVT::getIntegerVT(), llvm::TargetLoweringBase::getLoadExtAction(), getLog2EVal(), llvm::TargetLoweringBase::getNumRegisters(), llvm::TargetLoweringBase::getOperationAction(), llvm::EVT::getRawBits(), llvm::TargetLoweringBase::getRegClassFor(), llvm::HexagonTargetLowering::getRegForInlineAsmConstraint(), llvm::SITargetLowering::getRegForInlineAsmConstraint(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::TargetLoweringBase::getRegisterType(), llvm::TargetLoweringBase::getRepRegClassCostFor(), llvm::TargetLoweringBase::getRepRegClassFor(), getScalableVectorVT(), llvm::AVRTargetLowering::getSetCCResultType(), llvm::TargetLoweringBase::getSetCCResultType(), llvm::TargetLoweringBase::getTruncStoreAction(), llvm::TargetLoweringBase::ValueTypeActionImpl::getTypeAction(), llvm::EVT::getTypeForEVT(), llvm::TargetLoweringBase::getTypeToPromoteTo(), llvm::SelectionDAG::getValueType(), llvm::EVT::getVectorVT(), getVectorVT(), is32Bit(), llvm::SITargetLowering::isFMAFasterThanFMulAndFAdd(), llvm::AArch64TargetLowering::isFMAFasterThanFMulAndFAdd(), llvm::SystemZTargetLowering::isFMAFasterThanFMulAndFAdd(), llvm::PPCTargetLowering::isFMAFasterThanFMulAndFAdd(), llvm::X86TargetLowering::isFMAFasterThanFMulAndFAdd(), llvm::ARMTargetLowering::isFNegFree(), llvm::PPCTargetLowering::isFPImmLegal(), isLegalAddressImmediate(), llvm::ARMTargetLowering::isLegalAddressingMode(), isLegalT1AddressImmediate(), isLegalT2AddressImmediate(), llvm::ARMTargetLowering::isLegalT2ScaledAddressingMode(), isMulPowOf2(), isNEONModifiedImm(), isOpcWithIntImmediate(), isPerfectIncrement(), IsPTXVectorType(), isSExtLoad(), llvm::EVT::isSimple(), isSinCosLibcallAvailable(), llvm::TargetLoweringBase::isTypeLegal(), llvm::HexagonInstrInfo::isValidAutoIncImm(), isValidIndexedLoad(), llvm::XCoreTargetLowering::isZExtFree(), llvm::ARMTargetLowering::isZExtFree(), llvm::X86TargetLowering::isZExtFree(), lower128BitVectorShuffle(), lower1BitVectorShuffle(), lower256BitVectorShuffle(), lower512BitVectorShuffle(), lowerCallResult(), LowerCallResult(), LowerCMP_SWAP(), llvm::SystemZTargetLowering::LowerFormalArguments(), llvm::BPFTargetLowering::LowerOperation(), lowerRegToMasks(), lowerUINT_TO_FP_vec(), lowerVectorShuffleAsBlend(), lowerVSELECTtoVectorShuffle(), llvm::EVT::operator!=(), operator!=(), llvm::EVT::compareRawBits::operator()(), operator<(), operator<=(), operator==(), operator>(), operator>=(), pickOpcodeForVT(), PrepareCall(), ReplaceINTRINSIC_W_CHAIN(), ReplaceLoadVector(), llvm::AVRDAGToDAGISel::selectIndexedLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedLoad(), llvm::AVRDAGToDAGISel::selectIndexedProgMemLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedStore(), llvm::NVPTXDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::TargetLoweringBase::setCondCodeAction(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setJumpIsExpensive(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::TargetLoweringBase::ValueTypeActionImpl::setTypeAction(), llvm::X86InstrInfo::shouldScheduleLoadsNear(), ShrinkLoadReplaceStoreWithStore(), llvm::WebAssembly::toValType(), usePartialVectorLoads(), useSinCos(), VerifySDNode(), X86ChooseCmpImmediateOpcode(), and X86ChooseCmpOpcode().

The documentation for this class was generated from the following files:

- include/llvm/Support/MachineValueType.h

- lib/CodeGen/ValueTypes.cpp

1.8.13

1.8.13