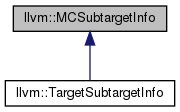

Generic base class for all target subtargets. More...

#include "llvm/MC/MCSubtargetInfo.h"

Protected Member Functions | |

| void | InitMCProcessorInfo (StringRef CPU, StringRef FS) |

| Initialize the scheduling model and feature bits. More... | |

Detailed Description

Generic base class for all target subtargets.

Definition at line 36 of file MCSubtargetInfo.h.

Constructor & Destructor Documentation

◆ MCSubtargetInfo() [1/3]

|

default |

◆ MCSubtargetInfo() [2/3]

| MCSubtargetInfo::MCSubtargetInfo | ( | const Triple & | TT, |

| StringRef | CPU, | ||

| StringRef | FS, | ||

| ArrayRef< SubtargetFeatureKV > | PF, | ||

| ArrayRef< SubtargetFeatureKV > | PD, | ||

| const SubtargetInfoKV * | ProcSched, | ||

| const MCWriteProcResEntry * | WPR, | ||

| const MCWriteLatencyEntry * | WL, | ||

| const MCReadAdvanceEntry * | RA, | ||

| const InstrStage * | IS, | ||

| const unsigned * | OC, | ||

| const unsigned * | FP | ||

| ) |

Definition at line 42 of file MCSubtargetInfo.cpp.

References InitMCProcessorInfo().

◆ MCSubtargetInfo() [3/3]

|

delete |

◆ ~MCSubtargetInfo()

|

virtualdefault |

Member Function Documentation

◆ ApplyFeatureFlag()

| FeatureBitset MCSubtargetInfo::ApplyFeatureFlag | ( | StringRef | FS | ) |

Apply a feature flag and return the re-computed feature bits, including all feature bits implied by the flag.

Definition at line 69 of file MCSubtargetInfo.cpp.

References llvm::SubtargetFeatures::ApplyFeatureFlag().

Referenced by hasFeature(), and llvm::IsCPSRDead< MCInst >().

◆ checkFeatures()

Check whether the subtarget features are enabled/disabled as per the provided string, ignoring all other features.

Definition at line 74 of file MCSubtargetInfo.cpp.

References llvm::SubtargetFeatures::ApplyFeatureFlag(), F(), llvm::SubtargetFeatures::getFeatures(), and T.

Referenced by hasFeature().

◆ getCPU()

|

inline |

Definition at line 69 of file MCSubtargetInfo.h.

Referenced by llvm::AMDGPUTargetELFStreamer::AMDGPUTargetELFStreamer(), llvm::createHexagonAsmBackend(), llvm::createMipsAsmBackend(), llvm::AMDGPUTargetAsmStreamer::EmitAmdhsaKernelDescriptor(), llvm::ARMTargetStreamer::emitTargetAttributes(), llvm::AMDGPU::IsaInfo::getAddressableNumSGPRs(), getArchForCPU(), llvm::Hexagon_MC::GetELFFlags(), llvm::AMDGPU::IsaInfo::getMaxNumSGPRs(), llvm::AMDGPU::IsaInfo::getNumExtraSGPRs(), llvm::AMDGPU::IsaInfo::getSGPRAllocGranule(), llvm::AMDGPU::IsaInfo::getTotalNumSGPRs(), llvm::HexagonShuffler::HexagonShuffler(), llvm::AMDGPU::initDefaultAMDKernelCodeT(), llvm::HexagonMCInstrInfo::isOrderedDuplexPair(), llvm::AMDGPUInstPrinter::printWaitFlag(), and llvm::AMDGPU::IsaInfo::streamIsaVersion().

◆ getFeatureBits()

|

inline |

Definition at line 71 of file MCSubtargetInfo.h.

Referenced by llvm::ARMAsmBackend::adjustFixupValue(), llvm::AArch64TTIImpl::areInlineCompatible(), llvm::ARMTTIImpl::areInlineCompatible(), llvm::X86TTIImpl::areInlineCompatible(), llvm::GCNTTIImpl::areInlineCompatible(), llvm::AVRELFStreamer::AVRELFStreamer(), llvm::HexagonMCInstrInfo::canonicalizePacket(), checkFeature(), clearFeature(), llvm::AMDGPUDisassembler::convertSDWAInst(), llvm::Hexagon_MC::createHexagonMCSubtargetInfo(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), llvm::CreateX86AsmInstrumentation(), DecodeHINTInstruction(), llvm::AMDGPUDisassembler::decodeSDWASrc(), llvm::AMDGPUDisassembler::decodeSDWAVopcDst(), DecodeSETPANInstruction(), DecodeSystemPStateInstruction(), llvm::MipsTargetStreamer::emitNop(), llvm::HexagonMCCodeEmitter::encodeInstruction(), llvm::PPCMCCodeEmitter::encodeInstruction(), ExpandCryptoAEK(), llvm::MipsTargetELFStreamer::finish(), llvm::AMDGPU::IsaInfo::getAddressableNumSGPRs(), getARMLoadDeprecationInfo(), getARMStoreDeprecationInfo(), llvm::MCInstrDesc::getDeprecatedInfo(), llvm::AMDGPUDisassembler::getInstruction(), getITDeprecationInfo(), getLit16Encoding(), getLit32Encoding(), getLit64Encoding(), llvm::AMDGPU::IsaInfo::getLocalMemorySize(), llvm::AMDGPU::IsaInfo::getMaxNumSGPRs(), llvm::AMDGPU::IsaInfo::getMaxWorkGroupsPerCU(), getMCRDeprecationInfo(), llvm::AMDGPU::IsaInfo::getMinNumSGPRs(), llvm::AMDGPU::IsaInfo::getNumExtraSGPRs(), llvm::ARMAsmBackend::getRelaxedOpcode(), getRelaxedOpcode(), llvm::AMDGPU::IsaInfo::getWavefrontSize(), llvm::AMDGPU::IsaInfo::hasCodeObjectV3(), llvm::AMDGPU::hasMIMG_R128(), llvm::ARMAsmBackend::hasNOP(), llvm::AMDGPU::hasPackedD16(), llvm::AMDGPU::hasSRAMECC(), llvm::AMDGPU::hasXNACK(), incrementLoc(), llvm::AMDGPU::isCI(), llvm::IsCPSRDead< MCInst >(), llvm::AMDGPU::isGCN3Encoding(), llvm::AMDGPUDisassembler::isGFX9(), llvm::AMDGPU::isGFX9(), llvm::AMDGPU::isSI(), IsSmallMemAccess(), isThumb(), llvm::SparcInstPrinter::isV9(), llvm::AMDGPUDisassembler::isVI(), llvm::AMDGPU::isVI(), LowerLargeShift(), llvm::MipsTargetELFStreamer::MipsTargetELFStreamer(), llvm::RISCVInstPrinter::printCSRSystemRegister(), llvm::X86ATTInstPrinter::printInst(), llvm::X86IntelInstPrinter::printInst(), llvm::PPCInstPrinter::printInst(), llvm::ARMInstPrinter::printMemBOption(), llvm::AArch64InstPrinter::printMRSSystemRegister(), llvm::ARMInstPrinter::printMSRMaskOperand(), llvm::AArch64InstPrinter::printMSRSystemRegister(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::AArch64InstPrinter::printSysAlias(), llvm::AArch64InstPrinter::printSystemPStateField(), llvm::RISCVAsmBackend::requiresDiffExpressionRelocations(), llvm::RISCVTargetELFStreamer::RISCVTargetELFStreamer(), llvm::RISCVAsmBackend::shouldForceRelocation(), SwapBits(), and llvm::RISCVAsmBackend::writeNopData().

◆ getInstrItineraryForCPU()

| InstrItineraryData MCSubtargetInfo::getInstrItineraryForCPU | ( | StringRef | CPU | ) | const |

Get scheduling itinerary of a CPU.

Definition at line 112 of file MCSubtargetInfo.cpp.

References getSchedModelForCPU().

Referenced by getItineraryLatency(), and getReadAdvanceCycles().

◆ getReadAdvanceCycles()

|

inline |

Definition at line 137 of file MCSubtargetInfo.h.

References E, getInstrItineraryForCPU(), I, initInstrItins(), llvm::MCSchedClassDesc::NumReadAdvanceEntries, and llvm::MCSchedClassDesc::ReadAdvanceIdx.

Referenced by llvm::TargetSchedModel::computeOperandLatency().

◆ getSchedInfoStr()

|

inlinevirtual |

Returns string representation of scheduler comment.

Reimplemented in llvm::TargetSubtargetInfo.

Definition at line 176 of file MCSubtargetInfo.h.

Referenced by PrintCFIEscape().

◆ getSchedModel()

|

inline |

Get the machine model for this subtarget's CPU.

Definition at line 116 of file MCSubtargetInfo.h.

Referenced by adjCycles(), llvm::mca::Context::createDefaultPipeline(), llvm::mca::InstrBuilder::createInstruction(), llvm::TargetSubtargetInfo::enablePostRAScheduler(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getInstructionLatency(), getLatency(), llvm::HexagonMCInstrInfo::getOtherReservedSlots(), llvm::MCSchedModel::getReciprocalThroughput(), llvm::HexagonMCInstrInfo::getUnits(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getUnrollingPreferences(), llvm::TargetSchedModel::init(), llvm::ConvergingVLIWScheduler::initialize(), llvm::mca::initializeUsedResources(), initInstrItins(), llvm::mca::InstrBuilder::InstrBuilder(), and llvm::mca::verifyOperands().

◆ getSchedModelForCPU()

| const MCSchedModel & MCSubtargetInfo::getSchedModelForCPU | ( | StringRef | CPU | ) | const |

Get the machine model of a CPU.

Definition at line 86 of file MCSubtargetInfo.cpp.

References assert(), llvm::errs(), llvm::MCSchedModel::GetDefaultSchedModel(), llvm::SubtargetInfoKV::Key, and llvm::lower_bound().

Referenced by getInstrItineraryForCPU(), hasFeature(), and InitMCProcessorInfo().

◆ getTargetTriple()

Definition at line 68 of file MCSubtargetInfo.h.

Referenced by llvm::ARMAsmBackend::adjustFixupValue(), llvm::createAArch64beAsmBackend(), llvm::createAArch64leAsmBackend(), llvm::createAArch64ObjectTargetStreamer(), llvm::createAMDGPUAsmBackend(), createARMAsmBackend(), llvm::createARMObjectTargetStreamer(), createAsmBackend(), llvm::createAVRAsmBackend(), llvm::createHexagonAsmBackend(), llvm::createLanaiAsmBackend(), llvm::createMipsAsmBackend(), llvm::createMSP430ObjectTargetStreamer(), createObjectTargetStreamer(), llvm::createPPCAsmBackend(), llvm::createRISCVAsmBackend(), createRISCVObjectTargetStreamer(), llvm::createSparcAsmBackend(), llvm::createSystemZMCAsmBackend(), llvm::createX86_32AsmBackend(), llvm::createX86_64AsmBackend(), llvm::CreateX86AsmInstrumentation(), llvm::createX86ObjectTargetStreamer(), llvm::AsmPrinter::emitXRayTable(), llvm::AMDGPU::getMCReg(), llvm::PPCMCCodeEmitter::getTLSRegEncoding(), llvm::AMDGPU::IsaInfo::hasCodeObjectV3(), lowerMSASplatZExt(), llvm::MipsTargetELFStreamer::MipsTargetELFStreamer(), llvm::AMDGPU::IsaInfo::streamIsaVersion(), and truncateVecElts().

◆ getWriteLatencyEntry()

|

inline |

Definition at line 129 of file MCSubtargetInfo.h.

References assert(), and llvm::MCSchedClassDesc::WriteLatencyIdx.

Referenced by llvm::MCSchedModel::computeInstrLatency(), llvm::TargetSchedModel::computeOperandLatency(), getLatency(), and llvm::mca::verifyOperands().

◆ getWriteProcResBegin()

|

inline |

Return an iterator at the first process resource consumed by the given scheduling class.

Definition at line 120 of file MCSubtargetInfo.h.

References llvm::MCSchedClassDesc::WriteProcResIdx.

Referenced by llvm::TargetSchedModel::computeOutputLatency(), llvm::MCSchedModel::getReciprocalThroughput(), llvm::TargetSchedModel::getWriteProcResBegin(), getWriteProcResEnd(), and llvm::mca::initializeUsedResources().

◆ getWriteProcResEnd()

|

inline |

Definition at line 124 of file MCSubtargetInfo.h.

References getWriteProcResBegin(), and llvm::MCSchedClassDesc::NumWriteProcResEntries.

Referenced by llvm::TargetSchedModel::computeOutputLatency(), llvm::MCSchedModel::getReciprocalThroughput(), and llvm::TargetSchedModel::getWriteProcResEnd().

◆ hasFeature()

Definition at line 76 of file MCSubtargetInfo.h.

References ApplyFeatureFlag(), checkFeatures(), getSchedModelForCPU(), InitMCProcessorInfo(), setDefaultFeatures(), and ToggleFeature().

Referenced by llvm::ARMTargetStreamer::emitTargetAttributes(), getArchForCPU(), llvm::ARMElfTargetObjectFile::Initialize(), isV8M(), and llvm::AMDGPUInstPrinter::printInst().

◆ initInstrItins()

| void MCSubtargetInfo::initInstrItins | ( | InstrItineraryData & | InstrItins | ) | const |

Initialize an InstrItineraryData instance.

Definition at line 117 of file MCSubtargetInfo.cpp.

References getSchedModel().

Referenced by getReadAdvanceCycles(), and llvm::TargetSchedModel::init().

◆ InitMCProcessorInfo()

Initialize the scheduling model and feature bits.

FIXME: Find a way to stick this in the constructor, since it should only be called during initialization.

Definition at line 30 of file MCSubtargetInfo.cpp.

References llvm::StringRef::empty(), llvm::MCSchedModel::GetDefaultSchedModel(), getFeatures(), and getSchedModelForCPU().

Referenced by hasFeature(), and MCSubtargetInfo().

◆ isCPUStringValid()

Check whether the CPU string is valid.

Definition at line 170 of file MCSubtargetInfo.h.

References llvm::ArrayRef< T >::begin(), llvm::ArrayRef< T >::end(), and llvm::lower_bound().

◆ operator=() [1/2]

|

delete |

◆ operator=() [2/2]

|

delete |

◆ resolveVariantSchedClass()

|

inlinevirtual |

Resolve a variant scheduling class for the given MCInst and CPU.

Definition at line 164 of file MCSubtargetInfo.h.

Referenced by llvm::MCSchedModel::computeInstrLatency(), llvm::MCSchedModel::getReciprocalThroughput(), and llvm::mca::verifyOperands().

◆ setDefaultFeatures()

Set the features to the default for the given CPU with an appended feature string.

Definition at line 38 of file MCSubtargetInfo.cpp.

References getFeatures().

Referenced by ExpandCryptoAEK(), hasFeature(), incrementLoc(), and llvm::IsCPSRDead< MCInst >().

◆ setFeatureBits()

|

inline |

Definition at line 72 of file MCSubtargetInfo.h.

Referenced by llvm::Hexagon_MC::createHexagonMCSubtargetInfo(), and RefineErrorLoc().

◆ ToggleFeature() [1/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | uint64_t | FB | ) |

Toggle a feature and return the re-computed feature bits.

This version does not change the implied bits.

Definition at line 54 of file MCSubtargetInfo.cpp.

Referenced by clearFeature(), ExpandCryptoAEK(), hasFeature(), and incrementLoc().

◆ ToggleFeature() [2/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | const FeatureBitset & | FB | ) |

Toggle a feature and return the re-computed feature bits.

This version does not change the implied bits.

Definition at line 59 of file MCSubtargetInfo.cpp.

◆ ToggleFeature() [3/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | StringRef | FS | ) |

Toggle a set of features and return the re-computed feature bits.

This version will also change all implied bits.

Definition at line 64 of file MCSubtargetInfo.cpp.

References llvm::SubtargetFeatures::ToggleFeature().

The documentation for this class was generated from the following files:

- include/llvm/MC/MCSubtargetInfo.h

- lib/MC/MCSubtargetInfo.cpp

1.8.13

1.8.13