Machine model for scheduling, bundling, and heuristics. More...

#include "llvm/MC/MCSchedule.h"

Public Member Functions | |

| bool | hasExtraProcessorInfo () const |

| unsigned | getProcessorID () const |

| bool | hasInstrSchedModel () const |

| Does this machine model include instruction-level scheduling. More... | |

| const MCExtraProcessorInfo & | getExtraProcessorInfo () const |

| bool | isComplete () const |

| Return true if this machine model data for all instructions with a scheduling class (itinerary class or SchedRW list). More... | |

| bool | isOutOfOrder () const |

| Return true if machine supports out of order execution. More... | |

| unsigned | getNumProcResourceKinds () const |

| const MCProcResourceDesc * | getProcResource (unsigned ProcResourceIdx) const |

| const MCSchedClassDesc * | getSchedClassDesc (unsigned SchedClassIdx) const |

| int | computeInstrLatency (const MCSubtargetInfo &STI, unsigned SClass) const |

| int | computeInstrLatency (const MCSubtargetInfo &STI, const MCInstrInfo &MCII, const MCInst &Inst) const |

| double | getReciprocalThroughput (const MCSubtargetInfo &STI, const MCInstrInfo &MCII, const MCInst &Inst) const |

Static Public Member Functions | |

| static int | computeInstrLatency (const MCSubtargetInfo &STI, const MCSchedClassDesc &SCDesc) |

| Returns the latency value for the scheduling class. More... | |

| static double | getReciprocalThroughput (const MCSubtargetInfo &STI, const MCSchedClassDesc &SCDesc) |

| static double | getReciprocalThroughput (unsigned SchedClass, const InstrItineraryData &IID) |

| static const MCSchedModel & | GetDefaultSchedModel () |

| Returns the default initialized model. More... | |

Static Public Attributes | |

| static const unsigned | DefaultIssueWidth = 1 |

| static const unsigned | DefaultMicroOpBufferSize = 0 |

| static const unsigned | DefaultLoopMicroOpBufferSize = 0 |

| static const unsigned | DefaultLoadLatency = 4 |

| static const unsigned | DefaultHighLatency = 10 |

| static const unsigned | DefaultMispredictPenalty = 10 |

| static const MCSchedModel | Default |

Friends | |

| class | InstrItineraryData |

Detailed Description

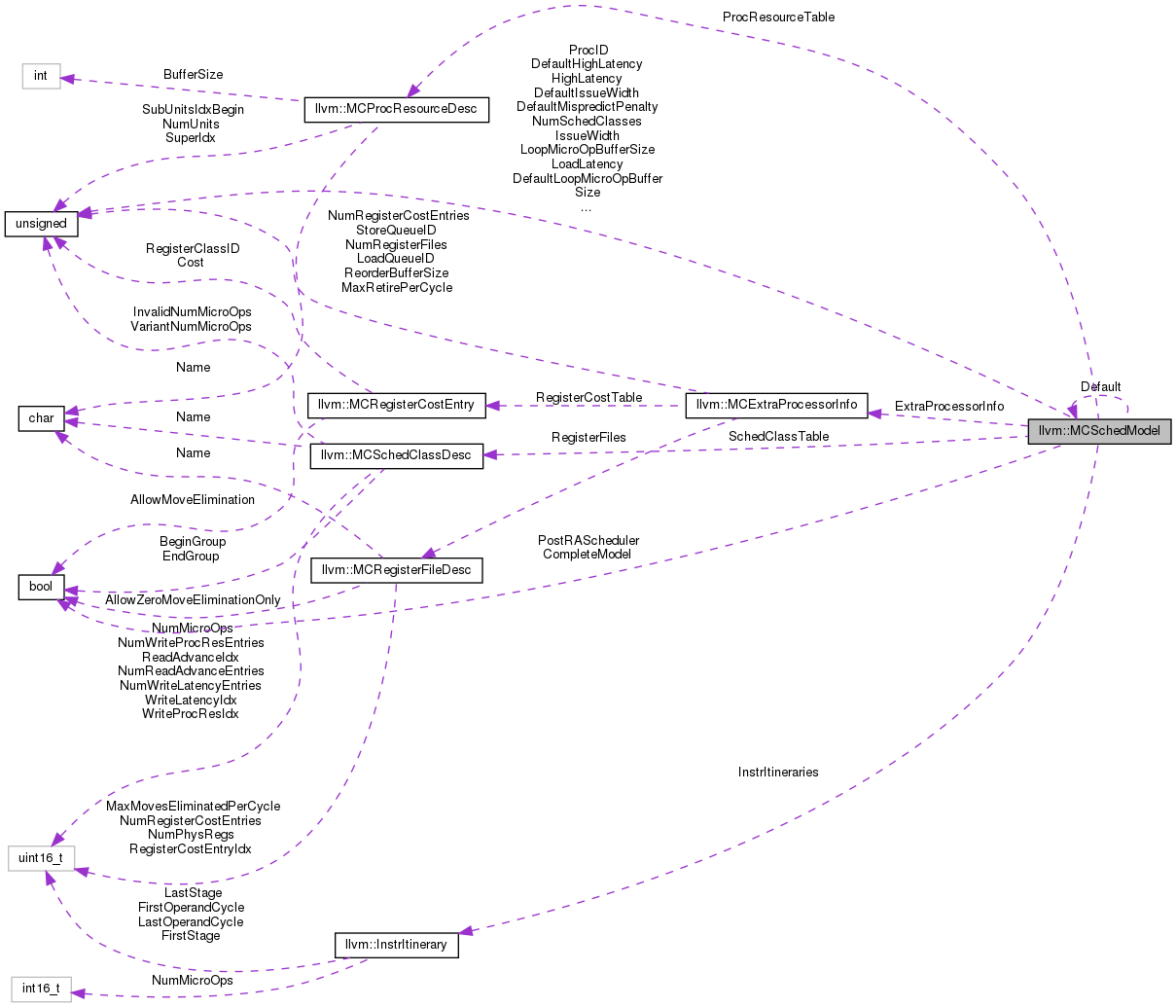

Machine model for scheduling, bundling, and heuristics.

The machine model directly provides basic information about the microarchitecture to the scheduler in the form of properties. It also optionally refers to scheduler resource tables and itinerary tables. Scheduler resource tables model the latency and cost for each instruction type. Itinerary tables are an independent mechanism that provides a detailed reservation table describing each cycle of instruction execution. Subtargets may define any or all of the above categories of data depending on the type of CPU and selected scheduler.

The machine independent properties defined here are used by the scheduler as an abstract machine model. A real micro-architecture has a number of buffers, queues, and stages. Declaring that a given machine-independent abstract property corresponds to a specific physical property across all subtargets can't be done. Nonetheless, the abstract model is useful. Futhermore, subtargets typically extend this model with processor specific resources to model any hardware features that can be exploited by sceduling heuristics and aren't sufficiently represented in the abstract.

The abstract pipeline is built around the notion of an "issue point". This is merely a reference point for counting machine cycles. The physical machine will have pipeline stages that delay execution. The scheduler does not model those delays because they are irrelevant as long as they are consistent. Inaccuracies arise when instructions have different execution delays relative to each other, in addition to their intrinsic latency. Those special cases can be handled by TableGen constructs such as, ReadAdvance, which reduces latency when reading data, and ResourceCycles, which consumes a processor resource when writing data for a number of abstract cycles.

TODO: One tool currently missing is the ability to add a delay to ResourceCycles. That would be easy to add and would likely cover all cases currently handled by the legacy itinerary tables.

A note on out-of-order execution and, more generally, instruction buffers. Part of the CPU pipeline is always in-order. The issue point, which is the point of reference for counting cycles, only makes sense as an in-order part of the pipeline. Other parts of the pipeline are sometimes falling behind and sometimes catching up. It's only interesting to model those other, decoupled parts of the pipeline if they may be predictably resource constrained in a way that the scheduler can exploit.

The LLVM machine model distinguishes between in-order constraints and out-of-order constraints so that the target's scheduling strategy can apply appropriate heuristics. For a well-balanced CPU pipeline, out-of-order resources would not typically be treated as a hard scheduling constraint. For example, in the GenericScheduler, a delay caused by limited out-of-order resources is not directly reflected in the number of cycles that the scheduler sees between issuing an instruction and its dependent instructions. In other words, out-of-order resources don't directly increase the latency between pairs of instructions. However, they can still be used to detect potential bottlenecks across a sequence of instructions and bias the scheduling heuristics appropriately.

Definition at line 244 of file MCSchedule.h.

Member Function Documentation

◆ computeInstrLatency() [1/3]

|

static |

Returns the latency value for the scheduling class.

Definition at line 41 of file MCSchedule.cpp.

References llvm::MCWriteLatencyEntry::Cycles, llvm::MCSubtargetInfo::getWriteLatencyEntry(), llvm::Latency, llvm::max(), and llvm::MCSchedClassDesc::NumWriteLatencyEntries.

Referenced by llvm::TargetSchedModel::computeInstrLatency(), computeInstrLatency(), llvm::mca::computeMaxLatency(), and llvm::TargetSchedModel::computeOperandLatency().

◆ computeInstrLatency() [2/3]

| int MCSchedModel::computeInstrLatency | ( | const MCSubtargetInfo & | STI, |

| unsigned | SClass | ||

| ) | const |

Definition at line 57 of file MCSchedule.cpp.

References computeInstrLatency(), getSchedClassDesc(), llvm::MCSchedClassDesc::isValid(), llvm::MCSchedClassDesc::isVariant(), and llvm_unreachable.

◆ computeInstrLatency() [3/3]

| int MCSchedModel::computeInstrLatency | ( | const MCSubtargetInfo & | STI, |

| const MCInstrInfo & | MCII, | ||

| const MCInst & | Inst | ||

| ) | const |

Definition at line 68 of file MCSchedule.cpp.

References computeInstrLatency(), llvm::MCInstrInfo::get(), llvm::MCInst::getOpcode(), getProcessorID(), getSchedClassDesc(), llvm::MCSchedClassDesc::isValid(), llvm::MCSchedClassDesc::isVariant(), llvm_unreachable, and llvm::MCSubtargetInfo::resolveVariantSchedClass().

◆ GetDefaultSchedModel()

|

inlinestatic |

Returns the default initialized model.

Definition at line 374 of file MCSchedule.h.

References llvm::Default.

Referenced by llvm::MCSubtargetInfo::getSchedModelForCPU(), and llvm::MCSubtargetInfo::InitMCProcessorInfo().

◆ getExtraProcessorInfo()

|

inline |

Definition at line 322 of file MCSchedule.h.

References assert().

Referenced by llvm::mca::LSUnit::LSUnit(), llvm::mca::RegisterFile::RegisterFile(), and llvm::mca::RetireControlUnit::RetireControlUnit().

◆ getNumProcResourceKinds()

|

inline |

Definition at line 335 of file MCSchedule.h.

Referenced by llvm::mca::computeBlockRThroughput(), llvm::mca::computeProcResourceMasks(), llvm::TargetSchedModel::getNumProcResourceKinds(), llvm::TargetSchedModel::init(), llvm::mca::initializeUsedResources(), llvm::mca::InstrBuilder::InstrBuilder(), and llvm::mca::ResourceManager::ResourceManager().

◆ getProcessorID()

|

inline |

Definition at line 317 of file MCSchedule.h.

Referenced by computeInstrLatency(), llvm::mca::InstrBuilder::createInstruction(), llvm::TargetSchedModel::getProcessorID(), getReciprocalThroughput(), and llvm::mca::verifyOperands().

◆ getProcResource()

|

inline |

Definition at line 339 of file MCSchedule.h.

References assert().

Referenced by llvm::mca::computeBlockRThroughput(), llvm::TargetSchedModel::computeOutputLatency(), llvm::mca::computeProcResourceMasks(), llvm::mca::InstructionTables::execute(), llvm::TargetSchedModel::getProcResource(), getReciprocalThroughput(), llvm::TargetSchedModel::getResourceBufferSize(), llvm::TargetSchedModel::getResourceName(), llvm::TargetSchedModel::init(), llvm::mca::initializeUsedResources(), llvm::mca::LSUnit::LSUnit(), and llvm::mca::ResourceManager::ResourceManager().

◆ getReciprocalThroughput() [1/3]

|

static |

Definition at line 89 of file MCSchedule.cpp.

References llvm::MCWriteProcResEntry::Cycles, E, getProcResource(), llvm::MCSubtargetInfo::getSchedModel(), llvm::Optional< T >::getValue(), llvm::MCSubtargetInfo::getWriteProcResBegin(), llvm::MCSubtargetInfo::getWriteProcResEnd(), llvm::Optional< T >::hasValue(), I, IssueWidth, llvm::MCSchedClassDesc::NumMicroOps, llvm::MCProcResourceDesc::NumUnits, and llvm::MCWriteProcResEntry::ProcResourceIdx.

Referenced by llvm::TargetSchedModel::computeReciprocalThroughput(), and getReciprocalThroughput().

◆ getReciprocalThroughput() [2/3]

|

static |

Definition at line 135 of file MCSchedule.cpp.

References llvm::InstrItineraryData::beginStage(), llvm::countPopulation(), DefaultIssueWidth, E, llvm::InstrItineraryData::endStage(), llvm::InstrStage::getCycles(), llvm::InstrStage::getUnits(), llvm::Optional< T >::getValue(), llvm::Optional< T >::hasValue(), and I.

◆ getReciprocalThroughput() [3/3]

| double MCSchedModel::getReciprocalThroughput | ( | const MCSubtargetInfo & | STI, |

| const MCInstrInfo & | MCII, | ||

| const MCInst & | Inst | ||

| ) | const |

Definition at line 111 of file MCSchedule.cpp.

References llvm::MCInstrInfo::get(), llvm::MCInst::getOpcode(), getProcessorID(), getReciprocalThroughput(), getSchedClassDesc(), IssueWidth, llvm::MCSchedClassDesc::isValid(), llvm::MCSchedClassDesc::isVariant(), llvm_unreachable, and llvm::MCSubtargetInfo::resolveVariantSchedClass().

◆ getSchedClassDesc()

|

inline |

Definition at line 346 of file MCSchedule.h.

References assert().

Referenced by computeInstrLatency(), llvm::TargetSchedModel::computeReciprocalThroughput(), getLatency(), getReciprocalThroughput(), llvm::TargetSchedModel::resolveSchedClass(), and llvm::mca::verifyOperands().

◆ hasExtraProcessorInfo()

|

inline |

Definition at line 315 of file MCSchedule.h.

Referenced by llvm::mca::LSUnit::LSUnit(), llvm::mca::RegisterFile::RegisterFile(), and llvm::mca::RetireControlUnit::RetireControlUnit().

◆ hasInstrSchedModel()

|

inline |

Does this machine model include instruction-level scheduling.

Definition at line 320 of file MCSchedule.h.

Referenced by getLatency(), llvm::TargetSchedModel::hasInstrSchedModel(), and llvm::mca::verifyOperands().

◆ isComplete()

|

inline |

Return true if this machine model data for all instructions with a scheduling class (itinerary class or SchedRW list).

Definition at line 330 of file MCSchedule.h.

Referenced by llvm::TargetSchedModel::computeOperandLatency().

◆ isOutOfOrder()

|

inline |

Return true if machine supports out of order execution.

Definition at line 333 of file MCSchedule.h.

Referenced by llvm::TargetSchedModel::computeOutputLatency().

Friends And Related Function Documentation

◆ InstrItineraryData

|

friend |

Definition at line 310 of file MCSchedule.h.

Member Data Documentation

◆ CompleteModel

| bool llvm::MCSchedModel::CompleteModel |

Definition at line 302 of file MCSchedule.h.

◆ Default

|

static |

Definition at line 375 of file MCSchedule.h.

◆ DefaultHighLatency

Definition at line 293 of file MCSchedule.h.

◆ DefaultIssueWidth

Definition at line 257 of file MCSchedule.h.

Referenced by getReciprocalThroughput().

◆ DefaultLoadLatency

Definition at line 286 of file MCSchedule.h.

Referenced by llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getInstructionLatency().

◆ DefaultLoopMicroOpBufferSize

Definition at line 282 of file MCSchedule.h.

◆ DefaultMicroOpBufferSize

Definition at line 274 of file MCSchedule.h.

◆ DefaultMispredictPenalty

Definition at line 298 of file MCSchedule.h.

◆ ExtraProcessorInfo

| const MCExtraProcessorInfo* llvm::MCSchedModel::ExtraProcessorInfo |

Definition at line 313 of file MCSchedule.h.

◆ HighLatency

| unsigned llvm::MCSchedModel::HighLatency |

Definition at line 292 of file MCSchedule.h.

Referenced by llvm::TargetInstrInfo::defaultDefLatency().

◆ InstrItineraries

| const InstrItinerary* llvm::MCSchedModel::InstrItineraries |

Definition at line 311 of file MCSchedule.h.

Referenced by llvm::HexagonMCInstrInfo::getOtherReservedSlots(), and llvm::HexagonMCInstrInfo::getUnits().

◆ IssueWidth

| unsigned llvm::MCSchedModel::IssueWidth |

Definition at line 256 of file MCSchedule.h.

Referenced by llvm::TargetSchedModel::getIssueWidth(), getReciprocalThroughput(), llvm::TargetSchedModel::init(), llvm::ResourcePriorityQueue::reserveResources(), and llvm::ScoreboardHazardRecognizer::ScoreboardHazardRecognizer().

◆ LoadLatency

| unsigned llvm::MCSchedModel::LoadLatency |

Definition at line 285 of file MCSchedule.h.

Referenced by llvm::TargetInstrInfo::defaultDefLatency().

◆ LoopMicroOpBufferSize

| unsigned llvm::MCSchedModel::LoopMicroOpBufferSize |

Definition at line 281 of file MCSchedule.h.

Referenced by llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getUnrollingPreferences().

◆ MicroOpBufferSize

| unsigned llvm::MCSchedModel::MicroOpBufferSize |

Definition at line 273 of file MCSchedule.h.

Referenced by llvm::TargetSchedModel::getMicroOpBufferSize().

◆ MispredictPenalty

| unsigned llvm::MCSchedModel::MispredictPenalty |

Definition at line 297 of file MCSchedule.h.

Referenced by llvm::ARMSubtarget::getMispredictionPenalty().

◆ NumProcResourceKinds

| unsigned llvm::MCSchedModel::NumProcResourceKinds |

Definition at line 307 of file MCSchedule.h.

◆ NumSchedClasses

| unsigned llvm::MCSchedModel::NumSchedClasses |

Definition at line 308 of file MCSchedule.h.

◆ PostRAScheduler

| bool llvm::MCSchedModel::PostRAScheduler |

Definition at line 300 of file MCSchedule.h.

Referenced by llvm::TargetSubtargetInfo::enablePostRAScheduler().

◆ ProcID

| unsigned llvm::MCSchedModel::ProcID |

Definition at line 304 of file MCSchedule.h.

◆ ProcResourceTable

| const MCProcResourceDesc* llvm::MCSchedModel::ProcResourceTable |

Definition at line 305 of file MCSchedule.h.

◆ SchedClassTable

| const MCSchedClassDesc* llvm::MCSchedModel::SchedClassTable |

Definition at line 306 of file MCSchedule.h.

The documentation for this struct was generated from the following files:

- include/llvm/MC/MCSchedule.h

- lib/MC/MCSchedule.cpp

1.8.13

1.8.13