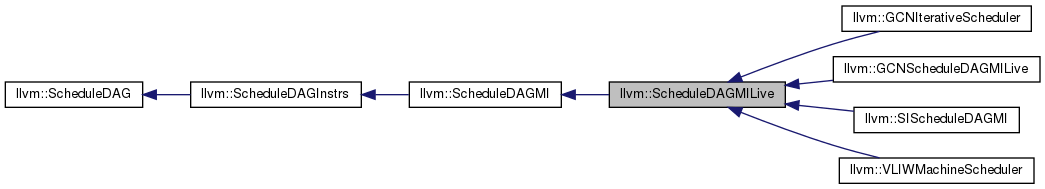

ScheduleDAGMILive is an implementation of ScheduleDAGInstrs that schedules machine instructions while updating LiveIntervals and tracking regpressure. More...

#include "llvm/CodeGen/MachineScheduler.h"

Public Member Functions | |

| ScheduleDAGMILive (MachineSchedContext *C, std::unique_ptr< MachineSchedStrategy > S) | |

| ~ScheduleDAGMILive () override | |

| bool | hasVRegLiveness () const override |

| Return true if this DAG supports VReg liveness and RegPressure. More... | |

| bool | isTrackingPressure () const |

| Return true if register pressure tracking is enabled. More... | |

| const IntervalPressure & | getTopPressure () const |

| Get current register pressure for the top scheduled instructions. More... | |

| const RegPressureTracker & | getTopRPTracker () const |

| const IntervalPressure & | getBotPressure () const |

| Get current register pressure for the bottom scheduled instructions. More... | |

| const RegPressureTracker & | getBotRPTracker () const |

| const IntervalPressure & | getRegPressure () const |

| Get register pressure for the entire scheduling region before scheduling. More... | |

| const std::vector< PressureChange > & | getRegionCriticalPSets () const |

| PressureDiff & | getPressureDiff (const SUnit *SU) |

| const PressureDiff & | getPressureDiff (const SUnit *SU) const |

| void | computeDFSResult () |

| Compute a DFSResult after DAG building is complete, and before any queue comparisons. More... | |

| const SchedDFSResult * | getDFSResult () const |

| Return a non-null DFS result if the scheduling strategy initialized it. More... | |

| BitVector & | getScheduledTrees () |

| void | enterRegion (MachineBasicBlock *bb, MachineBasicBlock::iterator begin, MachineBasicBlock::iterator end, unsigned regioninstrs) override |

| Implement the ScheduleDAGInstrs interface for handling the next scheduling region. More... | |

| void | schedule () override |

| Implement ScheduleDAGInstrs interface for scheduling a sequence of reorderable instructions. More... | |

| unsigned | computeCyclicCriticalPath () |

| Compute the cyclic critical path through the DAG. More... | |

| void | dump () const override |

Public Member Functions inherited from llvm::ScheduleDAGMI Public Member Functions inherited from llvm::ScheduleDAGMI | |

| ScheduleDAGMI (MachineSchedContext *C, std::unique_ptr< MachineSchedStrategy > S, bool RemoveKillFlags) | |

| ~ScheduleDAGMI () override | |

| bool | doMBBSchedRegionsTopDown () const override |

| If this method returns true, handling of the scheduling regions themselves (in case of a scheduling boundary in MBB) will be done beginning with the topmost region of MBB. More... | |

| LiveIntervals * | getLIS () const |

| void | addMutation (std::unique_ptr< ScheduleDAGMutation > Mutation) |

| Add a postprocessing step to the DAG builder. More... | |

| bool | canAddEdge (SUnit *SuccSU, SUnit *PredSU) |

| True if an edge can be added from PredSU to SuccSU without creating a cycle. More... | |

| bool | addEdge (SUnit *SuccSU, const SDep &PredDep) |

| Add a DAG edge to the given SU with the given predecessor dependence data. More... | |

| MachineBasicBlock::iterator | top () const |

| MachineBasicBlock::iterator | bottom () const |

| void | startBlock (MachineBasicBlock *bb) override |

| Prepares to perform scheduling in the given block. More... | |

| void | finishBlock () override |

| Cleans up after scheduling in the given block. More... | |

| void | moveInstruction (MachineInstr *MI, MachineBasicBlock::iterator InsertPos) |

| Change the position of an instruction within the basic block and update live ranges and region boundary iterators. More... | |

| const SUnit * | getNextClusterPred () const |

| const SUnit * | getNextClusterSucc () const |

| void | viewGraph (const Twine &Name, const Twine &Title) override |

| viewGraph - Pop up a ghostview window with the reachable parts of the DAG rendered using 'dot'. More... | |

| void | viewGraph () override |

| Out-of-line implementation with no arguments is handy for gdb. More... | |

Public Member Functions inherited from llvm::ScheduleDAGInstrs Public Member Functions inherited from llvm::ScheduleDAGInstrs | |

| ScheduleDAGInstrs (MachineFunction &mf, const MachineLoopInfo *mli, bool RemoveKillFlags=false) | |

| ~ScheduleDAGInstrs () override=default | |

| const TargetSchedModel * | getSchedModel () const |

| Gets the machine model for instruction scheduling. More... | |

| const MCSchedClassDesc * | getSchedClass (SUnit *SU) const |

| Resolves and cache a resolved scheduling class for an SUnit. More... | |

| MachineBasicBlock::iterator | begin () const |

| Returns an iterator to the top of the current scheduling region. More... | |

| MachineBasicBlock::iterator | end () const |

| Returns an iterator to the bottom of the current scheduling region. More... | |

| SUnit * | newSUnit (MachineInstr *MI) |

| Creates a new SUnit and return a ptr to it. More... | |

| SUnit * | getSUnit (MachineInstr *MI) const |

| Returns an existing SUnit for this MI, or nullptr. More... | |

| virtual void | exitRegion () |

| Called when the scheduler has finished scheduling the current region. More... | |

| void | buildSchedGraph (AliasAnalysis *AA, RegPressureTracker *RPTracker=nullptr, PressureDiffs *PDiffs=nullptr, LiveIntervals *LIS=nullptr, bool TrackLaneMasks=false) |

| Builds SUnits for the current region. More... | |

| void | addSchedBarrierDeps () |

| Adds dependencies from instructions in the current list of instructions being scheduled to scheduling barrier. More... | |

| virtual void | finalizeSchedule () |

| Allow targets to perform final scheduling actions at the level of the whole MachineFunction. More... | |

| void | dumpNode (const SUnit &SU) const override |

| void | dump () const override |

| std::string | getGraphNodeLabel (const SUnit *SU) const override |

| Returns a label for a DAG node that points to an instruction. More... | |

| std::string | getDAGName () const override |

| Returns a label for the region of code covered by the DAG. More... | |

| void | fixupKills (MachineBasicBlock &MBB) |

| Fixes register kill flags that scheduling has made invalid. More... | |

Public Member Functions inherited from llvm::ScheduleDAG Public Member Functions inherited from llvm::ScheduleDAG | |

| ScheduleDAG (MachineFunction &mf) | |

| virtual | ~ScheduleDAG () |

| void | clearDAG () |

| Clears the DAG state (between regions). More... | |

| const MCInstrDesc * | getInstrDesc (const SUnit *SU) const |

| Returns the MCInstrDesc of this SUnit. More... | |

| void | dumpNodeName (const SUnit &SU) const |

| virtual void | addCustomGraphFeatures (GraphWriter< ScheduleDAG *> &) const |

| Adds custom features for a visualization of the ScheduleDAG. More... | |

| unsigned | VerifyScheduledDAG (bool isBottomUp) |

| Verifies that all SUnits were scheduled and that their state is consistent. More... | |

Protected Member Functions | |

| void | buildDAGWithRegPressure () |

| Call ScheduleDAGInstrs::buildSchedGraph with register pressure tracking enabled. More... | |

| void | initQueues (ArrayRef< SUnit *> TopRoots, ArrayRef< SUnit *> BotRoots) |

| Release ExitSU predecessors and setup scheduler queues. More... | |

| void | scheduleMI (SUnit *SU, bool IsTopNode) |

| Move an instruction and update register pressure. More... | |

| void | initRegPressure () |

| void | updatePressureDiffs (ArrayRef< RegisterMaskPair > LiveUses) |

| Update the PressureDiff array for liveness after scheduling this instruction. More... | |

| void | updateScheduledPressure (const SUnit *SU, const std::vector< unsigned > &NewMaxPressure) |

| void | collectVRegUses (SUnit &SU) |

Protected Member Functions inherited from llvm::ScheduleDAGMI Protected Member Functions inherited from llvm::ScheduleDAGMI | |

| void | postprocessDAG () |

| Apply each ScheduleDAGMutation step in order. More... | |

| void | initQueues (ArrayRef< SUnit *> TopRoots, ArrayRef< SUnit *> BotRoots) |

| Release ExitSU predecessors and setup scheduler queues. More... | |

| void | updateQueues (SUnit *SU, bool IsTopNode) |

| Update scheduler DAG and queues after scheduling an instruction. More... | |

| void | placeDebugValues () |

| Reinsert debug_values recorded in ScheduleDAGInstrs::DbgValues. More... | |

| void | dumpSchedule () const |

| dump the scheduled Sequence. More... | |

| bool | checkSchedLimit () |

| void | findRootsAndBiasEdges (SmallVectorImpl< SUnit *> &TopRoots, SmallVectorImpl< SUnit *> &BotRoots) |

| void | releaseSucc (SUnit *SU, SDep *SuccEdge) |

| ReleaseSucc - Decrement the NumPredsLeft count of a successor. More... | |

| void | releaseSuccessors (SUnit *SU) |

| releaseSuccessors - Call releaseSucc on each of SU's successors. More... | |

| void | releasePred (SUnit *SU, SDep *PredEdge) |

| ReleasePred - Decrement the NumSuccsLeft count of a predecessor. More... | |

| void | releasePredecessors (SUnit *SU) |

| releasePredecessors - Call releasePred on each of SU's predecessors. More... | |

Protected Member Functions inherited from llvm::ScheduleDAGInstrs Protected Member Functions inherited from llvm::ScheduleDAGInstrs | |

| void | reduceHugeMemNodeMaps (Value2SUsMap &stores, Value2SUsMap &loads, unsigned N) |

| Reduces maps in FIFO order, by N SUs. More... | |

| void | addChainDependency (SUnit *SUa, SUnit *SUb, unsigned Latency=0) |

| Adds a chain edge between SUa and SUb, but only if both AliasAnalysis and Target fail to deny the dependency. More... | |

| void | addChainDependencies (SUnit *SU, SUList &SUs, unsigned Latency) |

| Adds dependencies as needed from all SUs in list to SU. More... | |

| void | addChainDependencies (SUnit *SU, Value2SUsMap &Val2SUsMap) |

| Adds dependencies as needed from all SUs in map, to SU. More... | |

| void | addChainDependencies (SUnit *SU, Value2SUsMap &Val2SUsMap, ValueType V) |

| Adds dependencies as needed to SU, from all SUs mapped to V. More... | |

| void | addBarrierChain (Value2SUsMap &map) |

| Adds barrier chain edges from all SUs in map, and then clear the map. More... | |

| void | insertBarrierChain (Value2SUsMap &map) |

| Inserts a barrier chain in a huge region, far below current SU. More... | |

| void | initSUnits () |

| Creates an SUnit for each real instruction, numbered in top-down topological order. More... | |

| void | addPhysRegDataDeps (SUnit *SU, unsigned OperIdx) |

| MO is an operand of SU's instruction that defines a physical register. More... | |

| void | addPhysRegDeps (SUnit *SU, unsigned OperIdx) |

| Adds register dependencies (data, anti, and output) from this SUnit to following instructions in the same scheduling region that depend the physical register referenced at OperIdx. More... | |

| void | addVRegDefDeps (SUnit *SU, unsigned OperIdx) |

| Adds register output and data dependencies from this SUnit to instructions that occur later in the same scheduling region if they read from or write to the virtual register defined at OperIdx. More... | |

| void | addVRegUseDeps (SUnit *SU, unsigned OperIdx) |

| Adds a register data dependency if the instruction that defines the virtual register used at OperIdx is mapped to an SUnit. More... | |

| void | startBlockForKills (MachineBasicBlock *BB) |

| Initializes register live-range state for updating kills. More... | |

| void | toggleKillFlag (MachineInstr &MI, MachineOperand &MO) |

| Toggles a register operand kill flag. More... | |

| LaneBitmask | getLaneMaskForMO (const MachineOperand &MO) const |

| Returns a mask for which lanes get read/written by the given (register) machine operand. More... | |

Protected Member Functions inherited from llvm::ScheduleDAG Protected Member Functions inherited from llvm::ScheduleDAG | |

| void | dumpNodeAll (const SUnit &SU) const |

Protected Attributes | |

| RegisterClassInfo * | RegClassInfo |

| SchedDFSResult * | DFSResult = nullptr |

| Information about DAG subtrees. More... | |

| BitVector | ScheduledTrees |

| MachineBasicBlock::iterator | LiveRegionEnd |

| VReg2SUnitMultiMap | VRegUses |

| Maps vregs to the SUnits of their uses in the current scheduling region. More... | |

| PressureDiffs | SUPressureDiffs |

| bool | ShouldTrackPressure = false |

| Register pressure in this region computed by initRegPressure. More... | |

| bool | ShouldTrackLaneMasks = false |

| IntervalPressure | RegPressure |

| RegPressureTracker | RPTracker |

| std::vector< PressureChange > | RegionCriticalPSets |

| List of pressure sets that exceed the target's pressure limit before scheduling, listed in increasing set ID order. More... | |

| IntervalPressure | TopPressure |

| The top of the unscheduled zone. More... | |

| RegPressureTracker | TopRPTracker |

| IntervalPressure | BotPressure |

| The bottom of the unscheduled zone. More... | |

| RegPressureTracker | BotRPTracker |

| bool | DisconnectedComponentsRenamed = false |

| True if disconnected subregister components are already renamed. More... | |

Protected Attributes inherited from llvm::ScheduleDAGMI Protected Attributes inherited from llvm::ScheduleDAGMI | |

| AliasAnalysis * | AA |

| LiveIntervals * | LIS |

| std::unique_ptr< MachineSchedStrategy > | SchedImpl |

| ScheduleDAGTopologicalSort | Topo |

| Topo - A topological ordering for SUnits which permits fast IsReachable and similar queries. More... | |

| std::vector< std::unique_ptr< ScheduleDAGMutation > > | Mutations |

| Ordered list of DAG postprocessing steps. More... | |

| MachineBasicBlock::iterator | CurrentTop |

| The top of the unscheduled zone. More... | |

| MachineBasicBlock::iterator | CurrentBottom |

| The bottom of the unscheduled zone. More... | |

| const SUnit * | NextClusterPred = nullptr |

| Record the next node in a scheduled cluster. More... | |

| const SUnit * | NextClusterSucc = nullptr |

| unsigned | NumInstrsScheduled = 0 |

| The number of instructions scheduled so far. More... | |

Protected Attributes inherited from llvm::ScheduleDAGInstrs Protected Attributes inherited from llvm::ScheduleDAGInstrs | |

| const MachineLoopInfo * | MLI |

| const MachineFrameInfo & | MFI |

| TargetSchedModel | SchedModel |

| TargetSchedModel provides an interface to the machine model. More... | |

| bool | RemoveKillFlags |

| True if the DAG builder should remove kill flags (in preparation for rescheduling). More... | |

| bool | CanHandleTerminators = false |

| The standard DAG builder does not normally include terminators as DAG nodes because it does not create the necessary dependencies to prevent reordering. More... | |

| bool | TrackLaneMasks = false |

| Whether lane masks should get tracked. More... | |

| MachineBasicBlock * | BB |

| The block in which to insert instructions. More... | |

| MachineBasicBlock::iterator | RegionBegin |

| The beginning of the range to be scheduled. More... | |

| MachineBasicBlock::iterator | RegionEnd |

| The end of the range to be scheduled. More... | |

| unsigned | NumRegionInstrs |

| Instructions in this region (distance(RegionBegin, RegionEnd)). More... | |

| DenseMap< MachineInstr *, SUnit * > | MISUnitMap |

| After calling BuildSchedGraph, each machine instruction in the current scheduling region is mapped to an SUnit. More... | |

| Reg2SUnitsMap | Defs |

| Defs, Uses - Remember where defs and uses of each register are as we iterate upward through the instructions. More... | |

| Reg2SUnitsMap | Uses |

| VReg2SUnitMultiMap | CurrentVRegDefs |

| Tracks the last instruction(s) in this region defining each virtual register. More... | |

| VReg2SUnitOperIdxMultiMap | CurrentVRegUses |

| Tracks the last instructions in this region using each virtual register. More... | |

| AliasAnalysis * | AAForDep = nullptr |

| SUnit * | BarrierChain = nullptr |

| Remember a generic side-effecting instruction as we proceed. More... | |

| UndefValue * | UnknownValue |

| For an unanalyzable memory access, this Value is used in maps. More... | |

| DbgValueVector | DbgValues |

| Remember instruction that precedes DBG_VALUE. More... | |

| MachineInstr * | FirstDbgValue = nullptr |

| LivePhysRegs | LiveRegs |

| Set of live physical registers for updating kill flags. More... | |

Additional Inherited Members | |

Public Types inherited from llvm::ScheduleDAGInstrs Public Types inherited from llvm::ScheduleDAGInstrs | |

| using | SUList = std::list< SUnit * > |

| A list of SUnits, used in Value2SUsMap, during DAG construction. More... | |

Public Attributes inherited from llvm::ScheduleDAG Public Attributes inherited from llvm::ScheduleDAG | |

| const LLVMTargetMachine & | TM |

| Target processor. More... | |

| const TargetInstrInfo * | TII |

| Target instruction information. More... | |

| const TargetRegisterInfo * | TRI |

| Target processor register info. More... | |

| MachineFunction & | MF |

| Machine function. More... | |

| MachineRegisterInfo & | MRI |

| Virtual/real register map. More... | |

| std::vector< SUnit > | SUnits |

| The scheduling units. More... | |

| SUnit | EntrySU |

| Special node for the region entry. More... | |

| SUnit | ExitSU |

| Special node for the region exit. More... | |

| bool | StressSched |

Protected Types inherited from llvm::ScheduleDAGInstrs Protected Types inherited from llvm::ScheduleDAGInstrs | |

| using | DbgValueVector = std::vector< std::pair< MachineInstr *, MachineInstr * > > |

Detailed Description

ScheduleDAGMILive is an implementation of ScheduleDAGInstrs that schedules machine instructions while updating LiveIntervals and tracking regpressure.

Definition at line 396 of file MachineScheduler.h.

Constructor & Destructor Documentation

◆ ScheduleDAGMILive()

|

inline |

Definition at line 439 of file MachineScheduler.h.

◆ ~ScheduleDAGMILive()

|

override |

Definition at line 938 of file MachineScheduler.cpp.

Member Function Documentation

◆ buildDAGWithRegPressure()

|

protected |

Call ScheduleDAGInstrs::buildSchedGraph with register pressure tracking enabled.

Build the DAG and setup three register pressure trackers.

This sets up three trackers. RPTracker will cover the entire DAG region, TopTracker and BottomTracker will be initialized to the top and bottom of the DAG region without covereing any unscheduled instruction.

Definition at line 1272 of file MachineScheduler.cpp.

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ collectVRegUses()

|

protected |

Definition at line 942 of file MachineScheduler.cpp.

References llvm::SUnit::getInstr(), llvm::LaneBitmask::getNone(), llvm::TargetRegisterInfo::isVirtualRegister(), MI, llvm::MachineInstr::operands(), and Reg.

◆ computeCyclicCriticalPath()

| unsigned ScheduleDAGMILive::computeCyclicCriticalPath | ( | ) |

Compute the cyclic critical path through the DAG.

Compute the max cyclic critical path through the DAG.

The scheduling DAG only provides the critical path for single block loops. To handle loops that span blocks, we could use the vreg path latencies provided by MachineTraceMetrics instead. However, MachineTraceMetrics is not currently available for use in the scheduler.

The cyclic path estimation identifies a def-use pair that crosses the back edge and considers the depth and height of the nodes. For example, consider the following instruction sequence where each instruction has unit latency and defines an epomymous virtual register:

a->b(a,c)->c(b)->d(c)->exit

The cyclic critical path is a two cycles: b->c->b The acyclic critical path is four cycles: a->b->c->d->exit LiveOutHeight = height(c) = len(c->d->exit) = 2 LiveOutDepth = depth(c) + 1 = len(a->b->c) + 1 = 3 LiveInHeight = height(b) + 1 = len(b->c->d->exit) + 1 = 4 LiveInDepth = depth(b) = len(a->b) = 1

LiveOutDepth - LiveInDepth = 3 - 1 = 2 LiveInHeight - LiveOutHeight = 4 - 2 = 2 CyclicCriticalPath = min(2, 2) = 2

This could be relevant to PostRA scheduling, but is currently implemented assuming LiveIntervals.

Definition at line 1331 of file MachineScheduler.cpp.

References llvm::dbgs(), llvm::VNInfo::def, DefMI, llvm::SUnit::getDepth(), llvm::SUnit::getHeight(), llvm::SUnit::getInstr(), llvm::LiveRange::getVNInfoBefore(), llvm::VNInfo::isPHIDef(), llvm::SUnit::Latency, LLVM_DEBUG, llvm::make_range(), llvm::SUnit::NodeNum, P, llvm::LiveRange::Query(), Reg, TRI, and llvm::LiveQueryResult::valueIn().

Referenced by llvm::GenericScheduler::registerRoots().

◆ computeDFSResult()

| void ScheduleDAGMILive::computeDFSResult | ( | ) |

Compute a DFSResult after DAG building is complete, and before any queue comparisons.

Definition at line 1295 of file MachineScheduler.cpp.

Referenced by llvm::createGenericSchedPostRA().

◆ dump()

|

overridevirtual |

Implements llvm::ScheduleDAG.

Definition at line 1177 of file MachineScheduler.cpp.

References llvm::dbgs(), and TRI.

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ enterRegion()

|

overridevirtual |

Implement the ScheduleDAGInstrs interface for handling the next scheduling region.

enterRegion - Called back from MachineScheduler::runOnMachineFunction after crossing a scheduling boundary.

This covers all instructions in a block, while schedule() may only cover a subset.

[begin, end) includes all instructions in the region, including the boundary itself and single-instruction regions that don't get scheduled.

Reimplemented from llvm::ScheduleDAGMI.

Reimplemented in llvm::GCNIterativeScheduler.

Definition at line 984 of file MachineScheduler.cpp.

References assert(), llvm::MachineBasicBlock::end(), and llvm::ScheduleDAGMI::enterRegion().

Referenced by llvm::GCNIterativeScheduler::enterRegion(), and llvm::GCNScheduleDAGMILive::finalizeSchedule().

◆ getBotPressure()

|

inline |

Get current register pressure for the bottom scheduled instructions.

Definition at line 458 of file MachineScheduler.h.

◆ getBotRPTracker()

|

inline |

Definition at line 459 of file MachineScheduler.h.

Referenced by llvm::GCNMaxOccupancySchedStrategy::initialize(), llvm::GCNMaxOccupancySchedStrategy::pickNode(), llvm::GenericScheduler::pickNode(), and llvm::GenericScheduler::pickNodeBidirectional().

◆ getDFSResult()

|

inline |

Return a non-null DFS result if the scheduling strategy initialized it.

Definition at line 480 of file MachineScheduler.h.

Referenced by llvm::createGenericSchedPostRA().

◆ getPressureDiff() [1/2]

|

inline |

Definition at line 468 of file MachineScheduler.h.

References llvm::SUnit::NodeNum.

Referenced by llvm::GenericScheduler::initCandidate().

◆ getPressureDiff() [2/2]

|

inline |

Definition at line 471 of file MachineScheduler.h.

References llvm::SUnit::NodeNum.

◆ getRegionCriticalPSets()

|

inline |

Definition at line 464 of file MachineScheduler.h.

Referenced by llvm::GenericScheduler::initCandidate().

◆ getRegPressure()

|

inline |

Get register pressure for the entire scheduling region before scheduling.

Definition at line 462 of file MachineScheduler.h.

References llvm::Sched::RegPressure.

Referenced by llvm::GenericScheduler::initCandidate().

◆ getScheduledTrees()

|

inline |

Definition at line 482 of file MachineScheduler.h.

References llvm::sys::path::begin(), llvm::dump(), and llvm::sys::path::end().

◆ getTopPressure()

|

inline |

Get current register pressure for the top scheduled instructions.

Definition at line 454 of file MachineScheduler.h.

◆ getTopRPTracker()

|

inline |

Definition at line 455 of file MachineScheduler.h.

Referenced by llvm::GCNMaxOccupancySchedStrategy::initialize(), llvm::GCNMaxOccupancySchedStrategy::pickNode(), llvm::GenericScheduler::pickNode(), and llvm::GenericScheduler::pickNodeBidirectional().

◆ hasVRegLiveness()

|

inlineoverridevirtual |

Return true if this DAG supports VReg liveness and RegPressure.

Reimplemented from llvm::ScheduleDAGMI.

Definition at line 448 of file MachineScheduler.h.

◆ initQueues()

|

protected |

Release ExitSU predecessors and setup scheduler queues.

Re-position the Top RP tracker in case the region beginning has changed.

Definition at line 1392 of file MachineScheduler.cpp.

References assert(), and llvm::ScheduleDAGMI::initQueues().

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ initRegPressure()

|

protected |

Definition at line 1006 of file MachineScheduler.cpp.

References assert(), llvm::dbgs(), llvm::dumpRegSetPressure(), LLVM_DEBUG, llvm::RegisterPressure::MaxSetPressure, MRI, priorNonDebug(), TRI, and updateScheduledPressure().

◆ isTrackingPressure()

|

inline |

Return true if register pressure tracking is enabled.

Definition at line 451 of file MachineScheduler.h.

Referenced by llvm::GenericScheduler::initCandidate(), and llvm::GenericScheduler::tryCandidate().

◆ schedule()

|

overridevirtual |

Implement ScheduleDAGInstrs interface for scheduling a sequence of reorderable instructions.

schedule - Called back from MachineScheduler::runOnMachineFunction after setting up the current scheduling region.

[RegionBegin, RegionEnd) only includes instructions that have DAG nodes, not scheduling boundaries.

This is a skeletal driver, with all the functionality pushed into helpers, so that it can be easily extended by experimental schedulers. Generally, implementing MachineSchedStrategy should be sufficient to implement a new scheduling algorithm. However, if a scheduler further subclasses ScheduleDAGMILive then it will want to override this virtual method in order to update any specialized state.

Reimplemented from llvm::ScheduleDAGMI.

Reimplemented in llvm::SIScheduleDAGMI, llvm::GCNScheduleDAGMILive, llvm::VLIWMachineScheduler, and llvm::GCNIterativeScheduler.

Definition at line 1210 of file MachineScheduler.cpp.

References assert(), llvm::sys::path::begin(), llvm::dbgs(), llvm::dump(), getParent(), llvm::SUnit::isScheduled, LLVM_DEBUG, and llvm::printMBBReference().

Referenced by llvm::GCNScheduleDAGMILive::schedule().

◆ scheduleMI()

Move an instruction and update register pressure.

Definition at line 1402 of file MachineScheduler.cpp.

References llvm::RegisterOperands::adjustLaneLiveness(), llvm::cl::apply(), assert(), llvm::RegisterOperands::collect(), llvm::dbgs(), llvm::RegisterOperands::detectDeadDefs(), llvm::dumpRegSetPressure(), llvm::TargetSubtargetInfo::getFrameLowering(), llvm::MachineOperand::getIndex(), llvm::SUnit::getInstr(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::SlotIndex::getRegSlot(), llvm::TargetFrameLowering::getStackGrowthDirection(), llvm::MachineFunction::getSubtarget(), llvm::MachineOperand::getType(), llvm::SUnit::isBottomReady(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isReg(), llvm::SUnit::isTopReady(), LLVM_DEBUG, llvm_unreachable, MI, MRI, nextIfDebug(), llvm::SUnit::NodeNum, llvm::operator<(), priorNonDebug(), llvm::TargetFrameLowering::StackGrowsDown, TII, and TRI.

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ updatePressureDiffs()

|

protected |

Update the PressureDiff array for liveness after scheduling this instruction.

FIXME: Currently assuming single-use physregs.

Definition at line 1109 of file MachineScheduler.cpp.

References llvm::PressureDiff::addPressureChange(), assert(), llvm::dbgs(), llvm::PressureDiff::dump(), llvm::SUnit::getInstr(), llvm::LiveRange::getVNInfoBefore(), I, llvm::SUnit::isScheduled, LLVM_DEBUG, llvm::make_range(), MRI, nextIfDebug(), llvm::SUnit::NodeNum, P, llvm::PrintLaneMask(), llvm::printReg(), llvm::printVRegOrUnit(), llvm::LiveRange::Query(), Reg, TRI, and llvm::LiveQueryResult::valueIn().

◆ updateScheduledPressure()

|

protected |

Definition at line 1081 of file MachineScheduler.cpp.

References llvm::dbgs(), LLVM_DEBUG, llvm::max(), and TRI.

Referenced by initRegPressure().

Member Data Documentation

◆ BotPressure

|

protected |

The bottom of the unscheduled zone.

Definition at line 431 of file MachineScheduler.h.

◆ BotRPTracker

|

protected |

Definition at line 432 of file MachineScheduler.h.

◆ DFSResult

|

protected |

Information about DAG subtrees.

If DFSResult is NULL, then SchedulerTrees will be empty.

Definition at line 402 of file MachineScheduler.h.

◆ DisconnectedComponentsRenamed

True if disconnected subregister components are already renamed.

The renaming is only done on demand if lane masks are tracked.

Definition at line 436 of file MachineScheduler.h.

◆ LiveRegionEnd

|

protected |

Definition at line 405 of file MachineScheduler.h.

◆ RegClassInfo

|

protected |

Definition at line 398 of file MachineScheduler.h.

◆ RegionCriticalPSets

|

protected |

List of pressure sets that exceed the target's pressure limit before scheduling, listed in increasing set ID order.

Each pressure set is paired with its max pressure in the currently scheduled regions.

Definition at line 424 of file MachineScheduler.h.

◆ RegPressure

|

protected |

Definition at line 418 of file MachineScheduler.h.

◆ RPTracker

|

protected |

Definition at line 419 of file MachineScheduler.h.

Referenced by llvm::GCNIterativeScheduler::getSchedulePressure(), and llvm::GCNScheduleDAGMILive::schedule().

◆ ScheduledTrees

|

protected |

Definition at line 403 of file MachineScheduler.h.

◆ ShouldTrackLaneMasks

Definition at line 417 of file MachineScheduler.h.

Referenced by llvm::GCNScheduleDAGMILive::schedule().

◆ ShouldTrackPressure

Register pressure in this region computed by initRegPressure.

Definition at line 416 of file MachineScheduler.h.

◆ SUPressureDiffs

|

protected |

Definition at line 413 of file MachineScheduler.h.

◆ TopPressure

|

protected |

The top of the unscheduled zone.

Definition at line 427 of file MachineScheduler.h.

◆ TopRPTracker

|

protected |

Definition at line 428 of file MachineScheduler.h.

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ VRegUses

|

protected |

Maps vregs to the SUnits of their uses in the current scheduling region.

Definition at line 408 of file MachineScheduler.h.

The documentation for this class was generated from the following files:

- include/llvm/CodeGen/MachineScheduler.h

- lib/CodeGen/MachineScheduler.cpp

1.8.13

1.8.13