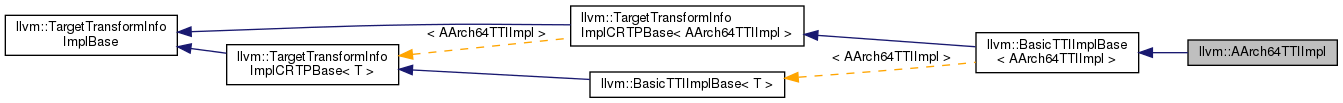

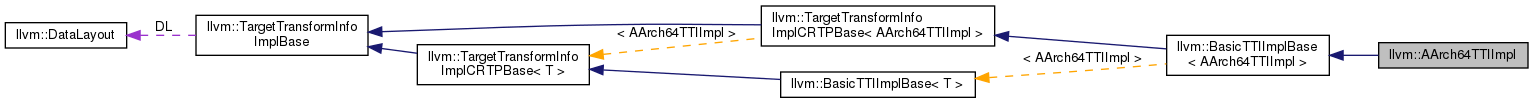

#include "Target/AArch64/AArch64TargetTransformInfo.h"

Additional Inherited Members | |

Protected Types inherited from llvm::TargetTransformInfoImplBase Protected Types inherited from llvm::TargetTransformInfoImplBase | |

| typedef TargetTransformInfo | TTI |

Protected Member Functions inherited from llvm::BasicTTIImplBase< AArch64TTIImpl > Protected Member Functions inherited from llvm::BasicTTIImplBase< AArch64TTIImpl > | |

| BasicTTIImplBase (const TargetMachine *TM, const DataLayout &DL) | |

Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< AArch64TTIImpl > Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< AArch64TTIImpl > | |

| TargetTransformInfoImplCRTPBase (const DataLayout &DL) | |

Protected Member Functions inherited from llvm::TargetTransformInfoImplBase Protected Member Functions inherited from llvm::TargetTransformInfoImplBase | |

| TargetTransformInfoImplBase (const DataLayout &DL) | |

| unsigned | minRequiredElementSize (const Value *Val, bool &isSigned) |

| bool | isStridedAccess (const SCEV *Ptr) |

| const SCEVConstant * | getConstantStrideStep (ScalarEvolution *SE, const SCEV *Ptr) |

| bool | isConstantStridedAccessLessThan (ScalarEvolution *SE, const SCEV *Ptr, int64_t MergeDistance) |

Protected Attributes inherited from llvm::TargetTransformInfoImplBase Protected Attributes inherited from llvm::TargetTransformInfoImplBase | |

| const DataLayout & | DL |

Detailed Description

Definition at line 42 of file AArch64TargetTransformInfo.h.

Constructor & Destructor Documentation

◆ AArch64TTIImpl()

|

inlineexplicit |

Definition at line 64 of file AArch64TargetTransformInfo.h.

References areInlineCompatible(), Callee, getIntImmCost(), llvm::TargetTransformInfoImplBase::getIntImmCost(), and getPopcntSupport().

Member Function Documentation

◆ areInlineCompatible()

Definition at line 27 of file AArch64TargetTransformInfo.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), and llvm::SystemZISD::TM.

Referenced by AArch64TTIImpl().

◆ enableInterleavedAccessVectorization()

|

inline |

Definition at line 87 of file AArch64TargetTransformInfo.h.

◆ getAddressComputationCost()

| int AArch64TTIImpl::getAddressComputationCost | ( | Type * | Ty, |

| ScalarEvolution * | SE, | ||

| const SCEV * | Ptr | ||

| ) |

Definition at line 571 of file AArch64TargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::isConstantStridedAccessLessThan(), and llvm::Type::isVectorTy().

Referenced by getMinVectorRegisterBitWidth().

◆ getArithmeticInstrCost()

| int AArch64TTIImpl::getArithmeticInstrCost | ( | unsigned | Opcode, |

| Type * | Ty, | ||

| TTI::OperandValueKind | Opd1Info = TTI::OK_AnyValue, |

||

| TTI::OperandValueKind | Opd2Info = TTI::OK_AnyValue, |

||

| TTI::OperandValueProperties | Opd1PropInfo = TTI::OP_None, |

||

| TTI::OperandValueProperties | Opd2PropInfo = TTI::OP_None, |

||

| ArrayRef< const Value *> | Args = ArrayRef<const Value *>() |

||

| ) |

Definition at line 477 of file AArch64TargetTransformInfo.cpp.

References llvm::MCID::Add, llvm::ISD::ADD, llvm::ISD::AND, llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AArch64TTIImpl >::getArithmeticInstrCost(), llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::TargetLoweringBase::getValueType(), llvm::AArch64Subtarget::getWideningBaseCost(), llvm::TargetLoweringBase::InstructionOpcodeToISD(), llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::Type::isVectorTy(), LLVM_FALLTHROUGH, llvm::AArch64CC::LT, llvm::ISD::MUL, llvm::ISD::MULHU, llvm::TargetTransformInfo::OK_UniformConstantValue, llvm::TargetTransformInfo::OP_None, llvm::TargetTransformInfo::OP_PowerOf2, llvm::ISD::OR, llvm::ISD::SDIV, llvm::MCID::Select, llvm::ISD::UDIV, and llvm::ISD::XOR.

Referenced by getMinVectorRegisterBitWidth().

◆ getArithmeticReductionCost()

Definition at line 922 of file AArch64TargetTransformInfo.cpp.

References llvm::ISD::ADD, assert(), llvm::CostTableLookup(), llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AArch64TTIImpl >::getArithmeticReductionCost(), llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::TargetLoweringBase::InstructionOpcodeToISD(), llvm::AArch64CC::LT, llvm::MVT::v16i8, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v8i16, and llvm::MVT::v8i8.

Referenced by shouldExpandReduction().

◆ getCacheLineSize()

| unsigned AArch64TTIImpl::getCacheLineSize | ( | ) |

Definition at line 881 of file AArch64TargetTransformInfo.cpp.

References llvm::AArch64Subtarget::getCacheLineSize().

Referenced by getMinVectorRegisterBitWidth().

◆ getCastInstrCost()

| int AArch64TTIImpl::getCastInstrCost | ( | unsigned | Opcode, |

| Type * | Dst, | ||

| Type * | Src, | ||

| const Instruction * | I = nullptr |

||

| ) |

Definition at line 261 of file AArch64TargetTransformInfo.cpp.

References assert(), llvm::ConvertCostTableLookup(), llvm::TargetTransformInfoImplBase::DL, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::BasicTTIImplBase< AArch64TTIImpl >::getCastInstrCost(), llvm::Instruction::getOpcode(), llvm::User::getOperand(), llvm::EVT::getSimpleVT(), llvm::TargetLoweringBase::getValueType(), llvm::Value::hasOneUse(), llvm::TargetLoweringBase::InstructionOpcodeToISD(), llvm::EVT::isSimple(), llvm::ISD::SIGN_EXTEND, llvm::ISD::SINT_TO_FP, llvm::ISD::TRUNCATE, llvm::ISD::UINT_TO_FP, llvm::Value::user_begin(), llvm::MVT::v16f32, llvm::MVT::v16i16, llvm::MVT::v16i32, llvm::MVT::v16i8, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i16, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v2i8, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v4i64, llvm::MVT::v4i8, llvm::MVT::v8f32, llvm::MVT::v8i16, llvm::MVT::v8i32, llvm::MVT::v8i64, llvm::MVT::v8i8, and llvm::ISD::ZERO_EXTEND.

Referenced by getExtractWithExtendCost(), and getMinVectorRegisterBitWidth().

◆ getCmpSelInstrCost()

| int AArch64TTIImpl::getCmpSelInstrCost | ( | unsigned | Opcode, |

| Type * | ValTy, | ||

| Type * | CondTy, | ||

| const Instruction * | I = nullptr |

||

| ) |

Definition at line 589 of file AArch64TargetTransformInfo.cpp.

References llvm::ConvertCostTableLookup(), llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AArch64TTIImpl >::getCmpSelInstrCost(), llvm::EVT::getSimpleVT(), llvm::TargetLoweringBase::getValueType(), llvm::TargetLoweringBase::InstructionOpcodeToISD(), llvm::EVT::isSimple(), llvm::Type::isVectorTy(), llvm::ISD::SELECT, llvm::MVT::v16i1, llvm::MVT::v16i16, llvm::MVT::v16i32, llvm::MVT::v16i64, llvm::MVT::v4i1, llvm::MVT::v4i64, llvm::MVT::v8i1, llvm::MVT::v8i32, and llvm::MVT::v8i64.

Referenced by getMinVectorRegisterBitWidth().

◆ getCostOfKeepingLiveOverCall()

Definition at line 686 of file AArch64TargetTransformInfo.cpp.

References getMemoryOpCost(), I, llvm::SPII::Load, and llvm::SPII::Store.

Referenced by getMinVectorRegisterBitWidth().

◆ getExtractWithExtendCost()

| int AArch64TTIImpl::getExtractWithExtendCost | ( | unsigned | Opcode, |

| Type * | Dst, | ||

| VectorType * | VecTy, | ||

| unsigned | Index | ||

| ) |

Definition at line 397 of file AArch64TargetTransformInfo.cpp.

References assert(), llvm::TargetTransformInfoImplBase::DL, getCastInstrCost(), llvm::SequentialType::getElementType(), llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::TargetLoweringBase::getValueType(), getVectorInstrCost(), llvm::TargetLoweringBase::isTypeLegal(), and llvm_unreachable.

Referenced by getMinVectorRegisterBitWidth().

◆ getInterleavedMemoryOpCost()

| int AArch64TTIImpl::getInterleavedMemoryOpCost | ( | unsigned | Opcode, |

| Type * | VecTy, | ||

| unsigned | Factor, | ||

| ArrayRef< unsigned > | Indices, | ||

| unsigned | Alignment, | ||

| unsigned | AddressSpace, | ||

| bool | UseMaskForCond = false, |

||

| bool | UseMaskForGaps = false |

||

| ) |

Definition at line 658 of file AArch64TargetTransformInfo.cpp.

References assert(), llvm::TargetTransformInfoImplBase::DL, llvm::VectorType::get(), llvm::BasicTTIImplBase< AArch64TTIImpl >::getInterleavedMemoryOpCost(), llvm::AArch64TargetLowering::getNumInterleavedAccesses(), llvm::Type::getScalarType(), llvm::Type::getVectorNumElements(), and llvm::AArch64TargetLowering::isLegalInterleavedAccessType().

Referenced by getMinVectorRegisterBitWidth().

◆ getIntImmCost() [1/4]

| int AArch64TTIImpl::getIntImmCost | ( | int64_t | Val | ) |

Calculate the cost of materializing a 64-bit value.

This helper method might only calculate a fraction of a larger immediate. Therefore it is valid to return a cost of ZERO.

Definition at line 44 of file AArch64TargetTransformInfo.cpp.

References llvm::countLeadingZeros(), and llvm::AArch64_AM::isLogicalImmediate().

Referenced by AArch64TTIImpl(), and getIntImmCost().

◆ getIntImmCost() [2/4]

Calculate the cost of materializing the given constant.

Definition at line 58 of file AArch64TargetTransformInfo.cpp.

References llvm::APInt::ashr(), assert(), getIntImmCost(), llvm::Type::getPrimitiveSizeInBits(), llvm::APInt::getSExtValue(), llvm::Type::isIntegerTy(), llvm::max(), llvm::APInt::sext(), and llvm::APInt::sextOrTrunc().

Referenced by getIntImmCost().

◆ getIntImmCost() [3/4]

Definition at line 82 of file AArch64TargetTransformInfo.cpp.

References llvm::MCID::Add, assert(), llvm::MCID::Call, getIntImmCost(), llvm::Type::getPrimitiveSizeInBits(), llvm::Type::isIntegerTy(), llvm::SPII::Load, llvm::MipsISD::Ret, llvm::MCID::Select, llvm::SPII::Store, llvm::TargetTransformInfo::TCC_Basic, and llvm::TargetTransformInfo::TCC_Free.

◆ getIntImmCost() [4/4]

| int AArch64TTIImpl::getIntImmCost | ( | Intrinsic::ID | IID, |

| unsigned | Idx, | ||

| const APInt & | Imm, | ||

| Type * | Ty | ||

| ) |

Definition at line 148 of file AArch64TargetTransformInfo.cpp.

References assert(), llvm::Intrinsic::experimental_patchpoint_i64, llvm::Intrinsic::experimental_patchpoint_void, llvm::Intrinsic::experimental_stackmap, llvm::APInt::getBitWidth(), getIntImmCost(), llvm::Type::getPrimitiveSizeInBits(), llvm::APInt::getSExtValue(), llvm::Type::isIntegerTy(), llvm::Intrinsic::sadd_with_overflow, llvm::Intrinsic::smul_with_overflow, llvm::Intrinsic::ssub_with_overflow, llvm::TargetTransformInfo::TCC_Basic, llvm::TargetTransformInfo::TCC_Free, llvm::Intrinsic::uadd_with_overflow, llvm::Intrinsic::umul_with_overflow, and llvm::Intrinsic::usub_with_overflow.

◆ getMaxInterleaveFactor()

Definition at line 698 of file AArch64TargetTransformInfo.cpp.

References llvm::AArch64Subtarget::getMaxInterleaveFactor().

Referenced by getMinVectorRegisterBitWidth().

◆ getMaxPrefetchIterationsAhead()

| unsigned AArch64TTIImpl::getMaxPrefetchIterationsAhead | ( | ) |

Definition at line 893 of file AArch64TargetTransformInfo.cpp.

References llvm::AArch64Subtarget::getMaxPrefetchIterationsAhead().

Referenced by getMinVectorRegisterBitWidth().

◆ getMemoryOpCost()

| int AArch64TTIImpl::getMemoryOpCost | ( | unsigned | Opcode, |

| Type * | Src, | ||

| unsigned | Alignment, | ||

| unsigned | AddressSpace, | ||

| const Instruction * | I = nullptr |

||

| ) |

Definition at line 620 of file AArch64TargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::DL, llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::Type::getVectorElementType(), llvm::Type::getVectorNumElements(), llvm::Type::isIntegerTy(), llvm::AArch64Subtarget::isMisaligned128StoreSlow(), llvm::Type::isVectorTy(), llvm::AArch64CC::LT, and llvm::SPII::Store.

Referenced by getCostOfKeepingLiveOverCall(), and getMinVectorRegisterBitWidth().

◆ getMinPrefetchStride()

| unsigned AArch64TTIImpl::getMinPrefetchStride | ( | ) |

Definition at line 889 of file AArch64TargetTransformInfo.cpp.

References llvm::AArch64Subtarget::getMinPrefetchStride().

Referenced by getMinVectorRegisterBitWidth().

◆ getMinVectorRegisterBitWidth()

|

inline |

Definition at line 107 of file AArch64TargetTransformInfo.h.

References getAddressComputationCost(), getArithmeticInstrCost(), getCacheLineSize(), getCastInstrCost(), getCmpSelInstrCost(), getCostOfKeepingLiveOverCall(), getExtractWithExtendCost(), getInterleavedMemoryOpCost(), getMaxInterleaveFactor(), getMaxPrefetchIterationsAhead(), getMemoryOpCost(), getMinPrefetchStride(), llvm::AArch64Subtarget::getMinVectorRegisterBitWidth(), getOrCreateResultFromMemIntrinsic(), getPrefetchDistance(), getTgtMemIntrinsic(), getUnrollingPreferences(), getVectorInstrCost(), I, Info, llvm::TargetTransformInfo::OK_AnyValue, llvm::TargetTransformInfo::OP_None, and shouldConsiderAddressTypePromotion().

◆ getNumberOfRegisters()

Definition at line 89 of file AArch64TargetTransformInfo.h.

References llvm::AArch64Subtarget::hasNEON().

◆ getOrCreateResultFromMemIntrinsic()

| Value * AArch64TTIImpl::getOrCreateResultFromMemIntrinsic | ( | IntrinsicInst * | Inst, |

| Type * | ExpectedType | ||

| ) |

Definition at line 773 of file AArch64TargetTransformInfo.cpp.

References llvm::Intrinsic::aarch64_neon_ld2, llvm::Intrinsic::aarch64_neon_ld3, llvm::Intrinsic::aarch64_neon_ld4, llvm::Intrinsic::aarch64_neon_st2, llvm::Intrinsic::aarch64_neon_st3, llvm::Intrinsic::aarch64_neon_st4, llvm::IRBuilder< T, Inserter >::CreateInsertValue(), llvm::dyn_cast(), llvm::UndefValue::get(), llvm::CallBase::getArgOperand(), llvm::StructType::getElementType(), llvm::IntrinsicInst::getIntrinsicID(), llvm::CallBase::getNumArgOperands(), llvm::StructType::getNumElements(), and llvm::Value::getType().

Referenced by getMinVectorRegisterBitWidth().

◆ getPopcntSupport()

| TargetTransformInfo::PopcntSupportKind AArch64TTIImpl::getPopcntSupport | ( | unsigned | TyWidth | ) |

Definition at line 189 of file AArch64TargetTransformInfo.cpp.

References llvm::MCID::Add, llvm::AMDGPU::HSAMD::Kernel::Key::Args, assert(), llvm::TargetTransformInfoImplBase::DL, llvm::VectorType::get(), llvm::Type::getScalarSizeInBits(), llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::Type::getVectorNumElements(), llvm::isPowerOf2_32(), llvm::Type::isVectorTy(), llvm::TargetTransformInfo::PSK_FastHardware, llvm::TargetTransformInfo::PSK_Software, and llvm::ArrayRef< T >::size().

Referenced by AArch64TTIImpl().

◆ getPrefetchDistance()

| unsigned AArch64TTIImpl::getPrefetchDistance | ( | ) |

Definition at line 885 of file AArch64TargetTransformInfo.cpp.

References llvm::AArch64Subtarget::getPrefetchDistance().

Referenced by getMinVectorRegisterBitWidth().

◆ getRegisterBitWidth()

Definition at line 98 of file AArch64TargetTransformInfo.h.

References llvm::AArch64Subtarget::hasNEON().

◆ getShuffleCost()

| int AArch64TTIImpl::getShuffleCost | ( | TTI::ShuffleKind | Kind, |

| Type * | Tp, | ||

| int | Index, | ||

| Type * | SubTp | ||

| ) |

Definition at line 950 of file AArch64TargetTransformInfo.cpp.

References llvm::CostTableLookup(), llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AArch64TTIImpl >::getShuffleCost(), llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::AArch64CC::LT, llvm::TargetTransformInfo::SK_Broadcast, llvm::TargetTransformInfo::SK_PermuteSingleSrc, llvm::TargetTransformInfo::SK_Select, llvm::TargetTransformInfo::SK_Transpose, llvm::MVT::v16i8, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v8i16, and llvm::MVT::v8i8.

Referenced by shouldExpandReduction().

◆ getTgtMemIntrinsic()

| bool AArch64TTIImpl::getTgtMemIntrinsic | ( | IntrinsicInst * | Inst, |

| MemIntrinsicInfo & | Info | ||

| ) |

Definition at line 809 of file AArch64TargetTransformInfo.cpp.

References llvm::Intrinsic::aarch64_neon_ld2, llvm::Intrinsic::aarch64_neon_ld3, llvm::Intrinsic::aarch64_neon_ld4, llvm::Intrinsic::aarch64_neon_st2, llvm::Intrinsic::aarch64_neon_st3, llvm::Intrinsic::aarch64_neon_st4, llvm::CallBase::getArgOperand(), llvm::IntrinsicInst::getIntrinsicID(), llvm::CallBase::getNumArgOperands(), llvm::MemIntrinsicInfo::MatchingId, llvm::MemIntrinsicInfo::PtrVal, llvm::MemIntrinsicInfo::ReadMem, and llvm::MemIntrinsicInfo::WriteMem.

Referenced by getMinVectorRegisterBitWidth().

◆ getUnrollingPreferences()

| void AArch64TTIImpl::getUnrollingPreferences | ( | Loop * | L, |

| ScalarEvolution & | SE, | ||

| TTI::UnrollingPreferences & | UP | ||

| ) |

Definition at line 754 of file AArch64TargetTransformInfo.cpp.

References EnableFalkorHWPFUnrollFix, llvm::AArch64Subtarget::Falkor, getFalkorUnrollingPreferences(), llvm::LoopBase< BlockT, LoopT >::getLoopDepth(), llvm::AArch64Subtarget::getProcFamily(), llvm::BasicTTIImplBase< AArch64TTIImpl >::getUnrollingPreferences(), if(), llvm::TargetTransformInfo::UnrollingPreferences::PartialOptSizeThreshold, and llvm::TargetTransformInfo::UnrollingPreferences::PartialThreshold.

Referenced by getMinVectorRegisterBitWidth().

◆ getVectorInstrCost()

Definition at line 452 of file AArch64TargetTransformInfo.cpp.

References assert(), llvm::TargetTransformInfoImplBase::DL, llvm::TargetLoweringBase::getTypeLegalizationCost(), llvm::AArch64Subtarget::getVectorInsertExtractBaseCost(), llvm::Type::isVectorTy(), and llvm::AArch64CC::LT.

Referenced by getExtractWithExtendCost(), and getMinVectorRegisterBitWidth().

◆ shouldConsiderAddressTypePromotion()

| bool AArch64TTIImpl::shouldConsiderAddressTypePromotion | ( | const Instruction & | I, |

| bool & | AllowPromotionWithoutCommonHeader | ||

| ) |

See if I should be considered for address type promotion.

We check if I is a sext with right type and used in memory accesses. If it used in a "complex" getelementptr, we allow it to be promoted without finding other sext instructions that sign extended the same initial value. A getelementptr is considered as "complex" if it has more than 2 operands.

Definition at line 854 of file AArch64TargetTransformInfo.cpp.

References llvm::Function::getContext(), llvm::Type::getInt64Ty(), llvm::Instruction::getParent(), llvm::BasicBlock::getParent(), llvm::Value::getType(), and llvm::Value::users().

Referenced by getMinVectorRegisterBitWidth().

◆ shouldExpandReduction()

|

inline |

Definition at line 165 of file AArch64TargetTransformInfo.h.

References getArithmeticReductionCost(), getShuffleCost(), Kind, and useReductionIntrinsic().

◆ useReductionIntrinsic()

| bool AArch64TTIImpl::useReductionIntrinsic | ( | unsigned | Opcode, |

| Type * | Ty, | ||

| TTI::ReductionFlags | Flags | ||

| ) | const |

Definition at line 897 of file AArch64TargetTransformInfo.cpp.

References llvm::MCID::Add, assert(), llvm::Type::getScalarSizeInBits(), llvm::Type::getVectorNumElements(), llvm_unreachable, and llvm::TargetTransformInfo::ReductionFlags::NoNaN.

Referenced by shouldExpandReduction().

The documentation for this class was generated from the following files:

- lib/Target/AArch64/AArch64TargetTransformInfo.h

- lib/Target/AArch64/AArch64TargetTransformInfo.cpp

1.8.13

1.8.13