MCRegisterInfo base class - We assume that the target defines a static array of MCRegisterDesc objects that represent all of the machine registers that the target has. More...

#include "llvm/MC/MCRegisterInfo.h"

Classes | |

| class | DiffListIterator |

| DiffListIterator - Base iterator class that can traverse the differentially encoded register and regunit lists in DiffLists. More... | |

| struct | DwarfLLVMRegPair |

| DwarfLLVMRegPair - Emitted by tablegen so Dwarf<->LLVM reg mappings can be performed with a binary search. More... | |

| struct | SubRegCoveredBits |

| SubRegCoveredBits - Emitted by tablegen: bit range covered by a subreg index, -1 in any being invalid. More... | |

Public Types | |

| using | regclass_iterator = const MCRegisterClass * |

Public Member Functions | |

| void | InitMCRegisterInfo (const MCRegisterDesc *D, unsigned NR, unsigned RA, unsigned PC, const MCRegisterClass *C, unsigned NC, const MCPhysReg(*RURoots)[2], unsigned NRU, const MCPhysReg *DL, const LaneBitmask *RUMS, const char *Strings, const char *ClassStrings, const uint16_t *SubIndices, unsigned NumIndices, const SubRegCoveredBits *SubIdxRanges, const uint16_t *RET) |

| Initialize MCRegisterInfo, called by TableGen auto-generated routines. More... | |

| void | mapLLVMRegsToDwarfRegs (const DwarfLLVMRegPair *Map, unsigned Size, bool isEH) |

| Used to initialize LLVM register to Dwarf register number mapping. More... | |

| void | mapDwarfRegsToLLVMRegs (const DwarfLLVMRegPair *Map, unsigned Size, bool isEH) |

| Used to initialize Dwarf register to LLVM register number mapping. More... | |

| void | mapLLVMRegToSEHReg (unsigned LLVMReg, int SEHReg) |

| mapLLVMRegToSEHReg - Used to initialize LLVM register to SEH register number mapping. More... | |

| void | mapLLVMRegToCVReg (unsigned LLVMReg, int CVReg) |

| unsigned | getRARegister () const |

| This method should return the register where the return address can be found. More... | |

| unsigned | getProgramCounter () const |

| Return the register which is the program counter. More... | |

| const MCRegisterDesc & | operator[] (unsigned RegNo) const |

| const MCRegisterDesc & | get (unsigned RegNo) const |

| Provide a get method, equivalent to [], but more useful with a pointer to this object. More... | |

| unsigned | getSubReg (unsigned Reg, unsigned Idx) const |

| Returns the physical register number of sub-register "Index" for physical register RegNo. More... | |

| unsigned | getMatchingSuperReg (unsigned Reg, unsigned SubIdx, const MCRegisterClass *RC) const |

| Return a super-register of the specified register Reg so its sub-register of index SubIdx is Reg. More... | |

| unsigned | getSubRegIndex (unsigned RegNo, unsigned SubRegNo) const |

| For a given register pair, return the sub-register index if the second register is a sub-register of the first. More... | |

| unsigned | getSubRegIdxSize (unsigned Idx) const |

| Get the size of the bit range covered by a sub-register index. More... | |

| unsigned | getSubRegIdxOffset (unsigned Idx) const |

| Get the offset of the bit range covered by a sub-register index. More... | |

| const char * | getName (unsigned RegNo) const |

| Return the human-readable symbolic target-specific name for the specified physical register. More... | |

| unsigned | getNumRegs () const |

| Return the number of registers this target has (useful for sizing arrays holding per register information) More... | |

| unsigned | getNumSubRegIndices () const |

| Return the number of sub-register indices understood by the target. More... | |

| unsigned | getNumRegUnits () const |

| Return the number of (native) register units in the target. More... | |

| int | getDwarfRegNum (unsigned RegNum, bool isEH) const |

| Map a target register to an equivalent dwarf register number. More... | |

| int | getLLVMRegNum (unsigned RegNum, bool isEH) const |

| Map a dwarf register back to a target register. More... | |

| int | getLLVMRegNumFromEH (unsigned RegNum) const |

| Map a DWARF EH register back to a target register (same as getLLVMRegNum(RegNum, true)) but return -1 if there is no mapping, rather than asserting that there must be one. More... | |

| int | getDwarfRegNumFromDwarfEHRegNum (unsigned RegNum) const |

| Map a target EH register number to an equivalent DWARF register number. More... | |

| int | getSEHRegNum (unsigned RegNum) const |

| Map a target register to an equivalent SEH register number. More... | |

| int | getCodeViewRegNum (unsigned RegNum) const |

| Map a target register to an equivalent CodeView register number. More... | |

| regclass_iterator | regclass_begin () const |

| regclass_iterator | regclass_end () const |

| iterator_range< regclass_iterator > | regclasses () const |

| unsigned | getNumRegClasses () const |

| const MCRegisterClass & | getRegClass (unsigned i) const |

| Returns the register class associated with the enumeration value. More... | |

| const char * | getRegClassName (const MCRegisterClass *Class) const |

| uint16_t | getEncodingValue (unsigned RegNo) const |

| Returns the encoding for RegNo. More... | |

| bool | isSubRegister (unsigned RegA, unsigned RegB) const |

| Returns true if RegB is a sub-register of RegA. More... | |

| bool | isSuperRegister (unsigned RegA, unsigned RegB) const |

| Returns true if RegB is a super-register of RegA. More... | |

| bool | isSubRegisterEq (unsigned RegA, unsigned RegB) const |

| Returns true if RegB is a sub-register of RegA or if RegB == RegA. More... | |

| bool | isSuperRegisterEq (unsigned RegA, unsigned RegB) const |

| Returns true if RegB is a super-register of RegA or if RegB == RegA. More... | |

| bool | isSuperOrSubRegisterEq (unsigned RegA, unsigned RegB) const |

| Returns true if RegB is a super-register or sub-register of RegA or if RegB == RegA. More... | |

Friends | |

| class | MCSubRegIterator |

| class | MCSubRegIndexIterator |

| class | MCSuperRegIterator |

| class | MCRegUnitIterator |

| class | MCRegUnitMaskIterator |

| class | MCRegUnitRootIterator |

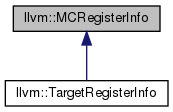

Detailed Description

MCRegisterInfo base class - We assume that the target defines a static array of MCRegisterDesc objects that represent all of the machine registers that the target has.

As such, we simply have to track a pointer to this array so that we can turn register number into a register descriptor.

Note this class is designed to be a base class of TargetRegisterInfo, which is the interface used by codegen. However, specific targets should never specialize this class. MCRegisterInfo should only contain getters to access TableGen generated physical register data. It must not be extended with virtual methods.

Definition at line 129 of file MCRegisterInfo.h.

Member Typedef Documentation

◆ regclass_iterator

Definition at line 131 of file MCRegisterInfo.h.

Member Function Documentation

◆ get()

|

inline |

Provide a get method, equivalent to [], but more useful with a pointer to this object.

Definition at line 340 of file MCRegisterInfo.h.

References Reg.

Referenced by llvm::TargetMachine::getMCRegisterInfo(), llvm::LLVMDisasmContext::getRegisterInfo(), llvm::DWARFContext::getRegisterInfo(), llvm::MCRegUnitIterator::MCRegUnitIterator(), llvm::MCRegUnitMaskIterator::MCRegUnitMaskIterator(), llvm::MCSubRegIndexIterator::MCSubRegIndexIterator(), llvm::MCSubRegIterator::MCSubRegIterator(), and llvm::MCSuperRegIterator::MCSuperRegIterator().

◆ getCodeViewRegNum()

| int MCRegisterInfo::getCodeViewRegNum | ( | unsigned | RegNum | ) | const |

Map a target register to an equivalent CodeView register number.

Definition at line 126 of file MCRegisterInfo.cpp.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::empty(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::end(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::find(), getName(), getNumRegs(), I, and llvm::report_fatal_error().

Referenced by needsReferenceType(), and printFPOReg().

◆ getDwarfRegNum()

Map a target register to an equivalent dwarf register number.

Returns -1 if there is no equivalent value. The second parameter allows targets to use different numberings for EH info and debugging info.

Definition at line 67 of file MCRegisterInfo.cpp.

References llvm::MCRegisterInfo::DwarfLLVMRegPair::FromReg, I, llvm::lower_bound(), Size, and llvm::MCRegisterInfo::DwarfLLVMRegPair::ToReg.

Referenced by llvm::DwarfExpression::addMachineReg(), llvm::ARMFrameLowering::adjustForSegmentedStacks(), llvm::AArch64InstrInfo::buildOutlinedFrame(), createAArch64MCAsmInfo(), createARMMCAsmInfo(), createHexagonMCAsmInfo(), createMipsMCAsmInfo(), createPPCMCAsmInfo(), createSparcMCAsmInfo(), createSparcV9MCAsmInfo(), createSystemZMCAsmInfo(), createX86MCAsmInfo(), llvm::AArch64FrameLowering::emitCalleeSavedFrameMoves(), llvm::X86FrameLowering::emitCalleeSavedFrameMoves(), llvm::Thumb1FrameLowering::emitPrologue(), llvm::Mips16FrameLowering::emitPrologue(), llvm::MipsSEFrameLowering::emitPrologue(), llvm::XCoreFrameLowering::emitPrologue(), llvm::ARMFrameLowering::emitPrologue(), llvm::ARCFrameLowering::emitPrologue(), llvm::SystemZFrameLowering::emitPrologue(), llvm::PPCFrameLowering::emitPrologue(), getCIEVersion(), getDwarfRegNum(), getDwarfRegNumFromDwarfEHRegNum(), and IsSmallMemAccess().

◆ getDwarfRegNumFromDwarfEHRegNum()

| int MCRegisterInfo::getDwarfRegNumFromDwarfEHRegNum | ( | unsigned | RegNum | ) | const |

Map a target EH register number to an equivalent DWARF register number.

Definition at line 105 of file MCRegisterInfo.cpp.

References getDwarfRegNum(), and getLLVMRegNumFromEH().

◆ getEncodingValue()

|

inline |

Returns the encoding for RegNo.

Definition at line 443 of file MCRegisterInfo.h.

References assert().

Referenced by llvm::AArch64InstrInfo::copyGPRRegTuple(), llvm::PPCInstrInfo::copyPhysReg(), llvm::MipsTargetELFStreamer::emitFrame(), llvm::MSP430MCCodeEmitter::encodeInstruction(), expandNOVLXLoad(), expandNOVLXStore(), llvm::X86InstrInfo::expandPostRAPseudo(), llvm::PPCMCCodeEmitter::get_crbitm_encoding(), GetAEABIUnwindPersonalityName(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), llvm::X86TargetLowering::getRegForInlineAsmConstraint(), llvm::MipsMCCodeEmitter::getRegisterListOpValue(), getTag(), llvm::PPCMCCodeEmitter::getTLSRegEncoding(), HandleVRSaveUpdate(), HasConditionalBranch(), llvm::AArch64_MC::initLLVMToCVRegMapping(), llvm::X86_MC::initLLVMToSEHAndCVRegMapping(), llvm::ARMBaseInstrInfo::isLoadFromStackSlotPostFE(), LowerADJUST_TRAMPOLINE(), LowerLargeShift(), makeCombineInst(), llvm::PPCInstPrinter::printOperand(), llvm::ARMInstPrinter::printRegisterList(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::MipsAsmPrinter::printSavedRegsBitmask(), llvm::ARMFrameLowering::ResolveFrameIndexReference(), llvm::MipsRegInfoRecord::SetPhysRegUsed(), llvm::AArch64ExternalSymbolizer::tryAddingSymbolicOperand(), and llvm::tryFoldSPUpdateIntoPushPop().

◆ getLLVMRegNum()

Map a dwarf register back to a target register.

Definition at line 80 of file MCRegisterInfo.cpp.

References assert(), llvm::MCRegisterInfo::DwarfLLVMRegPair::FromReg, I, llvm::lower_bound(), Size, and llvm::MCRegisterInfo::DwarfLLVMRegPair::ToReg.

Referenced by getDwarfRegNum(), llvm::X86AsmInstrumentation::GetFrameRegGeneric(), llvm::prettyPrintRegisterOp(), and printCFIRegister().

◆ getLLVMRegNumFromEH()

| int MCRegisterInfo::getLLVMRegNumFromEH | ( | unsigned | RegNum | ) | const |

Map a DWARF EH register back to a target register (same as getLLVMRegNum(RegNum, true)) but return -1 if there is no mapping, rather than asserting that there must be one.

Definition at line 92 of file MCRegisterInfo.cpp.

References llvm::MCRegisterInfo::DwarfLLVMRegPair::FromReg, I, llvm::lower_bound(), Size, and llvm::MCRegisterInfo::DwarfLLVMRegPair::ToReg.

Referenced by getDwarfRegNumFromDwarfEHRegNum(), and printDwarfFileDirective().

◆ getMatchingSuperReg()

| unsigned MCRegisterInfo::getMatchingSuperReg | ( | unsigned | Reg, |

| unsigned | SubIdx, | ||

| const MCRegisterClass * | RC | ||

| ) | const |

Return a super-register of the specified register Reg so its sub-register of index SubIdx is Reg.

Definition at line 24 of file MCRegisterInfo.cpp.

References llvm::MCRegisterClass::contains(), getSubReg(), and llvm::MCRegisterInfo::DiffListIterator::isValid().

Referenced by llvm::AMDGPUDisassembler::convertMIMGInst(), llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::ARMInstPrinter::printInst(), and llvm::AArch64InstPrinter::printVectorList().

◆ getName()

Return the human-readable symbolic target-specific name for the specified physical register.

Definition at line 371 of file MCRegisterInfo.h.

References Name.

Referenced by llvm::mca::RegisterFile::addRegisterWrite(), llvm::mca::RegisterFile::cycleStart(), llvm::mca::RegisterFile::dump(), EmitGCCInlineAsmStr(), getCodeViewRegNum(), llvm::HexagonEvaluator::getPhysRegBitWidth(), getRegisterName(), isACalleeSavedRegister(), llvm::prettyPrintRegisterOp(), llvm::printReg(), llvm::printRegUnit(), llvm::HexagonMCChecker::reportBranchErrors(), llvm::HexagonMCChecker::reportErrorNewValue(), llvm::HexagonMCChecker::reportErrorRegisters(), llvm::mca::RegisterFile::tryEliminateMove(), and llvm::mca::verifyOperands().

◆ getNumRegClasses()

|

inline |

Definition at line 427 of file MCRegisterInfo.h.

◆ getNumRegs()

|

inline |

Return the number of registers this target has (useful for sizing arrays holding per register information)

Definition at line 377 of file MCRegisterInfo.h.

Referenced by addLiveInRegs(), llvm::MachineFunction::allocateRegMask(), llvm::PPCFrameLowering::assignCalleeSavedSpillSlots(), llvm::ScheduleDAGInstrs::buildSchedGraph(), llvm::calculateDbgEntityHistory(), llvm::CCState::CCState(), llvm::TargetRegisterInfo::checkAllSuperRegsMarked(), llvm::LiveIntervals::checkRegMaskInterference(), llvm::HexagonBlockRanges::computeDeadMap(), llvm::createRegUsageInfoCollector(), CriticalPathStep(), llvm::TargetFrameLowering::determineCalleeSaves(), llvm::mca::RegisterFile::dump(), llvm::HexagonBlockRanges::expandToSubRegs(), llvm::MachineRegisterInfo::freezeReservedRegs(), llvm::rdf::PhysicalRegisterInfo::getAliasSet(), llvm::TargetRegisterInfo::getAllocatableSet(), getCodeViewRegNum(), getDwarfRegNum(), getMOVL(), llvm::rdf::DataFlowGraph::getNextShadow(), llvm::MachineFrameInfo::getPristineRegs(), getSubRegIndex(), llvm::LivePhysRegs::init(), llvm::LiveRegSet::init(), INITIALIZE_PASS(), InstructionStoresToFI(), llvm::MachineOperand::isIdenticalTo(), llvm::LivePhysRegs::LivePhysRegs(), llvm::MachineRegisterInfo::MachineRegisterInfo(), llvm::CriticalAntiDepBreaker::Observe(), llvm::AggressiveAntiDepBreaker::Observe(), llvm::rdf::PhysicalRegisterInfo::PhysicalRegisterInfo(), llvm::PhysicalRegisterUsageInfo::print(), llvm::MachineOperand::print(), printCustomRegMask(), llvm::printReg(), llvm::TargetRegisterInfo::regmaskSubsetEqual(), llvm::InterferenceCache::reinitPhysRegEntries(), llvm::RegisterClassInfo::runOnMachineFunction(), llvm::ExecutionDomainFix::runOnMachineFunction(), llvm::CriticalAntiDepBreaker::StartBlock(), llvm::AggressiveAntiDepBreaker::StartBlock(), and UpdatePredRedefs().

◆ getNumRegUnits()

|

inline |

Return the number of (native) register units in the target.

Register units are numbered from 0 to getNumRegUnits() - 1. They can be accessed through MCRegUnitIterator defined below.

Definition at line 391 of file MCRegisterInfo.h.

References getDwarfRegNum().

Referenced by llvm::LiveRegUnits::addRegsInMask(), llvm::LiveRegUnits::init(), INITIALIZE_PASS(), llvm::LiveRegMatrix::LiveRegMatrix(), matchPair(), llvm::rdf::PhysicalRegisterInfo::PhysicalRegisterInfo(), llvm::LiveIntervals::print(), llvm::printRegUnit(), pushDepHeight(), llvm::LiveRegUnits::removeRegsNotPreserved(), llvm::ReachingDefAnalysis::runOnMachineFunction(), and llvm::LiveIntervals::runOnMachineFunction().

◆ getNumSubRegIndices()

|

inline |

Return the number of sub-register indices understood by the target.

Index 0 is reserved for the no-op sub-register, while 1 to getNumSubRegIndices() - 1 represent real sub-registers.

Definition at line 384 of file MCRegisterInfo.h.

Referenced by llvm::SplitEditor::dump(), llvm::AVRInstPrinter::getPrettyRegisterName(), getSubReg(), getSubRegIdxOffset(), and getSubRegIdxSize().

◆ getProgramCounter()

|

inline |

Return the register which is the program counter.

Definition at line 328 of file MCRegisterInfo.h.

Referenced by llvm::MCInstrDesc::mayAffectControlFlow().

◆ getRARegister()

|

inline |

This method should return the register where the return address can be found.

Definition at line 323 of file MCRegisterInfo.h.

Referenced by llvm::MipsAsmPrinter::emitFrameDirective(), and getCIEVersion().

◆ getRegClass()

|

inline |

Returns the register class associated with the enumeration value.

See class MCOperandInfo.

Definition at line 433 of file MCRegisterInfo.h.

References assert().

Referenced by llvm::X86_MC::X86MCInstrAnalysis::clearsSuperRegisters(), llvm::AMDGPUDisassembler::convertMIMGInst(), llvm::mca::RegisterFile::cycleStart(), getReg(), llvm::AMDGPU::getRegOperandSize(), getSpecialRegForName(), llvm::AMDGPU::isSGPR(), llvm::MipsRegInfoRecord::MipsRegInfoRecord(), llvm::ARMInstPrinter::printInst(), llvm::AMDGPUInstPrinter::printRegOperand(), and llvm::AArch64InstPrinter::printVectorList().

◆ getRegClassName()

|

inline |

Definition at line 438 of file MCRegisterInfo.h.

References llvm::MCRegisterClass::NameIdx.

Referenced by llvm::TargetRegisterInfo::getRegClassName().

◆ getSEHRegNum()

| int MCRegisterInfo::getSEHRegNum | ( | unsigned | RegNum | ) | const |

Map a target register to an equivalent SEH register number.

Returns LLVM register number if there is no equivalent value.

Definition at line 120 of file MCRegisterInfo.cpp.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::end(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::find(), and I.

◆ getSubReg()

Returns the physical register number of sub-register "Index" for physical register RegNo.

Return zero if the sub-register does not exist.

Definition at line 32 of file MCRegisterInfo.cpp.

References assert(), getNumSubRegIndices(), llvm::MCRegisterInfo::DiffListIterator::isValid(), and Reg.

Referenced by llvm::ARMBaseInstrInfo::AddDReg(), addExclusiveRegPair(), addSavedGPR(), AddSubReg(), llvm::X86InstrInfo::breakPartialRegDependency(), llvm::AMDGPUDisassembler::convertMIMGInst(), copyHint(), llvm::SparcInstrInfo::copyPhysReg(), llvm::ARMBaseInstrInfo::copyPhysReg(), CriticalPathStep(), definesFullReg(), llvm::X86InstrInfo::expandPostRAPseudo(), GetDSubRegs(), getImplicitSPRUseForDPRUse(), getMatchingSuperReg(), getPairedGPR(), llvm::AVRInstPrinter::getPrettyRegisterName(), llvm::BitTracker::MachineEvaluator::getRegBitWidth(), INITIALIZE_PASS(), llvm::CoalescerPair::isCoalescable(), llvm::AMDGPU::isSGPR(), llvm::MipsSEInstrInfo::loadImmediate(), loadRegPairFromStackSlot(), llvm::rdf::DataFlowGraph::makeRegRef(), llvm::HexagonAsmPrinter::PrintAsmOperand(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::ARMInstPrinter::printGPRPairOperand(), llvm::AArch64InstPrinter::printGPRSeqPairsClassOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::AArch64InstPrinter::printVectorList(), llvm::ARMInstPrinter::printVectorListTwo(), llvm::ARMInstPrinter::printVectorListTwoAllLanes(), llvm::ARMInstPrinter::printVectorListTwoSpaced(), llvm::ARMInstPrinter::printVectorListTwoSpacedAllLanes(), llvm::CoalescerPair::setRegisters(), storeRegPairToStackSlot(), llvm::MachineInstr::substituteRegister(), and llvm::MachineOperand::substPhysReg().

◆ getSubRegIdxOffset()

Get the offset of the bit range covered by a sub-register index.

If an Offset doesn't make sense (the index isn't continuous, or is used to access sub-registers at different offsets), return -1.

Definition at line 61 of file MCRegisterInfo.cpp.

References assert(), getNumSubRegIndices(), and llvm::MCRegisterInfo::SubRegCoveredBits::Offset.

Referenced by llvm::DwarfExpression::addMachineReg(), getDwarfRegNum(), and llvm::TargetInstrInfo::getStackSlotRange().

◆ getSubRegIdxSize()

Get the size of the bit range covered by a sub-register index.

If the index isn't continuous, return the sum of the sizes of its parts. If the index is used to access subregisters of different sizes, return -1.

Definition at line 55 of file MCRegisterInfo.cpp.

References assert(), getNumSubRegIndices(), and llvm::MCRegisterInfo::SubRegCoveredBits::Size.

Referenced by llvm::DwarfExpression::addMachineReg(), llvm::TargetInstrInfo::foldMemoryOperand(), and llvm::TargetInstrInfo::getStackSlotRange().

◆ getSubRegIndex()

For a given register pair, return the sub-register index if the second register is a sub-register of the first.

Return zero otherwise.

Definition at line 44 of file MCRegisterInfo.cpp.

References assert(), getNumRegs(), llvm::MCRegisterInfo::DiffListIterator::isValid(), and Reg.

Referenced by llvm::DwarfExpression::addMachineReg(), CriticalPathStep(), getDwarfRegNum(), INITIALIZE_PASS(), isNopCopy(), and llvm::rdf::PhysicalRegisterInfo::mapTo().

◆ InitMCRegisterInfo()

|

inline |

Initialize MCRegisterInfo, called by TableGen auto-generated routines.

DO NOT USE.

Definition at line 239 of file MCRegisterInfo.h.

References C, D, NC, RA, and llvm::ARCISD::RET.

◆ isSubRegister()

Returns true if RegB is a sub-register of RegA.

Definition at line 450 of file MCRegisterInfo.h.

Referenced by llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterKilled(), CriticalPathStep(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::MCInstrDesc::hasImplicitDefOfPhysReg(), isNopCopy(), and llvm::HexagonMCChecker::reportBranchErrors().

◆ isSubRegisterEq()

Returns true if RegB is a sub-register of RegA or if RegB == RegA.

Definition at line 458 of file MCRegisterInfo.h.

Referenced by llvm::MCInstrDesc::hasDefOfPhysReg(), and isMatchingOrAlias().

◆ isSuperOrSubRegisterEq()

Returns true if RegB is a super-register or sub-register of RegA or if RegB == RegA.

Definition at line 470 of file MCRegisterInfo.h.

◆ isSuperRegister()

Returns true if RegB is a super-register of RegA.

Definition at line 546 of file MCRegisterInfo.h.

References I.

Referenced by llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterKilled(), llvm::ARMBaseInstrInfo::breakPartialRegDependency(), CriticalPathStep(), llvm::mca::RegisterFile::cycleStart(), getDwarfRegNum(), INITIALIZE_PASS(), and InstructionStoresToFI().

◆ isSuperRegisterEq()

Returns true if RegB is a super-register of RegA or if RegB == RegA.

Definition at line 464 of file MCRegisterInfo.h.

Referenced by llvm::MachineOperandIteratorBase::analyzePhysReg().

◆ mapDwarfRegsToLLVMRegs()

|

inline |

Used to initialize Dwarf register to LLVM register number mapping.

Called by TableGen auto-generated routines. DO NOT USE.

Definition at line 297 of file MCRegisterInfo.h.

References Size.

◆ mapLLVMRegsToDwarfRegs()

|

inline |

Used to initialize LLVM register to Dwarf register number mapping.

Called by TableGen auto-generated routines. DO NOT USE.

Definition at line 283 of file MCRegisterInfo.h.

References Size.

◆ mapLLVMRegToCVReg()

|

inline |

Definition at line 317 of file MCRegisterInfo.h.

Referenced by llvm::AArch64_MC::initLLVMToCVRegMapping(), and llvm::X86_MC::initLLVMToSEHAndCVRegMapping().

◆ mapLLVMRegToSEHReg()

|

inline |

mapLLVMRegToSEHReg - Used to initialize LLVM register to SEH register number mapping.

By default the SEH register number is just the same as the LLVM register number. FIXME: TableGen these numbers. Currently this requires target specific initialization code.

Definition at line 313 of file MCRegisterInfo.h.

Referenced by llvm::X86_MC::initLLVMToSEHAndCVRegMapping().

◆ operator[]()

|

inline |

Definition at line 332 of file MCRegisterInfo.h.

References assert().

◆ regclass_begin()

|

inline |

Definition at line 421 of file MCRegisterInfo.h.

◆ regclass_end()

|

inline |

Definition at line 422 of file MCRegisterInfo.h.

◆ regclasses()

|

inline |

Definition at line 423 of file MCRegisterInfo.h.

References llvm::make_range().

Friends And Related Function Documentation

◆ MCRegUnitIterator

|

friend |

Definition at line 233 of file MCRegisterInfo.h.

◆ MCRegUnitMaskIterator

|

friend |

Definition at line 234 of file MCRegisterInfo.h.

◆ MCRegUnitRootIterator

|

friend |

Definition at line 235 of file MCRegisterInfo.h.

◆ MCSubRegIndexIterator

|

friend |

Definition at line 231 of file MCRegisterInfo.h.

◆ MCSubRegIterator

|

friend |

Definition at line 230 of file MCRegisterInfo.h.

◆ MCSuperRegIterator

|

friend |

Definition at line 232 of file MCRegisterInfo.h.

The documentation for this class was generated from the following files:

- include/llvm/MC/MCRegisterInfo.h

- lib/MC/MCRegisterInfo.cpp

1.8.13

1.8.13