#include "Target/AMDGPU/AMDGPUTargetTransformInfo.h"

Additional Inherited Members | |

Protected Types inherited from llvm::TargetTransformInfoImplBase Protected Types inherited from llvm::TargetTransformInfoImplBase | |

| typedef TargetTransformInfo | TTI |

Protected Member Functions inherited from llvm::BasicTTIImplBase< GCNTTIImpl > Protected Member Functions inherited from llvm::BasicTTIImplBase< GCNTTIImpl > | |

| BasicTTIImplBase (const TargetMachine *TM, const DataLayout &DL) | |

Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< GCNTTIImpl > Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< GCNTTIImpl > | |

| TargetTransformInfoImplCRTPBase (const DataLayout &DL) | |

Protected Member Functions inherited from llvm::TargetTransformInfoImplBase Protected Member Functions inherited from llvm::TargetTransformInfoImplBase | |

| TargetTransformInfoImplBase (const DataLayout &DL) | |

| unsigned | minRequiredElementSize (const Value *Val, bool &isSigned) |

| bool | isStridedAccess (const SCEV *Ptr) |

| const SCEVConstant * | getConstantStrideStep (ScalarEvolution *SE, const SCEV *Ptr) |

| bool | isConstantStridedAccessLessThan (ScalarEvolution *SE, const SCEV *Ptr, int64_t MergeDistance) |

Protected Attributes inherited from llvm::TargetTransformInfoImplBase Protected Attributes inherited from llvm::TargetTransformInfoImplBase | |

| const DataLayout & | DL |

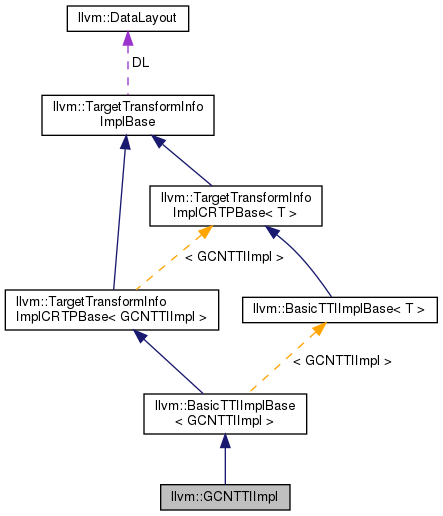

Detailed Description

Definition at line 59 of file AMDGPUTargetTransformInfo.h.

Constructor & Destructor Documentation

◆ GCNTTIImpl()

|

inlineexplicit |

Definition at line 119 of file AMDGPUTargetTransformInfo.h.

Member Function Documentation

◆ areInlineCompatible()

Definition at line 611 of file AMDGPUTargetTransformInfo.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), llvm::TargetMachine::getSubtargetImpl(), and llvm::SystemZISD::TM.

◆ getArithmeticInstrCost()

| int GCNTTIImpl::getArithmeticInstrCost | ( | unsigned | Opcode, |

| Type * | Ty, | ||

| TTI::OperandValueKind | Opd1Info = TTI::OK_AnyValue, |

||

| TTI::OperandValueKind | Opd2Info = TTI::OK_AnyValue, |

||

| TTI::OperandValueProperties | Opd1PropInfo = TTI::OP_None, |

||

| TTI::OperandValueProperties | Opd2PropInfo = TTI::OP_None, |

||

| ArrayRef< const Value *> | Args = ArrayRef<const Value *>() |

||

| ) |

Definition at line 337 of file AMDGPUTargetTransformInfo.cpp.

References llvm::ISD::ADD, llvm::ISD::AND, llvm::TargetTransformInfoImplBase::DL, llvm::ArrayRef< T >::empty(), llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FADD, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FREM, llvm::ISD::FSUB, llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getArithmeticInstrCost(), llvm::MVT::i64, llvm::EVT::isSimple(), llvm::AArch64CC::LT, llvm::PatternMatch::m_FPOne(), llvm::PatternMatch::match(), llvm::ISD::MUL, llvm::ISD::OR, llvm::ISD::SHL, llvm::AMDGPUSubtarget::SOUTHERN_ISLANDS, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ARM_MB::ST, llvm::ISD::SUB, and llvm::ISD::XOR.

◆ getArithmeticReductionCost()

Definition at line 458 of file AMDGPUTargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getArithmeticReductionCost(), llvm::EVT::getScalarSizeInBits(), llvm::AArch64CC::LT, and llvm::ARM_MB::ST.

◆ getCFInstrCost()

Definition at line 447 of file AMDGPUTargetTransformInfo.cpp.

References llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getCFInstrCost(), and llvm::MipsISD::Ret.

◆ getFlatAddressSpace()

|

inline |

Definition at line 176 of file AMDGPUTargetTransformInfo.h.

References AMDGPUAS::FLAT_ADDRESS, llvm::GCNSubtarget::hasFlatAddressSpace(), and AMDGPUAS::UNKNOWN_ADDRESS_SPACE.

◆ getHardwareNumberOfRegisters()

Definition at line 213 of file AMDGPUTargetTransformInfo.cpp.

◆ getInliningThresholdMultiplier()

|

inline |

Definition at line 193 of file AMDGPUTargetTransformInfo.h.

References llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getArithmeticReductionCost(), and llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getMinMaxReductionCost().

◆ getLoadStoreVecRegBitWidth()

Definition at line 254 of file AMDGPUTargetTransformInfo.cpp.

References AMDGPUAS::CONSTANT_ADDRESS, AMDGPUAS::CONSTANT_ADDRESS_32BIT, AMDGPUAS::FLAT_ADDRESS, AMDGPUAS::GLOBAL_ADDRESS, llvm_unreachable, AMDGPUAS::LOCAL_ADDRESS, AMDGPUAS::PRIVATE_ADDRESS, AMDGPUAS::REGION_ADDRESS, and llvm::ARM_MB::ST.

◆ getLoadVectorFactor()

| unsigned GCNTTIImpl::getLoadVectorFactor | ( | unsigned | VF, |

| unsigned | LoadSize, | ||

| unsigned | ChainSizeInBytes, | ||

| VectorType * | VecTy | ||

| ) | const |

Definition at line 233 of file AMDGPUTargetTransformInfo.cpp.

References llvm::Type::getScalarSizeInBits().

◆ getMaxInterleaveFactor()

Definition at line 297 of file AMDGPUTargetTransformInfo.cpp.

◆ getMinMaxReductionCost()

| int GCNTTIImpl::getMinMaxReductionCost | ( | Type * | Ty, |

| Type * | CondTy, | ||

| bool | IsPairwiseForm, | ||

| bool | IsUnsigned | ||

| ) |

Definition at line 473 of file AMDGPUTargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::DL, llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getMinMaxReductionCost(), llvm::EVT::getScalarSizeInBits(), llvm::AArch64CC::LT, and llvm::ARM_MB::ST.

◆ getMinVectorRegisterBitWidth()

| unsigned GCNTTIImpl::getMinVectorRegisterBitWidth | ( | ) | const |

Definition at line 229 of file AMDGPUTargetTransformInfo.cpp.

◆ getNumberOfRegisters()

Definition at line 219 of file AMDGPUTargetTransformInfo.cpp.

◆ getPopcntSupport()

|

inline |

Definition at line 131 of file AMDGPUTargetTransformInfo.h.

References llvm::AMDGPU::HSAMD::Kernel::Key::Args, assert(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getArithmeticInstrCost(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getCFInstrCost(), llvm::TargetTransformInfoImplBase::getLoadStoreVecRegBitWidth(), llvm::TargetTransformInfoImplBase::getLoadVectorFactor(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getMaxInterleaveFactor(), llvm::TargetTransformInfoImplBase::getMinVectorRegisterBitWidth(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getNumberOfRegisters(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getRegisterBitWidth(), llvm::TargetTransformInfoImplBase::getStoreVectorFactor(), llvm::TargetTransformInfoImplBase::getTgtMemIntrinsic(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getVectorInstrCost(), Info, llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isAlwaysUniform(), llvm::TargetTransformInfoImplBase::isLegalToVectorizeLoadChain(), llvm::TargetTransformInfoImplBase::isLegalToVectorizeStoreChain(), llvm::isPowerOf2_32(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isSourceOfDivergence(), llvm::TargetTransformInfo::OK_AnyValue, llvm::TargetTransformInfo::OP_None, and llvm::TargetTransformInfo::PSK_FastHardware.

◆ getRegisterBitWidth()

Definition at line 225 of file AMDGPUTargetTransformInfo.cpp.

◆ getShuffleCost()

| unsigned GCNTTIImpl::getShuffleCost | ( | TTI::ShuffleKind | Kind, |

| Type * | Tp, | ||

| int | Index, | ||

| Type * | SubTp | ||

| ) |

Definition at line 588 of file AMDGPUTargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::DL, llvm::SequentialType::getElementType(), llvm::SequentialType::getNumElements(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getShuffleCost(), llvm::DataLayout::getTypeSizeInBits(), llvm::TargetTransformInfo::SK_Broadcast, llvm::TargetTransformInfo::SK_PermuteSingleSrc, llvm::TargetTransformInfo::SK_Reverse, and llvm::ARM_MB::ST.

◆ getStoreVectorFactor()

| unsigned GCNTTIImpl::getStoreVectorFactor | ( | unsigned | VF, |

| unsigned | StoreSize, | ||

| unsigned | ChainSizeInBytes, | ||

| VectorType * | VecTy | ||

| ) | const |

Definition at line 244 of file AMDGPUTargetTransformInfo.cpp.

◆ getTgtMemIntrinsic()

| bool GCNTTIImpl::getTgtMemIntrinsic | ( | IntrinsicInst * | Inst, |

| MemIntrinsicInfo & | Info | ||

| ) | const |

Definition at line 306 of file AMDGPUTargetTransformInfo.cpp.

References llvm::Intrinsic::amdgcn_atomic_dec, llvm::Intrinsic::amdgcn_atomic_inc, llvm::Intrinsic::amdgcn_ds_fadd, llvm::Intrinsic::amdgcn_ds_fmax, llvm::Intrinsic::amdgcn_ds_fmin, llvm::Intrinsic::amdgcn_ds_ordered_add, llvm::Intrinsic::amdgcn_ds_ordered_swap, llvm::dyn_cast(), llvm::CallBase::getArgOperand(), llvm::IntrinsicInst::getIntrinsicID(), llvm::ConstantInt::getZExtValue(), llvm::MemIntrinsicInfo::IsVolatile, llvm::MemIntrinsicInfo::Ordering, llvm::MemIntrinsicInfo::PtrVal, llvm::MemIntrinsicInfo::ReadMem, llvm::SequentiallyConsistent, and llvm::MemIntrinsicInfo::WriteMem.

◆ getUnrollingPreferences()

| void GCNTTIImpl::getUnrollingPreferences | ( | Loop * | L, |

| ScalarEvolution & | SE, | ||

| TTI::UnrollingPreferences & | UP | ||

| ) |

Definition at line 624 of file AMDGPUTargetTransformInfo.cpp.

◆ getVectorInstrCost()

Definition at line 489 of file AMDGPUTargetTransformInfo.cpp.

References llvm::TargetTransformInfoImplBase::DL, llvm::DataLayout::getTypeSizeInBits(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getVectorInstrCost(), and llvm::ARM_MB::ST.

◆ getVectorSplitCost()

|

inline |

Definition at line 185 of file AMDGPUTargetTransformInfo.h.

References llvm::TargetTransformInfoImplBase::areInlineCompatible(), Callee, llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getShuffleCost(), and Kind.

◆ hasBranchDivergence()

|

inline |

Definition at line 126 of file AMDGPUTargetTransformInfo.h.

References llvm::AMDGPUTTIImpl::getUnrollingPreferences().

◆ isAlwaysUniform()

Definition at line 575 of file AMDGPUTargetTransformInfo.cpp.

References llvm::Intrinsic::amdgcn_readfirstlane, and llvm::Intrinsic::amdgcn_readlane.

◆ isLegalToVectorizeLoadChain()

| bool GCNTTIImpl::isLegalToVectorizeLoadChain | ( | unsigned | ChainSizeInBytes, |

| unsigned | Alignment, | ||

| unsigned | AddrSpace | ||

| ) | const |

Definition at line 285 of file AMDGPUTargetTransformInfo.cpp.

◆ isLegalToVectorizeMemChain()

| bool GCNTTIImpl::isLegalToVectorizeMemChain | ( | unsigned | ChainSizeInBytes, |

| unsigned | Alignment, | ||

| unsigned | AddrSpace | ||

| ) | const |

Definition at line 272 of file AMDGPUTargetTransformInfo.cpp.

References AMDGPUAS::PRIVATE_ADDRESS, and llvm::ARM_MB::ST.

◆ isLegalToVectorizeStoreChain()

| bool GCNTTIImpl::isLegalToVectorizeStoreChain | ( | unsigned | ChainSizeInBytes, |

| unsigned | Alignment, | ||

| unsigned | AddrSpace | ||

| ) | const |

Definition at line 291 of file AMDGPUTargetTransformInfo.cpp.

◆ isSourceOfDivergence()

- Returns

- true if the result of the value could potentially be different across workitems in a wavefront.

Definition at line 544 of file AMDGPUTargetTransformInfo.cpp.

References AMDGPUAS::FLAT_ADDRESS, isArgPassedInSGPR(), llvm::AMDGPU::isIntrinsicSourceOfDivergence(), llvm::SPII::Load, and AMDGPUAS::PRIVATE_ADDRESS.

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPUTargetTransformInfo.h

- lib/Target/AMDGPU/AMDGPUTargetTransformInfo.cpp

1.8.13

1.8.13