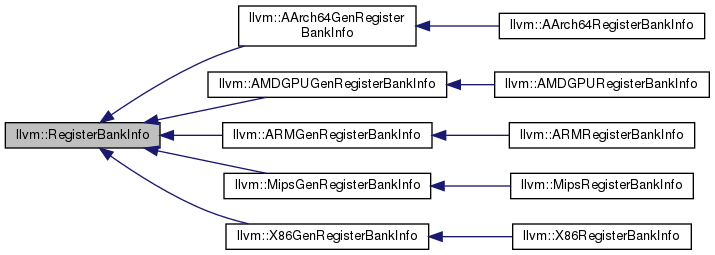

Holds all the information related to register banks. More...

#include "llvm/CodeGen/GlobalISel/RegisterBankInfo.h"

Classes | |

| class | InstructionMapping |

| Helper class that represents how the value of an instruction may be mapped and what is the related cost of such mapping. More... | |

| class | OperandsMapper |

| Helper class used to get/create the virtual registers that will be used to replace the MachineOperand when applying a mapping. More... | |

| struct | PartialMapping |

| Helper struct that represents how a value is partially mapped into a register. More... | |

| struct | ValueMapping |

| Helper struct that represents how a value is mapped through different register banks. More... | |

Public Types | |

| using | InstructionMappings = SmallVector< const InstructionMapping *, 4 > |

| Convenient type to represent the alternatives for mapping an instruction. More... | |

Static Public Member Functions | |

| static void | applyDefaultMapping (const OperandsMapper &OpdMapper) |

| Helper method to apply something that is like the default mapping. More... | |

| static const TargetRegisterClass * | constrainGenericRegister (unsigned Reg, const TargetRegisterClass &RC, MachineRegisterInfo &MRI) |

Constrain the (possibly generic) virtual register Reg to RC. More... | |

Public Attributes | |

| struct llvm::RegisterBankInfo::PartialMapping | ScalarAddx2 |

| VectorAdd | |

Get the possible mapping for MI. More... | |

Static Public Attributes | |

| static const unsigned | DefaultMappingID = UINT_MAX |

| Identifier used when the related instruction mapping instance is generated by target independent code. More... | |

| static const unsigned | InvalidMappingID = UINT_MAX - 1 |

| Identifier used when the related instruction mapping instance is generated by the default constructor. More... | |

Protected Member Functions | |

| RegisterBankInfo (RegisterBank **RegBanks, unsigned NumRegBanks) | |

Create a RegisterBankInfo that can accommodate up to NumRegBanks RegisterBank instances. More... | |

| RegisterBankInfo () | |

| This constructor is meaningless. More... | |

| RegisterBank & | getRegBank (unsigned ID) |

Get the register bank identified by ID. More... | |

| const TargetRegisterClass & | getMinimalPhysRegClass (unsigned Reg, const TargetRegisterInfo &TRI) const |

| Get the MinimalPhysRegClass for Reg. More... | |

| const InstructionMapping & | getInstrMappingImpl (const MachineInstr &MI) const |

Try to get the mapping of MI. More... | |

| const PartialMapping & | getPartialMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| Get the uniquely generated PartialMapping for the given arguments. More... | |

Methods to get a uniquely generated ValueMapping. | |

| const ValueMapping & | getValueMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| The most common ValueMapping consists of a single PartialMapping. More... | |

| const ValueMapping & | getValueMapping (const PartialMapping *BreakDown, unsigned NumBreakDowns) const |

| Get the ValueMapping for the given arguments. More... | |

Methods to get a uniquely generated array of ValueMapping. | |

| template<typename Iterator > | |

| const ValueMapping * | getOperandsMapping (Iterator Begin, Iterator End) const |

Get the uniquely generated array of ValueMapping for the elements of between Begin and End. More... | |

| const ValueMapping * | getOperandsMapping (const SmallVectorImpl< const ValueMapping *> &OpdsMapping) const |

Get the uniquely generated array of ValueMapping for the elements of OpdsMapping. More... | |

| const ValueMapping * | getOperandsMapping (std::initializer_list< const ValueMapping *> OpdsMapping) const |

| Get the uniquely generated array of ValueMapping for the given arguments. More... | |

Protected Attributes | |

| RegisterBank ** | RegBanks |

| Hold the set of supported register banks. More... | |

| unsigned | NumRegBanks |

| Total number of register banks. More... | |

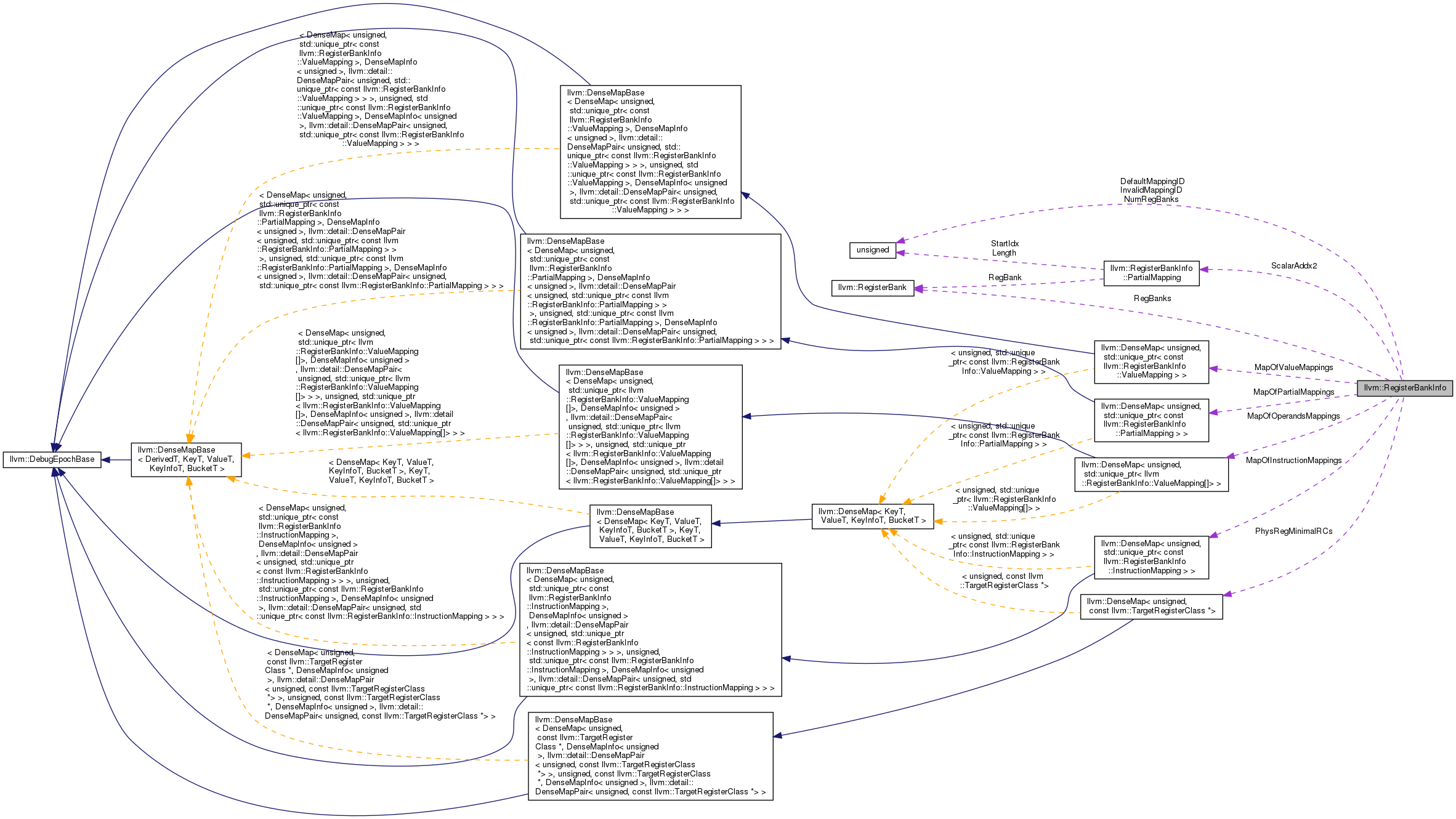

| DenseMap< unsigned, std::unique_ptr< const PartialMapping > > | MapOfPartialMappings |

| Keep dynamically allocated PartialMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const ValueMapping > > | MapOfValueMappings |

| Keep dynamically allocated ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< ValueMapping[]> > | MapOfOperandsMappings |

| Keep dynamically allocated array of ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const InstructionMapping > > | MapOfInstructionMappings |

| Keep dynamically allocated InstructionMapping in a separate map. More... | |

| DenseMap< unsigned, const TargetRegisterClass * > | PhysRegMinimalRCs |

| Getting the minimal register class of a physreg is expensive. More... | |

Methods to get a uniquely generated InstructionMapping. | |

| const InstructionMapping & | getInstructionMapping (unsigned ID, unsigned Cost, const ValueMapping *OperandsMapping, unsigned NumOperands) const |

| Method to get a uniquely generated InstructionMapping. More... | |

| const InstructionMapping & | getInvalidInstructionMapping () const |

| Method to get a uniquely generated invalid InstructionMapping. More... | |

Detailed Description

Holds all the information related to register banks.

Definition at line 38 of file RegisterBankInfo.h.

Member Typedef Documentation

◆ InstructionMappings

Convenient type to represent the alternatives for mapping an instruction.

- Todo:

- When we move to TableGen this should be an array ref.

Definition at line 274 of file RegisterBankInfo.h.

Constructor & Destructor Documentation

◆ RegisterBankInfo() [1/2]

|

protected |

Create a RegisterBankInfo that can accommodate up to NumRegBanks RegisterBank instances.

Definition at line 59 of file RegisterBankInfo.cpp.

◆ RegisterBankInfo() [2/2]

|

inlineprotected |

This constructor is meaningless.

It just provides a default constructor that can be used at link time when GlobalISel is not built. That way, targets can still inherit from this class without doing crazy gymnastic to avoid link time failures.

- Note

- That works because the constructor is inlined.

Definition at line 425 of file RegisterBankInfo.h.

References llvm_unreachable.

◆ ~RegisterBankInfo()

|

virtualdefault |

Referenced by applyMappingImpl().

Member Function Documentation

◆ applyDefaultMapping()

|

static |

Helper method to apply something that is like the default mapping.

Basically, that means that OpdMapper.getMI() is left untouched aside from the reassignment of the register operand that have been remapped.

The type of all the new registers that have been created by the mapper are properly remapped to the type of the original registers they replace. In other words, the semantic of the instruction does not change, only the register banks.

If the mapping of one of the operand spans several registers, this method will abort as this is not like a default mapping anymore.

- Precondition

- For OpIdx in {0..

OpdMapper.getMI().getNumOperands()) the range OpdMapper.getVRegs(OpIdx) is empty or of size 1.

Definition at line 404 of file RegisterBankInfo.cpp.

References assert(), llvm::dbgs(), llvm::empty(), llvm::RegisterBankInfo::OperandsMapper::getInstrMapping(), llvm::RegisterBankInfo::OperandsMapper::getMI(), getMinimalPhysRegClass(), llvm::RegisterBankInfo::OperandsMapper::getMRI(), llvm::RegisterBankInfo::InstructionMapping::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::TargetRegisterInfo::getRegSizeInBits(), llvm::LLT::getSizeInBits(), llvm::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::RegisterBankInfo::OperandsMapper::getVRegs(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), LLVM_DEBUG, MRI, llvm::RegisterBankInfo::ValueMapping::NumBreakDowns, llvm::printReg(), Reg, llvm::MachineOperand::setReg(), and llvm::MachineRegisterInfo::setType().

Referenced by llvm::applyMapping(), llvm::X86RegisterBankInfo::applyMappingImpl(), llvm::AMDGPURegisterBankInfo::getInstrAlternativeMappings(), llvm::AArch64RegisterBankInfo::getInstrAlternativeMappings(), and getInvalidInstructionMapping().

◆ applyMappingImpl()

|

inlinevirtual |

See applyMapping.

Reimplemented in llvm::X86RegisterBankInfo.

Definition at line 566 of file RegisterBankInfo.h.

References llvm_unreachable, and ~RegisterBankInfo().

Referenced by llvm::applyMapping().

◆ constrainGenericRegister()

|

static |

Constrain the (possibly generic) virtual register Reg to RC.

- Precondition

Regis a virtual register that either has a bank or a class.

- Returns

- The constrained register class, or nullptr if there is none.

- Note

- This is a generic variant of MachineRegisterInfo::constrainRegClass

- Use MachineRegisterInfo::constrainRegAttrs instead for any non-isel purpose, including non-select passes of GlobalISel

Definition at line 128 of file RegisterBankInfo.cpp.

References llvm::MachineRegisterInfo::constrainRegClass(), llvm::RegisterBank::covers(), llvm::MachineRegisterInfo::getRegClassOrRegBank(), and llvm::MachineRegisterInfo::setRegClass().

Referenced by llvm::AMDGPUInstructionSelector::AMDGPUInstructionSelector(), buildEXP(), changeFCMPPredToAArch64CC(), llvm::constrainRegToClass(), copyCost(), getConstant(), and selectCopy().

◆ copyCost()

|

inlinevirtual |

Get the cost of a copy from B to A, or put differently, get the cost of A = COPY B.

Since register banks may cover different size, Size specifies what will be the size in bits that will be copied around.

- Note

- Since this is a copy, both registers have the same size.

Reimplemented in llvm::AArch64RegisterBankInfo, and llvm::AMDGPURegisterBankInfo.

Definition at line 612 of file RegisterBankInfo.h.

References B, and constrainGenericRegister().

Referenced by llvm::AMDGPURegisterBankInfo::copyCost(), llvm::AArch64RegisterBankInfo::copyCost(), and llvm::RegBankSelect::getAnalysisUsage().

◆ getInstrAlternativeMappings()

|

virtual |

Get the alternative mappings for MI.

Alternative in the sense different from getInstrMapping.

Reimplemented in llvm::AArch64RegisterBankInfo, llvm::X86RegisterBankInfo, and llvm::AMDGPURegisterBankInfo.

Definition at line 399 of file RegisterBankInfo.cpp.

Referenced by llvm::AMDGPURegisterBankInfo::getInstrAlternativeMappings(), llvm::X86RegisterBankInfo::getInstrAlternativeMappings(), llvm::AArch64RegisterBankInfo::getInstrAlternativeMappings(), and getInstrMapping().

◆ getInstrMapping()

|

virtual |

Get the mapping of the different operands of MI on the register bank.

This mapping should be the direct translation of MI. In other words, when MI is mapped with the returned mapping, only the register banks of the operands of MI need to be updated. In particular, neither the opcode nor the type of MI needs to be updated for this direct mapping.

The target independent implementation gives a mapping based on the register classes for the target specific opcode. It uses the ID RegisterBankInfo::DefaultMappingID for that mapping. Make sure you do not use that ID for the alternative mapping for MI. See getInstrAlternativeMappings for the alternative mappings.

For instance, if MI is a vector add, the mapping should not be a scalarization of the add.

- Postcondition

- returnedVal.verify(MI).

- Note

- If returnedVal does not verify MI, this would probably mean that the target does not support that instruction.

Reimplemented in llvm::AArch64RegisterBankInfo, llvm::X86RegisterBankInfo, llvm::AMDGPURegisterBankInfo, llvm::ARMRegisterBankInfo, and llvm::MipsRegisterBankInfo.

Definition at line 375 of file RegisterBankInfo.cpp.

References assert(), getInstrAlternativeMappings(), getInstrMappingImpl(), llvm::RegisterBankInfo::InstructionMapping::isValid(), llvm_unreachable, MI, and llvm::SmallVectorTemplateBase< T, bool >::push_back().

Referenced by llvm::RegBankSelect::getAnalysisUsage().

◆ getInstrMappingImpl()

|

protected |

Try to get the mapping of MI.

See getInstrMapping for more details on what a mapping represents.

Unlike getInstrMapping the returned InstructionMapping may be invalid (isValid() == false). This means that the target independent code is not smart enough to get the mapping of MI and thus, the target has to provide the information for MI.

This implementation is able to get the mapping of:

- Target specific instructions by looking at the encoding constraints.

- Any instruction if all the register operands have already been assigned a register, a register class, or a register bank.

- Copies and phis if at least one of the operands has been assigned a register, a register class, or a register bank. In other words, this method will likely fail to find a mapping for any generic opcode that has not been lowered by target specific code.

Definition at line 158 of file RegisterBankInfo.cpp.

References assert(), DefaultMappingID, llvm::TargetSubtargetInfo::getInstrInfo(), getInstructionMapping(), getInvalidInstructionMapping(), llvm::MachineInstr::getMF(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), getOperandsMapping(), llvm::MachineOperand::getReg(), getRegBank(), getRegBankFromConstraints(), llvm::MachineFunction::getRegInfo(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::getSizeInBits(), llvm::MachineFunction::getSubtarget(), getValueMapping(), isCopyLike(), llvm::MachineOperand::isReg(), MRI, Reg, and TII.

Referenced by llvm::ARMRegisterBankInfo::getInstrMapping(), llvm::MipsRegisterBankInfo::getInstrMapping(), llvm::AMDGPURegisterBankInfo::getInstrMapping(), llvm::X86RegisterBankInfo::getInstrMapping(), llvm::AArch64RegisterBankInfo::getInstrMapping(), getInstrMapping(), and getRegBank().

◆ getInstructionMapping()

|

inline |

Method to get a uniquely generated InstructionMapping.

Definition at line 524 of file RegisterBankInfo.h.

Referenced by llvm::AMDGPURegisterBankInfo::getInstrAlternativeMappings(), llvm::X86RegisterBankInfo::getInstrAlternativeMappings(), llvm::AArch64RegisterBankInfo::getInstrAlternativeMappings(), llvm::ARMRegisterBankInfo::getInstrMapping(), llvm::MipsRegisterBankInfo::getInstrMapping(), llvm::AMDGPURegisterBankInfo::getInstrMapping(), llvm::X86RegisterBankInfo::getInstrMapping(), llvm::AArch64RegisterBankInfo::getInstrMapping(), getInstrMappingImpl(), llvm::X86GenRegisterBankInfo::getPartialMappingIdx(), isInstrUniform(), and isPreISelGenericFloatingPointOpcode().

◆ getInvalidInstructionMapping()

|

inline |

Method to get a uniquely generated invalid InstructionMapping.

Definition at line 532 of file RegisterBankInfo.h.

References applyDefaultMapping(), getRegBankFromConstraints(), and TII.

Referenced by llvm::ARMRegisterBankInfo::getInstrMapping(), llvm::MipsRegisterBankInfo::getInstrMapping(), llvm::AMDGPURegisterBankInfo::getInstrMapping(), llvm::X86RegisterBankInfo::getInstrMapping(), llvm::AArch64RegisterBankInfo::getInstrMapping(), and getInstrMappingImpl().

◆ getMinimalPhysRegClass()

|

protected |

Get the MinimalPhysRegClass for Reg.

- Precondition

- Reg is a physical register.

Definition at line 99 of file RegisterBankInfo.cpp.

References assert(), llvm::TargetRegisterInfo::getMinimalPhysRegClass(), llvm::TargetRegisterInfo::isPhysicalRegister(), PhysRegMinimalRCs, and Reg.

Referenced by applyDefaultMapping(), and getRegBank().

◆ getNumRegBanks()

|

inline |

Get the total number of register banks.

Definition at line 587 of file RegisterBankInfo.h.

References NumRegBanks.

Referenced by getRegBank(), and llvm::MIRParserImpl::initializeJumpTableInfo().

◆ getOperandsMapping() [1/3]

|

protected |

Get the uniquely generated array of ValueMapping for the elements of between Begin and End.

Elements that are nullptr will be replaced by invalid ValueMapping (ValueMapping::isValid == false).

- Precondition

- The pointers on ValueMapping between

BeginandEndmust uniquely identify a ValueMapping. Otherwise, there is no guarantee that the return instance will be unique, i.e., another OperandsMapping could have the same content.

Definition at line 298 of file RegisterBankInfo.cpp.

Referenced by llvm::AMDGPURegisterBankInfo::getInstrAlternativeMappings(), llvm::X86RegisterBankInfo::getInstrAlternativeMappings(), llvm::AArch64RegisterBankInfo::getInstrAlternativeMappings(), llvm::ARMRegisterBankInfo::getInstrMapping(), llvm::MipsRegisterBankInfo::getInstrMapping(), llvm::AMDGPURegisterBankInfo::getInstrMapping(), llvm::X86RegisterBankInfo::getInstrMapping(), llvm::AArch64RegisterBankInfo::getInstrMapping(), getInstrMappingImpl(), getOperandsMapping(), getRegBank(), and isInstrUniform().

◆ getOperandsMapping() [2/3]

|

protected |

Get the uniquely generated array of ValueMapping for the elements of OpdsMapping.

Elements of OpdsMapping that are nullptr will be replaced by invalid ValueMapping (ValueMapping::isValid == false).

Definition at line 327 of file RegisterBankInfo.cpp.

References llvm::SmallVectorTemplateCommon< T >::begin(), llvm::SmallVectorTemplateCommon< T >::end(), and getOperandsMapping().

◆ getOperandsMapping() [3/3]

|

protected |

Get the uniquely generated array of ValueMapping for the given arguments.

Arguments that are nullptr will be replaced by invalid ValueMapping (ValueMapping::isValid == false).

◆ getPartialMapping()

|

protected |

Get the uniquely generated PartialMapping for the given arguments.

Definition at line 246 of file RegisterBankInfo.cpp.

References hashPartialMapping(), and MapOfPartialMappings.

Referenced by getRegBank(), and getValueMapping().

◆ getRegBank() [1/3]

|

inlineprotected |

Get the register bank identified by ID.

Definition at line 430 of file RegisterBankInfo.h.

References assert(), getInstrMappingImpl(), getMinimalPhysRegClass(), getNumRegBanks(), getOperandsMapping(), getPartialMapping(), getValueMapping(), llvm::RegisterBankInfo::PartialMapping::Length, MI, Reg, llvm::RegisterBankInfo::PartialMapping::RegBank, llvm::RegisterBankInfo::PartialMapping::StartIdx, and TRI.

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo(), llvm::AMDGPURegisterBankInfo::AMDGPURegisterBankInfo(), llvm::ARMRegisterBankInfo::ARMRegisterBankInfo(), changeFCMPPredToAArch64CC(), llvm::InstructionSelector::executeMatchTable(), llvm::RegBankSelect::getAnalysisUsage(), llvm::AArch64RegisterBankInfo::getInstrMapping(), getInstrMappingImpl(), getRegBank(), llvm::ARMRegisterBankInfo::getRegBankFromRegClass(), llvm::MipsRegisterBankInfo::getRegBankFromRegClass(), llvm::AMDGPURegisterBankInfo::getRegBankFromRegClass(), llvm::X86RegisterBankInfo::getRegBankFromRegClass(), llvm::AArch64RegisterBankInfo::getRegBankFromRegClass(), llvm::MIRParserImpl::initializeJumpTableInfo(), isConstant(), isInstrUniform(), selectCopy(), selectMergeValues(), selectUnmergeValues(), unsupportedBinOp(), and llvm::X86RegisterBankInfo::X86RegisterBankInfo().

◆ getRegBank() [2/3]

|

inline |

Get the register bank identified by ID.

Definition at line 574 of file RegisterBankInfo.h.

References getRegBank(), and MRI.

◆ getRegBank() [3/3]

| const RegisterBank * RegisterBankInfo::getRegBank | ( | unsigned | Reg, |

| const MachineRegisterInfo & | MRI, | ||

| const TargetRegisterInfo & | TRI | ||

| ) | const |

Get the register bank of Reg.

If Reg has not been assigned a register, a register class, or a register bank, then this returns nullptr.

- Precondition

- Reg != 0 (NoRegister)

Definition at line 84 of file RegisterBankInfo.cpp.

References assert(), llvm::PointerUnion< PT1, PT2 >::dyn_cast(), getMinimalPhysRegClass(), getRegBankFromRegClass(), llvm::MachineRegisterInfo::getRegClassOrRegBank(), and llvm::TargetRegisterInfo::isPhysicalRegister().

◆ getRegBankFromConstraints()

| const RegisterBank * RegisterBankInfo::getRegBankFromConstraints | ( | const MachineInstr & | MI, |

| unsigned | OpIdx, | ||

| const TargetInstrInfo & | TII, | ||

| const TargetRegisterInfo & | TRI | ||

| ) | const |

Get the register bank for the OpIdx-th operand of MI form the encoding constraints, if any.

- Returns

- A register bank that covers the register class of the related encoding constraints or nullptr if

MIdid not provide enough information to deduce it.

Definition at line 111 of file RegisterBankInfo.cpp.

References assert(), llvm::RegisterBank::covers(), getRegBankFromRegClass(), and llvm::MachineInstr::getRegClassConstraint().

Referenced by getInstrMappingImpl(), and getInvalidInstructionMapping().

◆ getRegBankFromRegClass()

|

inlinevirtual |

Get a register bank that covers RC.

- Precondition

RCis a user-defined register class (as opposed as one generated by TableGen).

- Note

- The mapping RC -> RegBank could be built while adding the coverage for the register banks. However, we do not do it, because, at least for now, we only need this information for register classes that are used in the description of instruction. In other words, there are just a handful of them and we do not want to waste space.

- Todo:

- This should be TableGen'ed.

Reimplemented in llvm::AArch64RegisterBankInfo, llvm::X86RegisterBankInfo, llvm::AMDGPURegisterBankInfo, llvm::ARMRegisterBankInfo, and llvm::MipsRegisterBankInfo.

Definition at line 602 of file RegisterBankInfo.h.

References llvm_unreachable.

Referenced by llvm::InstructionSelector::executeMatchTable(), getRegBank(), and getRegBankFromConstraints().

◆ getValueMapping() [1/2]

|

protected |

The most common ValueMapping consists of a single PartialMapping.

Feature a method for that.

Definition at line 263 of file RegisterBankInfo.cpp.

References getPartialMapping().

Referenced by getInstrMappingImpl(), and getRegBank().

◆ getValueMapping() [2/2]

|

protected |

Get the ValueMapping for the given arguments.

Definition at line 280 of file RegisterBankInfo.cpp.

References hashValueMapping(), and MapOfValueMappings.

Member Data Documentation

◆ DefaultMappingID

Identifier used when the related instruction mapping instance is generated by target independent code.

Make sure not to use that identifier to avoid possible collision.

Definition at line 635 of file RegisterBankInfo.h.

Referenced by llvm::applyMapping(), llvm::ARMRegisterBankInfo::getInstrMapping(), llvm::MipsRegisterBankInfo::getInstrMapping(), llvm::X86RegisterBankInfo::getInstrMapping(), llvm::AArch64RegisterBankInfo::getInstrMapping(), getInstrMappingImpl(), llvm::X86GenRegisterBankInfo::getPartialMappingIdx(), and isPreISelGenericFloatingPointOpcode().

◆ InvalidMappingID

Identifier used when the related instruction mapping instance is generated by the default constructor.

Make sure not to use that identifier.

Definition at line 640 of file RegisterBankInfo.h.

Referenced by hashInstructionMapping(), llvm::RegisterBankInfo::InstructionMapping::InstructionMapping(), and llvm::RegisterBankInfo::InstructionMapping::isValid().

◆ MapOfInstructionMappings

|

mutableprotected |

Keep dynamically allocated InstructionMapping in a separate map.

This shouldn't be needed when everything gets TableGen'ed.

Definition at line 409 of file RegisterBankInfo.h.

Referenced by hashInstructionMapping().

◆ MapOfOperandsMappings

|

mutableprotected |

Keep dynamically allocated array of ValueMapping in a separate map.

This shouldn't be needed when everything gets TableGen'ed.

Definition at line 404 of file RegisterBankInfo.h.

◆ MapOfPartialMappings

|

mutableprotected |

Keep dynamically allocated PartialMapping in a separate map.

This shouldn't be needed when everything gets TableGen'ed.

Definition at line 394 of file RegisterBankInfo.h.

Referenced by getPartialMapping().

◆ MapOfValueMappings

|

mutableprotected |

Keep dynamically allocated ValueMapping in a separate map.

This shouldn't be needed when everything gets TableGen'ed.

Definition at line 399 of file RegisterBankInfo.h.

Referenced by getValueMapping().

◆ NumRegBanks

|

protected |

Total number of register banks.

Definition at line 389 of file RegisterBankInfo.h.

Referenced by getNumRegBanks().

◆ PhysRegMinimalRCs

|

mutableprotected |

Getting the minimal register class of a physreg is expensive.

Cache this information as we get it.

Definition at line 413 of file RegisterBankInfo.h.

Referenced by getMinimalPhysRegClass().

◆ RegBanks

|

protected |

Hold the set of supported register banks.

Definition at line 386 of file RegisterBankInfo.h.

◆ ScalarAddx2

| struct llvm::RegisterBankInfo::PartialMapping llvm::RegisterBankInfo::ScalarAddx2 |

◆ VectorAdd

| llvm::RegisterBankInfo::VectorAdd |

Get the possible mapping for MI.

A mapping defines where the different operands may live and at what cost. For instance, let us consider: v0(16) = G_ADD <2 x i8> v1, v2 The possible mapping could be:

{/*ID

Definition at line 678 of file RegisterBankInfo.h.

The documentation for this class was generated from the following files:

- include/llvm/CodeGen/GlobalISel/RegisterBankInfo.h

- lib/CodeGen/GlobalISel/RegisterBankInfo.cpp

1.8.13

1.8.13