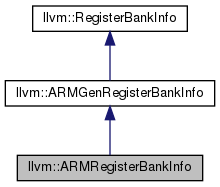

This class provides the information for the target register banks. More...

#include "Target/ARM/ARMRegisterBankInfo.h"

Additional Inherited Members | |

Public Types inherited from llvm::RegisterBankInfo Public Types inherited from llvm::RegisterBankInfo | |

| using | InstructionMappings = SmallVector< const InstructionMapping *, 4 > |

| Convenient type to represent the alternatives for mapping an instruction. More... | |

Static Public Member Functions inherited from llvm::RegisterBankInfo Static Public Member Functions inherited from llvm::RegisterBankInfo | |

| static void | applyDefaultMapping (const OperandsMapper &OpdMapper) |

| Helper method to apply something that is like the default mapping. More... | |

| static const TargetRegisterClass * | constrainGenericRegister (unsigned Reg, const TargetRegisterClass &RC, MachineRegisterInfo &MRI) |

Constrain the (possibly generic) virtual register Reg to RC. More... | |

Public Attributes inherited from llvm::RegisterBankInfo Public Attributes inherited from llvm::RegisterBankInfo | |

| struct llvm::RegisterBankInfo::PartialMapping | ScalarAddx2 |

| VectorAdd | |

Get the possible mapping for MI. More... | |

Static Public Attributes inherited from llvm::RegisterBankInfo Static Public Attributes inherited from llvm::RegisterBankInfo | |

| static const unsigned | DefaultMappingID = UINT_MAX |

| Identifier used when the related instruction mapping instance is generated by target independent code. More... | |

| static const unsigned | InvalidMappingID = UINT_MAX - 1 |

| Identifier used when the related instruction mapping instance is generated by the default constructor. More... | |

Protected Member Functions inherited from llvm::RegisterBankInfo Protected Member Functions inherited from llvm::RegisterBankInfo | |

| RegisterBankInfo (RegisterBank **RegBanks, unsigned NumRegBanks) | |

Create a RegisterBankInfo that can accommodate up to NumRegBanks RegisterBank instances. More... | |

| RegisterBankInfo () | |

| This constructor is meaningless. More... | |

| RegisterBank & | getRegBank (unsigned ID) |

Get the register bank identified by ID. More... | |

| const TargetRegisterClass & | getMinimalPhysRegClass (unsigned Reg, const TargetRegisterInfo &TRI) const |

| Get the MinimalPhysRegClass for Reg. More... | |

| const InstructionMapping & | getInstrMappingImpl (const MachineInstr &MI) const |

Try to get the mapping of MI. More... | |

| const PartialMapping & | getPartialMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| Get the uniquely generated PartialMapping for the given arguments. More... | |

| const ValueMapping & | getValueMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| The most common ValueMapping consists of a single PartialMapping. More... | |

| const ValueMapping & | getValueMapping (const PartialMapping *BreakDown, unsigned NumBreakDowns) const |

| Get the ValueMapping for the given arguments. More... | |

| template<typename Iterator > | |

| const ValueMapping * | getOperandsMapping (Iterator Begin, Iterator End) const |

Get the uniquely generated array of ValueMapping for the elements of between Begin and End. More... | |

| const ValueMapping * | getOperandsMapping (const SmallVectorImpl< const ValueMapping *> &OpdsMapping) const |

Get the uniquely generated array of ValueMapping for the elements of OpdsMapping. More... | |

| const ValueMapping * | getOperandsMapping (std::initializer_list< const ValueMapping *> OpdsMapping) const |

| Get the uniquely generated array of ValueMapping for the given arguments. More... | |

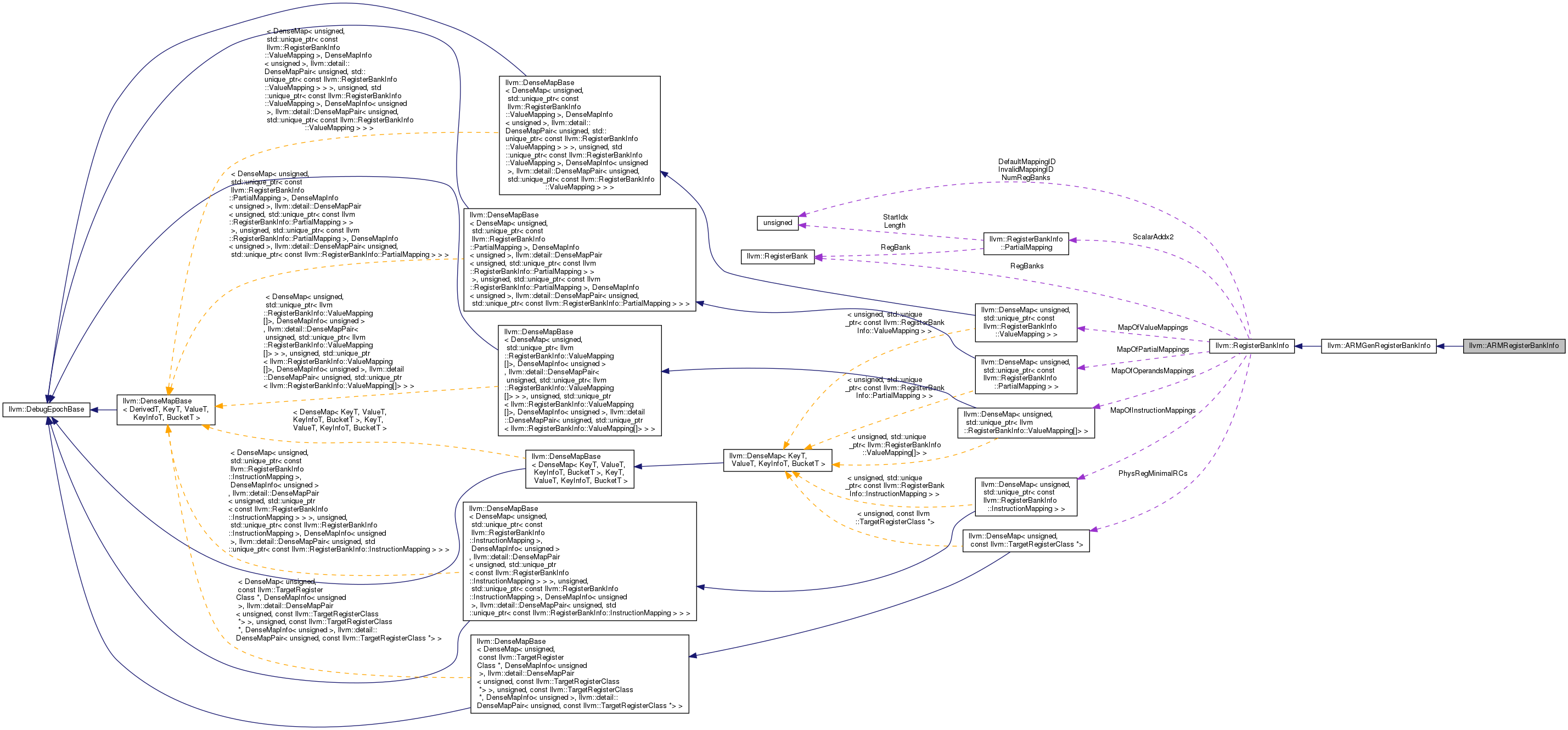

Protected Attributes inherited from llvm::RegisterBankInfo Protected Attributes inherited from llvm::RegisterBankInfo | |

| RegisterBank ** | RegBanks |

| Hold the set of supported register banks. More... | |

| unsigned | NumRegBanks |

| Total number of register banks. More... | |

| DenseMap< unsigned, std::unique_ptr< const PartialMapping > > | MapOfPartialMappings |

| Keep dynamically allocated PartialMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const ValueMapping > > | MapOfValueMappings |

| Keep dynamically allocated ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< ValueMapping[]> > | MapOfOperandsMappings |

| Keep dynamically allocated array of ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const InstructionMapping > > | MapOfInstructionMappings |

| Keep dynamically allocated InstructionMapping in a separate map. More... | |

| DenseMap< unsigned, const TargetRegisterClass * > | PhysRegMinimalRCs |

| Getting the minimal register class of a physreg is expensive. More... | |

Detailed Description

This class provides the information for the target register banks.

Definition at line 32 of file ARMRegisterBankInfo.h.

Constructor & Destructor Documentation

◆ ARMRegisterBankInfo()

| ARMRegisterBankInfo::ARMRegisterBankInfo | ( | const TargetRegisterInfo & | TRI | ) |

Definition at line 133 of file ARMRegisterBankInfo.cpp.

References assert(), llvm::ARM::checkPartialMappings(), llvm::ARM::checkValueMappings(), llvm::RegisterBank::covers(), llvm::RegisterBankInfo::getRegBank(), llvm::TargetRegisterInfo::getRegClass(), and llvm::RegisterBank::getSize().

Member Function Documentation

◆ getInstrMapping()

|

overridevirtual |

Get the mapping of the different operands of MI on the register bank.

This mapping should be the direct translation of MI. In other words, when MI is mapped with the returned mapping, only the register banks of the operands of MI need to be updated. In particular, neither the opcode nor the type of MI needs to be updated for this direct mapping.

The target independent implementation gives a mapping based on the register classes for the target specific opcode. It uses the ID RegisterBankInfo::DefaultMappingID for that mapping. Make sure you do not use that ID for the alternative mapping for MI. See getInstrAlternativeMappings for the alternative mappings.

For instance, if MI is a vector add, the mapping should not be a scalarization of the add.

- Postcondition

- returnedVal.verify(MI).

- Note

- If returnedVal does not verify MI, this would probably mean that the target does not support that instruction.

Reimplemented from llvm::RegisterBankInfo.

Definition at line 201 of file ARMRegisterBankInfo.cpp.

References assert(), llvm::RegisterBankInfo::DefaultMappingID, llvm::ARM::DPR3OpsIdx, llvm::RegisterBankInfo::getInstrMappingImpl(), llvm::RegisterBankInfo::getInstructionMapping(), llvm::RegisterBankInfo::getInvalidInstructionMapping(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::RegisterBankInfo::getOperandsMapping(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::LLT::getSizeInBits(), llvm::MachineFunction::getSubtarget(), llvm::MachineRegisterInfo::getType(), llvm::ARM::GPR3OpsIdx, llvm::isPreISelGenericOpcode(), llvm::RegisterBankInfo::InstructionMapping::isValid(), MRI, Size, llvm::ARM::SPR3OpsIdx, and llvm::ARM::ValueMappings.

◆ getRegBankFromRegClass()

|

overridevirtual |

Get a register bank that covers RC.

- Precondition

RCis a user-defined register class (as opposed as one generated by TableGen).

- Note

- The mapping RC -> RegBank could be built while adding the coverage for the register banks. However, we do not do it, because, at least for now, we only need this information for register classes that are used in the description of instruction. In other words, there are just a handful of them and we do not want to waste space.

- Todo:

- This should be TableGen'ed.

Reimplemented from llvm::RegisterBankInfo.

Definition at line 172 of file ARMRegisterBankInfo.cpp.

References llvm::ARM, llvm::TargetRegisterClass::getID(), llvm::RegisterBankInfo::getRegBank(), and llvm_unreachable.

The documentation for this class was generated from the following files:

- lib/Target/ARM/ARMRegisterBankInfo.h

- lib/Target/ARM/ARMRegisterBankInfo.cpp

1.8.13

1.8.13