|

| virtual void | anchor () |

| |

| | ARMRegisterInfo () |

| |

| const MCPhysReg * | getCalleeSavedRegs (const MachineFunction *MF) const override |

| | Code Generation virtual methods... More...

|

| |

| const MCPhysReg * | getCalleeSavedRegsViaCopy (const MachineFunction *MF) const |

| |

| const uint32_t * | getCallPreservedMask (const MachineFunction &MF, CallingConv::ID) const override |

| |

| const uint32_t * | getNoPreservedMask () const override |

| |

| const uint32_t * | getTLSCallPreservedMask (const MachineFunction &MF) const |

| |

| const uint32_t * | getSjLjDispatchPreservedMask (const MachineFunction &MF) const |

| |

| const uint32_t * | getThisReturnPreservedMask (const MachineFunction &MF, CallingConv::ID) const |

| | getThisReturnPreservedMask - Returns a call preserved mask specific to the case that 'returned' is on an i32 first argument if the calling convention is one that can (partially) model this attribute with a preserved mask (i.e. More...

|

| |

| BitVector | getReservedRegs (const MachineFunction &MF) const override |

| |

| bool | isAsmClobberable (const MachineFunction &MF, unsigned PhysReg) const override |

| |

| const TargetRegisterClass * | getPointerRegClass (const MachineFunction &MF, unsigned Kind=0) const override |

| |

| const TargetRegisterClass * | getCrossCopyRegClass (const TargetRegisterClass *RC) const override |

| |

| const TargetRegisterClass * | getLargestLegalSuperClass (const TargetRegisterClass *RC, const MachineFunction &MF) const override |

| |

| unsigned | getRegPressureLimit (const TargetRegisterClass *RC, MachineFunction &MF) const override |

| |

| bool | getRegAllocationHints (unsigned VirtReg, ArrayRef< MCPhysReg > Order, SmallVectorImpl< MCPhysReg > &Hints, const MachineFunction &MF, const VirtRegMap *VRM, const LiveRegMatrix *Matrix) const override |

| |

| void | updateRegAllocHint (unsigned Reg, unsigned NewReg, MachineFunction &MF) const override |

| |

| bool | hasBasePointer (const MachineFunction &MF) const |

| |

| bool | canRealignStack (const MachineFunction &MF) const override |

| |

| int64_t | getFrameIndexInstrOffset (const MachineInstr *MI, int Idx) const override |

| |

| bool | needsFrameBaseReg (MachineInstr *MI, int64_t Offset) const override |

| | needsFrameBaseReg - Returns true if the instruction's frame index reference would be better served by a base register other than FP or SP. More...

|

| |

| void | materializeFrameBaseRegister (MachineBasicBlock *MBB, unsigned BaseReg, int FrameIdx, int64_t Offset) const override |

| | materializeFrameBaseRegister - Insert defining instruction(s) for BaseReg to be a pointer to FrameIdx at the beginning of the basic block. More...

|

| |

| void | resolveFrameIndex (MachineInstr &MI, unsigned BaseReg, int64_t Offset) const override |

| |

| bool | isFrameOffsetLegal (const MachineInstr *MI, unsigned BaseReg, int64_t Offset) const override |

| |

| bool | cannotEliminateFrame (const MachineFunction &MF) const |

| |

| unsigned | getFrameRegister (const MachineFunction &MF) const override |

| |

| unsigned | getBaseRegister () const |

| |

| bool | isLowRegister (unsigned Reg) const |

| |

| virtual void | emitLoadConstPool (MachineBasicBlock &MBB, MachineBasicBlock::iterator &MBBI, const DebugLoc &dl, unsigned DestReg, unsigned SubIdx, int Val, ARMCC::CondCodes Pred=ARMCC::AL, unsigned PredReg=0, unsigned MIFlags=MachineInstr::NoFlags) const |

| | emitLoadConstPool - Emits a load from constpool to materialize the specified immediate. More...

|

| |

| bool | requiresRegisterScavenging (const MachineFunction &MF) const override |

| | Code Generation virtual methods... More...

|

| |

| bool | trackLivenessAfterRegAlloc (const MachineFunction &MF) const override |

| |

| bool | requiresFrameIndexScavenging (const MachineFunction &MF) const override |

| |

| bool | requiresVirtualBaseRegisters (const MachineFunction &MF) const override |

| |

| void | eliminateFrameIndex (MachineBasicBlock::iterator II, int SPAdj, unsigned FIOperandNum, RegScavenger *RS=nullptr) const override |

| |

| bool | shouldCoalesce (MachineInstr *MI, const TargetRegisterClass *SrcRC, unsigned SubReg, const TargetRegisterClass *DstRC, unsigned DstSubReg, const TargetRegisterClass *NewRC, LiveIntervals &LIS) const override |

| | SrcRC and DstRC will be morphed into NewRC if this returns true. More...

|

| |

Definition at line 23 of file ARMRegisterInfo.h.

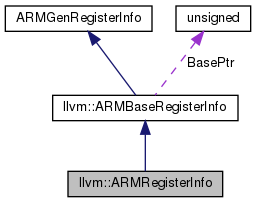

Protected Member Functions inherited from llvm::ARMBaseRegisterInfo

Protected Member Functions inherited from llvm::ARMBaseRegisterInfo Protected Attributes inherited from llvm::ARMBaseRegisterInfo

Protected Attributes inherited from llvm::ARMBaseRegisterInfo 1.8.13

1.8.13