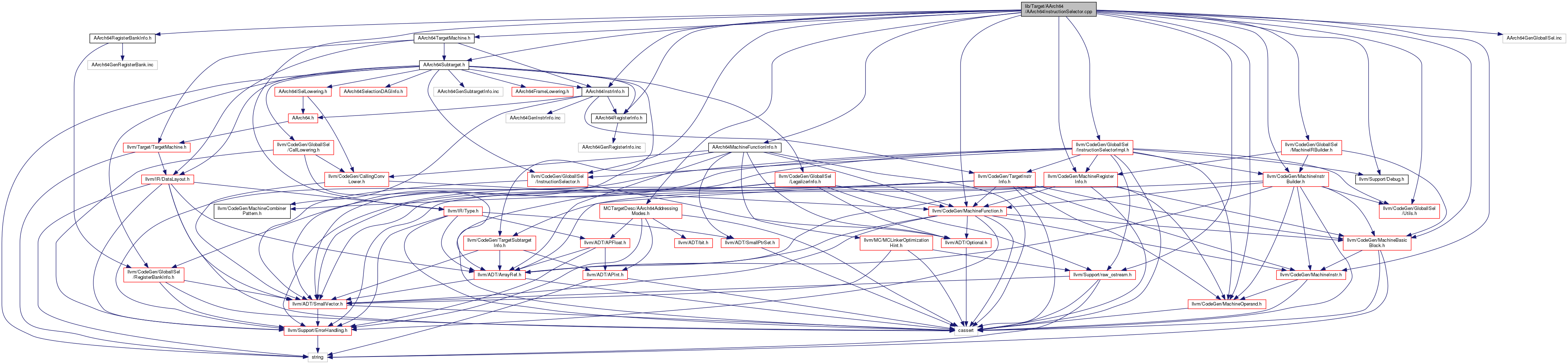

This file implements the targeting of the InstructionSelector class for AArch64. More...

#include "AArch64InstrInfo.h"#include "AArch64MachineFunctionInfo.h"#include "AArch64RegisterBankInfo.h"#include "AArch64RegisterInfo.h"#include "AArch64Subtarget.h"#include "AArch64TargetMachine.h"#include "MCTargetDesc/AArch64AddressingModes.h"#include "llvm/CodeGen/GlobalISel/InstructionSelector.h"#include "llvm/CodeGen/GlobalISel/InstructionSelectorImpl.h"#include "llvm/CodeGen/GlobalISel/MachineIRBuilder.h"#include "llvm/CodeGen/GlobalISel/Utils.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/IR/Type.h"#include "llvm/Support/Debug.h"#include "llvm/Support/raw_ostream.h"#include "AArch64GenGlobalISel.inc"

Go to the source code of this file.

Namespaces | |

| llvm | |

| This class represents lattice values for constants. | |

Macros | |

| #define | DEBUG_TYPE "aarch64-isel" |

| #define | GET_GLOBALISEL_PREDICATE_BITSET |

| #define | GET_GLOBALISEL_PREDICATES_DECL |

| #define | GET_GLOBALISEL_TEMPORARIES_DECL |

| #define | GET_GLOBALISEL_IMPL |

| #define | GET_GLOBALISEL_PREDICATES_INIT |

| #define | GET_GLOBALISEL_TEMPORARIES_INIT |

Detailed Description

This file implements the targeting of the InstructionSelector class for AArch64.

- Todo:

- This should be generated by TableGen.

Definition in file AArch64InstructionSelector.cpp.

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "aarch64-isel" |

Definition at line 36 of file AArch64InstructionSelector.cpp.

◆ GET_GLOBALISEL_IMPL

| #define GET_GLOBALISEL_IMPL |

Definition at line 131 of file AArch64InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATE_BITSET

| #define GET_GLOBALISEL_PREDICATE_BITSET |

Definition at line 42 of file AArch64InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATES_DECL

| #define GET_GLOBALISEL_PREDICATES_DECL |

Definition at line 118 of file AArch64InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATES_INIT

| #define GET_GLOBALISEL_PREDICATES_INIT |

◆ GET_GLOBALISEL_TEMPORARIES_DECL

| #define GET_GLOBALISEL_TEMPORARIES_DECL |

Definition at line 124 of file AArch64InstructionSelector.cpp.

◆ GET_GLOBALISEL_TEMPORARIES_INIT

| #define GET_GLOBALISEL_TEMPORARIES_INIT |

Function Documentation

◆ changeFCMPPredToAArch64CC()

|

static |

Definition at line 541 of file AArch64InstructionSelector.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addGlobalAddress(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstr::addOperand(), llvm::MachineInstrBuilder::addUse(), llvm::AArch64ISD::ADR, llvm::AArch64CC::AL, llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, assert(), llvm::AMDGPUISD::BFM, llvm::APFloat::bitcastToAPInt(), llvm::ISD::BR, llvm::MachineIRBuilder::buildInstr(), llvm::BuildMI(), changeICMPPredToAArch64CC(), llvm::MachineOperand::ChangeToFrameIndex(), llvm::MachineOperand::ChangeToImmediate(), llvm::ARCISD::CMP, llvm::MachineInstrBuilder::constrainAllUses(), llvm::RegisterBankInfo::constrainGenericRegister(), llvm::constrainSelectedInstRegOperands(), llvm::MachineRegisterInfo::createGenericVirtualRegister(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::dbgs(), llvm::tgtok::Def, llvm::PointerUnion< PT1, PT2 >::dyn_cast(), llvm::AArch64_AM::encodeLogicalImmediate(), EQ, llvm::MachineInstr::eraseFromParent(), llvm::AArch64CC::GE, llvm::PointerUnion< PT1, PT2 >::get(), llvm::ConstantInt::getBitWidth(), llvm::MachineOperand::getBlockAddress(), llvm::MachineOperand::getCImm(), llvm::getConstantVRegVal(), llvm::MachineInstr::getDebugLoc(), llvm::LLT::getElementType(), llvm::MachineOperand::getFPImm(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getGlobal(), llvm::RegisterBank::getID(), llvm::MachineOperand::getImm(), llvm::MachineFunction::getInfo(), llvm::MachineOperand::getIntrinsicID(), llvm::AArch64CC::getInvertedCondCode(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getNumExplicitOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineOperand::getOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getPredicate(), llvm::MachineOperand::getReg(), llvm::RegisterBankInfo::getRegBank(), llvm::MachineRegisterInfo::getRegClassOrRegBank(), llvm::MachineFunction::getRegInfo(), llvm::ConstantInt::getSExtValue(), llvm::AArch64_AM::getShifterImm(), llvm::LLT::getSizeInBits(), llvm::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::ConstantFP::getValueAPF(), llvm::AArch64FunctionInfo::getVarArgsStackIndex(), llvm::MachineRegisterInfo::getVRegDef(), llvm::ConstantInt::getZExtValue(), llvm::APInt::getZExtValue(), llvm::AArch64CC::GT, llvm::Function::hasFnAttribute(), llvm::AArch64CC::HI, I, llvm::MachineOperand::isCImm(), llvm::MachineInstr::isCopy(), llvm::APFloat::isExactlyValue(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isIntrinsicID(), llvm::LLT::isPointer(), llvm::isPreISelGenericOpcode(), llvm::MachineOperand::isReg(), llvm::LLT::isScalar(), llvm::LLT::isValid(), llvm::LLT::isVector(), llvm::CodeModel::Large, llvm::AArch64CC::LE, LLVM_DEBUG, llvm_unreachable, llvm::AArch64ISD::LOADgot, llvm::Log2_32(), llvm::AArch64CC::LS, llvm::AArch64_AM::LSL, llvm::AArch64CC::LT, llvm::BitmaskEnumDetail::Mask(), llvm::MachineInstr::memoperands_begin(), MI, llvm::AArch64II::MO_G0, llvm::AArch64II::MO_G1, llvm::AArch64II::MO_G2, llvm::AArch64II::MO_G3, llvm::AArch64II::MO_GOT, llvm::AArch64II::MO_NC, llvm::AArch64II::MO_PAGE, llvm::AArch64II::MO_PAGEOFF, MRI, llvm::AArch64CC::NE, llvm::None, llvm::AArch64CC::PL, llvm::NVPTX::PTXLdStInstCode::Scalar, selectBinaryOp(), selectCopy(), selectFPConvOpc(), llvm::mca::selectImpl(), selectLoadStoreUIOp(), selectMergeValues(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), llvm::MachineOperand::setReg(), llvm::MachineOperand::setSubReg(), llvm::MachineOperand::setTargetFlags(), Size, std::swap(), TII, llvm::CodeModel::Tiny, llvm::SystemZISD::TM, llvm::Intrinsic::trap, TRI, unsupportedBinOp(), llvm::AArch64CC::VC, and llvm::AArch64CC::VS.

◆ changeICMPPredToAArch64CC()

|

static |

Definition at line 514 of file AArch64InstructionSelector.cpp.

References EQ, llvm::AArch64CC::GE, llvm::AArch64CC::GT, llvm::AArch64CC::HI, llvm::AArch64CC::HS, llvm::AArch64CC::LE, llvm_unreachable, llvm::AArch64CC::LO, llvm::AArch64CC::LS, llvm::AArch64CC::LT, and llvm::AArch64CC::NE.

Referenced by changeFCMPPredToAArch64CC().

◆ selectBinaryOp()

Select the AArch64 opcode for the basic binary operation GenericOpc (such as G_OR or G_SDIV), appropriate for the register bank RegBankID and of size OpSize.

- Returns

GenericOpcif the combination is unsupported.

Definition at line 232 of file AArch64InstructionSelector.cpp.

Referenced by CC_MipsO32_FP64(), changeFCMPPredToAArch64CC(), isSExtLoad(), and llvm::FastISel::selectOperator().

◆ selectCopy()

|

static |

Definition at line 352 of file AArch64InstructionSelector.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addUse(), assert(), llvm::BuildMI(), llvm::TargetRegisterClass::contains(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::dbgs(), llvm::PointerUnion< PT1, PT2 >::dyn_cast(), llvm::MCInstrInfo::get(), llvm::PointerUnion< PT1, PT2 >::get(), llvm::MachineInstr::getDebugLoc(), llvm::RegisterBank::getID(), llvm::MCInstrInfo::getName(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::RegisterBankInfo::getRegBank(), llvm::TargetRegisterInfo::getRegClass(), llvm::MachineRegisterInfo::getRegClassOrRegBank(), llvm::LLT::getSizeInBits(), llvm::MachineRegisterInfo::getType(), I, llvm::MachineInstr::isCopy(), LLVM_DEBUG, selectFP16CopyFromGPR32(), llvm::MachineInstr::setDesc(), and llvm::MachineOperand::setReg().

Referenced by changeFCMPPredToAArch64CC(), and getRegClassFromGRPhysReg().

◆ selectFP16CopyFromGPR32()

|

static |

Definition at line 335 of file AArch64InstructionSelector.cpp.

References llvm::MachineInstrBuilder::addUse(), llvm::BuildMI(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), I, and llvm::MachineOperand::setReg().

Referenced by selectCopy().

◆ selectFPConvOpc()

Definition at line 438 of file AArch64InstructionSelector.cpp.

References llvm::LLT::getSizeInBits(), and llvm::LLT::isScalar().

Referenced by changeFCMPPredToAArch64CC().

◆ selectLoadStoreUIOp()

|

static |

Select the AArch64 opcode for the G_LOAD or G_STORE operation GenericOpc, appropriate for the (value) register bank RegBankID and of memory access size OpSize.

This returns the variant with the base+unsigned-immediate addressing mode (e.g., LDRXui).

- Returns

GenericOpcif the combination is unsupported.

Definition at line 303 of file AArch64InstructionSelector.cpp.

References isStore().

Referenced by changeFCMPPredToAArch64CC().

◆ unsupportedBinOp()

|

static |

Check whether I is a currently unsupported binary operation:

- it has an unsized type

- an operand is not a vreg

- all operands are not in the same bank These are checks that should someday live in the verifier, but right now, these are mostly limitations of the aarch64 selector.

Definition at line 186 of file AArch64InstructionSelector.cpp.

References llvm::dbgs(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::RegisterBankInfo::getRegBank(), llvm::MachineRegisterInfo::getType(), llvm::LLT::isValid(), LLVM_DEBUG, MRI, llvm::MachineInstr::operands(), and TRI.

Referenced by changeFCMPPredToAArch64CC().

1.8.13

1.8.13