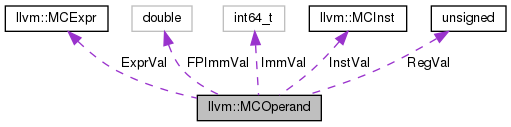

Instances of this class represent operands of the MCInst class. More...

#include "llvm/MC/MCInst.h"

Public Member Functions | |

| MCOperand () | |

| bool | isValid () const |

| bool | isReg () const |

| bool | isImm () const |

| bool | isFPImm () const |

| bool | isExpr () const |

| bool | isInst () const |

| unsigned | getReg () const |

| Returns the register number. More... | |

| void | setReg (unsigned Reg) |

| Set the register number. More... | |

| int64_t | getImm () const |

| void | setImm (int64_t Val) |

| double | getFPImm () const |

| void | setFPImm (double Val) |

| const MCExpr * | getExpr () const |

| void | setExpr (const MCExpr *Val) |

| const MCInst * | getInst () const |

| void | setInst (const MCInst *Val) |

| void | print (raw_ostream &OS) const |

| void | dump () const |

| bool | isBareSymbolRef () const |

| bool | evaluateAsConstantImm (int64_t &Imm) const |

Static Public Member Functions | |

| static MCOperand | createReg (unsigned Reg) |

| static MCOperand | createImm (int64_t Val) |

| static MCOperand | createFPImm (double Val) |

| static MCOperand | createExpr (const MCExpr *Val) |

| static MCOperand | createInst (const MCInst *Val) |

Detailed Description

Instances of this class represent operands of the MCInst class.

This is a simple discriminated union.

Constructor & Destructor Documentation

◆ MCOperand()

Member Function Documentation

◆ createExpr()

Definition at line 137 of file MCInst.h.

References ExprVal.

Referenced by llvm::X86Operand::addAbsMemOperands(), llvm::HexagonMCInstrInfo::addConstant(), llvm::MCInstBuilder::addExpr(), llvm::X86Operand::addExpr(), llvm::X86Operand::addMemOffsOperands(), addNegOperand(), adjustDuplex(), llvm::ARCMCInstLower::ARCMCInstLower(), countMCSymbolRefExpr(), llvm::createRISCVMCCodeEmitter(), createSparcMCOperand(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::MipsTargetELFStreamer::emitDirectiveCpLoad(), llvm::MipsTargetELFStreamer::emitDirectiveCpsetup(), EmitHiLo(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::MipsAsmPrinter::EmitStartOfAsmFile(), getRealVLDOpcode(), getRetOpcode(), GetSymbolRef(), getVariantKind(), llvm::HexagonLowerToMC(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), incrementLoc(), llvm::XCoreMCInstLower::Initialize(), llvm::MipsMCInstLower::Initialize(), isShiftedUIntAtAnyPosition(), llvm::MSP430MCInstLower::Lower(), llvm::BPFMCInstLower::Lower(), llvm::LanaiMCInstLower::Lower(), llvm::WebAssemblyMCInstLower::Lower(), llvm::AVRMCInstLower::lowerInstruction(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), lowerSymbolOperand(), LowerSymbolOperand(), llvm::AVRMCInstLower::lowerSymbolOperand(), llvm::MSP430MCInstLower::LowerSymbolOperand(), llvm::BPFMCInstLower::LowerSymbolOperand(), llvm::LanaiMCInstLower::LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandCOFF(), llvm::AArch64MCInstLower::lowerSymbolOperandDarwin(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), makeCombineInst(), nextReg(), ScaleVectorOffset(), llvm::AArch64ExternalSymbolizer::tryAddingSymbolicOperand(), llvm::MCExternalSymbolizer::tryAddingSymbolicOperand(), llvm::AMDGPUSymbolizer::tryAddingSymbolicOperand(), and VisitGlobalVariableForEmission().

◆ createFPImm()

|

inlinestatic |

Definition at line 130 of file MCInst.h.

References FPImmVal.

Referenced by llvm::MCInstBuilder::addFPImm(), llvm::WebAssemblyMCInstLower::Lower(), llvm::ARMAsmPrinter::lowerOperand(), and parseImmediate().

◆ createImm()

|

inlinestatic |

Definition at line 123 of file MCInst.h.

References ImmVal.

Referenced by llvm::X86Operand::addAbsMemOperands(), llvm::X86Operand::addExpr(), llvm::MCInstBuilder::addImm(), llvm::X86Operand::addMemOffsOperands(), llvm::X86Operand::addMemOperands(), addNegOperand(), addOptionalImmOperand(), AddThumb1SBit(), llvm::AMDGPUDisassembler::convertSDWAInst(), llvm::HexagonMCShuffler::copyTo(), Decode2RImmInstruction(), Decode2RUSInstruction(), Decode3RImmInstruction(), DecodeAddiGroupBranch(), DecodeAddiur2Simm7(), DecodeAddrMode2IdxInstruction(), DecodeAddrMode3Instruction(), DecodeAddrMode5FP16Operand(), DecodeAddrMode5Operand(), DecodeAddrMode6Operand(), DecodeAddrModeImm12Operand(), DecodeAddSubERegInstruction(), DecodeAddSubImmShift(), DecodeAdrInstruction(), DecodeANDI16Imm(), DecodeArmMOVTWInstruction(), DecodeBankedReg(), decodeBDAddr12Operand(), decodeBDAddr20Operand(), decodeBDLAddr12Len4Operand(), decodeBDLAddr12Len8Operand(), decodeBDRAddr12Operand(), decodeBDVAddr12Operand(), decodeBDXAddr12Operand(), decodeBDXAddr20Operand(), DecodeBgtzGroupBranch(), DecodeBgtzGroupBranchMMR6(), DecodeBgtzlGroupBranch(), DecodeBitfieldMaskOperand(), DecodeBitpOperand(), DecodeBlezGroupBranch(), DecodeBlezGroupBranchMMR6(), DecodeBlezlGroupBranch(), decodeBranch(), DecodeBranchImmInstruction(), DecodeBranchTarget(), DecodeBranchTarget10MM(), DecodeBranchTarget1SImm16(), DecodeBranchTarget21(), DecodeBranchTarget21MM(), DecodeBranchTarget26(), DecodeBranchTarget26MM(), DecodeBranchTarget7MM(), DecodeBranchTargetMM(), DecodeCacheeOp_CacheOpR6(), DecodeCacheOp(), DecodeCacheOpMM(), DecodeCall(), DecodeCGImm(), decodeCLUIImmOperand(), DecodeCopMemInstruction(), DecodeCoprocessor(), DecodeCPSInstruction(), DecodeDaddiGroupBranch(), DecodeDAHIDATI(), DecodeDAHIDATIMMR6(), DecodeDEXT(), DecodeDINS(), DecodeFixedPointScaleImm32(), DecodeFixedPointScaleImm64(), DecodeFMem(), DecodeFMem2(), DecodeFMem3(), DecodeFMemCop2MMR6(), DecodeFMemCop2R6(), DecodeFMemMMR2(), DecodeFMOVLaneInstruction(), DecodeForVMRSandVMSR(), llvm::AMDGPUDisassembler::decodeFPImmed(), decodeFRMArg(), DecodeFromCyclicRange(), DecodeHINTInstruction(), DecodeImm8OptLsl(), DecodeInsSize(), DecodeInstSyncBarrierOption(), DecodeINSVE_DF(), llvm::AMDGPUDisassembler::decodeIntImmed(), DecodeIT(), DecodeJMPL(), DecodeJumpTarget(), DecodeJumpTargetMM(), DecodeL2RUSInstruction(), DecodeLdLImmInstruction(), DecodeLdRLImmInstruction(), DecodeLi16Imm(), llvm::AMDGPUDisassembler::decodeLiteralConstant(), DecodeLoadByte15(), DecodeLogicalImmInstruction(), DecodeMem(), DecodeMemBarrierOption(), DecodeMemEVA(), DecodeMemExtend(), DecodeMemMMGPImm7Lsl2(), DecodeMemMMImm12(), DecodeMemMMImm16(), DecodeMemMMImm4(), DecodeMemMMImm9(), DecodeMemMMReglistImm4Lsl2(), DecodeMemMMSPImm5Lsl2(), DecodeMemMultipleWritebackInstruction(), DecodeMemOperand(), decodeMemoryOpValue(), decodeMemRIOperands(), decodeMemRIX16Operands(), decodeMemRIXOperands(), DecodeMEMrs9(), DecodeModImmInstruction(), DecodeModImmTiedInstruction(), DecodeMoveHRegInstruction(), DecodeMoveImmInstruction(), DecodeMRSSystemRegister(), DecodeMSA128Mem(), DecodeMSRMask(), DecodeMSRSystemRegister(), DecodeNegImmOperand(), DecodeNEONComplexLane64Instruction(), DecodeNEONModImmInstruction(), DecodePairLdStInstruction(), decodePCDBLOperand(), DecodePCRel24BranchTarget(), DecodePCRelLabel19(), DecodePOOL16BEncodedField(), DecodePOP35GroupBranchMMR6(), DecodePOP37GroupBranchMMR6(), DecodePOP65GroupBranchMMR6(), DecodePOP75GroupBranchMMR6(), DecodePostIdxReg(), decodePredicateOperand(), DecodePredicateOperand(), DecodePrefeOpMM(), DecodeReturn(), DecodeRFEInstruction(), DecoderForMRRC2AndMCRR2(), decodeRiMemoryValue(), DecodeRUSInstruction(), DecodeSETPANInstruction(), decodeShiftImm(), DecodeShiftRight16Imm(), DecodeShiftRight32Imm(), DecodeShiftRight64Imm(), DecodeShiftRight8Imm(), DecodeSignedLdStInstruction(), DecodeSignedOperand(), DecodeSImm(), DecodeSIMM13(), DecodeSimm18Lsl3(), DecodeSimm19Lsl2(), DecodeSimm23Lsl2(), DecodeSimm9SP(), decodeSImmOperand(), decodeSImmOperandAndLsl1(), DecodeSImmWithOffsetAndScale(), decodeSoppBrTarget(), DecodeSORegImmOperand(), DecodeSORegMemOperand(), DecodeSORegRegOperand(), decodeSPE2Operands(), decodeSPE4Operands(), decodeSPE8Operands(), DecodeSpecial3LlSc(), decodeSplsValue(), DecodeStLImmInstruction(), DecodeSVEIncDecImm(), DecodeSVELogicalImmInstruction(), DecodeSWAP(), DecodeSymbolicOperandOff(), DecodeSyncI(), DecodeSyncI_MM(), DecodeSynciR6(), DecodeSystemPStateInstruction(), DecodeT2AddrModeImm0_1020s4(), DecodeT2AddrModeImm12(), DecodeT2AddrModeSOReg(), DecodeT2Adr(), DecodeT2BInstruction(), DecodeT2BROperand(), DecodeT2CPSInstruction(), DecodeT2Imm8(), DecodeT2Imm8S4(), DecodeT2LoadLabel(), DecodeT2MOVTWInstruction(), DecodeT2ShifterImmOperand(), DecodeT2SOImm(), DecodeTestAndBranch(), DecodeThreeAddrSRegInstruction(), DecodeThumbAddrModeIS(), DecodeThumbAddrModePC(), DecodeThumbAddrModeSP(), DecodeThumbAddSpecialReg(), DecodeThumbAddSPImm(), DecodeThumbBCCTargetOperand(), DecodeThumbBLTargetOperand(), DecodeThumbBLXOffset(), DecodeThumbBROperand(), DecodeThumbCmpBROperand(), DecodeThumbCPS(), DecodeTRAP(), decodeUImmOperand(), DecodeUImmWithOffsetAndScale(), DecodeUnconditionalBranch(), DecodeUnsignedLdStInstruction(), DecodeVCVTD(), DecodeVCVTQ(), DecodeVecShiftLImm(), DecodeVecShiftRImm(), DecodeVLD1DupInstruction(), DecodeVLD1LN(), DecodeVLD2DupInstruction(), DecodeVLD2LN(), DecodeVLD3DupInstruction(), DecodeVLD3LN(), DecodeVLD4DupInstruction(), DecodeVLD4LN(), DecodeVLDInstruction(), DecodeVSHLMaxInstruction(), DecodeVST1LN(), DecodeVST2LN(), DecodeVST3LN(), DecodeVST4LN(), DecodeVSTInstruction(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::MipsTargetELFStreamer::emitDirectiveCpreturn(), llvm::MipsTargetStreamer::emitII(), llvm::HexagonAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitInstruction(), EmitNops(), llvm::MipsTargetStreamer::emitRI(), llvm::MipsTargetStreamer::emitRRI(), llvm::MipsTargetStreamer::emitRRIII(), getCondCode(), llvm::AMDGPUDisassembler::getInstruction(), llvm::ARMInstrInfo::getNoop(), llvm::Thumb1InstrInfo::getNoop(), llvm::Thumb2InstrInfo::getNoop(), llvm::AArch64InstrInfo::getNoop(), getRealVLDOpcode(), getRetOpcode(), getVariantKind(), HasSecRelSymbolRef(), isRegOrImmWithInputMods(), IsSmallMemAccess(), LLVMInitializeHexagonDisassembler(), llvm::MSP430MCInstLower::Lower(), llvm::BPFMCInstLower::Lower(), llvm::LanaiMCInstLower::Lower(), llvm::WebAssemblyMCInstLower::Lower(), llvm::AVRMCInstLower::lowerInstruction(), llvm::XCoreMCInstLower::LowerOperand(), llvm::ARCMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), llvm::MipsMCInstLower::LowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), nextReg(), parseImmediate(), parseLEBImmediate(), PostOperandDecodeAdjust(), llvm::ARMAsmBackend::relaxInstruction(), translateImmediate(), translateOperand(), translateRMMemory(), and VisitGlobalVariableForEmission().

◆ createInst()

Definition at line 144 of file MCInst.h.

References dump(), evaluateAsConstantImm(), InstVal, isBareSymbolRef(), and print().

Referenced by llvm::HexagonMCInstrInfo::addConstExtender(), llvm::MCInstBuilder::addInst(), adjustDuplex(), llvm::HexagonMCShuffler::copyTo(), llvm::HexagonMCInstrInfo::deriveDuplex(), llvm::HexagonLowerToMC(), LLVMInitializeHexagonDisassembler(), and llvm::HexagonMCInstrInfo::padEndloop().

◆ createReg()

Definition at line 116 of file MCInst.h.

Referenced by llvm::X86Operand::addDstIdxOperands(), llvm::X86Operand::addGR32orGR64Operands(), llvm::X86Operand::addMemOffsOperands(), llvm::X86Operand::addMemOperands(), addOptionalImmOperand(), llvm::MCInstBuilder::addReg(), llvm::X86Operand::addRegOperands(), llvm::X86Operand::addSrcIdxOperands(), AddThumb1SBit(), llvm::AMDGPUDisassembler::convertMIMGInst(), countMCSymbolRefExpr(), llvm::AMDGPUDisassembler::createRegOperand(), DecodeACC64DSPRegisterClass(), DecodeAddiGroupBranch(), DecodeAddrMode2IdxInstruction(), DecodeAddrMode3Instruction(), DecodeAFGR64RegisterClass(), DecodeASRRegsRegisterClass(), decodeBDAddr12Operand(), decodeBDAddr20Operand(), decodeBDLAddr12Len4Operand(), decodeBDLAddr12Len8Operand(), decodeBDRAddr12Operand(), decodeBDVAddr12Operand(), decodeBDXAddr12Operand(), decodeBDXAddr20Operand(), DecodeBgtzGroupBranch(), DecodeBgtzGroupBranchMMR6(), DecodeBgtzlGroupBranch(), DecodeBlezGroupBranch(), DecodeBlezGroupBranchMMR6(), DecodeBlezlGroupBranch(), DecodeCacheeOp_CacheOpR6(), DecodeCacheOp(), DecodeCacheOpMM(), DecodeCCOutOperand(), DecodeCCRRegisterClass(), DecodeCOP0RegisterClass(), DecodeCOP2RegisterClass(), DecodeCPPairRegisterClass(), DecodeCPRegsRegisterClass(), decodeCRBitMOperand(), DecodeCRC(), DecodeCtrRegs64RegisterClass(), DecodeCtrRegsRegisterClass(), DecodeDaddiGroupBranch(), DecodeDAHIDATI(), DecodeDAHIDATIMMR6(), DecodeDDDDRegisterClass(), DecodeDDDRegisterClass(), DecodeDDRegisterClass(), DecodeDEXT(), DecodeDFPRegsRegisterClass(), DecodeDINS(), DecodeDPairRegisterClass(), DecodeDPairSpacedRegisterClass(), DecodeDPRRegisterClass(), DecodeFCCRegisterClass(), DecodeFCCRegsRegisterClass(), DecodeFGR32RegisterClass(), DecodeFGR64RegisterClass(), DecodeFGRCCRegisterClass(), DecodeFMem(), DecodeFMem2(), DecodeFMem3(), DecodeFMemCop2MMR6(), DecodeFMemCop2R6(), DecodeFMemMMR2(), DecodeForVMRSandVMSR(), DecodeFPR128RegisterClass(), DecodeFPR16RegisterClass(), DecodeFPR32CRegisterClass(), DecodeFPR32RegisterClass(), DecodeFPR64CRegisterClass(), DecodeFPR64RegisterClass(), DecodeFPR8RegisterClass(), DecodeFPRegsRegisterClass(), DecodeGPR32RegisterClass(), DecodeGPR32spRegisterClass(), DecodeGPR64commonRegisterClass(), DecodeGPR64RegisterClass(), DecodeGPR64spRegisterClass(), DecodeGPRCRegisterClass(), DecodeGPRMM16MovePRegisterClass(), DecodeGPRMM16RegisterClass(), DecodeGPRMM16ZeroRegisterClass(), DecodeGPRPairRegisterClass(), DecodeGPRRegisterClass(), DecodeGPRSeqPairsClassRegisterClass(), DecodeGPRwithAPSRRegisterClass(), DecodeGR16RegisterClass(), DecodeGR8RegisterClass(), DecodeGRRegsRegisterClass(), DecodeGuestRegs64RegisterClass(), DecodeGuestRegsRegisterClass(), DecodeHI32DSPRegisterClass(), DecodeHWRegsRegisterClass(), DecodeI64RegsRegisterClass(), DecodeIntPairRegisterClass(), DecodeIntRegsRegisterClass(), DecodeLO32DSPRegisterClass(), DecodeLoadByte15(), DecodeMem(), DecodeMemEVA(), DecodeMemMMGPImm7Lsl2(), DecodeMemMMImm12(), DecodeMemMMImm16(), DecodeMemMMImm9(), DecodeMemMMReglistImm4Lsl2(), DecodeMemMMSPImm5Lsl2(), decodeMemoryOpValue(), decodeMemRIOperands(), decodeMemRIX16Operands(), decodeMemRIXOperands(), DecodeModRegsRegisterClass(), DecodeMovePRegPair(), DecodeMSA128BRegisterClass(), DecodeMSA128DRegisterClass(), DecodeMSA128HRegisterClass(), DecodeMSA128Mem(), DecodeMSA128WRegisterClass(), DecodeMSACtrlRegisterClass(), DecodePOP35GroupBranchMMR6(), DecodePOP37GroupBranchMMR6(), DecodePOP65GroupBranchMMR6(), DecodePOP75GroupBranchMMR6(), DecodePPRRegisterClass(), DecodePredicateOperand(), DecodePrefeOpMM(), DecodePRRegsRegisterClass(), DecodeQFPRegsRegisterClass(), DecodeQPRRegisterClass(), DecodeQQQQRegisterClass(), DecodeQQQRegisterClass(), DecodeQQRegisterClass(), decodeRegisterClass(), DecodeRegisterClass(), DecodeRegListOperand(), DecodeRegListOperand16(), decodeRiMemoryValue(), DecodeRRegsRegisterClass(), decodeRrMemoryValue(), decodeSPE2Operands(), decodeSPE4Operands(), decodeSPE8Operands(), DecodeSpecial3LlSc(), decodeSplsValue(), DecodeSPRRegisterClass(), DecodeSyncI(), DecodeSyncI_MM(), DecodeSynciR6(), DecodetcGPRRegisterClass(), DecodeThumbAddrModeSP(), DecodeThumbAddSpecialReg(), DecodeThumbAddSPImm(), DecodeThumbAddSPReg(), DecodeVectorRegisterClass(), DecodeVLD1LN(), DecodeVLD2LN(), DecodeVLD3DupInstruction(), DecodeVLD3LN(), DecodeVLD4DupInstruction(), DecodeVLD4LN(), DecodeVLDInstruction(), DecodeVST1LN(), DecodeVST2LN(), DecodeVST3LN(), DecodeVST4LN(), DecodeVSTInstruction(), DecodeZPR2RegisterClass(), DecodeZPR3RegisterClass(), DecodeZPR4RegisterClass(), DecodeZPRRegisterClass(), llvm::MipsTargetELFStreamer::emitDirectiveCpLoad(), llvm::MipsTargetELFStreamer::emitDirectiveCpreturn(), EmitHiLo(), llvm::ARMAsmPrinter::EmitInstruction(), EmitNops(), llvm::MipsTargetStreamer::emitR(), llvm::MipsTargetStreamer::emitRR(), llvm::MipsTargetStreamer::emitRRIII(), llvm::MipsTargetStreamer::emitRRR(), llvm::MipsTargetStreamer::emitRRX(), llvm::MipsTargetStreamer::emitRX(), llvm::MipsAsmPrinter::EmitStartOfAsmFile(), llvm::HexagonMCInstrInfo::getNewValueOperand(), llvm::Thumb1InstrInfo::getNoop(), llvm::ARMInstrInfo::getNoop(), llvm::Thumb2InstrInfo::getNoop(), getRealVLDOpcode(), getRetOpcode(), getVariantKind(), llvm::HexagonLowerToMC(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), IsSmallMemAccess(), llvm::MSP430MCInstLower::Lower(), llvm::BPFMCInstLower::Lower(), llvm::LanaiMCInstLower::Lower(), llvm::AArch64MCInstLower::Lower(), llvm::WebAssemblyMCInstLower::Lower(), llvm::AVRMCInstLower::lowerInstruction(), llvm::XCoreMCInstLower::LowerOperand(), llvm::ARCMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), llvm::MipsMCInstLower::LowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineOperandToMCOperand(), llvm::LowerRISCVMachineOperandToMCOperand(), makeCombineInst(), nextReg(), llvm::ARMInstPrinter::printInst(), readInstruction64(), RefineErrorLoc(), llvm::ARMAsmBackend::relaxInstruction(), llvm::RISCVAsmBackend::relaxInstruction(), llvm::MipsAsmPrinter::runOnMachineFunction(), translateDstIndex(), translateFPRegister(), translateImmediate(), translateMaskRegister(), translateRegister(), translateRMMemory(), translateSrcIndex(), and VisitGlobalVariableForEmission().

◆ dump()

| LLVM_DUMP_METHOD void MCOperand::dump | ( | ) | const |

Definition at line 58 of file MCInst.cpp.

References llvm::dbgs(), and print().

Referenced by createInst(), and llvm::MCInst::insert().

◆ evaluateAsConstantImm()

| bool MCOperand::evaluateAsConstantImm | ( | int64_t & | Imm | ) | const |

Definition at line 40 of file MCInst.cpp.

References getImm(), and isImm().

Referenced by createInst().

◆ getExpr()

Definition at line 96 of file MCInst.h.

References assert(), ExprVal, and isExpr().

Referenced by addNegOperand(), llvm::adjustPqBits(), convertFPR32ToFPR64(), countMCSymbolRefExpr(), llvm::createBPFbeMCCodeEmitter(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::HexagonMCInstrInfo::deriveSubInst(), llvm::MCStreamer::EmitInstruction(), llvm::HexagonMCELFStreamer::EmitSymbol(), llvm::MSP430MCCodeEmitter::encodeInstruction(), llvm::FixupKind(), llvm::PPCMCCodeEmitter::getAbsCondBrEncoding(), llvm::PPCMCCodeEmitter::getAbsDirectBrEncoding(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget7OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue(), getBranchTargetOpValue(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue1SImm16(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueLsl2MMR6(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMPC10(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMR6(), getCompoundInsn(), llvm::PPCMCCodeEmitter::getCondBrEncoding(), llvm::PPCMCCodeEmitter::getDirectBrEncoding(), llvm::PPCMCCodeEmitter::getImm16Encoding(), llvm::MipsMCCodeEmitter::getJumpTargetOpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValueMM(), getLit64Encoding(), llvm::HexagonMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), llvm::AVRInstPrinter::getPrettyRegisterName(), getRealVLDOpcode(), llvm::MipsMCCodeEmitter::getSimm18Lsl3Encoding(), llvm::MipsMCCodeEmitter::getSimm19Lsl2Encoding(), llvm::PPCMCCodeEmitter::getTLSCallEncoding(), llvm::PPCMCCodeEmitter::getTLSRegEncoding(), HasConditionalBranch(), HasSecRelSymbolRef(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), isBareSymbolRef(), llvm::HexagonMCInstrInfo::isConstExtended(), isMatchingOrAlias(), isPCRel(), isShiftedUIntAtAnyPosition(), makeCombineInst(), llvm::HexagonMCInstrInfo::minConstant(), needsPCRel(), nextReg(), print(), llvm::AArch64InstPrinter::printAddSubImm(), llvm::ARMInstPrinter::printAdrLabelOperand(), llvm::AArch64InstPrinter::printAdrpLabel(), llvm::AArch64InstPrinter::printAlignedLabel(), llvm::AArch64InstPrinter::printAMIndexedWB(), llvm::HexagonInstPrinter::printBrtarget(), llvm::BPFInstPrinter::printBrTargetOperand(), printExpr(), llvm::LanaiInstPrinter::printHi16AndImmOperand(), llvm::LanaiInstPrinter::printHi16ImmOperand(), llvm::BPFInstPrinter::printImm64Operand(), llvm::MSP430InstPrinter::printInst(), llvm::AArch64InstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::R600InstPrinter::printLiteral(), llvm::LanaiInstPrinter::printLo16AndImmOperand(), llvm::LanaiInstPrinter::printMemImmOperand(), llvm::X86IntelInstPrinter::printMemOffset(), llvm::X86ATTInstPrinter::printMemOffset(), printMemoryImmediateOffset(), llvm::X86IntelInstPrinter::printMemReference(), llvm::X86ATTInstPrinter::printMemReference(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::HexagonInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64InstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::X86InstPrinterCommon::printPCRelImm(), llvm::NVPTXInstPrinter::printProtoIdent(), llvm::AMDGPUInstPrinter::printRegOperand(), printSImmOperand(), llvm::ARMInstPrinter::printThumbLdrLabelOperand(), llvm::PPCInstPrinter::printTLSCall(), llvm::X86IntelInstPrinter::printU8Imm(), llvm::AArch64InstPrinter::printUImm12Offset(), ScaleVectorOffset(), SimplifyShortMoveForm(), smallData(), and llvm::HexagonMCInstrInfo::subInstWouldBeExtended().

◆ getFPImm()

|

inline |

Definition at line 86 of file MCInst.h.

References assert(), FPImmVal, and isFPImm().

Referenced by llvm::MipsMCCodeEmitter::getMachineOpValue(), print(), llvm::AArch64InstPrinter::printFPImmOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), and llvm::AMDGPUInstPrinter::printRegOperand().

◆ getImm()

|

inline |

Definition at line 76 of file MCInst.h.

References assert(), ImmVal, and isImm().

Referenced by addNegOperand(), AddThumb1SBit(), llvm::adjustPqBits(), allOpsDefaultValue(), convertFPR32ToFPR64(), llvm::AMDGPUDisassembler::convertMIMGInst(), countMCSymbolRefExpr(), createARMMCRelocationInfo(), llvm::createBPFbeMCCodeEmitter(), createBPFMCInstPrinter(), createLanaiElfRelocation(), createMipsObjectTargetStreamer(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), createWinCOFFStreamer(), decIncOperator(), DecodeInsSize(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::EmitAnyX86InstComments(), llvm::MSP430MCCodeEmitter::encodeInstruction(), encodeThumbBLOffset(), llvm::RuntimeDyldCheckerExprEval::evaluate(), evaluateAsConstantImm(), llvm::MCInstrAnalysis::evaluateBranch(), llvm::FixupKind(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget7OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue(), getBranchTargetOpValue(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue1SImm16(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueLsl2MMR6(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMPC10(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMR6(), getITDeprecationInfo(), llvm::MipsMCCodeEmitter::getJumpOffset16OpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValueMM(), getLit64Encoding(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), getMCRDeprecationInfo(), llvm::AVRInstPrinter::getPrettyRegisterName(), getRealVLDOpcode(), getRegisterForMxtrC0(), llvm::MipsMCCodeEmitter::getSimm23Lsl2Encoding(), llvm::MipsMCCodeEmitter::getSImm3Lsa2Value(), llvm::MipsMCCodeEmitter::getSImm9AddiuspValue(), getSpecialRegForName(), llvm::MipsMCCodeEmitter::getUImm3Mod8Encoding(), llvm::MipsMCCodeEmitter::getUImm6Lsl2Encoding(), HasConditionalBranch(), HasSecRelSymbolRef(), instIsBreakpoint(), llvm::HexagonMCInstrInfo::isInnerLoop(), llvm::HexagonMCInstrInfo::isMemReorderDisabled(), llvm::HexagonMCInstrInfo::isOuterLoop(), isPostIncrementForm(), isPreIncrementForm(), isRegOrImmWithInputMods(), isShiftedUIntAtAnyPosition(), llvm::LowerARMMachineInstrToMCInst(), LowerLargeShift(), needsPCRel(), nextReg(), print(), llvm::PPCInstPrinter::printAbsBranchOperand(), llvm::ARMInstPrinter::printAddrMode2OffsetOperand(), llvm::ARMInstPrinter::printAddrMode2Operand(), llvm::ARMInstPrinter::printAddrMode3OffsetOperand(), llvm::ARMInstPrinter::printAddrMode3Operand(), llvm::ARMInstPrinter::printAddrMode5FP16Operand(), llvm::ARMInstPrinter::printAddrMode5Operand(), llvm::ARMInstPrinter::printAddrMode6Operand(), llvm::ARMInstPrinter::printAddrModeImm12Operand(), llvm::AArch64InstPrinter::printAddSubImm(), llvm::ARMInstPrinter::printAdrLabelOperand(), llvm::AArch64InstPrinter::printAdrpLabel(), llvm::AArch64InstPrinter::printAlignedLabel(), llvm::ARMInstPrinter::printAM2PreOrOffsetIndexOp(), llvm::ARMInstPrinter::printAM3PreOrOffsetIndexOp(), llvm::AArch64InstPrinter::printAMIndexedWB(), llvm::AArch64InstPrinter::printArithExtend(), llvm::PPCInstPrinter::printATBitsAsHint(), llvm::ARMInstPrinter::printBankedRegOperand(), llvm::R600InstPrinter::printBankSwizzle(), llvm::AArch64InstPrinter::printBarrierOption(), llvm::ARMInstPrinter::printBitfieldInvMaskImmOperand(), llvm::PPCInstPrinter::printBranchOperand(), llvm::WebAssemblyInstPrinter::printBrList(), llvm::BPFInstPrinter::printBrTargetOperand(), llvm::AArch64InstPrinter::printBTIHintOp(), llvm::LanaiInstPrinter::printCCOperand(), llvm::SparcInstPrinter::printCCOperand(), llvm::ARMInstPrinter::printCImmediate(), llvm::AMDGPUInstPrinter::printClampSI(), llvm::NVPTXInstPrinter::printCmpMode(), llvm::AArch64InstPrinter::printComplexRotationOp(), llvm::ARMInstPrinter::printComplexRotationOp(), llvm::AArch64InstPrinter::printCondCode(), llvm::ARMInstPrinter::printCoprocOptionImm(), llvm::ARMInstPrinter::printCPSIFlag(), llvm::ARMInstPrinter::printCPSIMod(), llvm::RISCVInstPrinter::printCSRSystemRegister(), llvm::R600InstPrinter::printCT(), llvm::NVPTXInstPrinter::printCvtMode(), llvm::AArch64InstPrinter::printExactFPImm(), printExpr(), llvm::ARMInstPrinter::printFBits16(), llvm::ARMInstPrinter::printFBits32(), llvm::RISCVInstPrinter::printFenceArg(), llvm::AArch64InstPrinter::printFPImmOperand(), llvm::ARMInstPrinter::printFPImmOperand(), llvm::RISCVInstPrinter::printFRMArg(), llvm::LanaiInstPrinter::printHi16AndImmOperand(), llvm::LanaiInstPrinter::printHi16ImmOperand(), llvm::AMDGPUInstPrinter::printHigh(), llvm::AMDGPUInstPrinter::printHwreg(), llvm::AMDGPUInstPrinter::printIfSet(), llvm::AArch64InstPrinter::printImm(), llvm::BPFInstPrinter::printImm64Operand(), llvm::AArch64InstPrinter::printImm8OptLsl(), llvm::AArch64InstPrinter::printImmHex(), llvm::ARMInstPrinter::printImmPlusOneOperand(), llvm::AArch64InstPrinter::printImmScale(), llvm::ARMInstPrinter::printInst(), llvm::MSP430InstPrinter::printInst(), llvm::AArch64InstPrinter::printInst(), llvm::AMDGPUInstPrinter::printInst(), llvm::PPCInstPrinter::printInst(), llvm::WebAssemblyInstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::AArch64AppleInstPrinter::printInst(), llvm::ARMInstPrinter::printInstSyncBOption(), llvm::AArch64InstPrinter::printInverseCondCode(), llvm::R600InstPrinter::printKCache(), llvm::NVPTXInstPrinter::printLdStCode(), llvm::ARMInstPrinter::printLdStmModeOperand(), llvm::R600InstPrinter::printLiteral(), llvm::LanaiInstPrinter::printLo16AndImmOperand(), llvm::AArch64InstPrinter::printLogicalImm(), llvm::ARMInstPrinter::printMandatoryPredicateOperand(), llvm::SparcInstPrinter::printMembarTag(), llvm::ARMInstPrinter::printMemBOption(), llvm::AArch64InstPrinter::printMemExtend(), llvm::LanaiInstPrinter::printMemImmOperand(), llvm::X86IntelInstPrinter::printMemOffset(), llvm::X86ATTInstPrinter::printMemOffset(), llvm::BPFInstPrinter::printMemOperand(), llvm::NVPTXInstPrinter::printMemOperand(), llvm::SparcInstPrinter::printMemOperand(), printMemoryImmediateOffset(), llvm::X86IntelInstPrinter::printMemReference(), llvm::X86ATTInstPrinter::printMemReference(), llvm::LanaiInstPrinter::printMemRiOperand(), llvm::LanaiInstPrinter::printMemRrOperand(), llvm::LanaiInstPrinter::printMemSplsOperand(), llvm::ARMInstPrinter::printModImmOperand(), llvm::AArch64InstPrinter::printMRSSystemRegister(), llvm::ARMInstPrinter::printMSRMaskOperand(), llvm::AArch64InstPrinter::printMSRSystemRegister(), llvm::ARMInstPrinter::printNEONModImmOperand(), llvm::ARMInstPrinter::printNoHashImmediate(), llvm::R600InstPrinter::printOMOD(), llvm::AMDGPUInstPrinter::printOModSI(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::X86InstPrinterCommon::printPCRelImm(), llvm::ARMInstPrinter::printPImmediate(), llvm::ARMInstPrinter::printPKHASRShiftImm(), llvm::ARMInstPrinter::printPKHLSLShiftImm(), llvm::ARMInstPrinter::printPostIdxImm8Operand(), llvm::ARMInstPrinter::printPostIdxImm8s4Operand(), llvm::ARMInstPrinter::printPostIdxRegOperand(), llvm::LanaiInstPrinter::printPredicateOperand(), llvm::PPCInstPrinter::printPredicateOperand(), llvm::ARMInstPrinter::printPredicateOperand(), llvm::AArch64InstPrinter::printPrefetchOp(), llvm::AArch64InstPrinter::printPSBHintOp(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::ARMInstPrinter::printRotImmOperand(), llvm::X86InstPrinterCommon::printRoundingControl(), llvm::R600InstPrinter::printRSel(), llvm::PPCInstPrinter::printS16ImmOperand(), llvm::PPCInstPrinter::printS5ImmOperand(), llvm::AMDGPUInstPrinter::printSendMsg(), llvm::ARMInstPrinter::printSetendOperand(), llvm::AArch64InstPrinter::printShifter(), llvm::ARMInstPrinter::printShiftImmOperand(), llvm::AArch64InstPrinter::printSIMDType10Operand(), printSImmOperand(), llvm::ARMInstPrinter::printSORegImmOperand(), llvm::ARMInstPrinter::printSORegRegOperand(), llvm::SparcInstPrinter::printSparcAliasInstr(), llvm::X86InstPrinterCommon::printSSEAVXCC(), llvm::AArch64InstPrinter::printSVELogicalImm(), llvm::AArch64InstPrinter::printSVEPattern(), llvm::AMDGPUInstPrinter::printSwizzle(), llvm::AArch64InstPrinter::printSysAlias(), llvm::AArch64InstPrinter::printSysCROperand(), llvm::AArch64InstPrinter::printSystemPStateField(), llvm::ARMInstPrinter::printT2AddrModeImm0_1020s4Operand(), llvm::ARMInstPrinter::printT2AddrModeImm8OffsetOperand(), llvm::ARMInstPrinter::printT2AddrModeImm8Operand(), llvm::ARMInstPrinter::printT2AddrModeImm8s4OffsetOperand(), llvm::ARMInstPrinter::printT2AddrModeImm8s4Operand(), llvm::ARMInstPrinter::printT2AddrModeSoRegOperand(), llvm::ARMInstPrinter::printT2SOOperand(), llvm::ARMInstPrinter::printThumbAddrModeImm5SOperand(), llvm::ARMInstPrinter::printThumbITMask(), llvm::ARMInstPrinter::printThumbLdrLabelOperand(), llvm::ARMInstPrinter::printThumbS4ImmOperand(), llvm::ARMInstPrinter::printThumbSRImm(), llvm::ARMInstPrinter::printTraceSyncBOption(), llvm::PPCInstPrinter::printU10ImmOperand(), llvm::PPCInstPrinter::printU12ImmOperand(), llvm::PPCInstPrinter::printU16ImmOperand(), llvm::PPCInstPrinter::printU1ImmOperand(), llvm::PPCInstPrinter::printU2ImmOperand(), llvm::PPCInstPrinter::printU3ImmOperand(), llvm::PPCInstPrinter::printU4ImmOperand(), llvm::PPCInstPrinter::printU5ImmOperand(), llvm::PPCInstPrinter::printU6ImmOperand(), llvm::PPCInstPrinter::printU7ImmOperand(), llvm::X86IntelInstPrinter::printU8Imm(), llvm::X86ATTInstPrinter::printU8Imm(), llvm::PPCInstPrinter::printU8ImmOperand(), llvm::AArch64InstPrinter::printUImm12Offset(), printUImmOperand(), llvm::AArch64InstPrinter::printVectorIndex(), llvm::ARMInstPrinter::printVectorIndex(), llvm::AMDGPUInstPrinter::printWaitFlag(), llvm::WebAssemblyInstPrinter::printWebAssemblyP2AlignOperand(), llvm::WebAssemblyInstPrinter::printWebAssemblySignatureOperand(), llvm::R600InstPrinter::printWrite(), llvm::X86InstPrinterCommon::printXOPCC(), llvm::HexagonMCInstrInfo::setInnerLoop(), llvm::HexagonMCInstrInfo::setMemReorderDisabled(), llvm::HexagonMCInstrInfo::setOuterLoop(), SimplifyShortMoveForm(), SwapBits(), and usesGivenOffset().

◆ getInst()

Definition at line 106 of file MCInst.h.

References assert(), InstVal, and isInst().

Referenced by adjustDuplex(), llvm::HexagonShuffler::check(), llvm::HexagonMCCodeEmitter::EncodeSingleInstruction(), llvm::HexagonMCInstrInfo::extenderForIndex(), llvm::HexagonMCInstrInfo::getDuplexPossibilties(), llvm::HexagonMCCodeEmitter::getMachineOpValue(), llvm::HexagonMCInstrInfo::instruction(), isNeitherAnorX(), print(), llvm::HexagonInstPrinter::printInst(), and llvm::HexagonMCInstrInfo::replaceDuplex().

◆ getReg()

|

inline |

Returns the register number.

Definition at line 65 of file MCInst.h.

References assert(), isReg(), and RegVal.

Referenced by addOps(), addOptionalImmOperand(), adjustDuplex(), llvm::adjustPqBits(), checkLowRegisterList(), llvm::X86_MC::X86MCInstrAnalysis::clearsSuperRegisters(), convertFPR32ToFPR64(), llvm::AMDGPUDisassembler::convertMIMGInst(), countMCSymbolRefExpr(), llvm::createBPFbeMCCodeEmitter(), llvm::mca::InstrBuilder::createInstruction(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), decIncOperator(), DecodeLoadAllocTagArrayInstruction(), DecodeRegListOperand(), llvm::HexagonMCInstrInfo::deriveSubInst(), llvm::EmitAnyX86InstComments(), llvm::MipsELFStreamer::EmitInstruction(), llvm::MSP430MCCodeEmitter::encodeInstruction(), llvm::FixupKind(), llvm::PPCMCCodeEmitter::get_crbitm_encoding(), getARMLoadDeprecationInfo(), getARMStoreDeprecationInfo(), getCompoundCandidateGroup(), getCompoundOp(), llvm::HexagonMCInstrInfo::getDuplexCandidateGroup(), getLit64Encoding(), llvm::HexagonMCCodeEmitter::getMachineOpValue(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMemEncodingMMGPImm7Lsl2(), llvm::MipsMCCodeEmitter::getMemEncodingMMSPImm5Lsl2(), llvm::MipsMCCodeEmitter::getMovePRegPairOpValue(), llvm::MipsMCCodeEmitter::getMovePRegSingleOpValue(), llvm::AVRInstPrinter::getPrettyRegisterName(), getRealVLDOpcode(), getRegisterForMxtrC0(), getRegisterForMxtrDSP(), getRegisterForMxtrFP(), llvm::MipsMCCodeEmitter::getRegisterListOpValue(), getRegOperandNumElts(), getRetOpcode(), getSpecialRegForName(), HasConditionalBranch(), llvm::MCInstrDesc::hasDefOfPhysReg(), HasSecRelSymbolRef(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), instIsBreakpoint(), Is32BitMemOperand(), Is64BitMemOperand(), isMatchingOrAlias(), isOrderedCompoundPair(), llvm::HexagonMCInstrInfo::isOrderedDuplexPair(), isReg(), listContainsReg(), LLVMInitializeHexagonDisassembler(), LowerLargeShift(), makeCombineInst(), needsPCRel(), nextReg(), llvm::HexagonMCInstrInfo::predicateInfo(), print(), llvm::ARMInstPrinter::printAddrMode2OffsetOperand(), llvm::ARMInstPrinter::printAddrMode3OffsetOperand(), llvm::ARMInstPrinter::printAddrMode5FP16Operand(), llvm::ARMInstPrinter::printAddrMode5Operand(), llvm::ARMInstPrinter::printAddrMode6OffsetOperand(), llvm::ARMInstPrinter::printAddrMode6Operand(), llvm::ARMInstPrinter::printAddrMode7Operand(), llvm::ARMInstPrinter::printAddrModeImm12Operand(), llvm::ARMInstPrinter::printAddrModeTBB(), llvm::ARMInstPrinter::printAddrModeTBH(), llvm::ARMInstPrinter::printAM2PreOrOffsetIndexOp(), llvm::ARMInstPrinter::printAM3PreOrOffsetIndexOp(), llvm::AArch64InstPrinter::printAMIndexedWB(), llvm::AArch64InstPrinter::printAMNoIndex(), llvm::AArch64InstPrinter::printArithExtend(), llvm::PPCInstPrinter::printcrbitm(), printExpr(), llvm::AArch64InstPrinter::printExtendedRegister(), printFMA3Comments(), llvm::AArch64InstPrinter::printGPR64as32(), llvm::ARMInstPrinter::printGPRPairOperand(), llvm::AArch64InstPrinter::printGPRSeqPairsClassOperand(), llvm::ARMInstPrinter::printInst(), llvm::MSP430InstPrinter::printInst(), llvm::AArch64InstPrinter::printInst(), llvm::PPCInstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::AArch64AppleInstPrinter::printInst(), printMasking(), llvm::BPFInstPrinter::printMemOperand(), llvm::SparcInstPrinter::printMemOperand(), printMemoryBaseRegister(), llvm::X86IntelInstPrinter::printMemReference(), llvm::X86ATTInstPrinter::printMemReference(), llvm::PPCInstPrinter::printMemRegImm(), llvm::PPCInstPrinter::printMemRegReg(), llvm::LanaiInstPrinter::printMemRrOperand(), llvm::ARMInstPrinter::printModImmOperand(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::HexagonInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64InstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::X86InstPrinterCommon::printOptionalSegReg(), llvm::ARMInstPrinter::printPostIdxRegOperand(), llvm::AArch64InstPrinter::printPostIncOperand(), llvm::ARMInstPrinter::printRegisterList(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::ARMInstPrinter::printSBitModifierOperand(), llvm::AArch64InstPrinter::printShiftedRegister(), printSImmOperand(), llvm::ARMInstPrinter::printSORegImmOperand(), llvm::ARMInstPrinter::printSORegRegOperand(), llvm::SparcInstPrinter::printSparcAliasInstr(), llvm::X86IntelInstPrinter::printSTiRegOperand(), llvm::X86ATTInstPrinter::printSTiRegOperand(), llvm::AArch64InstPrinter::printSVERegOp(), llvm::AArch64InstPrinter::printSysAlias(), llvm::ARMInstPrinter::printT2AddrModeImm0_1020s4Operand(), llvm::ARMInstPrinter::printT2AddrModeImm8Operand(), llvm::ARMInstPrinter::printT2AddrModeImm8s4Operand(), llvm::ARMInstPrinter::printT2AddrModeSoRegOperand(), llvm::ARMInstPrinter::printT2SOOperand(), llvm::ARMInstPrinter::printThumbAddrModeImm5SOperand(), llvm::ARMInstPrinter::printThumbAddrModeRROperand(), llvm::AArch64InstPrinter::printVectorList(), llvm::ARMInstPrinter::printVectorListFour(), llvm::ARMInstPrinter::printVectorListFourAllLanes(), llvm::ARMInstPrinter::printVectorListFourSpaced(), llvm::ARMInstPrinter::printVectorListFourSpacedAllLanes(), llvm::ARMInstPrinter::printVectorListOne(), llvm::ARMInstPrinter::printVectorListOneAllLanes(), llvm::ARMInstPrinter::printVectorListThree(), llvm::ARMInstPrinter::printVectorListThreeAllLanes(), llvm::ARMInstPrinter::printVectorListThreeSpaced(), llvm::ARMInstPrinter::printVectorListThreeSpacedAllLanes(), llvm::ARMInstPrinter::printVectorListTwo(), llvm::ARMInstPrinter::printVectorListTwoAllLanes(), llvm::ARMInstPrinter::printVectorListTwoSpaced(), llvm::ARMInstPrinter::printVectorListTwoSpacedAllLanes(), llvm::AArch64InstPrinter::printVRegOperand(), llvm::AArch64InstPrinter::printZPRasFPR(), llvm::HexagonMCChecker::reportBranchErrors(), SimplifyMOVSX(), SimplifyShortImmForm(), SimplifyShortMoveForm(), llvm::HexagonMCInstrInfo::subInstWouldBeExtended(), SwapBits(), and llvm::AArch64ExternalSymbolizer::tryAddingSymbolicOperand().

◆ isBareSymbolRef()

| bool MCOperand::isBareSymbolRef | ( | ) | const |

Definition at line 48 of file MCInst.cpp.

References assert(), getExpr(), llvm::MCExpr::getKind(), isExpr(), llvm::MCExpr::SymbolRef, and llvm::MCSymbolRefExpr::VK_None.

Referenced by createInst().

◆ isExpr()

|

inline |

Definition at line 61 of file MCInst.h.

Referenced by llvm::adjustPqBits(), convertFPR32ToFPR64(), countMCSymbolRefExpr(), llvm::createBPFbeMCCodeEmitter(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::MCStreamer::EmitInstruction(), llvm::HexagonMCELFStreamer::EmitSymbol(), llvm::MSP430MCCodeEmitter::encodeInstruction(), encodeThumbBLOffset(), llvm::FixupKind(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget7OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue(), getBranchTargetOpValue(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue1SImm16(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueLsl2MMR6(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMPC10(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMR6(), getExpr(), llvm::HexagonMCInstrInfo::getExtendableOperand(), llvm::MipsMCCodeEmitter::getJumpOffset16OpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValueMM(), getLit64Encoding(), llvm::MipsMCCodeEmitter::getMachineOpValue(), llvm::AVRInstPrinter::getPrettyRegisterName(), getRealVLDOpcode(), getRelaxedOpcode(), llvm::MipsMCCodeEmitter::getSimm18Lsl3Encoding(), llvm::MipsMCCodeEmitter::getSimm19Lsl2Encoding(), llvm::MipsMCCodeEmitter::getUImm5Lsl2Encoding(), HasConditionalBranch(), HasSecRelSymbolRef(), isBareSymbolRef(), isMatchingOrAlias(), makeCombineInst(), llvm::HexagonMCInstrInfo::minConstant(), needsPCRel(), print(), llvm::AArch64InstPrinter::printAddSubImm(), llvm::ARMInstPrinter::printAdrLabelOperand(), llvm::AArch64InstPrinter::printAMIndexedWB(), llvm::HexagonInstPrinter::printBrtarget(), llvm::BPFInstPrinter::printBrTargetOperand(), printExpr(), llvm::LanaiInstPrinter::printHi16AndImmOperand(), llvm::LanaiInstPrinter::printHi16ImmOperand(), llvm::BPFInstPrinter::printImm64Operand(), llvm::MSP430InstPrinter::printInst(), llvm::AArch64InstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::R600InstPrinter::printLiteral(), llvm::LanaiInstPrinter::printLo16AndImmOperand(), llvm::LanaiInstPrinter::printMemImmOperand(), llvm::X86IntelInstPrinter::printMemOffset(), llvm::X86ATTInstPrinter::printMemOffset(), printMemoryImmediateOffset(), llvm::X86IntelInstPrinter::printMemReference(), llvm::X86ATTInstPrinter::printMemReference(), llvm::ARMInstPrinter::printModImmOperand(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::HexagonInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64InstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::X86InstPrinterCommon::printPCRelImm(), llvm::NVPTXInstPrinter::printProtoIdent(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::ARMInstPrinter::printThumbLdrLabelOperand(), llvm::X86IntelInstPrinter::printU8Imm(), llvm::X86ATTInstPrinter::printU8Imm(), llvm::AArch64InstPrinter::printUImm12Offset(), setExpr(), SimplifyShortImmForm(), SimplifyShortMoveForm(), and smallData().

◆ isFPImm()

|

inline |

Definition at line 60 of file MCInst.h.

Referenced by getFPImm(), getLit64Encoding(), llvm::MipsMCCodeEmitter::getMachineOpValue(), print(), llvm::AArch64InstPrinter::printFPImmOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::AMDGPUInstPrinter::printRegOperand(), and setFPImm().

◆ isImm()

|

inline |

Definition at line 59 of file MCInst.h.

Referenced by addNegOperand(), llvm::adjustPqBits(), countMCSymbolRefExpr(), llvm::createBPFbeMCCodeEmitter(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), llvm::HexagonMCInstrInfo::deriveExtender(), llvm::EmitAnyX86InstComments(), llvm::MSP430MCCodeEmitter::encodeInstruction(), llvm::RuntimeDyldCheckerExprEval::evaluate(), evaluateAsConstantImm(), llvm::FixupKind(), llvm::PPCMCCodeEmitter::getAbsCondBrEncoding(), llvm::PPCMCCodeEmitter::getAbsDirectBrEncoding(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget21OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValue(), llvm::MipsMCCodeEmitter::getBranchTarget26OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTarget7OpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue(), getBranchTargetOpValue(), llvm::MipsMCCodeEmitter::getBranchTargetOpValue1SImm16(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueLsl2MMR6(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMM(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMPC10(), llvm::MipsMCCodeEmitter::getBranchTargetOpValueMMR6(), llvm::PPCMCCodeEmitter::getCondBrEncoding(), llvm::PPCMCCodeEmitter::getDirectBrEncoding(), llvm::HexagonMCInstrInfo::getExtendableOperand(), getImm(), llvm::PPCMCCodeEmitter::getImm16Encoding(), getITDeprecationInfo(), llvm::MipsMCCodeEmitter::getJumpOffset16OpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValue(), llvm::MipsMCCodeEmitter::getJumpTargetOpValueMM(), getLit64Encoding(), llvm::HexagonMCCodeEmitter::getMachineOpValue(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), getMCRDeprecationInfo(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm4sp(), llvm::AVRInstPrinter::getPrettyRegisterName(), getRealVLDOpcode(), getRegisterForMxtrC0(), llvm::MipsMCCodeEmitter::getSimm18Lsl3Encoding(), llvm::MipsMCCodeEmitter::getSimm19Lsl2Encoding(), llvm::MipsMCCodeEmitter::getSimm23Lsl2Encoding(), llvm::MipsMCCodeEmitter::getSImm3Lsa2Value(), llvm::MipsMCCodeEmitter::getSImm9AddiuspValue(), llvm::MipsMCCodeEmitter::getSizeInsEncoding(), getSpecialRegForName(), llvm::MipsMCCodeEmitter::getUImm3Mod8Encoding(), llvm::MipsMCCodeEmitter::getUImm4AndValue(), llvm::MipsMCCodeEmitter::getUImm5Lsl2Encoding(), llvm::MipsMCCodeEmitter::getUImm6Lsl2Encoding(), llvm::MipsMCCodeEmitter::getUImmWithOffsetEncoding(), HasConditionalBranch(), HasSecRelSymbolRef(), llvm::HexagonMCInstrInfo::isBundle(), llvm::HexagonMCInstrInfo::isConstExtended(), isShiftedUIntAtAnyPosition(), llvm::LowerARMMachineInstrToMCInst(), LowerLargeShift(), needsPCRel(), nextReg(), PostOperandDecodeAdjust(), print(), llvm::PPCInstPrinter::printAbsBranchOperand(), llvm::AArch64InstPrinter::printAddSubImm(), llvm::AArch64InstPrinter::printAdrpLabel(), llvm::AArch64InstPrinter::printAlignedLabel(), llvm::AArch64InstPrinter::printAMIndexedWB(), llvm::ARMInstPrinter::printBitfieldInvMaskImmOperand(), llvm::PPCInstPrinter::printBranchOperand(), llvm::BPFInstPrinter::printBrTargetOperand(), printExpr(), llvm::LanaiInstPrinter::printHi16AndImmOperand(), llvm::LanaiInstPrinter::printHi16ImmOperand(), llvm::AMDGPUInstPrinter::printIfSet(), llvm::BPFInstPrinter::printImm64Operand(), llvm::MSP430InstPrinter::printInst(), llvm::AArch64InstPrinter::printInst(), llvm::WebAssemblyInstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::R600InstPrinter::printLiteral(), llvm::LanaiInstPrinter::printLo16AndImmOperand(), llvm::LanaiInstPrinter::printMemImmOperand(), llvm::X86IntelInstPrinter::printMemOffset(), llvm::X86ATTInstPrinter::printMemOffset(), llvm::BPFInstPrinter::printMemOperand(), llvm::NVPTXInstPrinter::printMemOperand(), llvm::SparcInstPrinter::printMemOperand(), printMemoryImmediateOffset(), llvm::X86IntelInstPrinter::printMemReference(), llvm::X86ATTInstPrinter::printMemReference(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64InstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::X86InstPrinterCommon::printPCRelImm(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::PPCInstPrinter::printS16ImmOperand(), printSImmOperand(), llvm::SparcInstPrinter::printSparcAliasInstr(), llvm::AArch64InstPrinter::printSysCROperand(), llvm::ARMInstPrinter::printT2SOOperand(), llvm::PPCInstPrinter::printU16ImmOperand(), llvm::AArch64InstPrinter::printUImm12Offset(), setImm(), SimplifyShortImmForm(), SimplifyShortMoveForm(), and SwapBits().

◆ isInst()

|

inline |

◆ isReg()

|

inline |

Definition at line 58 of file MCInst.h.

Referenced by addOps(), adjustDuplex(), llvm::adjustPqBits(), countMCSymbolRefExpr(), llvm::createBPFbeMCCodeEmitter(), llvm::mca::InstrBuilder::createInstruction(), llvm::createR600MCCodeEmitter(), llvm::createRISCVMCCodeEmitter(), llvm::MipsELFStreamer::EmitInstruction(), llvm::MSP430MCCodeEmitter::encodeInstruction(), llvm::FixupKind(), llvm::PPCMCCodeEmitter::getAbsCondBrEncoding(), llvm::PPCMCCodeEmitter::getAbsDirectBrEncoding(), getARMLoadDeprecationInfo(), getARMStoreDeprecationInfo(), llvm::PPCMCCodeEmitter::getCondBrEncoding(), llvm::PPCMCCodeEmitter::getDirectBrEncoding(), llvm::PPCMCCodeEmitter::getImm16Encoding(), getLit64Encoding(), llvm::HexagonMCCodeEmitter::getMachineOpValue(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMachineOpValue(), llvm::MipsMCCodeEmitter::getMemEncoding(), llvm::MipsMCCodeEmitter::getMemEncodingMMGPImm7Lsl2(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm11(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm12(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm16(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm4(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm4Lsl1(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm4Lsl2(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm4sp(), llvm::MipsMCCodeEmitter::getMemEncodingMMImm9(), llvm::MipsMCCodeEmitter::getMemEncodingMMSPImm5Lsl2(), llvm::PPCMCCodeEmitter::getMemRIEncoding(), llvm::PPCMCCodeEmitter::getMemRIX16Encoding(), llvm::PPCMCCodeEmitter::getMemRIXEncoding(), llvm::MipsMCCodeEmitter::getMovePRegSingleOpValue(), llvm::HexagonMCInstrInfo::getNewValueOperand(), llvm::HexagonMCInstrInfo::getNewValueOperand2(), llvm::AVRInstPrinter::getPrettyRegisterName(), getReg(), llvm::PPCMCCodeEmitter::getSPE2DisEncoding(), llvm::PPCMCCodeEmitter::getSPE4DisEncoding(), llvm::PPCMCCodeEmitter::getSPE8DisEncoding(), getSpecialRegForName(), llvm::PPCMCCodeEmitter::getTLSRegEncoding(), HasConditionalBranch(), llvm::MCInstrDesc::hasDefOfPhysReg(), HasSecRelSymbolRef(), hasShortDelaySlot(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), isMatchingOrAlias(), llvm::HexagonMCInstrInfo::isOrderedDuplexPair(), isReg(), needsPCRel(), nextReg(), PostOperandDecodeAdjust(), print(), llvm::ARMInstPrinter::printAddrMode2Operand(), llvm::ARMInstPrinter::printAddrMode3Operand(), llvm::ARMInstPrinter::printAddrMode5FP16Operand(), llvm::ARMInstPrinter::printAddrMode5Operand(), llvm::ARMInstPrinter::printAddrModeImm12Operand(), printExpr(), llvm::MSP430InstPrinter::printInst(), llvm::MipsInstPrinter::printInst(), llvm::BPFInstPrinter::printMemOperand(), llvm::SparcInstPrinter::printMemOperand(), printMemoryBaseRegister(), llvm::LanaiInstPrinter::printMemRrOperand(), llvm::BPFInstPrinter::printOperand(), llvm::LanaiInstPrinter::printOperand(), llvm::RISCVInstPrinter::printOperand(), llvm::X86IntelInstPrinter::printOperand(), llvm::NVPTXInstPrinter::printOperand(), llvm::HexagonInstPrinter::printOperand(), llvm::SystemZInstPrinter::printOperand(), llvm::X86ATTInstPrinter::printOperand(), llvm::ARMInstPrinter::printOperand(), llvm::SparcInstPrinter::printOperand(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64InstPrinter::printOperand(), llvm::R600InstPrinter::printOperand(), llvm::AArch64InstPrinter::printPostIncOperand(), llvm::AMDGPUInstPrinter::printRegOperand(), llvm::SparcInstPrinter::printSparcAliasInstr(), llvm::ARMInstPrinter::printT2AddrModeImm8s4Operand(), llvm::ARMInstPrinter::printThumbAddrModeImm5SOperand(), llvm::ARMInstPrinter::printThumbAddrModeRROperand(), llvm::AArch64InstPrinter::printVRegOperand(), llvm::HexagonMCChecker::reportBranchErrors(), setReg(), SimplifyShortImmForm(), SimplifyShortMoveForm(), SwapBits(), and llvm::mca::verifyOperands().

◆ isValid()

|

inline |

Definition at line 57 of file MCInst.h.

Referenced by addOperand(), llvm::XCoreMCInstLower::Lower(), llvm::ARCMCInstLower::Lower(), llvm::MipsMCInstLower::Lower(), llvm::LowerSparcMachineInstrToMCInst(), print(), and llvm::MipsAsmPrinter::runOnMachineFunction().

◆ print()

| void MCOperand::print | ( | raw_ostream & | OS | ) | const |

Definition at line 21 of file MCInst.cpp.

References getExpr(), getFPImm(), getImm(), getInst(), getReg(), isExpr(), isFPImm(), isImm(), isInst(), isReg(), and isValid().

Referenced by createInst(), dump(), llvm::MCInst::dump(), llvm::MCInst::insert(), and llvm::operator<<().

◆ setExpr()

Definition at line 101 of file MCInst.h.

References assert(), ExprVal, and isExpr().

Referenced by llvm::HexagonAsmPrinter::HexagonProcessInstruction(), and makeCombineInst().

◆ setFPImm()

|

inline |

◆ setImm()

|

inline |

Definition at line 81 of file MCInst.h.

References assert(), ImmVal, and isImm().

Referenced by countMCSymbolRefExpr(), getRealVLDOpcode(), isRegOrImmWithInputMods(), llvm::LowerARMMachineInstrToMCInst(), LowerLargeShift(), PostOperandDecodeAdjust(), llvm::HexagonMCInstrInfo::setInnerLoop(), llvm::HexagonMCInstrInfo::setMemReorderDisabled(), and llvm::HexagonMCInstrInfo::setOuterLoop().

◆ setInst()

◆ setReg()

|

inline |

Set the register number.

Definition at line 71 of file MCInst.h.

References assert(), isReg(), Reg, and RegVal.

Referenced by addOptionalImmOperand(), adjustDuplex(), llvm::HexagonAsmPrinter::HexagonProcessInstruction(), LowerLargeShift(), makeCombineInst(), and PostOperandDecodeAdjust().

Member Data Documentation

◆ ExprVal

Definition at line 50 of file MCInst.h.

Referenced by createExpr(), getExpr(), and setExpr().

◆ FPImmVal

| double llvm::MCOperand::FPImmVal |

Definition at line 49 of file MCInst.h.

Referenced by createFPImm(), getFPImm(), and setFPImm().

◆ ImmVal

| int64_t llvm::MCOperand::ImmVal |

Definition at line 48 of file MCInst.h.

Referenced by createImm(), getImm(), and setImm().

◆ InstVal

Definition at line 51 of file MCInst.h.

Referenced by createInst(), getInst(), and setInst().

◆ RegVal

| unsigned llvm::MCOperand::RegVal |

Definition at line 47 of file MCInst.h.

Referenced by createReg(), getReg(), and setReg().

The documentation for this class was generated from the following files:

- include/llvm/MC/MCInst.h

- lib/MC/MCInst.cpp

1.8.13

1.8.13