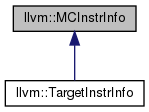

Interface to description of machine instruction set. More...

#include "llvm/MC/MCInstrInfo.h"

Public Member Functions | |

| void | InitMCInstrInfo (const MCInstrDesc *D, const unsigned *NI, const char *ND, unsigned NO) |

| Initialize MCInstrInfo, called by TableGen auto-generated routines. More... | |

| unsigned | getNumOpcodes () const |

| const MCInstrDesc & | get (unsigned Opcode) const |

| Return the machine instruction descriptor that corresponds to the specified instruction opcode. More... | |

| StringRef | getName (unsigned Opcode) const |

| Returns the name for the instructions with the given opcode. More... | |

Detailed Description

Interface to description of machine instruction set.

Definition at line 24 of file MCInstrInfo.h.

Member Function Documentation

◆ get()

|

inline |

Return the machine instruction descriptor that corresponds to the specified instruction opcode.

Definition at line 45 of file MCInstrInfo.h.

References assert().

Referenced by addEpilog(), addEpilogLeaf(), addEpilogOnlyR10(), llvm::MachineBasicBlock::addLiveIn(), addProlog(), addPrologLeaf(), addSegmentsWithValNo(), allPhiOperandsUndefined(), llvm::analyzeArguments(), AnyAliasLiveIn(), buildEXP(), canClobberPhysRegDefs(), canClobberReachingPhysRegUse(), llvm::TailDuplicator::canTailDuplicate(), CheckForPhysRegDependency(), llvm::X86_MC::X86MCInstrAnalysis::clearsSuperRegisters(), CombineCVTAToLocal(), combineRestoreADD(), combineRestoreOR(), combineRestoreSETHIi(), ComputeCommonTailLength(), llvm::TargetSchedModel::computeInstrLatency(), llvm::MCSchedModel::computeInstrLatency(), llvm::ScheduleDAGSDNodes::computeOperandLatency(), llvm::TargetSchedModel::computeReciprocalThroughput(), llvm::FastISel::constrainOperandRegClass(), llvm::constrainRegToClass(), convertCalleeSaveRestoreToSPPrePostIncDec(), ConvertImplicitDefToConstZero(), createARMMCRelocationInfo(), createLanaiElfRelocation(), createMipsObjectTargetStreamer(), createPHIsForCMOVsInSinkBB(), createPHIsForSelects(), createSwiftErrorEntriesInEntryBlock(), createWinCOFFStreamer(), llvm::SplitEditor::dump(), llvm::PPCFrameLowering::eliminateCallFramePseudoInstr(), llvm::BPFRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::LanaiRegisterInfo::eliminateFrameIndex(), llvm::AVRRegisterInfo::eliminateFrameIndex(), emitAlignedDPRCS2Restores(), emitAlignedDPRCS2Spills(), emitAligningInstructions(), llvm::PPCTargetLowering::EmitAtomicBinary(), emitBuildPairF64Pseudo(), llvm::AArch64FrameLowering::emitCalleeSavedFrameMoves(), EmitCfiOffset(), emitClzero(), llvm::InstrEmitter::EmitDbgLabel(), llvm::InstrEmitter::EmitDbgValue(), EmitDefCfaOffset(), EmitDefCfaRegister(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::emitFrameOffset(), emitIncrement(), llvm::BPFTargetLowering::EmitInstrWithCustomInserter(), llvm::RISCVTargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86TargetLowering::EmitInstrWithCustomInserter(), llvm::MachineRegisterInfo::EmitLiveInCopies(), llvm::ARMBaseRegisterInfo::emitLoadConstPool(), emitMonitor(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), emitPostLd(), emitPostSt(), llvm::NVPTXFrameLowering::emitPrologue(), llvm::AArch64FrameLowering::emitPrologue(), emitRDPKRU(), llvm::MSP430TargetLowering::EmitShiftInstr(), emitSplitF64Pseudo(), emitThumb2LoadConstPool(), llvm::emitThumbRegPlusImmediate(), emitThumbRegPlusImmInReg(), emitWRPKRU(), emitXBegin(), llvm::MipsMCCodeEmitter::encodeInstruction(), llvm::MSP430MCCodeEmitter::encodeInstruction(), llvm::MCInstrAnalysis::evaluateBranch(), llvm::InstructionSelector::executeMatchTable(), expandLoadStackGuard(), expandMOV32r1(), ExpandMOVImmSExti8(), llvm::AArch64InstrInfo::expandPostRAPseudo(), llvm::SparcTargetLowering::expandSelectCC(), expandXorFP(), llvm::FastISel::fastEmitInst_(), llvm::FastISel::fastEmitInst_extractsubreg(), llvm::FastISel::fastEmitInst_f(), llvm::FastISel::fastEmitInst_i(), llvm::FastISel::fastEmitInst_r(), llvm::FastISel::fastEmitInst_ri(), llvm::FastISel::fastEmitInst_rii(), llvm::FastISel::fastEmitInst_rr(), llvm::FastISel::fastEmitInst_rri(), llvm::FastISel::fastEmitInst_rrr(), llvm::finalizeBundle(), findNextInsertLocation(), findTemporariesForLR(), llvm::fixStackStores(), foldPatchpoint(), FuseInst(), FuseTwoAddrInst(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), genFusedMultiply(), genMaddR(), getComparePred(), llvm::HexagonMCInstrInfo::getDesc(), llvm::ARMTargetLowering::getExceptionSelectorRegister(), llvm::LLVMDisasmContext::getInstrInfo(), llvm::PPCMCCodeEmitter::getInstSizeInBytes(), getItineraryLatency(), getLatency(), llvm::PPCMCCodeEmitter::getMachineOpValue(), llvm::TargetMachine::getMCInstrInfo(), getNewSource(), getPhysicalRegisterVT(), llvm::AVRInstPrinter::getPrettyRegisterName(), llvm::MCSchedModel::getReciprocalThroughput(), getRegsUsedByPHIs(), getRetpolineSymbol(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::BPFTargetLowering::getTargetNodeName(), llvm::HexagonMCInstrInfo::getType(), getUnderlyingArgReg(), llvm::MipsTargetLowering::HandleByVal(), HandleVRSaveUpdate(), HasConditionalBranch(), hasUseAfterLoop(), IfNeededExtSP(), IfNeededLDAWSP(), INITIALIZE_PASS(), llvm::ResourcePriorityQueue::initNumRegDefsLeft(), llvm::SITargetLowering::insertCopiesSplitCSR(), llvm::AArch64TargetLowering::insertCopiesSplitCSR(), llvm::PPCTargetLowering::insertCopiesSplitCSR(), insertCopy(), insertDivByZeroTrap(), InsertLDR_STR(), InsertNewDef(), insertNopBeforeInstruction(), insertPHI(), InsertSEH(), llvm::MCInstrAnalysis::isBranch(), llvm::MCInstrAnalysis::isCall(), llvm::MCInstrAnalysis::isConditionalBranch(), isCopyFeedingInvariantStore(), llvm::isCopyMulResult(), isHardwareLoop(), llvm::MCInstrAnalysis::isIndirectBranch(), llvm::X86TargetLowering::isIntDivCheap(), llvm::ResourcePriorityQueue::isResourceAvailable(), llvm::MCInstrAnalysis::isReturn(), IsSmallMemAccess(), llvm::HexagonMCInstrInfo::isSolo(), llvm::MCInstrAnalysis::isTerminator(), llvm::MCInstrAnalysis::isUnconditionalBranch(), IsUnconditionalJump(), LowerFPToInt(), MakeM0Inst(), mapWasmLandingPadIndex(), llvm::ARMBaseRegisterInfo::materializeFrameBaseRegister(), mergeOperations(), Mips16WhichOp8uOr16simm(), parseCond(), llvm::PPCHazardRecognizer970::PPCHazardRecognizer970(), llvm::WebAssemblyInstPrinter::printInst(), llvm::X86InstPrinterCommon::printInstFlags(), printMasking(), llvm::WebAssemblyInstPrinter::printOperand(), llvm::PPCInstPrinter::printOperand(), llvm::AArch64FrameLowering::processFunctionBeforeFrameFinalized(), ProcessSourceNode(), propagateSwiftErrorVRegs(), llvm::TargetInstrInfo::reassociateOps(), replaceFI(), llvm::ARMTargetLowering::ReplaceNodeResults(), llvm::ResourcePriorityQueue::reserveResources(), llvm::ARMFrameLowering::ResolveFrameIndexReference(), llvm::SystemZFrameLowering::restoreCalleeSavedRegisters(), llvm::MSP430FrameLowering::restoreCalleeSavedRegisters(), llvm::AArch64FrameLowering::restoreCalleeSavedRegisters(), RestoreSpillList(), rewritesSort(), llvm::UnreachableBlockElimPass::run(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::MachinePipeliner::runOnMachineFunction(), llvm::ThumbRegisterInfo::saveScavengerRegister(), llvm::SelectionDAGISel::SelectCodeCommon(), selectCopy(), selectFP16CopyFromGPR32(), llvm::FunctionLoweringInfo::set(), setCallTargetReg(), llvm::Thumb1FrameLowering::spillCalleeSavedRegisters(), llvm::SystemZFrameLowering::spillCalleeSavedRegisters(), llvm::MipsSEFrameLowering::spillCalleeSavedRegisters(), llvm::MSP430FrameLowering::spillCalleeSavedRegisters(), llvm::AArch64FrameLowering::spillCalleeSavedRegisters(), llvm::ResourcePriorityQueue::SUSchedulingCost(), usedAsAddr(), llvm::LegalizerInfo::verify(), and llvm::mca::verifyOperands().

◆ getName()

Returns the name for the instructions with the given opcode.

Definition at line 51 of file MCInstrInfo.h.

References assert().

Referenced by fuseInstructionPair(), llvm::X86Disassembler::GetInstrName(), llvm::HexagonMCInstrInfo::getName(), llvm::MCInstPrinter::getOpcodeName(), llvm::SelectionDAGISel::isOrEquivalentToAdd(), llvm::MachineInstr::print(), selectCopy(), llvm::LegalizerInfo::verify(), and llvm::mca::verifyOperands().

◆ getNumOpcodes()

|

inline |

Definition at line 41 of file MCInstrInfo.h.

◆ InitMCInstrInfo()

|

inline |

Initialize MCInstrInfo, called by TableGen auto-generated routines.

DO NOT USE.

Definition at line 33 of file MCInstrInfo.h.

References D.

The documentation for this class was generated from the following file:

- include/llvm/MC/MCInstrInfo.h

1.8.13

1.8.13