#include "PPC.h"#include "PPCInstrInfo.h"#include "llvm/CodeGen/CallingConvLower.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineMemOperand.h"#include "llvm/CodeGen/SelectionDAG.h"#include "llvm/CodeGen/SelectionDAGNodes.h"#include "llvm/CodeGen/TargetLowering.h"#include "llvm/CodeGen/ValueTypes.h"#include "llvm/IR/Attributes.h"#include "llvm/IR/CallingConv.h"#include "llvm/IR/Function.h"#include "llvm/IR/InlineAsm.h"#include "llvm/IR/Metadata.h"#include "llvm/IR/Type.h"#include "llvm/Support/MachineValueType.h"#include <utility>

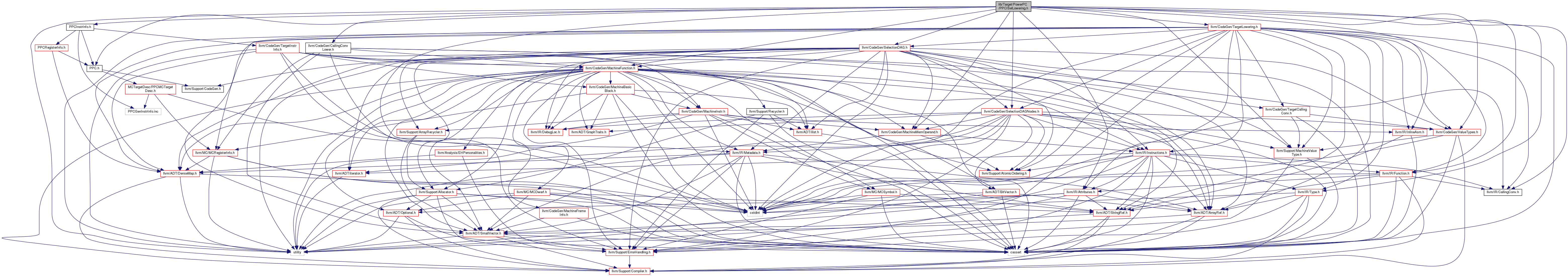

Include dependency graph for PPCISelLowering.h:

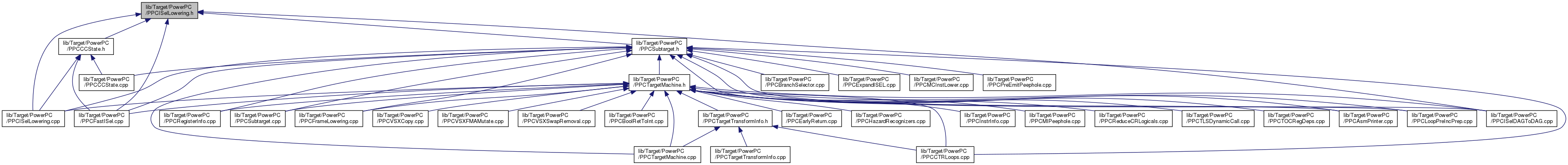

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| class | llvm::PPCTargetLowering |

Namespaces | |

| llvm | |

| This class represents lattice values for constants. | |

| llvm::PPCISD | |

| llvm::PPC | |

| Define some predicates that are used for node matching. | |

Functions | |

| bool | llvm::PPC::isVPKUHUMShuffleMask (ShuffleVectorSDNode *N, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVPKUHUMShuffleMask - Return true if this is the shuffle mask for a VPKUHUM instruction. More... | |

| bool | llvm::PPC::isVPKUWUMShuffleMask (ShuffleVectorSDNode *N, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVPKUWUMShuffleMask - Return true if this is the shuffle mask for a VPKUWUM instruction. More... | |

| bool | llvm::PPC::isVPKUDUMShuffleMask (ShuffleVectorSDNode *N, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVPKUDUMShuffleMask - Return true if this is the shuffle mask for a VPKUDUM instruction. More... | |

| bool | llvm::PPC::isVMRGLShuffleMask (ShuffleVectorSDNode *N, unsigned UnitSize, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVMRGLShuffleMask - Return true if this is a shuffle mask suitable for a VRGL* instruction with the specified unit size (1,2 or 4 bytes). More... | |

| bool | llvm::PPC::isVMRGHShuffleMask (ShuffleVectorSDNode *N, unsigned UnitSize, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVMRGHShuffleMask - Return true if this is a shuffle mask suitable for a VRGH* instruction with the specified unit size (1,2 or 4 bytes). More... | |

| bool | llvm::PPC::isVMRGEOShuffleMask (ShuffleVectorSDNode *N, bool CheckEven, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVMRGEOShuffleMask - Return true if this is a shuffle mask suitable for a VMRGEW or VMRGOW instruction More... | |

| bool | llvm::PPC::isXXSLDWIShuffleMask (ShuffleVectorSDNode *N, unsigned &ShiftElts, bool &Swap, bool IsLE) |

| isXXSLDWIShuffleMask - Return true if this is a shuffle mask suitable for a XXSLDWI instruction. More... | |

| bool | llvm::PPC::isXXBRHShuffleMask (ShuffleVectorSDNode *N) |

| isXXBRHShuffleMask - Return true if this is a shuffle mask suitable for a XXBRH instruction. More... | |

| bool | llvm::PPC::isXXBRWShuffleMask (ShuffleVectorSDNode *N) |

| isXXBRWShuffleMask - Return true if this is a shuffle mask suitable for a XXBRW instruction. More... | |

| bool | llvm::PPC::isXXBRDShuffleMask (ShuffleVectorSDNode *N) |

| isXXBRDShuffleMask - Return true if this is a shuffle mask suitable for a XXBRD instruction. More... | |

| bool | llvm::PPC::isXXBRQShuffleMask (ShuffleVectorSDNode *N) |

| isXXBRQShuffleMask - Return true if this is a shuffle mask suitable for a XXBRQ instruction. More... | |

| bool | llvm::PPC::isXXPERMDIShuffleMask (ShuffleVectorSDNode *N, unsigned &ShiftElts, bool &Swap, bool IsLE) |

| isXXPERMDIShuffleMask - Return true if this is a shuffle mask suitable for a XXPERMDI instruction. More... | |

| int | llvm::PPC::isVSLDOIShuffleMask (SDNode *N, unsigned ShuffleKind, SelectionDAG &DAG) |

| isVSLDOIShuffleMask - If this is a vsldoi shuffle mask, return the shift amount, otherwise return -1. More... | |

| bool | llvm::PPC::isSplatShuffleMask (ShuffleVectorSDNode *N, unsigned EltSize) |

| isSplatShuffleMask - Return true if the specified VECTOR_SHUFFLE operand specifies a splat of a single element that is suitable for input to VSPLTB/VSPLTH/VSPLTW. More... | |

| bool | llvm::PPC::isXXINSERTWMask (ShuffleVectorSDNode *N, unsigned &ShiftElts, unsigned &InsertAtByte, bool &Swap, bool IsLE) |

| isXXINSERTWMask - Return true if this VECTOR_SHUFFLE can be handled by the XXINSERTW instruction introduced in ISA 3.0. More... | |

| unsigned | llvm::PPC::getVSPLTImmediate (SDNode *N, unsigned EltSize, SelectionDAG &DAG) |

| getVSPLTImmediate - Return the appropriate VSPLT* immediate to splat the specified isSplatShuffleMask VECTOR_SHUFFLE mask. More... | |

| SDValue | llvm::PPC::get_VSPLTI_elt (SDNode *N, unsigned ByteSize, SelectionDAG &DAG) |

| get_VSPLTI_elt - If this is a build_vector of constants which can be formed by using a vspltis[bhw] instruction of the specified element size, return the constant being splatted. More... | |

| int | llvm::PPC::isQVALIGNIShuffleMask (SDNode *N) |

| If this is a qvaligni shuffle mask, return the shift amount, otherwise return -1. More... | |

| FastISel * | llvm::PPC::createFastISel (FunctionLoweringInfo &FuncInfo, const TargetLibraryInfo *LibInfo) |

| bool | llvm::CC_PPC32_SVR4_Custom_Dummy (unsigned &ValNo, MVT &ValVT, MVT &LocVT, CCValAssign::LocInfo &LocInfo, ISD::ArgFlagsTy &ArgFlags, CCState &State) |

| bool | llvm::CC_PPC32_SVR4_Custom_AlignArgRegs (unsigned &ValNo, MVT &ValVT, MVT &LocVT, CCValAssign::LocInfo &LocInfo, ISD::ArgFlagsTy &ArgFlags, CCState &State) |

| bool | llvm::CC_PPC32_SVR4_Custom_SkipLastArgRegsPPCF128 (unsigned &ValNo, MVT &ValVT, MVT &LocVT, CCValAssign::LocInfo &LocInfo, ISD::ArgFlagsTy &ArgFlags, CCState &State) |

| bool | llvm::CC_PPC32_SVR4_Custom_AlignFPArgRegs (unsigned &ValNo, MVT &ValVT, MVT &LocVT, CCValAssign::LocInfo &LocInfo, ISD::ArgFlagsTy &ArgFlags, CCState &State) |

| bool | llvm::isIntS16Immediate (SDNode *N, int16_t &Imm) |

| isIntS16Immediate - This method tests to see if the node is either a 32-bit or 64-bit immediate, and if the value can be accurately represented as a sign extension from a 16-bit value. More... | |

| bool | llvm::isIntS16Immediate (SDValue Op, int16_t &Imm) |

1.8.13

1.8.13