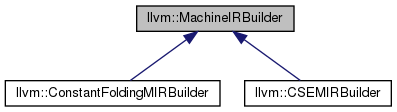

Helper class to build MachineInstr. More...

#include "llvm/CodeGen/GlobalISel/MachineIRBuilder.h"

Public Member Functions | |

| MachineIRBuilder ()=default | |

| Some constructors for easy use. More... | |

| MachineIRBuilder (MachineFunction &MF) | |

| MachineIRBuilder (MachineInstr &MI) | |

| virtual | ~MachineIRBuilder ()=default |

| MachineIRBuilder (const MachineIRBuilderState &BState) | |

| const TargetInstrInfo & | getTII () |

| MachineFunction & | getMF () |

| Getter for the function we currently build. More... | |

| const DebugLoc & | getDL () |

| Getter for DebugLoc. More... | |

| MachineRegisterInfo * | getMRI () |

| Getter for MRI. More... | |

| const MachineRegisterInfo * | getMRI () const |

| MachineIRBuilderState & | getState () |

| Getter for the State. More... | |

| const MachineBasicBlock & | getMBB () const |

| Getter for the basic block we currently build. More... | |

| MachineBasicBlock & | getMBB () |

| GISelCSEInfo * | getCSEInfo () |

| const GISelCSEInfo * | getCSEInfo () const |

| MachineBasicBlock::iterator | getInsertPt () |

| Current insertion point for new instructions. More... | |

| void | setInsertPt (MachineBasicBlock &MBB, MachineBasicBlock::iterator II) |

| Set the insertion point before the specified position. More... | |

| void | setCSEInfo (GISelCSEInfo *Info) |

| void | setChangeObserver (GISelChangeObserver &Observer) |

| void | stopObservingChanges () |

| void | setDebugLoc (const DebugLoc &DL) |

Set the debug location to DL for all the next build instructions. More... | |

| DebugLoc | getDebugLoc () |

| Get the current instruction's debug location. More... | |

| MachineInstrBuilder | buildInstr (unsigned Opcode) |

Build and insert <empty> = Opcode <empty>. More... | |

| MachineInstrBuilder | buildInstrNoInsert (unsigned Opcode) |

Build but don't insert <empty> = Opcode <empty>. More... | |

| MachineInstrBuilder | insertInstr (MachineInstrBuilder MIB) |

| Insert an existing instruction at the insertion point. More... | |

| MachineInstrBuilder | buildDirectDbgValue (unsigned Reg, const MDNode *Variable, const MDNode *Expr) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in Reg (suitably modified by Expr). More... | |

| MachineInstrBuilder | buildIndirectDbgValue (unsigned Reg, const MDNode *Variable, const MDNode *Expr) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in memory at Reg (suitably modified by Expr). More... | |

| MachineInstrBuilder | buildFIDbgValue (int FI, const MDNode *Variable, const MDNode *Expr) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in the stack slot specified by FI (suitably modified by Expr). More... | |

| MachineInstrBuilder | buildConstDbgValue (const Constant &C, const MDNode *Variable, const MDNode *Expr) |

Build and insert a DBG_VALUE instructions specifying that Variable is given by C (suitably modified by Expr). More... | |

| MachineInstrBuilder | buildDbgLabel (const MDNode *Label) |

Build and insert a DBG_LABEL instructions specifying that Label is given. More... | |

| MachineInstrBuilder | buildFrameIndex (unsigned Res, int Idx) |

Build and insert Res = G_FRAME_INDEX Idx. More... | |

| MachineInstrBuilder | buildGlobalValue (unsigned Res, const GlobalValue *GV) |

Build and insert Res = G_GLOBAL_VALUE GV. More... | |

| MachineInstrBuilder | buildGEP (unsigned Res, unsigned Op0, unsigned Op1) |

Build and insert Res = G_GEP Op0, Op1. More... | |

| Optional< MachineInstrBuilder > | materializeGEP (unsigned &Res, unsigned Op0, const LLT &ValueTy, uint64_t Value) |

Materialize and insert Res = G_GEP Op0, (G_CONSTANT Value) More... | |

| MachineInstrBuilder | buildPtrMask (unsigned Res, unsigned Op0, uint32_t NumBits) |

Build and insert Res = G_PTR_MASK Op0, NumBits. More... | |

| MachineInstrBuilder | buildUAdde (const DstOp &Res, const DstOp &CarryOut, const SrcOp &Op0, const SrcOp &Op1, const SrcOp &CarryIn) |

Build and insert Res, CarryOut = G_UADDE Op0, Op1, CarryIn. More... | |

| MachineInstrBuilder | buildAnyExt (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_ANYEXT Op0. More... | |

| MachineInstrBuilder | buildSExt (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_SEXT Op. More... | |

| MachineInstrBuilder | buildZExt (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_ZEXT Op. More... | |

| MachineInstrBuilder | buildSExtOrTrunc (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_SEXT Op, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op. More... | |

| MachineInstrBuilder | buildZExtOrTrunc (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_ZEXT Op, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op. More... | |

| MachineInstrBuilder | buildAnyExtOrTrunc (const DstOp &Res, const SrcOp &Op) |

Res = COPY Op depending on the differing sizes of Res and Op. More... | |

| MachineInstrBuilder | buildExtOrTrunc (unsigned ExtOpc, const DstOp &Res, const SrcOp &Op) |

Build and insert Res = ExtOpc, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op. More... | |

| MachineInstrBuilder | buildCast (const DstOp &Dst, const SrcOp &Src) |

| Build and insert an appropriate cast between two registers of equal size. More... | |

| MachineInstrBuilder | buildBr (MachineBasicBlock &Dest) |

Build and insert G_BR Dest. More... | |

| MachineInstrBuilder | buildBrCond (unsigned Tst, MachineBasicBlock &Dest) |

Build and insert G_BRCOND Tst, Dest. More... | |

| MachineInstrBuilder | buildBrIndirect (unsigned Tgt) |

Build and insert G_BRINDIRECT Tgt. More... | |

| virtual MachineInstrBuilder | buildConstant (const DstOp &Res, const ConstantInt &Val) |

Build and insert Res = G_CONSTANT Val. More... | |

| MachineInstrBuilder | buildConstant (const DstOp &Res, int64_t Val) |

Build and insert Res = G_CONSTANT Val. More... | |

| virtual MachineInstrBuilder | buildFConstant (const DstOp &Res, const ConstantFP &Val) |

Build and insert Res = G_FCONSTANT Val. More... | |

| MachineInstrBuilder | buildFConstant (const DstOp &Res, double Val) |

| MachineInstrBuilder | buildCopy (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = COPY Op. More... | |

| MachineInstrBuilder | buildLoad (unsigned Res, unsigned Addr, MachineMemOperand &MMO) |

Build and insert Res = G_LOAD Addr, MMO. More... | |

| MachineInstrBuilder | buildLoadInstr (unsigned Opcode, unsigned Res, unsigned Addr, MachineMemOperand &MMO) |

Build and insert Res = <opcode> Addr, MMO. More... | |

| MachineInstrBuilder | buildStore (unsigned Val, unsigned Addr, MachineMemOperand &MMO) |

Build and insert G_STORE Val, Addr, MMO. More... | |

| MachineInstrBuilder | buildExtract (unsigned Res, unsigned Src, uint64_t Index) |

| Build and insert `Res0, ... More... | |

| MachineInstrBuilder | buildUndef (const DstOp &Res) |

Build and insert Res = IMPLICIT_DEF. More... | |

| void | buildSequence (unsigned Res, ArrayRef< unsigned > Ops, ArrayRef< uint64_t > Indices) |

Build and insert instructions to put Ops together at the specified p Indices to form a larger register. More... | |

| MachineInstrBuilder | buildMerge (const DstOp &Res, ArrayRef< unsigned > Ops) |

Build and insert Res = G_MERGE_VALUES Op0, ... More... | |

| MachineInstrBuilder | buildUnmerge (ArrayRef< LLT > Res, const SrcOp &Op) |

Build and insert Res0, ... More... | |

| MachineInstrBuilder | buildUnmerge (ArrayRef< unsigned > Res, const SrcOp &Op) |

| MachineInstrBuilder | buildBuildVector (const DstOp &Res, ArrayRef< unsigned > Ops) |

Build and insert Res = G_BUILD_VECTOR Op0, ... More... | |

| MachineInstrBuilder | buildBuildVectorTrunc (const DstOp &Res, ArrayRef< unsigned > Ops) |

Build and insert Res = G_BUILD_VECTOR_TRUNC Op0, ... More... | |

| MachineInstrBuilder | buildConcatVectors (const DstOp &Res, ArrayRef< unsigned > Ops) |

Build and insert Res = G_CONCAT_VECTORS Op0, ... More... | |

| MachineInstrBuilder | buildInsert (unsigned Res, unsigned Src, unsigned Op, unsigned Index) |

| MachineInstrBuilder | buildIntrinsic (Intrinsic::ID ID, unsigned Res, bool HasSideEffects) |

Build and insert either a G_INTRINSIC (if HasSideEffects is false) or G_INTRINSIC_W_SIDE_EFFECTS instruction. More... | |

| MachineInstrBuilder | buildFPTrunc (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_FPTRUNC Op. More... | |

| MachineInstrBuilder | buildTrunc (const DstOp &Res, const SrcOp &Op) |

Build and insert Res = G_TRUNC Op. More... | |

| MachineInstrBuilder | buildICmp (CmpInst::Predicate Pred, const DstOp &Res, const SrcOp &Op0, const SrcOp &Op1) |

Build and insert a Res = G_ICMP Pred, Op0, Op1. More... | |

| MachineInstrBuilder | buildFCmp (CmpInst::Predicate Pred, const DstOp &Res, const SrcOp &Op0, const SrcOp &Op1) |

Build and insert a Res = G_FCMP Pred Op1. More... | |

| MachineInstrBuilder | buildSelect (const DstOp &Res, const SrcOp &Tst, const SrcOp &Op0, const SrcOp &Op1) |

Build and insert a Res = G_SELECT Tst, Op0, Op1. More... | |

| MachineInstrBuilder | buildInsertVectorElement (const DstOp &Res, const SrcOp &Val, const SrcOp &Elt, const SrcOp &Idx) |

Build and insert Res = G_INSERT_VECTOR_ELT Val, Elt, Idx. More... | |

| MachineInstrBuilder | buildExtractVectorElement (const DstOp &Res, const SrcOp &Val, const SrcOp &Idx) |

Build and insert Res = G_EXTRACT_VECTOR_ELT Val, Idx. More... | |

| MachineInstrBuilder | buildAtomicCmpXchgWithSuccess (unsigned OldValRes, unsigned SuccessRes, unsigned Addr, unsigned CmpVal, unsigned NewVal, MachineMemOperand &MMO) |

Build and insert OldValRes<def>, SuccessRes<def> = G_ATOMIC_CMPXCHG_WITH_SUCCESS Addr, CmpVal, NewVal, MMO. More... | |

| MachineInstrBuilder | buildAtomicCmpXchg (unsigned OldValRes, unsigned Addr, unsigned CmpVal, unsigned NewVal, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMIC_CMPXCHG Addr, CmpVal, NewVal, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMW (unsigned Opcode, unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_<Opcode> Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWXchg (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_XCHG Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWAdd (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_ADD Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWSub (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_SUB Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWAnd (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_AND Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWNand (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_NAND Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWOr (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_OR Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWXor (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_XOR Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWMax (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_MAX Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWMin (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_MIN Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWUmax (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_UMAX Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildAtomicRMWUmin (unsigned OldValRes, unsigned Addr, unsigned Val, MachineMemOperand &MMO) |

Build and insert OldValRes<def> = G_ATOMICRMW_UMIN Addr, Val, MMO. More... | |

| MachineInstrBuilder | buildBlockAddress (unsigned Res, const BlockAddress *BA) |

Build and insert Res = G_BLOCK_ADDR BA. More... | |

| MachineInstrBuilder | buildAdd (const DstOp &Dst, const SrcOp &Src0, const SrcOp &Src1, Optional< unsigned > Flags=None) |

Build and insert Res = G_ADD Op0, Op1. More... | |

| MachineInstrBuilder | buildSub (const DstOp &Dst, const SrcOp &Src0, const SrcOp &Src1, Optional< unsigned > Flags=None) |

Build and insert Res = G_SUB Op0, Op1. More... | |

| MachineInstrBuilder | buildMul (const DstOp &Dst, const SrcOp &Src0, const SrcOp &Src1, Optional< unsigned > Flags=None) |

Build and insert Res = G_MUL Op0, Op1. More... | |

| MachineInstrBuilder | buildAnd (const DstOp &Dst, const SrcOp &Src0, const SrcOp &Src1) |

Build and insert Res = G_AND Op0, Op1. More... | |

| MachineInstrBuilder | buildOr (const DstOp &Dst, const SrcOp &Src0, const SrcOp &Src1) |

Build and insert Res = G_OR Op0, Op1. More... | |

| virtual MachineInstrBuilder | buildInstr (unsigned Opc, ArrayRef< DstOp > DstOps, ArrayRef< SrcOp > SrcOps, Optional< unsigned > Flags=None) |

Setters for the insertion point. | |

Set the MachineFunction where to build instructions. | |

| void | setMF (MachineFunction &MF) |

| void | setMBB (MachineBasicBlock &MBB) |

Set the insertion point to the end of MBB. More... | |

| void | setInstr (MachineInstr &MI) |

| Set the insertion point to before MI. More... | |

Protected Member Functions | |

| void | validateTruncExt (const LLT &Dst, const LLT &Src, bool IsExtend) |

| void | validateBinaryOp (const LLT &Res, const LLT &Op0, const LLT &Op1) |

| void | validateSelectOp (const LLT &ResTy, const LLT &TstTy, const LLT &Op0Ty, const LLT &Op1Ty) |

| void | recordInsertion (MachineInstr *MI) const |

Detailed Description

Helper class to build MachineInstr.

It keeps internally the insertion point and debug location for all the new instructions we want to create. This information can be modify via the related setters.

Definition at line 197 of file MachineIRBuilder.h.

Constructor & Destructor Documentation

◆ MachineIRBuilder() [1/4]

|

default |

Some constructors for easy use.

◆ MachineIRBuilder() [2/4]

|

inline |

Definition at line 213 of file MachineIRBuilder.h.

◆ MachineIRBuilder() [3/4]

|

inline |

Definition at line 214 of file MachineIRBuilder.h.

◆ ~MachineIRBuilder()

|

virtualdefault |

◆ MachineIRBuilder() [4/4]

|

inline |

Definition at line 220 of file MachineIRBuilder.h.

Member Function Documentation

◆ buildAdd()

|

inline |

Build and insert Res = G_ADD Op0, Op1.

G_ADD sets Res to the sum of integer parameters Op0 and Op1, truncated to their width.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same (scalar or vector) type).

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 1088 of file MachineIRBuilder.h.

Referenced by llvm::LegalizerHelper::fewerElementsVector(), and llvm::LegalizerHelper::lower().

◆ buildAnd()

|

inline |

Build and insert Res = G_AND Op0, Op1.

G_AND sets Res to the bitwise and of integer parameters Op0 and Op1.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same (scalar or vector) type).

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 1138 of file MachineIRBuilder.h.

Referenced by llvm::LegalizationArtifactCombiner::tryCombineZExt().

◆ buildAnyExt()

| MachineInstrBuilder MachineIRBuilder::buildAnyExt | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_ANYEXT Op0.

G_ANYEXT produces a register of the specified width, with bits 0 to sizeof(Ty) * 8 set to Op. The remaining bits are unspecified (i.e. this is neither zero nor sign-extension). For a vector register, each element is extended individually.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type. -

Opmust be smaller thanRes

- Returns

- The newly created instruction.

Definition at line 332 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), llvm::CallLowering::ValueHandler::extendRegister(), llvm::LegalizerHelper::lower(), and llvm::X86CallLowering::X86CallLowering().

◆ buildAnyExtOrTrunc()

| MachineInstrBuilder MachineIRBuilder::buildAnyExtOrTrunc | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Res = COPY Op depending on the differing sizes of Res and Op.

///

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type.

- Returns

- The newly created instruction.

Definition at line 381 of file MachineIRBuilder.cpp.

References buildExtOrTrunc().

Referenced by llvm::LegalizationArtifactCombiner::tryCombineAnyExt(), llvm::LegalizationArtifactCombiner::tryCombineSExt(), and llvm::LegalizationArtifactCombiner::tryCombineZExt().

◆ buildAtomicCmpXchg()

| MachineInstrBuilder MachineIRBuilder::buildAtomicCmpXchg | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | CmpVal, | ||

| unsigned | NewVal, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMIC_CMPXCHG Addr, CmpVal, NewVal, MMO.

Atomically replace the value at Addr with NewVal if it is currently CmpVal otherwise leaves it unchanged. Puts the original value from Addr in Res.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register of scalar type. -

Addrmust be a generic virtual register with pointer type. -

OldValRes,CmpVal, andNewValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 631 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), llvm::MachineRegisterInfo::getType(), llvm::LLT::isPointer(), llvm::LLT::isScalar(), and llvm::LLT::isValid().

Referenced by llvm::LegalizerHelper::lower().

◆ buildAtomicCmpXchgWithSuccess()

| MachineInstrBuilder MachineIRBuilder::buildAtomicCmpXchgWithSuccess | ( | unsigned | OldValRes, |

| unsigned | SuccessRes, | ||

| unsigned | Addr, | ||

| unsigned | CmpVal, | ||

| unsigned | NewVal, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def>, SuccessRes<def> = G_ATOMIC_CMPXCHG_WITH_SUCCESS Addr, CmpVal, NewVal, MMO.

Atomically replace the value at Addr with NewVal if it is currently CmpVal otherwise leaves it unchanged. Puts the original value from Addr in Res, along with an s1 indicating whether it was replaced.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register of scalar type. -

SuccessResmust be a generic virtual register of scalar type. It will be assigned 0 on failure and 1 on success. -

Addrmust be a generic virtual register with pointer type. -

OldValRes,CmpVal, andNewValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 603 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), llvm::MachineRegisterInfo::getType(), llvm::LLT::isPointer(), llvm::LLT::isScalar(), and llvm::LLT::isValid().

Referenced by getOffsetFromIndices().

◆ buildAtomicRMW()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMW | ( | unsigned | Opcode, |

| unsigned | OldValRes, | ||

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_<Opcode> Addr, Val, MMO.

Atomically read-modify-update the value at Addr with Val. Puts the original value from Addr in OldValRes. The modification is determined by the opcode.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 655 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), llvm::MachineRegisterInfo::getType(), llvm::LLT::isPointer(), llvm::LLT::isScalar(), and llvm::LLT::isValid().

Referenced by buildAtomicRMWAdd(), buildAtomicRMWAnd(), buildAtomicRMWMax(), buildAtomicRMWMin(), buildAtomicRMWNand(), buildAtomicRMWOr(), buildAtomicRMWSub(), buildAtomicRMWUmax(), buildAtomicRMWUmin(), buildAtomicRMWXchg(), buildAtomicRMWXor(), and getOffsetFromIndices().

◆ buildAtomicRMWAdd()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWAdd | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_ADD Addr, Val, MMO.

Atomically replace the value at Addr with the addition of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 684 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWAnd()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWAnd | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_AND Addr, Val, MMO.

Atomically replace the value at Addr with the bitwise and of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 696 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWMax()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWMax | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_MAX Addr, Val, MMO.

Atomically replace the value at Addr with the signed maximum of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 721 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWMin()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWMin | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_MIN Addr, Val, MMO.

Atomically replace the value at Addr with the signed minimum of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 727 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWNand()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWNand | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_NAND Addr, Val, MMO.

Atomically replace the value at Addr with the bitwise nand of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 702 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWOr()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWOr | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_OR Addr, Val, MMO.

Atomically replace the value at Addr with the bitwise or of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 707 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWSub()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWSub | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_SUB Addr, Val, MMO.

Atomically replace the value at Addr with the subtraction of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 690 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWUmax()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWUmax | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_UMAX Addr, Val, MMO.

Atomically replace the value at Addr with the unsigned maximum of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 733 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWUmin()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWUmin | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_UMIN Addr, Val, MMO.

Atomically replace the value at Addr with the unsigned minimum of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 739 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWXchg()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWXchg | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_XCHG Addr, Val, MMO.

Atomically replace the value at Addr with Val. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 678 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildAtomicRMWXor()

| MachineInstrBuilder MachineIRBuilder::buildAtomicRMWXor | ( | unsigned | OldValRes, |

| unsigned | Addr, | ||

| unsigned | Val, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert OldValRes<def> = G_ATOMICRMW_XOR Addr, Val, MMO.

Atomically replace the value at Addr with the bitwise xor of Val and the original value. Puts the original value from Addr in OldValRes.

- Precondition

- setBasicBlock or setMI must have been called.

-

OldValResmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type. -

OldValRes, andValmust be generic virtual registers of the same type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 715 of file MachineIRBuilder.cpp.

References buildAtomicRMW().

◆ buildBlockAddress()

| MachineInstrBuilder MachineIRBuilder::buildBlockAddress | ( | unsigned | Res, |

| const BlockAddress * | BA | ||

| ) |

Build and insert Res = G_BLOCK_ADDR BA.

G_BLOCK_ADDR computes the address of a basic block.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register of a pointer type.

- Returns

- The newly created instruction.

Definition at line 746 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addBlockAddress(), llvm::MachineInstrBuilder::addDef(), assert(), buildInstr(), getMRI(), and getType().

◆ buildBr()

| MachineInstrBuilder MachineIRBuilder::buildBr | ( | MachineBasicBlock & | Dest | ) |

Build and insert G_BR Dest.

G_BR is an unconditional branch to Dest.

- Precondition

- setBasicBlock or setMI must have been called.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 229 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addMBB(), and buildInstr().

Referenced by computeValueLLTs(), and getOffsetFromIndices().

◆ buildBrCond()

| MachineInstrBuilder MachineIRBuilder::buildBrCond | ( | unsigned | Tst, |

| MachineBasicBlock & | Dest | ||

| ) |

Build and insert G_BRCOND Tst, Dest.

G_BRCOND is a conditional branch to Dest.

- Precondition

- setBasicBlock or setMI must have been called.

-

Tstmust be a generic virtual register with scalar type. At the beginning of legalization, this will be a single bit (s1). Targets with interesting flags registers may change this. For a wider type, whether the branch is taken must only depend on bit 0 (for now).

- Returns

- The newly created instruction.

Definition at line 287 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), getType(), and llvm::LegalityPredicates::isScalar().

Referenced by computeValueLLTs().

◆ buildBrIndirect()

| MachineInstrBuilder MachineIRBuilder::buildBrIndirect | ( | unsigned | Tgt | ) |

Build and insert G_BRINDIRECT Tgt.

G_BRINDIRECT is an indirect branch to Tgt.

- Precondition

- setBasicBlock or setMI must have been called.

-

Tgtmust be a generic virtual register with pointer type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 233 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), and getType().

Referenced by computeValueLLTs().

◆ buildBuildVector()

| MachineInstrBuilder MachineIRBuilder::buildBuildVector | ( | const DstOp & | Res, |

| ArrayRef< unsigned > | Ops | ||

| ) |

Build and insert Res = G_BUILD_VECTOR Op0, ...

G_BUILD_VECTOR creates a vector value from multiple scalar registers.

- Precondition

- setBasicBlock or setMI must have been called.

-

The entire register

Res(and no more) must be covered by the input scalar registers. -

The type of all

Opsregisters must be identical.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 500 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

Referenced by llvm::LegalizerHelper::fewerElementsVector(), and llvm::LegalizerHelper::narrowScalar().

◆ buildBuildVectorTrunc()

| MachineInstrBuilder MachineIRBuilder::buildBuildVectorTrunc | ( | const DstOp & | Res, |

| ArrayRef< unsigned > | Ops | ||

| ) |

Build and insert Res = G_BUILD_VECTOR_TRUNC Op0, ...

G_BUILD_VECTOR_TRUNC creates a vector value from multiple scalar registers which have types larger than the destination vector element type, and truncates the values to fit.

If the operands given are already the same size as the vector elt type, then this method will instead create a G_BUILD_VECTOR instruction.

- Precondition

- setBasicBlock or setMI must have been called.

-

The type of all

Opsregisters must be identical.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 510 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

◆ buildCast()

| MachineInstrBuilder MachineIRBuilder::buildCast | ( | const DstOp & | Dst, |

| const SrcOp & | Src | ||

| ) |

Build and insert an appropriate cast between two registers of equal size.

Definition at line 386 of file MachineIRBuilder.cpp.

References assert(), buildCopy(), buildInstr(), llvm::DstOp::getLLTTy(), llvm::SrcOp::getLLTTy(), getMRI(), llvm::LLT::isPointer(), and llvm::LLT::isScalar().

Referenced by buildExtract(), buildInsert(), buildInstr(), and getOffsetFromIndices().

◆ buildConcatVectors()

| MachineInstrBuilder MachineIRBuilder::buildConcatVectors | ( | const DstOp & | Res, |

| ArrayRef< unsigned > | Ops | ||

| ) |

Build and insert Res = G_CONCAT_VECTORS Op0, ...

G_CONCAT_VECTORS creates a vector from the concatenation of 2 or more vectors.

- Precondition

- setBasicBlock or setMI must have been called.

-

The entire register

Res(and no more) must be covered by the input registers. - The type of all source operands must be identical.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 520 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

Referenced by llvm::LegalizerHelper::fewerElementsVector().

◆ buildConstant() [1/2]

|

virtual |

Build and insert Res = G_CONSTANT Val.

G_CONSTANT is an integer constant with the specified size and value. Val will be extended or truncated to the size of Reg.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or pointer type.

- Returns

- The newly created instruction.

Reimplemented in llvm::CSEMIRBuilder.

Definition at line 243 of file MachineIRBuilder.cpp.

References llvm::DstOp::addDefToMIB(), assert(), buildInstr(), llvm::ConstantInt::get(), llvm::ConstantInt::getBitWidth(), llvm::Function::getContext(), llvm::MachineFunction::getFunction(), llvm::DstOp::getLLTTy(), getMF(), getMRI(), llvm::LLT::getSizeInBits(), llvm::ConstantInt::getValue(), llvm::LLT::isPointer(), llvm::LLT::isScalar(), and llvm::APInt::sextOrTrunc().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), llvm::CSEMIRBuilder::buildConstant(), buildConstant(), llvm::ConstantFoldingMIRBuilder::buildInstr(), llvm::LegalizerHelper::fewerElementsVector(), getOffsetFromIndices(), isSupportedType(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::lower(), llvm::AMDGPUCallLowering::lowerReturn(), materializeGEP(), llvm::LegalizerHelper::narrowScalar(), llvm::LegalizationArtifactCombiner::tryCombineSExt(), llvm::LegalizationArtifactCombiner::tryCombineZExt(), llvm::LegalizationArtifactCombiner::tryFoldImplicitDef(), llvm::LegalizerHelper::widenScalar(), and llvm::X86CallLowering::X86CallLowering().

◆ buildConstant() [2/2]

| MachineInstrBuilder MachineIRBuilder::buildConstant | ( | const DstOp & | Res, |

| int64_t | Val | ||

| ) |

Build and insert Res = G_CONSTANT Val.

G_CONSTANT is an integer constant with the specified size and value.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar type.

- Returns

- The newly created instruction.

Definition at line 260 of file MachineIRBuilder.cpp.

References buildConstant(), llvm::IntegerType::get(), llvm::ConstantInt::get(), getFunction(), llvm::DstOp::getLLTTy(), getMF(), getMRI(), and llvm::LLT::getSizeInBits().

◆ buildConstDbgValue()

| MachineInstrBuilder MachineIRBuilder::buildConstDbgValue | ( | const Constant & | C, |

| const MDNode * | Variable, | ||

| const MDNode * | Expr | ||

| ) |

Build and insert a DBG_VALUE instructions specifying that Variable is given by C (suitably modified by Expr).

Definition at line 130 of file MachineIRBuilder.cpp.

References assert(), buildInstr(), and getDL().

Referenced by getOffsetFromIndices().

◆ buildCopy()

| MachineInstrBuilder MachineIRBuilder::buildCopy | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = COPY Op.

Register-to-register COPY sets Res to Op.

- Precondition

- setBasicBlock or setMI must have been called.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 238 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), buildCast(), computeValueLLTs(), getOffsetFromIndices(), isSupportedType(), llvm::AMDGPUCallLowering::lowerFormalArguments(), llvm::AArch64CallLowering::lowerFormalArguments(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), llvm::CombinerHelper::replaceRegWith(), and llvm::X86CallLowering::X86CallLowering().

◆ buildDbgLabel()

| MachineInstrBuilder MachineIRBuilder::buildDbgLabel | ( | const MDNode * | Label | ) |

Build and insert a DBG_LABEL instructions specifying that Label is given.

Convert "llvm.dbg.label Label" to "DBG_LABEL Label".

Definition at line 154 of file MachineIRBuilder.cpp.

References assert(), buildInstr(), and llvm::MachineIRBuilderState::DL.

Referenced by getOffsetFromIndices().

◆ buildDirectDbgValue()

| MachineInstrBuilder MachineIRBuilder::buildDirectDbgValue | ( | unsigned | Reg, |

| const MDNode * | Variable, | ||

| const MDNode * | Expr | ||

| ) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in Reg (suitably modified by Expr).

Definition at line 90 of file MachineIRBuilder.cpp.

References assert(), llvm::BuildMI(), getDL(), getMF(), getTII(), and insertInstr().

Referenced by getOffsetFromIndices().

◆ buildExtOrTrunc()

| MachineInstrBuilder MachineIRBuilder::buildExtOrTrunc | ( | unsigned | ExtOpc, |

| const DstOp & | Res, | ||

| const SrcOp & | Op | ||

| ) |

Build and insert Res = ExtOpc, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op.

///

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type.

- Returns

- The newly created instruction.

Definition at line 347 of file MachineIRBuilder.cpp.

References assert(), buildInstr(), llvm::DstOp::getLLTTy(), llvm::SrcOp::getLLTTy(), getMRI(), llvm::LLT::getSizeInBits(), llvm::LLT::isScalar(), and llvm::LLT::isVector().

Referenced by buildAnyExtOrTrunc(), buildSExtOrTrunc(), and buildZExtOrTrunc().

◆ buildExtract()

| MachineInstrBuilder MachineIRBuilder::buildExtract | ( | unsigned | Res, |

| unsigned | Src, | ||

| uint64_t | Index | ||

| ) |

Build and insert `Res0, ...

= G_EXTRACT Src, Idx0`.

- Precondition

- setBasicBlock or setMI must have been called.

-

ResandSrcmust be generic virtual registers.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 406 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addUse(), assert(), buildCast(), buildInstr(), getMRI(), llvm::getSizeInBits(), and getType().

Referenced by getOffsetFromIndices(), llvm::AArch64CallLowering::lowerCall(), llvm::AArch64CallLowering::lowerReturn(), and llvm::LegalizerHelper::narrowScalar().

◆ buildExtractVectorElement()

| MachineInstrBuilder MachineIRBuilder::buildExtractVectorElement | ( | const DstOp & | Res, |

| const SrcOp & | Val, | ||

| const SrcOp & | Idx | ||

| ) |

Build and insert Res = G_EXTRACT_VECTOR_ELT Val, Idx.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar type. -

Valmust be a generic virtual register with vector type. -

Idxmust be a generic virtual register with scalar type.

- Returns

- The newly created instruction.

Definition at line 598 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by getOffsetFromIndices().

◆ buildFCmp()

| MachineInstrBuilder MachineIRBuilder::buildFCmp | ( | CmpInst::Predicate | Pred, |

| const DstOp & | Res, | ||

| const SrcOp & | Op0, | ||

| const SrcOp & | Op1 | ||

| ) |

Build and insert a Res = G_FCMP Pred Op0,Op1.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. Typically this starts as s1 or <N x="" s1>="">. -

Op0and Op1 must be generic virtual registers with the same number of elements asRes(or scalar, ifResis scalar). -

Predmust be a floating-point predicate.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 575 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by computeValueLLTs().

◆ buildFConstant() [1/2]

|

virtual |

Build and insert Res = G_FCONSTANT Val.

G_FCONSTANT is a floating-point constant with the specified size and value.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar type.

- Returns

- The newly created instruction.

Reimplemented in llvm::CSEMIRBuilder.

Definition at line 268 of file MachineIRBuilder.cpp.

References llvm::DstOp::addDefToMIB(), assert(), buildInstr(), llvm::DstOp::getLLTTy(), getMRI(), and llvm::LLT::isScalar().

Referenced by llvm::CSEMIRBuilder::buildFConstant(), buildFConstant(), and llvm::LegalizerHelper::lower().

◆ buildFConstant() [2/2]

| MachineInstrBuilder MachineIRBuilder::buildFConstant | ( | const DstOp & | Res, |

| double | Val | ||

| ) |

Definition at line 278 of file MachineIRBuilder.cpp.

References buildFConstant(), llvm::ConstantFP::get(), llvm::getAPFloatFromSize(), llvm::Function::getContext(), llvm::MachineFunction::getFunction(), llvm::DstOp::getLLTTy(), getMF(), getMRI(), and llvm::LLT::getSizeInBits().

◆ buildFIDbgValue()

| MachineInstrBuilder MachineIRBuilder::buildFIDbgValue | ( | int | FI, |

| const MDNode * | Variable, | ||

| const MDNode * | Expr | ||

| ) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in the stack slot specified by FI (suitably modified by Expr).

Definition at line 115 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMetadata(), assert(), buildInstr(), and getDL().

◆ buildFPTrunc()

| MachineInstrBuilder MachineIRBuilder::buildFPTrunc | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_FPTRUNC Op.

G_FPTRUNC converts a floating-point value into one with a smaller type.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type. -

Resmust be smaller thanOp

- Returns

- The newly created instruction.

Definition at line 563 of file MachineIRBuilder.cpp.

References buildInstr().

◆ buildFrameIndex()

| MachineInstrBuilder MachineIRBuilder::buildFrameIndex | ( | unsigned | Res, |

| int | Idx | ||

| ) |

Build and insert Res = G_FRAME_INDEX Idx.

G_FRAME_INDEX materializes the address of an alloca value or other stack-based object.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with pointer type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 163 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addFrameIndex(), assert(), buildInstr(), getMRI(), and getType().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), getOffsetFromIndices(), llvm::X86CallLowering::lowerReturn(), and llvm::ARMCallLowering::lowerReturn().

◆ buildGEP()

| MachineInstrBuilder MachineIRBuilder::buildGEP | ( | unsigned | Res, |

| unsigned | Op0, | ||

| unsigned | Op1 | ||

| ) |

Build and insert Res = G_GEP Op0, Op1.

G_GEP adds Op1 bytes to the pointer specified by Op0, storing the resulting pointer in Res.

- Precondition

- setBasicBlock or setMI must have been called.

-

ResandOp0must be generic virtual registers with pointer type. -

Op1must be a generic virtual register with scalar type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 188 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), getType(), and llvm::LegalityPredicates::isScalar().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), getOffsetFromIndices(), isSupportedType(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::AMDGPUCallLowering::lowerReturn(), materializeGEP(), and llvm::X86CallLowering::X86CallLowering().

◆ buildGlobalValue()

| MachineInstrBuilder MachineIRBuilder::buildGlobalValue | ( | unsigned | Res, |

| const GlobalValue * | GV | ||

| ) |

Build and insert Res = G_GLOBAL_VALUE GV.

G_GLOBAL_VALUE materializes the address of the specified global into Res.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with pointer type in the same address space asGV.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 170 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addGlobalAddress(), assert(), buildInstr(), llvm::PointerType::getAddressSpace(), getMRI(), getType(), and llvm::GlobalValue::getType().

◆ buildICmp()

| MachineInstrBuilder MachineIRBuilder::buildICmp | ( | CmpInst::Predicate | Pred, |

| const DstOp & | Res, | ||

| const SrcOp & | Op0, | ||

| const SrcOp & | Op1 | ||

| ) |

Build and insert a Res = G_ICMP Pred, Op0, Op1.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. Typically this starts as s1 or <N x="" s1>="">. -

Op0and Op1 must be generic virtual registers with the same number of elements asRes. IfResis a scalar,Op0must be either a scalar or pointer. -

Predmust be an integer predicate.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 568 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by computeValueLLTs(), llvm::LegalizerHelper::fewerElementsVector(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::lower(), and llvm::LegalizerHelper::widenScalar().

◆ buildIndirectDbgValue()

| MachineInstrBuilder MachineIRBuilder::buildIndirectDbgValue | ( | unsigned | Reg, |

| const MDNode * | Variable, | ||

| const MDNode * | Expr | ||

| ) |

Build and insert a DBG_VALUE instruction expressing the fact that the associated Variable lives in memory at Reg (suitably modified by Expr).

Definition at line 103 of file MachineIRBuilder.cpp.

References assert(), llvm::BuildMI(), getDL(), getMF(), getTII(), and insertInstr().

Referenced by getOffsetFromIndices().

◆ buildInsert()

| MachineInstrBuilder MachineIRBuilder::buildInsert | ( | unsigned | Res, |

| unsigned | Src, | ||

| unsigned | Op, | ||

| unsigned | Index | ||

| ) |

Definition at line 528 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addUse(), assert(), buildCast(), buildInstr(), getMRI(), llvm::getSizeInBits(), and getType().

Referenced by buildSequence(), getOffsetFromIndices(), llvm::AArch64CallLowering::lowerFormalArguments(), and llvm::LegalizerHelper::narrowScalar().

◆ buildInsertVectorElement()

| MachineInstrBuilder MachineIRBuilder::buildInsertVectorElement | ( | const DstOp & | Res, |

| const SrcOp & | Val, | ||

| const SrcOp & | Elt, | ||

| const SrcOp & | Idx | ||

| ) |

Build and insert Res = G_INSERT_VECTOR_ELT Val, Elt, Idx.

- Precondition

- setBasicBlock or setMI must have been called.

-

ResandValmust be a generic virtual register -

EltandIdxmust be a generic virtual register with scalar type.

- Returns

- The newly created instruction.

Definition at line 592 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by getOffsetFromIndices().

◆ buildInstr() [1/2]

| MachineInstrBuilder MachineIRBuilder::buildInstr | ( | unsigned | Opcode | ) |

Build and insert <empty> = Opcode <empty>.

The insertion point is the one set by the last call of either setBasicBlock or setMI.

- Precondition

- setBasicBlock or setMI must have been called.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 74 of file MachineIRBuilder.cpp.

References buildInstrNoInsert(), and insertInstr().

Referenced by buildAnyExt(), buildAtomicCmpXchg(), buildAtomicCmpXchgWithSuccess(), buildAtomicRMW(), buildBlockAddress(), buildBr(), buildBrCond(), buildBrIndirect(), buildBuildVector(), buildBuildVectorTrunc(), buildCast(), buildConcatVectors(), buildConstant(), buildConstDbgValue(), buildCopy(), buildDbgLabel(), buildExtOrTrunc(), buildExtract(), buildExtractVectorElement(), buildFCmp(), buildFConstant(), buildFIDbgValue(), buildFPTrunc(), buildFrameIndex(), buildGEP(), buildGlobalValue(), buildICmp(), buildInsert(), buildInsertVectorElement(), llvm::ConstantFoldingMIRBuilder::buildInstr(), llvm::CSEMIRBuilder::buildInstr(), buildInstr(), buildIntrinsic(), buildLoadInstr(), buildMerge(), buildPtrMask(), buildSelect(), buildSExt(), buildStore(), buildTrunc(), buildUAdde(), buildUndef(), buildUnmerge(), buildZExt(), changeFCMPPredToAArch64CC(), computeValueLLTs(), llvm::LegalizerHelper::fewerElementsVector(), getOffsetFromIndices(), llvm::LegalizerHelper::lower(), llvm::X86CallLowering::lowerCall(), llvm::ARMCallLowering::lowerCall(), llvm::AArch64CallLowering::lowerCall(), llvm::MipsCallLowering::lowerCall(), llvm::AMDGPUCallLowering::lowerReturn(), llvm::LegalizerHelper::narrowScalar(), llvm::LegalizationArtifactCombiner::tryCombineAnyExt(), llvm::LegalizationArtifactCombiner::tryCombineSExt(), llvm::LegalizationArtifactCombiner::tryFoldImplicitDef(), and llvm::LegalizerHelper::widenScalar().

◆ buildInstr() [2/2]

|

virtual |

Reimplemented in llvm::CSEMIRBuilder, and llvm::ConstantFoldingMIRBuilder.

Definition at line 789 of file MachineIRBuilder.cpp.

References llvm::all_of(), assert(), llvm::ArrayRef< T >::begin(), buildCast(), buildInstr(), llvm::ArrayRef< T >::empty(), llvm::ArrayRef< T >::end(), getMRI(), llvm::LLT::getNumElements(), llvm::getSizeInBits(), llvm::CmpInst::isFPPredicate(), llvm::CmpInst::isIntPredicate(), llvm::LLT::isPointer(), llvm::LLT::isScalar(), llvm::LegalityPredicates::isScalar(), llvm::LLT::isVector(), llvm::HexagonMCInstrInfo::isVector(), llvm::ArrayRef< T >::size(), llvm::SrcOp::Ty_Predicate, validateBinaryOp(), validateSelectOp(), and validateTruncExt().

◆ buildInstrNoInsert()

| MachineInstrBuilder MachineIRBuilder::buildInstrNoInsert | ( | unsigned | Opcode | ) |

Build but don't insert <empty> = Opcode <empty>.

- Precondition

- setMF, setBasicBlock or setMI must have been called.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 78 of file MachineIRBuilder.cpp.

References llvm::BuildMI(), getDL(), getMF(), and getTII().

Referenced by buildInstr(), llvm::RegBankSelect::getAnalysisUsage(), llvm::X86CallLowering::lowerCall(), llvm::ARMCallLowering::lowerCall(), llvm::AArch64CallLowering::lowerCall(), llvm::MipsCallLowering::lowerCall(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), llvm::AArch64CallLowering::lowerReturn(), and llvm::MipsCallLowering::lowerReturn().

◆ buildIntrinsic()

| MachineInstrBuilder MachineIRBuilder::buildIntrinsic | ( | Intrinsic::ID | ID, |

| unsigned | Res, | ||

| bool | HasSideEffects | ||

| ) |

Build and insert either a G_INTRINSIC (if HasSideEffects is false) or G_INTRINSIC_W_SIDE_EFFECTS instruction.

Its first operand will be the result register definition unless Reg is NoReg (== 0). The second operand will be the intrinsic's ID.

Callers are expected to add the required definitions and uses afterwards.

- Precondition

- setBasicBlock or setMI must have been called.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 546 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by getOffsetFromIndices().

◆ buildLoad()

| MachineInstrBuilder MachineIRBuilder::buildLoad | ( | unsigned | Res, |

| unsigned | Addr, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert Res = G_LOAD Addr, MMO.

Loads the value stored at Addr. Puts the result in Res.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 294 of file MachineIRBuilder.cpp.

References buildLoadInstr().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), computeValueLLTs(), llvm::LegalizerHelper::fewerElementsVector(), llvm::MipsCallLowering::MipsHandler::handle(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::lower(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), llvm::AMDGPUCallLowering::lowerReturn(), and llvm::LegalizerHelper::narrowScalar().

◆ buildLoadInstr()

| MachineInstrBuilder MachineIRBuilder::buildLoadInstr | ( | unsigned | Opcode, |

| unsigned | Res, | ||

| unsigned | Addr, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert Res = <opcode> Addr, MMO.

Loads the value stored at Addr. Puts the result in Res.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 299 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), and getType().

Referenced by buildLoad().

◆ buildMerge()

| MachineInstrBuilder MachineIRBuilder::buildMerge | ( | const DstOp & | Res, |

| ArrayRef< unsigned > | Ops | ||

| ) |

Build and insert Res = G_MERGE_VALUES Op0, ...

G_MERGE_VALUES combines the input elements contiguously into a larger register.

- Precondition

- setBasicBlock or setMI must have been called.

-

The entire register

Res(and no more) must be covered by the input registers. -

The type of all

Opsregisters must be identical.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 473 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

Referenced by buildSequence(), llvm::X86CallLowering::lowerCall(), llvm::ARMCallLowering::lowerCall(), llvm::X86CallLowering::lowerFormalArguments(), llvm::ARMCallLowering::lowerFormalArguments(), llvm::ARMCallLowering::lowerReturn(), llvm::LegalizerHelper::narrowScalar(), and llvm::LegalizationArtifactCombiner::tryCombineMerges().

◆ buildMul()

|

inline |

Build and insert Res = G_MUL Op0, Op1.

G_MUL sets Res to the sum of integer parameters Op0 and Op1, truncated to their width.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same (scalar or vector) type).

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 1121 of file MachineIRBuilder.h.

Referenced by getOffsetFromIndices(), and llvm::LegalizerHelper::lower().

◆ buildOr()

|

inline |

Build and insert Res = G_OR Op0, Op1.

G_OR sets Res to the bitwise or of integer parameters Op0 and Op1.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same (scalar or vector) type).

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 1153 of file MachineIRBuilder.h.

References llvm::None.

Referenced by llvm::ARMLegalizerInfo::legalizeCustom().

◆ buildPtrMask()

| MachineInstrBuilder MachineIRBuilder::buildPtrMask | ( | unsigned | Res, |

| unsigned | Op0, | ||

| uint32_t | NumBits | ||

| ) |

Build and insert Res = G_PTR_MASK Op0, NumBits.

G_PTR_MASK clears the low bits of a pointer operand without destroying its pointer properties. This has the effect of rounding the address down to a specified alignment in bits.

- Precondition

- setBasicBlock or setMI must have been called.

-

ResandOp0must be generic virtual registers with pointer type. -

NumBitsmust be an integer representing the number of low bits to be cleared inOp0.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 218 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), and getType().

Referenced by getOffsetFromIndices(), and llvm::AArch64LegalizerInfo::legalizeCustom().

◆ buildSelect()

| MachineInstrBuilder MachineIRBuilder::buildSelect | ( | const DstOp & | Res, |

| const SrcOp & | Tst, | ||

| const SrcOp & | Op0, | ||

| const SrcOp & | Op1 | ||

| ) |

Build and insert a Res = G_SELECT Tst, Op0, Op1.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same type. -

Tstmust be a generic virtual register with scalar, pointer or vector type. If vector then it must have the same number of elements as the other parameters.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 583 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::LegalizerHelper::fewerElementsVector(), and getOffsetFromIndices().

◆ buildSequence()

| void MachineIRBuilder::buildSequence | ( | unsigned | Res, |

| ArrayRef< unsigned > | Ops, | ||

| ArrayRef< uint64_t > | Indices | ||

| ) |

Build and insert instructions to put Ops together at the specified p Indices to form a larger register.

If the types of the input registers are uniform and cover the entirity of Res then a G_MERGE_VALUES will be produced. Otherwise an IMPLICIT_DEF followed by a sequence of G_INSERT instructions.

- Precondition

- setBasicBlock or setMI must have been called.

- The final element of the sequence must not extend past the end of the destination register.

- The bits defined by each Op (derived from index and scalar size) must not overlap.

-

Indicesmust be in ascending order of bit position.

Definition at line 428 of file MachineIRBuilder.cpp.

References assert(), llvm::ArrayRef< T >::begin(), buildInsert(), buildMerge(), buildUndef(), llvm::MachineRegisterInfo::createGenericVirtualRegister(), llvm::ArrayRef< T >::empty(), llvm::ArrayRef< T >::end(), getMRI(), llvm::LLT::getSizeInBits(), getType(), llvm::MachineRegisterInfo::getType(), and llvm::ArrayRef< T >::size().

Referenced by llvm::AArch64CallLowering::lowerCall().

◆ buildSExt()

| MachineInstrBuilder MachineIRBuilder::buildSExt | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_SEXT Op.

G_SEXT produces a register of the specified width, with bits 0 to sizeof(Ty) * 8 set to Op. The remaining bits are duplicated from the high bit of Op (i.e. 2s-complement sign extended).

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type. -

Opmust be smaller thanRes

- Returns

- The newly created instruction.

Definition at line 337 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::CallLowering::ValueHandler::extendRegister(), and llvm::LegalizerHelper::lower().

◆ buildSExtOrTrunc()

| MachineInstrBuilder MachineIRBuilder::buildSExtOrTrunc | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_SEXT Op, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op.

///

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type.

- Returns

- The newly created instruction.

Definition at line 371 of file MachineIRBuilder.cpp.

References buildExtOrTrunc().

Referenced by getOffsetFromIndices().

◆ buildStore()

| MachineInstrBuilder MachineIRBuilder::buildStore | ( | unsigned | Val, |

| unsigned | Addr, | ||

| MachineMemOperand & | MMO | ||

| ) |

Build and insert G_STORE Val, Addr, MMO.

Stores the value Val to Addr.

- Precondition

- setBasicBlock or setMI must have been called.

-

Valmust be a generic virtual register. -

Addrmust be a generic virtual register with pointer type.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 312 of file MachineIRBuilder.cpp.

References llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addUse(), assert(), buildInstr(), getMRI(), and getType().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), computeValueLLTs(), llvm::LegalizerHelper::fewerElementsVector(), getOffsetFromIndices(), isSupportedType(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::narrowScalar(), and llvm::X86CallLowering::X86CallLowering().

◆ buildSub()

|

inline |

Build and insert Res = G_SUB Op0, Op1.

G_SUB sets Res to the sum of integer parameters Op0 and Op1, truncated to their width.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same (scalar or vector) type).

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 1105 of file MachineIRBuilder.h.

Referenced by llvm::LegalizerHelper::lower().

◆ buildTrunc()

| MachineInstrBuilder MachineIRBuilder::buildTrunc | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_TRUNC Op.

G_TRUNC extracts the low bits of a type. For a vector type each element is truncated independently before being packed into the destination.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type. -

Resmust be smaller thanOp

- Returns

- The newly created instruction.

Definition at line 558 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), and llvm::LegalizerHelper::widenScalar().

◆ buildUAdde()

| MachineInstrBuilder MachineIRBuilder::buildUAdde | ( | const DstOp & | Res, |

| const DstOp & | CarryOut, | ||

| const SrcOp & | Op0, | ||

| const SrcOp & | Op1, | ||

| const SrcOp & | CarryIn | ||

| ) |

Build and insert Res, CarryOut = G_UADDE Op0, Op1, CarryIn.

G_UADDE sets Res to Op0 + Op1 + CarryIn (truncated to the bit width) and sets CarryOut to 1 if the result overflowed in unsigned arithmetic.

- Precondition

- setBasicBlock or setMI must have been called.

-

Res,Op0andOp1must be generic virtual registers with the same scalar type. -

CarryOutandCarryInmust be generic virtual registers with the same scalar type (typically s1)

- Returns

- The newly created instruction.

Definition at line 323 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::LegalizerHelper::narrowScalar().

◆ buildUndef()

| MachineInstrBuilder MachineIRBuilder::buildUndef | ( | const DstOp & | Res | ) |

Build and insert Res = IMPLICIT_DEF.

Definition at line 469 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by buildSequence(), llvm::LegalizerHelper::fewerElementsVector(), getOffsetFromIndices(), llvm::AArch64CallLowering::lowerFormalArguments(), and llvm::LegalizerHelper::narrowScalar().

◆ buildUnmerge() [1/2]

| MachineInstrBuilder MachineIRBuilder::buildUnmerge | ( | ArrayRef< LLT > | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res0, ...

= G_UNMERGE_VALUES Op

G_UNMERGE_VALUES splits contiguous bits of the input into multiple

- Precondition

- setBasicBlock or setMI must have been called.

-

The entire register

Res(and no more) must be covered by the input registers. -

The type of all

Resregisters must be identical.

- Returns

- a MachineInstrBuilder for the newly created instruction.

Definition at line 482 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

Referenced by isSupportedType(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::legalizeInstrStep(), llvm::X86CallLowering::lowerCall(), llvm::ARMCallLowering::lowerCall(), llvm::X86CallLowering::lowerReturn(), llvm::LegalizerHelper::narrowScalar(), and llvm::LegalizationArtifactCombiner::tryCombineMerges().

◆ buildUnmerge() [2/2]

| MachineInstrBuilder MachineIRBuilder::buildUnmerge | ( | ArrayRef< unsigned > | Res, |

| const SrcOp & | Op | ||

| ) |

Definition at line 491 of file MachineIRBuilder.cpp.

References llvm::ArrayRef< T >::begin(), buildInstr(), and llvm::ArrayRef< T >::end().

◆ buildZExt()

| MachineInstrBuilder MachineIRBuilder::buildZExt | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_ZEXT Op.

G_ZEXT produces a register of the specified width, with bits 0 to sizeof(Ty) * 8 set to Op. The remaining bits are 0. For a vector register, each element is extended individually.

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type. -

Opmust be smaller thanRes

- Returns

- The newly created instruction.

Definition at line 342 of file MachineIRBuilder.cpp.

References buildInstr().

Referenced by llvm::CallLowering::ValueHandler::extendRegister(), llvm::LegalizerHelper::lower(), llvm::AArch64CallLowering::lowerReturn(), and llvm::LegalizerHelper::widenScalar().

◆ buildZExtOrTrunc()

| MachineInstrBuilder MachineIRBuilder::buildZExtOrTrunc | ( | const DstOp & | Res, |

| const SrcOp & | Op | ||

| ) |

Build and insert Res = G_ZEXT Op, Res = G_TRUNC Op, or Res = COPY Op depending on the differing sizes of Res and Op.

///

- Precondition

- setBasicBlock or setMI must have been called.

-

Resmust be a generic virtual register with scalar or vector type. -

Opmust be a generic virtual register with scalar or vector type.

- Returns

- The newly created instruction.

Definition at line 376 of file MachineIRBuilder.cpp.

References buildExtOrTrunc().

Referenced by getOffsetFromIndices().

◆ getCSEInfo() [1/2]

|

inline |

Definition at line 254 of file MachineIRBuilder.h.

References llvm::MachineIRBuilderState::CSEInfo.

Referenced by llvm::CSEMIRBuilder::buildInstr().

◆ getCSEInfo() [2/2]

|

inline |

Definition at line 255 of file MachineIRBuilder.h.

References llvm::MachineIRBuilderState::CSEInfo.

◆ getDebugLoc()

|

inline |

Get the current instruction's debug location.

Definition at line 290 of file MachineIRBuilder.h.

References buildGEP(), C, llvm::MachineIRBuilderState::DL, and Reg.

Referenced by getOffsetFromIndices().

◆ getDL()

Getter for DebugLoc.

Definition at line 234 of file MachineIRBuilder.h.

References llvm::MachineIRBuilderState::DL.

Referenced by buildConstDbgValue(), buildDirectDbgValue(), buildFIDbgValue(), buildIndirectDbgValue(), and buildInstrNoInsert().

◆ getInsertPt()

|

inline |

Current insertion point for new instructions.

Definition at line 258 of file MachineIRBuilder.h.

References llvm::MachineIRBuilderState::II, Info, llvm::MachineIRBuilderState::MBB, llvm::MachineIRBuilderState::MF, and llvm::MachineIRBuilderState::Observer.

Referenced by insertInstr(), and llvm::LegalizerHelper::narrowScalar().

◆ getMBB() [1/2]

|

inline |

Getter for the basic block we currently build.

Definition at line 244 of file MachineIRBuilder.h.

References assert(), and llvm::MachineIRBuilderState::MBB.

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), computeValueLLTs(), getOffsetFromIndices(), llvm::MipsCallLowering::MipsHandler::handle(), insertInstr(), llvm::X86CallLowering::lowerFormalArguments(), llvm::AMDGPUCallLowering::lowerFormalArguments(), llvm::ARMCallLowering::lowerFormalArguments(), llvm::AArch64CallLowering::lowerFormalArguments(), llvm::X86CallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), and llvm::LegalizerHelper::narrowScalar().

◆ getMBB() [2/2]

|

inline |

Definition at line 249 of file MachineIRBuilder.h.

◆ getMF()

|

inline |

Getter for the function we currently build.

Definition at line 228 of file MachineIRBuilder.h.

References assert(), and llvm::MachineIRBuilderState::MF.

Referenced by llvm::AArch64CallLowering::AArch64CallLowering(), buildConstant(), buildDirectDbgValue(), buildFConstant(), buildIndirectDbgValue(), buildInstrNoInsert(), llvm::createLibcall(), llvm::RegBankSelect::getAnalysisUsage(), llvm::CallLowering::handleAssignments(), isSupportedType(), llvm::AArch64LegalizerInfo::legalizeCustom(), llvm::ARMLegalizerInfo::legalizeCustom(), llvm::LegalizerHelper::libcall(), llvm::LegalizerHelper::lower(), llvm::X86CallLowering::lowerCall(), llvm::ARMCallLowering::lowerCall(), llvm::AArch64CallLowering::lowerCall(), llvm::MipsCallLowering::lowerCall(), llvm::X86CallLowering::lowerFormalArguments(), llvm::AMDGPUCallLowering::lowerFormalArguments(), llvm::ARMCallLowering::lowerFormalArguments(), llvm::AArch64CallLowering::lowerFormalArguments(), llvm::MipsCallLowering::lowerFormalArguments(), llvm::X86CallLowering::lowerReturn(), llvm::AMDGPUCallLowering::lowerReturn(), llvm::ARMCallLowering::lowerReturn(), llvm::AArch64CallLowering::lowerReturn(), llvm::MipsCallLowering::lowerReturn(), llvm::LegalizerHelper::narrowScalar(), setInsertPt(), setMBB(), llvm::LegalizerHelper::widenScalar(), and llvm::X86CallLowering::X86CallLowering().

◆ getMRI() [1/2]

|

inline |

Getter for MRI.

Definition at line 237 of file MachineIRBuilder.h.