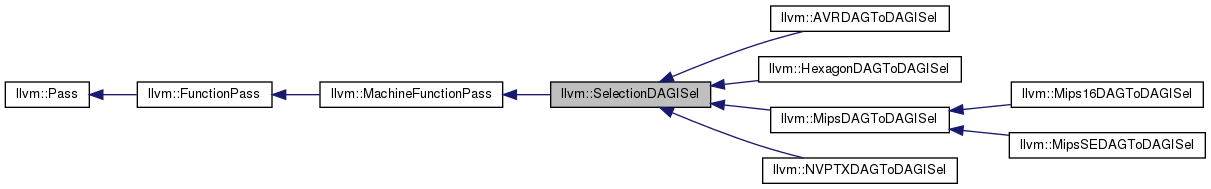

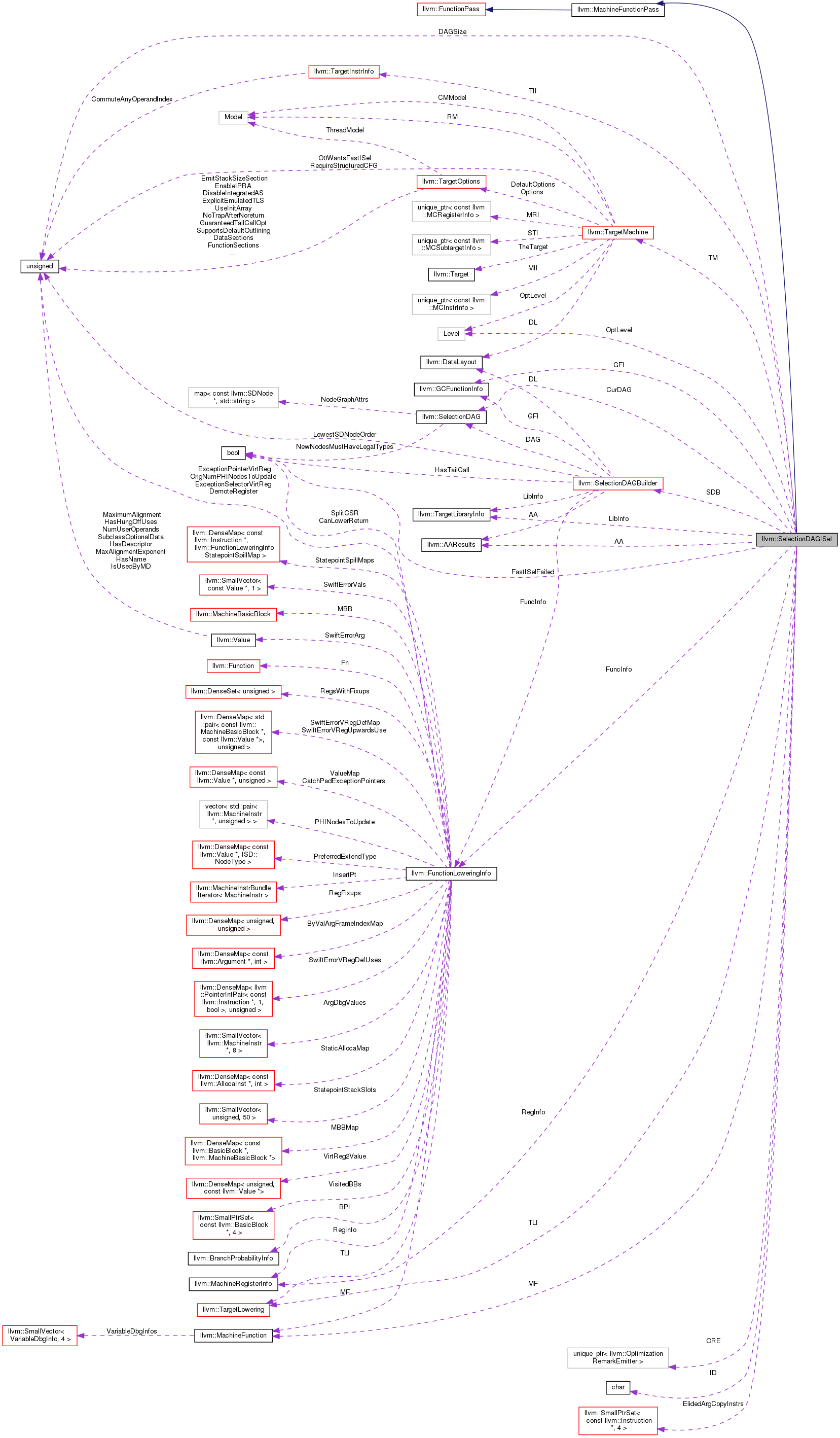

SelectionDAGISel - This is the common base class used for SelectionDAG-based pattern-matching instruction selectors. More...

#include "llvm/CodeGen/SelectionDAGISel.h"

Public Member Functions | |

| SelectionDAGISel (TargetMachine &tm, CodeGenOpt::Level OL=CodeGenOpt::Default) | |

| ~SelectionDAGISel () override | |

| const TargetLowering * | getTargetLowering () const |

| void | getAnalysisUsage (AnalysisUsage &AU) const override |

| getAnalysisUsage - Subclasses that override getAnalysisUsage must call this. More... | |

| bool | runOnMachineFunction (MachineFunction &MF) override |

| runOnMachineFunction - This method must be overloaded to perform the desired machine code transformation or analysis. More... | |

| virtual void | EmitFunctionEntryCode () |

| virtual void | PreprocessISelDAG () |

| PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts. More... | |

| virtual void | PostprocessISelDAG () |

| PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection. More... | |

| virtual void | Select (SDNode *N)=0 |

| Main hook for targets to transform nodes into machine nodes. More... | |

| virtual bool | SelectInlineAsmMemoryOperand (const SDValue &Op, unsigned ConstraintID, std::vector< SDValue > &OutOps) |

| SelectInlineAsmMemoryOperand - Select the specified address as a target addressing mode, according to the specified constraint. More... | |

| virtual bool | IsProfitableToFold (SDValue N, SDNode *U, SDNode *Root) const |

| IsProfitableToFold - Returns true if it's profitable to fold the specific operand node N of U during instruction selection that starts at Root. More... | |

| bool | CheckAndMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckAndMask - The isel is trying to match something like (and X, 255). More... | |

| bool | CheckOrMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckOrMask - The isel is trying to match something like (or X, 255). More... | |

| virtual bool | CheckPatternPredicate (unsigned PredNo) const |

| CheckPatternPredicate - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckNodePredicate (SDNode *N, unsigned PredNo) const |

| CheckNodePredicate - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckNodePredicateWithOperands (SDNode *N, unsigned PredNo, const SmallVectorImpl< SDValue > &Operands) const |

| CheckNodePredicateWithOperands - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckComplexPattern (SDNode *Root, SDNode *Parent, SDValue N, unsigned PatternNo, SmallVectorImpl< std::pair< SDValue, SDNode *> > &Result) |

| virtual SDValue | RunSDNodeXForm (SDValue V, unsigned XFormNo) |

| void | SelectCodeCommon (SDNode *NodeToMatch, const unsigned char *MatcherTable, unsigned TableSize) |

| virtual bool | ComplexPatternFuncMutatesDAG () const |

| Return true if complex patterns for this target can mutate the DAG. More... | |

| bool | isOrEquivalentToAdd (const SDNode *N) const |

Public Member Functions inherited from llvm::MachineFunctionPass Public Member Functions inherited from llvm::MachineFunctionPass | |

| bool | doInitialization (Module &) override |

| doInitialization - Virtual method overridden by subclasses to do any necessary initialization before any pass is run. More... | |

Public Member Functions inherited from llvm::FunctionPass Public Member Functions inherited from llvm::FunctionPass | |

| FunctionPass (char &pid) | |

| Pass * | createPrinterPass (raw_ostream &OS, const std::string &Banner) const override |

| createPrinterPass - Get a function printer pass. More... | |

| void | assignPassManager (PMStack &PMS, PassManagerType T) override |

| Find appropriate Function Pass Manager or Call Graph Pass Manager in the PM Stack and add self into that manager. More... | |

| PassManagerType | getPotentialPassManagerType () const override |

| Return what kind of Pass Manager can manage this pass. More... | |

Public Member Functions inherited from llvm::Pass Public Member Functions inherited from llvm::Pass | |

| Pass (PassKind K, char &pid) | |

| Pass (const Pass &)=delete | |

| Pass & | operator= (const Pass &)=delete |

| virtual | ~Pass () |

| PassKind | getPassKind () const |

| virtual StringRef | getPassName () const |

| getPassName - Return a nice clean name for a pass. More... | |

| AnalysisID | getPassID () const |

| getPassID - Return the PassID number that corresponds to this pass. More... | |

| virtual bool | doFinalization (Module &) |

| doFinalization - Virtual method overriden by subclasses to do any necessary clean up after all passes have run. More... | |

| virtual void | print (raw_ostream &OS, const Module *M) const |

| print - Print out the internal state of the pass. More... | |

| void | dump () const |

| virtual void | preparePassManager (PMStack &) |

| Check if available pass managers are suitable for this pass or not. More... | |

| void | setResolver (AnalysisResolver *AR) |

| AnalysisResolver * | getResolver () const |

| virtual void | releaseMemory () |

| releaseMemory() - This member can be implemented by a pass if it wants to be able to release its memory when it is no longer needed. More... | |

| virtual void * | getAdjustedAnalysisPointer (AnalysisID ID) |

| getAdjustedAnalysisPointer - This method is used when a pass implements an analysis interface through multiple inheritance. More... | |

| virtual ImmutablePass * | getAsImmutablePass () |

| virtual PMDataManager * | getAsPMDataManager () |

| virtual void | verifyAnalysis () const |

| verifyAnalysis() - This member can be implemented by a analysis pass to check state of analysis information. More... | |

| virtual void | dumpPassStructure (unsigned Offset=0) |

| template<typename AnalysisType > | |

| AnalysisType * | getAnalysisIfAvailable () const |

| getAnalysisIfAvailable<AnalysisType>() - Subclasses use this function to get analysis information that might be around, for example to update it. More... | |

| bool | mustPreserveAnalysisID (char &AID) const |

| mustPreserveAnalysisID - This method serves the same function as getAnalysisIfAvailable, but works if you just have an AnalysisID. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis () const |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis (Function &F) |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI) const |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI, Function &F) |

Static Public Member Functions | |

| static bool | IsLegalToFold (SDValue N, SDNode *U, SDNode *Root, CodeGenOpt::Level OptLevel, bool IgnoreChains=false) |

| IsLegalToFold - Returns true if the specific operand node N of U can be folded during instruction selection that starts at Root. More... | |

| static void | InvalidateNodeId (SDNode *N) |

| static int | getUninvalidatedNodeId (SDNode *N) |

| static void | EnforceNodeIdInvariant (SDNode *N) |

| static int | getNumFixedFromVariadicInfo (unsigned Flags) |

| getNumFixedFromVariadicInfo - Transform an EmitNode flags word into the number of fixed arity values that should be skipped when copying from the root. More... | |

Static Public Member Functions inherited from llvm::Pass Static Public Member Functions inherited from llvm::Pass | |

| static const PassInfo * | lookupPassInfo (const void *TI) |

| static const PassInfo * | lookupPassInfo (StringRef Arg) |

| static Pass * | createPass (AnalysisID ID) |

Public Attributes | |

| TargetMachine & | TM |

| const TargetLibraryInfo * | LibInfo |

| FunctionLoweringInfo * | FuncInfo |

| MachineFunction * | MF |

| MachineRegisterInfo * | RegInfo |

| SelectionDAG * | CurDAG |

| SelectionDAGBuilder * | SDB |

| AliasAnalysis * | AA |

| GCFunctionInfo * | GFI |

| CodeGenOpt::Level | OptLevel |

| const TargetInstrInfo * | TII |

| const TargetLowering * | TLI |

| bool | FastISelFailed |

| SmallPtrSet< const Instruction *, 4 > | ElidedArgCopyInstrs |

| std::unique_ptr< OptimizationRemarkEmitter > | ORE |

| Current optimization remark emitter. More... | |

Static Public Attributes | |

| static char | ID = 0 |

Protected Member Functions | |

| void | ReplaceUses (SDValue F, SDValue T) |

| ReplaceUses - replace all uses of the old node F with the use of the new node T. More... | |

| void | ReplaceUses (const SDValue *F, const SDValue *T, unsigned Num) |

| ReplaceUses - replace all uses of the old nodes F with the use of the new nodes T. More... | |

| void | ReplaceUses (SDNode *F, SDNode *T) |

| ReplaceUses - replace all uses of the old node F with the use of the new node T. More... | |

| void | ReplaceNode (SDNode *F, SDNode *T) |

Replace all uses of F with T, then remove F from the DAG. More... | |

| void | SelectInlineAsmMemoryOperands (std::vector< SDValue > &Ops, const SDLoc &DL) |

| SelectInlineAsmMemoryOperands - Calls to this are automatically generated by tblgen. More... | |

| virtual StringRef | getPatternForIndex (unsigned index) |

| getPatternForIndex - Patterns selected by tablegen during ISEL More... | |

| virtual StringRef | getIncludePathForIndex (unsigned index) |

| getIncludePathForIndex - get the td source location of pattern instantiation More... | |

Protected Member Functions inherited from llvm::MachineFunctionPass Protected Member Functions inherited from llvm::MachineFunctionPass | |

| MachineFunctionPass (char &ID) | |

| virtual MachineFunctionProperties | getRequiredProperties () const |

| virtual MachineFunctionProperties | getSetProperties () const |

| virtual MachineFunctionProperties | getClearedProperties () const |

Protected Member Functions inherited from llvm::FunctionPass Protected Member Functions inherited from llvm::FunctionPass | |

| bool | skipFunction (const Function &F) const |

| Optional passes call this function to check whether the pass should be skipped. More... | |

Protected Attributes | |

| unsigned | DAGSize |

| DAGSize - Size of DAG being instruction selected. More... | |

Detailed Description

SelectionDAGISel - This is the common base class used for SelectionDAG-based pattern-matching instruction selectors.

Definition at line 44 of file SelectionDAGISel.h.

Member Enumeration Documentation

◆ anonymous enum

| anonymous enum |

| Enumerator | |

|---|---|

| OPFL_None | |

| OPFL_Chain | |

| OPFL_GlueInput | |

| OPFL_GlueOutput | |

| OPFL_MemRefs | |

| OPFL_Variadic0 | |

| OPFL_Variadic1 | |

| OPFL_Variadic2 | |

| OPFL_Variadic3 | |

| OPFL_Variadic4 | |

| OPFL_Variadic5 | |

| OPFL_Variadic6 | |

| OPFL_VariadicInfo | |

Definition at line 174 of file SelectionDAGISel.h.

◆ BuiltinOpcodes

Definition at line 119 of file SelectionDAGISel.h.

Constructor & Destructor Documentation

◆ SelectionDAGISel()

|

explicit |

◆ ~SelectionDAGISel()

|

override |

Definition at line 322 of file SelectionDAGISel.cpp.

Member Function Documentation

◆ CheckAndMask()

| bool SelectionDAGISel::CheckAndMask | ( | SDValue | LHS, |

| ConstantSDNode * | RHS, | ||

| int64_t | DesiredMaskS | ||

| ) | const |

CheckAndMask - The isel is trying to match something like (and X, 255).

If the dag combiner simplified the 255, we still want to match. RHS is the actual value in the DAG on the RHS of an AND, and DesiredMaskS is the value specified in the .td file (e.g. 255).

Definition at line 2169 of file SelectionDAGISel.cpp.

References CurDAG, llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getValueSizeInBits(), llvm::APInt::isSubsetOf(), and llvm::SelectionDAG::MaskedValueIsZero().

Referenced by CheckAndImm(), and getIncludePathForIndex().

◆ CheckComplexPattern()

|

inlinevirtual |

Definition at line 282 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by SelectCodeCommon().

◆ CheckNodePredicate()

|

inlinevirtual |

CheckNodePredicate - This function is generated by tblgen in the target.

It runs node predicate number PredNo and returns true if it succeeds or false if it fails. The number is a private implementation detail to the code tblgen produces.

Definition at line 267 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by CheckNodePredicate(), IsPredicateKnownToFail(), and SelectCodeCommon().

◆ CheckNodePredicateWithOperands()

|

inlinevirtual |

CheckNodePredicateWithOperands - This function is generated by tblgen in the target.

It runs node predicate number PredNo and returns true if it succeeds or false if it fails. The number is a private implementation detail to the code tblgen produces.

Definition at line 276 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by SelectCodeCommon().

◆ CheckOrMask()

| bool SelectionDAGISel::CheckOrMask | ( | SDValue | LHS, |

| ConstantSDNode * | RHS, | ||

| int64_t | DesiredMaskS | ||

| ) | const |

CheckOrMask - The isel is trying to match something like (or X, 255).

If the dag combiner simplified the 255, we still want to match. RHS is the actual value in the DAG on the RHS of an OR, and DesiredMaskS is the value specified in the .td file (e.g. 255).

Definition at line 2198 of file SelectionDAGISel.cpp.

References llvm::SelectionDAG::computeKnownBits(), CurDAG, llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getValueSizeInBits(), llvm::APInt::isSubsetOf(), and llvm::KnownBits::One.

Referenced by CheckOrImm(), and getIncludePathForIndex().

◆ CheckPatternPredicate()

CheckPatternPredicate - This function is generated by tblgen in the target.

It runs the specified pattern predicate and returns true if it succeeds or false if it fails. The number is a private implementation detail to the code tblgen produces.

Definition at line 259 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by CheckPatternPredicate(), IsPredicateKnownToFail(), and SelectCodeCommon().

◆ ComplexPatternFuncMutatesDAG()

|

inlinevirtual |

Return true if complex patterns for this target can mutate the DAG.

Reimplemented in llvm::HexagonDAGToDAGISel.

Definition at line 297 of file SelectionDAGISel.h.

References isOrEquivalentToAdd().

Referenced by SelectCodeCommon().

◆ EmitFunctionEntryCode()

|

inlinevirtual |

Reimplemented in llvm::HexagonDAGToDAGISel.

Definition at line 77 of file SelectionDAGISel.h.

◆ EnforceNodeIdInvariant()

|

static |

Definition at line 1000 of file SelectionDAGISel.cpp.

Referenced by ReplaceNode(), ReplaceUses(), and SelectInlineAsmMemoryOperand().

◆ getAnalysisUsage()

|

overridevirtual |

getAnalysisUsage - Subclasses that override getAnalysisUsage must call this.

For MachineFunctionPasses, calling AU.preservesCFG() indicates that the pass does not modify the MachineBasicBlock CFG.

Reimplemented from llvm::MachineFunctionPass.

Reimplemented in llvm::MipsDAGToDAGISel.

Definition at line 328 of file SelectionDAGISel.cpp.

References llvm::AnalysisUsage::addPreserved(), llvm::AnalysisUsage::addRequired(), llvm::MachineFunctionPass::getAnalysisUsage(), llvm::CodeGenOpt::None, OptLevel, and UseMBPI.

Referenced by llvm::MipsDAGToDAGISel::getAnalysisUsage(), and getTargetLowering().

◆ getIncludePathForIndex()

|

inlineprotectedvirtual |

getIncludePathForIndex - get the td source location of pattern instantiation

Definition at line 244 of file SelectionDAGISel.h.

References CheckAndMask(), CheckOrMask(), and llvm_unreachable.

Referenced by SelectCodeCommon().

◆ getNumFixedFromVariadicInfo()

|

inlinestatic |

getNumFixedFromVariadicInfo - Transform an EmitNode flags word into the number of fixed arity values that should be skipped when copying from the root.

Definition at line 194 of file SelectionDAGISel.h.

References OPFL_VariadicInfo.

Referenced by SelectCodeCommon().

◆ getPatternForIndex()

|

inlineprotectedvirtual |

getPatternForIndex - Patterns selected by tablegen during ISEL

Definition at line 239 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by SelectCodeCommon().

◆ getTargetLowering()

|

inline |

Definition at line 71 of file SelectionDAGISel.h.

References getAnalysisUsage(), runOnMachineFunction(), and TLI.

Referenced by llvm::AVRDAGToDAGISel::select< ISD::FrameIndex >(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), isTargetConstant(), llvm::AVRDAGToDAGISel::SelectAddr(), and llvm::AVRDAGToDAGISel::selectIndexedLoad().

◆ getUninvalidatedNodeId()

|

static |

Definition at line 1025 of file SelectionDAGISel.cpp.

References llvm::SelectionDAG::allnodes_begin(), llvm::SelectionDAG::AssignTopologicalOrder(), CurDAG, DAGSize, llvm::dbgs(), llvm::NVPTXISD::Dummy, FuncInfo, llvm::MachineBasicBlock::getName(), llvm::SDValue::getNode(), llvm::SDNode::getNodeId(), llvm::SelectionDAG::getRoot(), LLVM_DEBUG, llvm::FunctionLoweringInfo::MBB, PreprocessISelDAG(), and llvm::printMBBReference().

Referenced by insertDAGNode(), and SelectInlineAsmMemoryOperand().

◆ InvalidateNodeId()

|

static |

Definition at line 1019 of file SelectionDAGISel.cpp.

References llvm::SDNode::getNodeId(), and llvm::SDNode::setNodeId().

Referenced by insertDAGNode(), and SelectInlineAsmMemoryOperand().

◆ IsLegalToFold()

|

static |

IsLegalToFold - Returns true if the specific operand node N of U can be folded during instruction selection that starts at Root.

FIXME: This is a static member function because the MSP430/X86 targets, which uses it during isel. This could become a proper member.

Definition at line 2349 of file SelectionDAGISel.cpp.

References CurDAG, llvm::dyn_cast(), findGlueUse(), findNonImmUse(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::MDNodeSDNode::getMD(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getNumValues(), llvm::SDNode::getOperand(), llvm::MDNode::getOperand(), llvm::TargetLowering::getRegisterByName(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::MVT::Glue, llvm::ISD::INLINEASM, LLVM_ATTRIBUTE_ALWAYS_INLINE, N, llvm::CodeGenOpt::None, llvm::SDNode::op_begin(), llvm::SDNode::op_end(), llvm::MVT::Other, Reg, llvm::SelectionDAG::RemoveDeadNode(), ReplaceUses(), SelectInlineAsmMemoryOperands(), llvm::SelectionDAG::SelectNodeTo(), llvm::SDNode::setNodeId(), and TLI.

Referenced by SelectCodeCommon(), and SelectInlineAsmMemoryOperand().

◆ isOrEquivalentToAdd()

Definition at line 3795 of file SelectionDAGISel.cpp.

References assert(), C, CurDAG, llvm::dyn_cast(), llvm::MachineFunction::getFrameInfo(), llvm::TargetMachine::getIntrinsicInfo(), llvm::Intrinsic::getName(), llvm::MCInstrInfo::getName(), llvm::MachineFunction::getName(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SDValue::getValueType(), ID, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::isPowerOf2_32(), MF, llvm::None, llvm::Intrinsic::num_intrinsics, llvm::ISD::OR, llvm::MVT::Other, llvm::SDNode::printrFull(), llvm::report_fatal_error(), llvm::raw_string_ostream::str(), TII, and TM.

Referenced by ComplexPatternFuncMutatesDAG().

◆ IsProfitableToFold()

IsProfitableToFold - Returns true if it's profitable to fold the specific operand node N of U during instruction selection that starts at Root.

Definition at line 2341 of file SelectionDAGISel.cpp.

References llvm::SDValue::hasOneUse(), llvm::CodeGenOpt::None, and OptLevel.

Referenced by SelectCodeCommon(), and SelectInlineAsmMemoryOperand().

◆ PostprocessISelDAG()

|

inlinevirtual |

PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection.

Definition at line 85 of file SelectionDAGISel.h.

◆ PreprocessISelDAG()

|

inlinevirtual |

PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts.

Reimplemented in llvm::HexagonDAGToDAGISel.

Definition at line 81 of file SelectionDAGISel.h.

Referenced by getUninvalidatedNodeId().

◆ ReplaceNode()

Replace all uses of F with T, then remove F from the DAG.

Definition at line 227 of file SelectionDAGISel.h.

References EnforceNodeIdInvariant(), llvm::SelectionDAG::RemoveDeadNode(), llvm::SelectionDAG::ReplaceAllUsesWith(), and SelectInlineAsmMemoryOperands().

Referenced by canLowerToLDG(), getPTXCmpMode(), isMemOPCandidate(), pickOpcodeForVT(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), llvm::HexagonDAGToDAGISel::SelectAddSubCarry(), llvm::HexagonDAGToDAGISel::SelectConstant(), llvm::HexagonDAGToDAGISel::SelectConstantFP(), llvm::HexagonDAGToDAGISel::SelectD2P(), llvm::HexagonDAGToDAGISel::SelectFrameIndex(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWOChain(), llvm::HexagonDAGToDAGISel::SelectP2D(), llvm::HexagonDAGToDAGISel::SelectQ2V(), llvm::HvxSelector::selectRor(), llvm::HexagonDAGToDAGISel::SelectSHL(), llvm::HvxSelector::selectShuffle(), llvm::HexagonDAGToDAGISel::SelectTypecast(), llvm::HexagonDAGToDAGISel::SelectV2Q(), llvm::HexagonDAGToDAGISel::SelectVAlign(), llvm::HvxSelector::selectVAlign(), and llvm::HexagonDAGToDAGISel::SelectVAlignAddr().

◆ ReplaceUses() [1/3]

ReplaceUses - replace all uses of the old node F with the use of the new node T.

Definition at line 206 of file SelectionDAGISel.h.

References EnforceNodeIdInvariant(), llvm::SDValue::getNode(), and llvm::SelectionDAG::ReplaceAllUsesOfValueWith().

Referenced by llvm::AVRDAGToDAGISel::select< AVRISD::CALL >(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), llvm::AVRDAGToDAGISel::select< ISD::LOAD >(), llvm::AVRDAGToDAGISel::select< ISD::STORE >(), GetVBR(), IsLegalToFold(), pickOpcodeForVT(), llvm::HexagonDAGToDAGISel::SelectBrevLdIntrinsic(), SelectCodeCommon(), llvm::AVRDAGToDAGISel::selectIndexedLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedStore(), llvm::HexagonDAGToDAGISel::SelectNewCircIntrinsic(), llvm::HexagonDAGToDAGISel::StoreInstrForLoadIntrinsic(), and llvm::HexagonDAGToDAGISel::tryLoadOfLoadIntrinsic().

◆ ReplaceUses() [2/3]

|

inlineprotected |

ReplaceUses - replace all uses of the old nodes F with the use of the new nodes T.

Definition at line 213 of file SelectionDAGISel.h.

References EnforceNodeIdInvariant(), and llvm::SelectionDAG::ReplaceAllUsesOfValuesWith().

◆ ReplaceUses() [3/3]

ReplaceUses - replace all uses of the old node F with the use of the new node T.

Definition at line 221 of file SelectionDAGISel.h.

References EnforceNodeIdInvariant(), and llvm::SelectionDAG::ReplaceAllUsesWith().

◆ runOnMachineFunction()

|

overridevirtual |

runOnMachineFunction - This method must be overloaded to perform the desired machine code transformation or analysis.

Implements llvm::MachineFunctionPass.

Reimplemented in llvm::NVPTXDAGToDAGISel, llvm::MipsDAGToDAGISel, llvm::HexagonDAGToDAGISel, and llvm::AVRDAGToDAGISel.

Definition at line 382 of file SelectionDAGISel.cpp.

References AA, llvm::FunctionLoweringInfo::ArgDbgValues, assert(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::begin(), llvm::MachineBasicBlock::begin(), llvm::FunctionLoweringInfo::BPI, llvm::BuildMI(), llvm::Function::callsFunctionThatReturnsTwice(), llvm::FunctionLoweringInfo::clear(), llvm::MachineRegisterInfo::clearKillFlags(), llvm::MachineRegisterInfo::constrainRegClass(), CurDAG, llvm::dbgs(), llvm::tgtok::Def, llvm::LLVMContext::diagnose(), E, llvm::MachineRegisterInfo::EmitLiveInCopies(), llvm::TargetOptions::EnableFastISel, EnableFastISelAbort, EnableFastISelFallbackReport, llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::end(), FastISelFailed, llvm::TargetLoweringBase::finalizeLowering(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::find(), From, llvm::MachineFunction::front(), FuncInfo, llvm::MCInstrInfo::get(), llvm::Function::getContext(), llvm::MachineInstr::getDebugExpression(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDebugVariable(), llvm::MachineFunction::getFrameInfo(), llvm::TargetRegisterInfo::getFrameRegister(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::Value::getName(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineFunction::getProperties(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::MachineFunction::getSubtarget(), llvm::TargetSubtargetInfo::getTargetLowering(), llvm::MachineRegisterInfo::getVRegDef(), GFI, llvm::MachineFrameInfo::hasCalls(), llvm::Function::hasGC(), llvm::MachineFunctionProperties::hasProperty(), I, llvm::SelectionDAG::init(), llvm::SelectionDAGBuilder::init(), llvm::TargetLowering::initializeSplitCSR(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT, BucketT >::insert(), llvm::MachineBasicBlock::insert(), llvm::MachineBasicBlock::insertAfter(), llvm::TargetLowering::insertCopiesSplitCSR(), llvm::MCInstrDesc::isCall(), llvm::MachineInstr::isCopy(), llvm::MachineInstr::isDebugValue(), llvm::MachineOperand::isFI(), llvm::MachineInstr::isIndirectDebugValue(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MCInstrDesc::isReturn(), llvm::TargetRegisterInfo::isVirtualRegister(), LibInfo, llvm::MachineRegisterInfo::liveins(), LLVM_DEBUG, MF, MI, MRI, llvm::CodeGenOpt::None, llvm::TargetMachine::Options, OptLevel, ORE, llvm::SmallVectorTemplateBase< T >::push_back(), Reg, llvm::FunctionLoweringInfo::RegFixups, RegInfo, llvm::MachineRegisterInfo::replaceRegWith(), llvm::TargetMachine::resetTargetOptions(), SDB, llvm::MachineFunctionProperties::Selected, llvm::FunctionLoweringInfo::set(), llvm::MachineFrameInfo::setHasCalls(), llvm::MachineFunction::setHasInlineAsm(), llvm::FunctionPass::skipFunction(), SplitCriticalSideEffectEdges(), llvm::FunctionLoweringInfo::SplitCSR, llvm::succ_empty(), llvm::TargetLowering::supportSplitCSR(), TII, TLI, TM, TRI, llvm::MachineRegisterInfo::use_empty(), llvm::MachineRegisterInfo::use_instr_begin(), llvm::MachineRegisterInfo::use_instr_end(), UseMBPI, UseMI, and llvm::TargetRegisterInfo::virtReg2Index().

Referenced by llvm::createR600ISelDag(), getTargetLowering(), llvm::AVRDAGToDAGISel::runOnMachineFunction(), llvm::HexagonDAGToDAGISel::runOnMachineFunction(), llvm::MipsDAGToDAGISel::runOnMachineFunction(), and llvm::NVPTXDAGToDAGISel::runOnMachineFunction().

◆ RunSDNodeXForm()

|

inlinevirtual |

Definition at line 288 of file SelectionDAGISel.h.

References llvm_unreachable, and SelectCodeCommon().

Referenced by SelectCodeCommon().

◆ Select()

|

pure virtual |

Main hook for targets to transform nodes into machine nodes.

Implemented in llvm::HexagonDAGToDAGISel.

Referenced by PostprocessISelDAG().

◆ SelectCodeCommon()

| void SelectionDAGISel::SelectCodeCommon | ( | SDNode * | NodeToMatch, |

| const unsigned char * | MatcherTable, | ||

| unsigned | TableSize | ||

| ) |

Definition at line 2935 of file SelectionDAGISel.cpp.

References llvm::ISD::ANNOTATION_LABEL, assert(), llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::SmallVectorTemplateCommon< T >::back(), llvm::ISD::BasicBlock, CheckAndImm(), CheckChildInteger(), CheckChildSame(), CheckChildType(), CheckComplexPattern(), CheckCondCode(), CheckInteger(), CheckNodePredicate(), CheckNodePredicateWithOperands(), CheckOpcode(), CheckOrImm(), CheckPatternPredicate(), CheckSame(), CheckType(), CheckValueType(), llvm::SmallVectorImpl< T >::clear(), ComplexPatternFuncMutatesDAG(), llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::ISD::CopyFromReg, llvm::ISD::CopyToReg, CurDAG, llvm::dbgs(), llvm::ISD::DELETED_NODE, llvm::SDNode::dump(), E, llvm::ISD::EH_LABEL, llvm::SmallVectorBase::empty(), llvm::ISD::EntryToken, first, llvm::MCInstrInfo::get(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getDataLayout(), llvm::SelectionDAG::getEntryNode(), getIncludePathForIndex(), llvm::SelectionDAG::getMachineNode(), llvm::SDValue::getNode(), getNumFixedFromVariadicInfo(), llvm::SDValue::getNumOperands(), llvm::SDNode::getNumOperands(), llvm::SDNode::getNumValues(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), getPatternForIndex(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAG::getTargetConstantFP(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), GetVBR(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, HandleMergeInputChains(), llvm::ISD::HANDLENODE, llvm::ISD::INLINEASM, llvm::MVT::iPTR, llvm::is_contained(), IsLegalToFold(), llvm::SDNode::isMachineOpcode(), IsPredicateKnownToFail(), IsProfitableToFold(), llvm::ISD::LIFETIME_END, llvm::ISD::LIFETIME_START, LLVM_DEBUG, llvm::MCInstrDesc::mayLoad(), llvm::MCInstrDesc::mayStore(), llvm::ISD::MCSymbol, llvm::ISD::MDNODE_SDNODE, llvm::MachineSDNode::memoperands_empty(), N, OPC_CaptureGlueInput, OPC_CheckAndImm, OPC_CheckChild0Integer, OPC_CheckChild0Same, OPC_CheckChild0Type, OPC_CheckChild1Integer, OPC_CheckChild1Same, OPC_CheckChild1Type, OPC_CheckChild2Integer, OPC_CheckChild2Same, OPC_CheckChild2Type, OPC_CheckChild3Integer, OPC_CheckChild3Same, OPC_CheckChild3Type, OPC_CheckChild4Integer, OPC_CheckChild4Type, OPC_CheckChild5Type, OPC_CheckChild6Type, OPC_CheckChild7Type, OPC_CheckComplexPat, OPC_CheckCondCode, OPC_CheckFoldableChainNode, OPC_CheckInteger, OPC_CheckOpcode, OPC_CheckOrImm, OPC_CheckPatternPredicate, OPC_CheckPredicate, OPC_CheckPredicateWithOperands, OPC_CheckSame, OPC_CheckType, OPC_CheckTypeRes, OPC_CheckValueType, OPC_CompleteMatch, OPC_Coverage, OPC_EmitConvertToTarget, OPC_EmitCopyToReg, OPC_EmitInteger, OPC_EmitMergeInputChains, OPC_EmitMergeInputChains1_0, OPC_EmitMergeInputChains1_1, OPC_EmitMergeInputChains1_2, OPC_EmitNode, OPC_EmitNode0, OPC_EmitNode1, OPC_EmitNode2, OPC_EmitNodeXForm, OPC_EmitRegister, OPC_EmitRegister2, OPC_MorphNodeTo, OPC_MorphNodeTo0, OPC_MorphNodeTo1, OPC_MorphNodeTo2, OPC_MoveChild, OPC_MoveChild0, OPC_MoveChild1, OPC_MoveChild2, OPC_MoveChild3, OPC_MoveChild4, OPC_MoveChild5, OPC_MoveChild6, OPC_MoveChild7, OPC_MoveParent, OPC_RecordChild0, OPC_RecordChild1, OPC_RecordChild2, OPC_RecordChild3, OPC_RecordChild4, OPC_RecordChild5, OPC_RecordChild6, OPC_RecordChild7, OPC_RecordMemRef, OPC_RecordNode, OPC_Scope, OPC_SwitchOpcode, OPC_SwitchType, OPFL_Chain, OPFL_GlueInput, OPFL_GlueOutput, OPFL_MemRefs, OPFL_VariadicInfo, OptLevel, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T >::pop_back(), llvm::SmallVectorTemplateBase< T >::push_back(), llvm::ISD::READ_REGISTER, llvm::ISD::Register, llvm::ISD::RegisterMask, llvm::sys::fs::remove(), llvm::SelectionDAG::RemoveDeadNode(), ReplaceUses(), llvm::SmallVectorImpl< T >::resize(), RunSDNodeXForm(), llvm::SelectionDAG::salvageDebugInfo(), second, llvm::SDNode::setNodeId(), llvm::SelectionDAG::setNodeMemRefs(), llvm::SmallVectorBase::size(), llvm::ISD::TargetBlockAddress, llvm::ISD::TargetConstant, llvm::ISD::TargetConstantFP, llvm::ISD::TargetConstantPool, llvm::ISD::TargetExternalSymbol, llvm::ISD::TargetFrameIndex, llvm::ISD::TargetGlobalAddress, llvm::ISD::TargetGlobalTLSAddress, llvm::ISD::TargetJumpTable, TII, TLI, llvm::ISD::TokenFactor, llvm::ISD::UNDEF, llvm::SDNode::use_empty(), and llvm::ISD::WRITE_REGISTER.

Referenced by RunSDNodeXForm().

◆ SelectInlineAsmMemoryOperand()

|

inlinevirtual |

SelectInlineAsmMemoryOperand - Select the specified address as a target addressing mode, according to the specified constraint.

If this does not match or is not implemented, return true. The resultant operands (which will appear in the machine instruction) should be added to the OutOps vector.

Reimplemented in llvm::HexagonDAGToDAGISel, llvm::NVPTXDAGToDAGISel, and llvm::AVRDAGToDAGISel.

Definition at line 95 of file SelectionDAGISel.h.

References EnforceNodeIdInvariant(), getUninvalidatedNodeId(), InvalidateNodeId(), IsLegalToFold(), and IsProfitableToFold().

Referenced by SelectInlineAsmMemoryOperands().

◆ SelectInlineAsmMemoryOperands()

|

protected |

SelectInlineAsmMemoryOperands - Calls to this are automatically generated by tblgen.

Others should not call it.

Definition at line 2228 of file SelectionDAGISel.cpp.

References assert(), CurDAG, llvm::InlineAsm::getFlagWord(), llvm::InlineAsm::getFlagWordForMem(), llvm::InlineAsm::getMemoryConstraintID(), llvm::InlineAsm::getNumOperandRegisters(), llvm::SelectionDAG::getTargetConstant(), llvm::MVT::Glue, llvm::MVT::i32, llvm::InlineAsm::isMemKind(), llvm::InlineAsm::isUseOperandTiedToDef(), llvm::InlineAsm::Kind_Mem, llvm::InlineAsm::Op_AsmString, llvm::InlineAsm::Op_ExtraInfo, llvm::InlineAsm::Op_FirstOperand, llvm::InlineAsm::Op_InputChain, llvm::InlineAsm::Op_MDNode, llvm::report_fatal_error(), SelectInlineAsmMemoryOperand(), and std::swap().

Referenced by IsLegalToFold(), and ReplaceNode().

Member Data Documentation

◆ AA

| AliasAnalysis* llvm::SelectionDAGISel::AA |

Definition at line 53 of file SelectionDAGISel.h.

Referenced by llvm::createVLIWDAGScheduler(), runOnMachineFunction(), and llvm::HexagonDAGToDAGISel::SelectVAlignAddr().

◆ CurDAG

| SelectionDAG* llvm::SelectionDAGISel::CurDAG |

Definition at line 51 of file SelectionDAGISel.h.

Referenced by llvm::AVRDAGToDAGISel::select< AVRISD::CALL >(), llvm::AVRDAGToDAGISel::select< ISD::BRIND >(), llvm::AVRDAGToDAGISel::select< ISD::FrameIndex >(), llvm::AVRDAGToDAGISel::select< ISD::LOAD >(), llvm::AVRDAGToDAGISel::select< ISD::STORE >(), canLowerToLDG(), CheckAndMask(), CheckOrMask(), llvm::HexagonDAGToDAGISel::DetectUseSxtw(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), getPTXCmpMode(), getUninvalidatedNodeId(), GetVBR(), IsLegalToFold(), isMemOPCandidate(), isOrEquivalentToAdd(), IsPredicateKnownToFail(), isTargetConstant(), llvm::HexagonDAGToDAGISel::LoadInstrForLoadIntrinsic(), mapWasmLandingPadIndex(), pickOpcodeForVT(), llvm::HexagonDAGToDAGISel::PreprocessISelDAG(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), runOnMachineFunction(), llvm::AVRDAGToDAGISel::SelectAddr(), llvm::HexagonDAGToDAGISel::SelectAddrFI(), llvm::HexagonDAGToDAGISel::SelectAddSubCarry(), llvm::HexagonDAGToDAGISel::SelectAnyImmediate(), llvm::HexagonDAGToDAGISel::SelectBrevLdIntrinsic(), SelectCodeCommon(), llvm::HexagonDAGToDAGISel::SelectConstant(), llvm::HexagonDAGToDAGISel::SelectConstantFP(), llvm::HexagonDAGToDAGISel::SelectD2P(), llvm::HexagonDAGToDAGISel::SelectFrameIndex(), llvm::HexagonDAGToDAGISel::SelectGlobalAddress(), llvm::AVRDAGToDAGISel::selectIndexedLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedLoad(), llvm::HexagonDAGToDAGISel::SelectIndexedStore(), llvm::AVRDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::NVPTXDAGToDAGISel::SelectInlineAsmMemoryOperand(), llvm::HexagonDAGToDAGISel::SelectInlineAsmMemoryOperand(), SelectInlineAsmMemoryOperands(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWChain(), llvm::HexagonDAGToDAGISel::SelectIntrinsicWOChain(), llvm::HexagonDAGToDAGISel::SelectNewCircIntrinsic(), llvm::HexagonDAGToDAGISel::SelectP2D(), llvm::HexagonDAGToDAGISel::SelectQ2V(), llvm::HexagonDAGToDAGISel::SelectSHL(), llvm::HexagonDAGToDAGISel::SelectTypecast(), llvm::HexagonDAGToDAGISel::SelectV2Q(), llvm::HexagonDAGToDAGISel::SelectVAlign(), llvm::HexagonDAGToDAGISel::SelectVAlignAddr(), llvm::HexagonDAGToDAGISel::StoreInstrForLoadIntrinsic(), llvm::HexagonDAGToDAGISel::tryLoadOfLoadIntrinsic(), willShiftRightEliminate(), and ~SelectionDAGISel().

◆ DAGSize

|

protected |

DAGSize - Size of DAG being instruction selected.

Definition at line 202 of file SelectionDAGISel.h.

Referenced by getUninvalidatedNodeId().

◆ ElidedArgCopyInstrs

| SmallPtrSet<const Instruction *, 4> llvm::SelectionDAGISel::ElidedArgCopyInstrs |

Definition at line 59 of file SelectionDAGISel.h.

◆ FastISelFailed

| bool llvm::SelectionDAGISel::FastISelFailed |

Definition at line 58 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

◆ FuncInfo

| FunctionLoweringInfo* llvm::SelectionDAGISel::FuncInfo |

Definition at line 48 of file SelectionDAGISel.h.

Referenced by llvm::HexagonDAGToDAGISel::EmitFunctionEntryCode(), getUninvalidatedNodeId(), mapWasmLandingPadIndex(), runOnMachineFunction(), and ~SelectionDAGISel().

◆ GFI

| GCFunctionInfo* llvm::SelectionDAGISel::GFI |

Definition at line 54 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

◆ ID

|

static |

Definition at line 65 of file SelectionDAGISel.h.

Referenced by isOrEquivalentToAdd().

◆ LibInfo

| const TargetLibraryInfo* llvm::SelectionDAGISel::LibInfo |

Definition at line 47 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

◆ MF

| MachineFunction* llvm::SelectionDAGISel::MF |

Definition at line 49 of file SelectionDAGISel.h.

Referenced by llvm::createBURRListDAGScheduler(), llvm::createDAGLinearizer(), llvm::createDefaultScheduler(), llvm::createFastDAGScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::createSourceListDAGScheduler(), llvm::createVLIWDAGScheduler(), llvm::HexagonDAGToDAGISel::DetectUseSxtw(), llvm::HexagonDAGToDAGISel::EmitFunctionEntryCode(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), llvm::AVRDAGToDAGISel::getPassName(), llvm::MipsDAGToDAGISel::getPassName(), isOrEquivalentToAdd(), mapWasmLandingPadIndex(), llvm::Mips16DAGToDAGISel::Mips16DAGToDAGISel(), llvm::MipsSEDAGToDAGISel::MipsSEDAGToDAGISel(), llvm::OptLevelChanger::OptLevelChanger(), pickOpcodeForVT(), processDbgDeclares(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), runOnMachineFunction(), llvm::HexagonDAGToDAGISel::SelectAddrFI(), llvm::HexagonDAGToDAGISel::SelectFrameIndex(), llvm::AVRDAGToDAGISel::SelectInlineAsmMemoryOperand(), and llvm::OptLevelChanger::~OptLevelChanger().

◆ OptLevel

| CodeGenOpt::Level llvm::SelectionDAGISel::OptLevel |

Definition at line 55 of file SelectionDAGISel.h.

Referenced by getAnalysisUsage(), IsProfitableToFold(), llvm::OptLevelChanger::OptLevelChanger(), llvm::NVPTXDAGToDAGISel::runOnMachineFunction(), runOnMachineFunction(), SelectCodeCommon(), and llvm::OptLevelChanger::~OptLevelChanger().

◆ ORE

| std::unique_ptr<OptimizationRemarkEmitter> llvm::SelectionDAGISel::ORE |

Current optimization remark emitter.

Used to report things like combines and FastISel failures.

Definition at line 63 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

◆ RegInfo

| MachineRegisterInfo* llvm::SelectionDAGISel::RegInfo |

Definition at line 50 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

◆ SDB

| SelectionDAGBuilder* llvm::SelectionDAGISel::SDB |

Definition at line 52 of file SelectionDAGISel.h.

Referenced by mapWasmLandingPadIndex(), runOnMachineFunction(), and ~SelectionDAGISel().

◆ TII

| const TargetInstrInfo* llvm::SelectionDAGISel::TII |

Definition at line 56 of file SelectionDAGISel.h.

Referenced by isOrEquivalentToAdd(), mapWasmLandingPadIndex(), propagateSwiftErrorVRegs(), runOnMachineFunction(), and SelectCodeCommon().

◆ TLI

| const TargetLowering* llvm::SelectionDAGISel::TLI |

Definition at line 57 of file SelectionDAGISel.h.

Referenced by CheckChildType(), llvm::createDefaultScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), getTargetLowering(), IsLegalToFold(), IsPredicateKnownToFail(), isTargetConstant(), mapWasmLandingPadIndex(), propagateSwiftErrorVRegs(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), runOnMachineFunction(), and SelectCodeCommon().

◆ TM

| TargetMachine& llvm::SelectionDAGISel::TM |

Definition at line 46 of file SelectionDAGISel.h.

Referenced by isOrEquivalentToAdd(), llvm::OptLevelChanger::OptLevelChanger(), runOnMachineFunction(), and llvm::OptLevelChanger::~OptLevelChanger().

The documentation for this class was generated from the following files:

- include/llvm/CodeGen/SelectionDAGISel.h

- lib/CodeGen/SelectionDAG/SelectionDAGBuilder.cpp

- lib/CodeGen/SelectionDAG/SelectionDAGISel.cpp

1.8.13

1.8.13