#include "Target/NVPTX/NVPTXISelDAGToDAG.h"

Public Member Functions | |

| NVPTXDAGToDAGISel (NVPTXTargetMachine &tm, CodeGenOpt::Level OptLevel) | |

| StringRef | getPassName () const override |

| getPassName - Return a nice clean name for a pass. More... | |

| bool | runOnMachineFunction (MachineFunction &MF) override |

| runOnMachineFunction - This method must be overloaded to perform the desired machine code transformation or analysis. More... | |

| bool | SelectInlineAsmMemoryOperand (const SDValue &Op, unsigned ConstraintID, std::vector< SDValue > &OutOps) override |

| SelectInlineAsmMemoryOperand - Implement addressing mode selection for inline asm expressions. More... | |

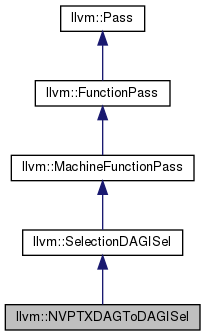

Public Member Functions inherited from llvm::SelectionDAGISel Public Member Functions inherited from llvm::SelectionDAGISel | |

| SelectionDAGISel (TargetMachine &tm, CodeGenOpt::Level OL=CodeGenOpt::Default) | |

| ~SelectionDAGISel () override | |

| const TargetLowering * | getTargetLowering () const |

| void | getAnalysisUsage (AnalysisUsage &AU) const override |

| getAnalysisUsage - Subclasses that override getAnalysisUsage must call this. More... | |

| virtual void | EmitFunctionEntryCode () |

| virtual void | PreprocessISelDAG () |

| PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts. More... | |

| virtual void | PostprocessISelDAG () |

| PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection. More... | |

| virtual bool | IsProfitableToFold (SDValue N, SDNode *U, SDNode *Root) const |

| IsProfitableToFold - Returns true if it's profitable to fold the specific operand node N of U during instruction selection that starts at Root. More... | |

| bool | CheckAndMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckAndMask - The isel is trying to match something like (and X, 255). More... | |

| bool | CheckOrMask (SDValue LHS, ConstantSDNode *RHS, int64_t DesiredMaskS) const |

| CheckOrMask - The isel is trying to match something like (or X, 255). More... | |

| virtual bool | CheckPatternPredicate (unsigned PredNo) const |

| CheckPatternPredicate - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckNodePredicate (SDNode *N, unsigned PredNo) const |

| CheckNodePredicate - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckNodePredicateWithOperands (SDNode *N, unsigned PredNo, const SmallVectorImpl< SDValue > &Operands) const |

| CheckNodePredicateWithOperands - This function is generated by tblgen in the target. More... | |

| virtual bool | CheckComplexPattern (SDNode *Root, SDNode *Parent, SDValue N, unsigned PatternNo, SmallVectorImpl< std::pair< SDValue, SDNode *> > &Result) |

| virtual SDValue | RunSDNodeXForm (SDValue V, unsigned XFormNo) |

| void | SelectCodeCommon (SDNode *NodeToMatch, const unsigned char *MatcherTable, unsigned TableSize) |

| virtual bool | ComplexPatternFuncMutatesDAG () const |

| Return true if complex patterns for this target can mutate the DAG. More... | |

| bool | isOrEquivalentToAdd (const SDNode *N) const |

Public Member Functions inherited from llvm::MachineFunctionPass Public Member Functions inherited from llvm::MachineFunctionPass | |

| bool | doInitialization (Module &) override |

| doInitialization - Virtual method overridden by subclasses to do any necessary initialization before any pass is run. More... | |

Public Member Functions inherited from llvm::FunctionPass Public Member Functions inherited from llvm::FunctionPass | |

| FunctionPass (char &pid) | |

| Pass * | createPrinterPass (raw_ostream &OS, const std::string &Banner) const override |

| createPrinterPass - Get a function printer pass. More... | |

| void | assignPassManager (PMStack &PMS, PassManagerType T) override |

| Find appropriate Function Pass Manager or Call Graph Pass Manager in the PM Stack and add self into that manager. More... | |

| PassManagerType | getPotentialPassManagerType () const override |

| Return what kind of Pass Manager can manage this pass. More... | |

Public Member Functions inherited from llvm::Pass Public Member Functions inherited from llvm::Pass | |

| Pass (PassKind K, char &pid) | |

| Pass (const Pass &)=delete | |

| Pass & | operator= (const Pass &)=delete |

| virtual | ~Pass () |

| PassKind | getPassKind () const |

| AnalysisID | getPassID () const |

| getPassID - Return the PassID number that corresponds to this pass. More... | |

| virtual bool | doFinalization (Module &) |

| doFinalization - Virtual method overriden by subclasses to do any necessary clean up after all passes have run. More... | |

| virtual void | print (raw_ostream &OS, const Module *M) const |

| print - Print out the internal state of the pass. More... | |

| void | dump () const |

| virtual void | preparePassManager (PMStack &) |

| Check if available pass managers are suitable for this pass or not. More... | |

| void | setResolver (AnalysisResolver *AR) |

| AnalysisResolver * | getResolver () const |

| virtual void | releaseMemory () |

| releaseMemory() - This member can be implemented by a pass if it wants to be able to release its memory when it is no longer needed. More... | |

| virtual void * | getAdjustedAnalysisPointer (AnalysisID ID) |

| getAdjustedAnalysisPointer - This method is used when a pass implements an analysis interface through multiple inheritance. More... | |

| virtual ImmutablePass * | getAsImmutablePass () |

| virtual PMDataManager * | getAsPMDataManager () |

| virtual void | verifyAnalysis () const |

| verifyAnalysis() - This member can be implemented by a analysis pass to check state of analysis information. More... | |

| virtual void | dumpPassStructure (unsigned Offset=0) |

| template<typename AnalysisType > | |

| AnalysisType * | getAnalysisIfAvailable () const |

| getAnalysisIfAvailable<AnalysisType>() - Subclasses use this function to get analysis information that might be around, for example to update it. More... | |

| bool | mustPreserveAnalysisID (char &AID) const |

| mustPreserveAnalysisID - This method serves the same function as getAnalysisIfAvailable, but works if you just have an AnalysisID. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis () const |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis (Function &F) |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI) const |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI, Function &F) |

Public Attributes | |

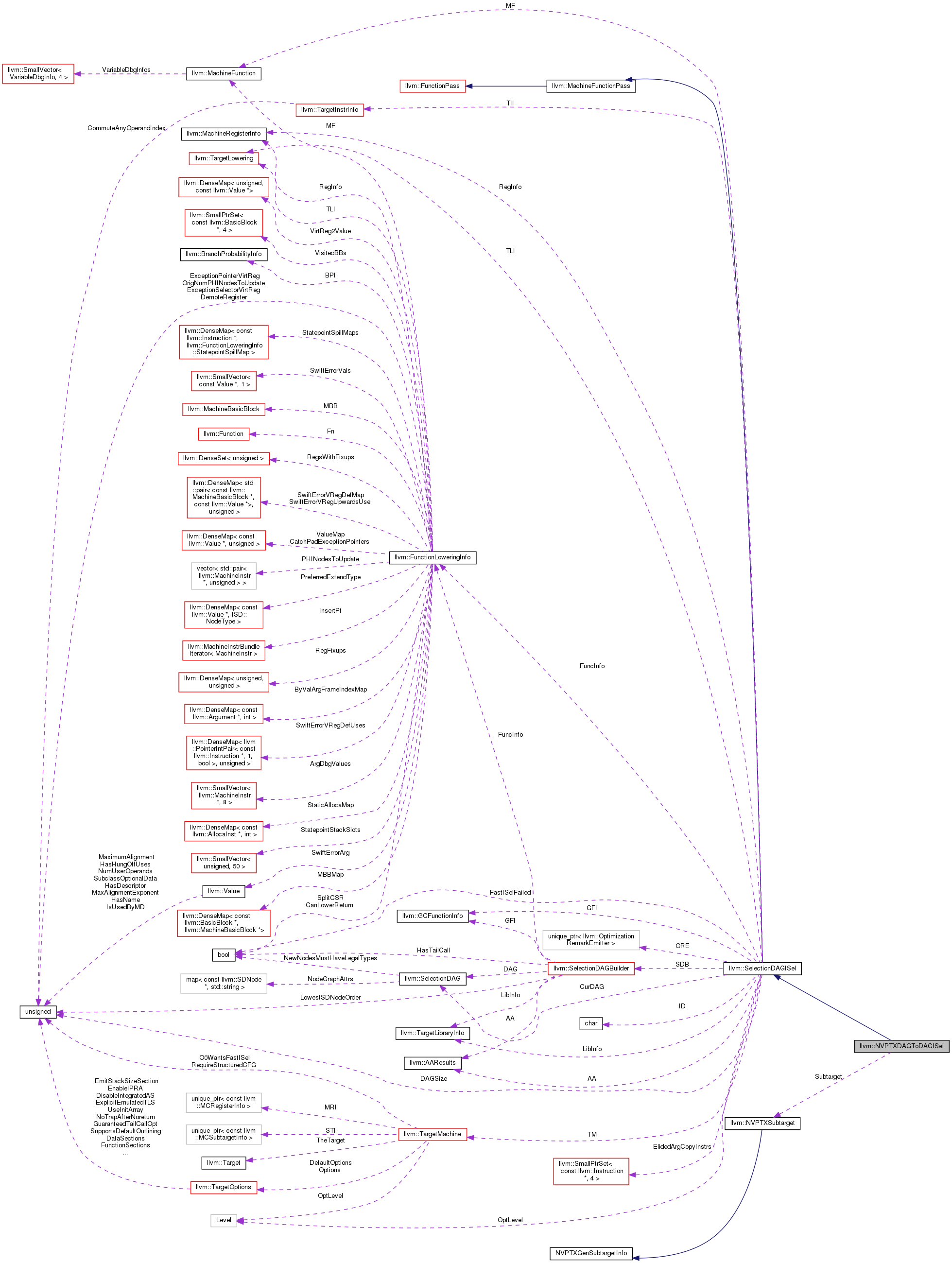

| const NVPTXSubtarget * | Subtarget |

Public Attributes inherited from llvm::SelectionDAGISel Public Attributes inherited from llvm::SelectionDAGISel | |

| TargetMachine & | TM |

| const TargetLibraryInfo * | LibInfo |

| FunctionLoweringInfo * | FuncInfo |

| MachineFunction * | MF |

| MachineRegisterInfo * | RegInfo |

| SelectionDAG * | CurDAG |

| SelectionDAGBuilder * | SDB |

| AliasAnalysis * | AA |

| GCFunctionInfo * | GFI |

| CodeGenOpt::Level | OptLevel |

| const TargetInstrInfo * | TII |

| const TargetLowering * | TLI |

| bool | FastISelFailed |

| SmallPtrSet< const Instruction *, 4 > | ElidedArgCopyInstrs |

| std::unique_ptr< OptimizationRemarkEmitter > | ORE |

| Current optimization remark emitter. More... | |

Detailed Description

Definition at line 27 of file NVPTXISelDAGToDAG.h.

Constructor & Destructor Documentation

◆ NVPTXDAGToDAGISel()

|

explicit |

Definition at line 37 of file NVPTXISelDAGToDAG.cpp.

Member Function Documentation

◆ getPassName()

|

inlineoverridevirtual |

getPassName - Return a nice clean name for a pass.

This usually implemented in terms of the name that is registered by one of the Registration templates, but can be overloaded directly.

Reimplemented from llvm::Pass.

Definition at line 45 of file NVPTXISelDAGToDAG.h.

◆ runOnMachineFunction()

|

overridevirtual |

runOnMachineFunction - This method must be overloaded to perform the desired machine code transformation or analysis.

Reimplemented from llvm::SelectionDAGISel.

Definition at line 43 of file NVPTXISelDAGToDAG.cpp.

References llvm::ISD::ADDRSPACECAST, llvm::NVPTXTargetLowering::allowFMA(), llvm::NVPTXTargetLowering::allowUnsafeFPMath(), llvm::ISD::AND, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, llvm::ISD::ConstantFP, llvm::SelectionDAGISel::CurDAG, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MVT::f16, llvm::NVPTXTargetLowering::getDivF32Level(), llvm::SelectionDAG::getMachineNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::MachineFunction::getSubtarget(), llvm::SelectionDAG::getTargetConstantFP(), llvm::NVPTXSubtarget::getTargetLowering(), llvm::SDNode::getValueType(), llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::SDNode::isMachineOpcode(), llvm::NVPTXISD::LDGV2, llvm::NVPTXISD::LDGV4, llvm::NVPTXISD::LDUV2, llvm::NVPTXISD::LDUV4, llvm::ISD::LOAD, llvm::NVPTXISD::LoadParam, llvm::NVPTXISD::LoadParamV2, llvm::NVPTXISD::LoadParamV4, llvm::NVPTXISD::LoadV2, llvm::NVPTXISD::LoadV4, llvm::SelectionDAGISel::MF, N, llvm::Intrinsic::nvvm_ldg_global_f, llvm::Intrinsic::nvvm_ldg_global_i, llvm::Intrinsic::nvvm_ldg_global_p, llvm::Intrinsic::nvvm_ldu_global_f, llvm::Intrinsic::nvvm_ldu_global_i, llvm::Intrinsic::nvvm_ldu_global_p, llvm::SelectionDAGISel::OptLevel, llvm::SelectionDAGISel::ReplaceNode(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::SDNode::setNodeId(), llvm::NVPTXISD::SETP_F16X2, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::STORE, llvm::NVPTXISD::StoreParam, llvm::NVPTXISD::StoreParamS32, llvm::NVPTXISD::StoreParamU32, llvm::NVPTXISD::StoreParamV2, llvm::NVPTXISD::StoreParamV4, llvm::NVPTXISD::StoreRetval, llvm::NVPTXISD::StoreRetvalV2, llvm::NVPTXISD::StoreRetvalV4, llvm::NVPTXISD::StoreV2, llvm::NVPTXISD::StoreV4, Subtarget, llvm::NVPTXISD::Suld1DArrayI16Clamp, llvm::NVPTXISD::Suld1DArrayI16Trap, llvm::NVPTXISD::Suld1DArrayI16Zero, llvm::NVPTXISD::Suld1DArrayI32Clamp, llvm::NVPTXISD::Suld1DArrayI32Trap, llvm::NVPTXISD::Suld1DArrayI32Zero, llvm::NVPTXISD::Suld1DArrayI64Clamp, llvm::NVPTXISD::Suld1DArrayI64Trap, llvm::NVPTXISD::Suld1DArrayI64Zero, llvm::NVPTXISD::Suld1DArrayI8Clamp, llvm::NVPTXISD::Suld1DArrayI8Trap, llvm::NVPTXISD::Suld1DArrayI8Zero, llvm::NVPTXISD::Suld1DArrayV2I16Clamp, llvm::NVPTXISD::Suld1DArrayV2I16Trap, llvm::NVPTXISD::Suld1DArrayV2I16Zero, llvm::NVPTXISD::Suld1DArrayV2I32Clamp, llvm::NVPTXISD::Suld1DArrayV2I32Trap, llvm::NVPTXISD::Suld1DArrayV2I32Zero, llvm::NVPTXISD::Suld1DArrayV2I64Clamp, llvm::NVPTXISD::Suld1DArrayV2I64Trap, llvm::NVPTXISD::Suld1DArrayV2I64Zero, llvm::NVPTXISD::Suld1DArrayV2I8Clamp, llvm::NVPTXISD::Suld1DArrayV2I8Trap, llvm::NVPTXISD::Suld1DArrayV2I8Zero, llvm::NVPTXISD::Suld1DArrayV4I16Clamp, llvm::NVPTXISD::Suld1DArrayV4I16Trap, llvm::NVPTXISD::Suld1DArrayV4I16Zero, llvm::NVPTXISD::Suld1DArrayV4I32Clamp, llvm::NVPTXISD::Suld1DArrayV4I32Trap, llvm::NVPTXISD::Suld1DArrayV4I32Zero, llvm::NVPTXISD::Suld1DArrayV4I8Clamp, llvm::NVPTXISD::Suld1DArrayV4I8Trap, llvm::NVPTXISD::Suld1DArrayV4I8Zero, llvm::NVPTXISD::Suld1DI16Clamp, llvm::NVPTXISD::Suld1DI16Trap, llvm::NVPTXISD::Suld1DI16Zero, llvm::NVPTXISD::Suld1DI32Clamp, llvm::NVPTXISD::Suld1DI32Trap, llvm::NVPTXISD::Suld1DI32Zero, llvm::NVPTXISD::Suld1DI64Clamp, llvm::NVPTXISD::Suld1DI64Trap, llvm::NVPTXISD::Suld1DI64Zero, llvm::NVPTXISD::Suld1DI8Clamp, llvm::NVPTXISD::Suld1DI8Trap, llvm::NVPTXISD::Suld1DI8Zero, llvm::NVPTXISD::Suld1DV2I16Clamp, llvm::NVPTXISD::Suld1DV2I16Trap, llvm::NVPTXISD::Suld1DV2I16Zero, llvm::NVPTXISD::Suld1DV2I32Clamp, llvm::NVPTXISD::Suld1DV2I32Trap, llvm::NVPTXISD::Suld1DV2I32Zero, llvm::NVPTXISD::Suld1DV2I64Clamp, llvm::NVPTXISD::Suld1DV2I64Trap, llvm::NVPTXISD::Suld1DV2I64Zero, llvm::NVPTXISD::Suld1DV2I8Clamp, llvm::NVPTXISD::Suld1DV2I8Trap, llvm::NVPTXISD::Suld1DV2I8Zero, llvm::NVPTXISD::Suld1DV4I16Clamp, llvm::NVPTXISD::Suld1DV4I16Trap, llvm::NVPTXISD::Suld1DV4I16Zero, llvm::NVPTXISD::Suld1DV4I32Clamp, llvm::NVPTXISD::Suld1DV4I32Trap, llvm::NVPTXISD::Suld1DV4I32Zero, llvm::NVPTXISD::Suld1DV4I8Clamp, llvm::NVPTXISD::Suld1DV4I8Trap, llvm::NVPTXISD::Suld1DV4I8Zero, llvm::NVPTXISD::Suld2DArrayI16Clamp, llvm::NVPTXISD::Suld2DArrayI16Trap, llvm::NVPTXISD::Suld2DArrayI16Zero, llvm::NVPTXISD::Suld2DArrayI32Clamp, llvm::NVPTXISD::Suld2DArrayI32Trap, llvm::NVPTXISD::Suld2DArrayI32Zero, llvm::NVPTXISD::Suld2DArrayI64Clamp, llvm::NVPTXISD::Suld2DArrayI64Trap, llvm::NVPTXISD::Suld2DArrayI64Zero, llvm::NVPTXISD::Suld2DArrayI8Clamp, llvm::NVPTXISD::Suld2DArrayI8Trap, llvm::NVPTXISD::Suld2DArrayI8Zero, llvm::NVPTXISD::Suld2DArrayV2I16Clamp, llvm::NVPTXISD::Suld2DArrayV2I16Trap, llvm::NVPTXISD::Suld2DArrayV2I16Zero, llvm::NVPTXISD::Suld2DArrayV2I32Clamp, llvm::NVPTXISD::Suld2DArrayV2I32Trap, llvm::NVPTXISD::Suld2DArrayV2I32Zero, llvm::NVPTXISD::Suld2DArrayV2I64Clamp, llvm::NVPTXISD::Suld2DArrayV2I64Trap, llvm::NVPTXISD::Suld2DArrayV2I64Zero, llvm::NVPTXISD::Suld2DArrayV2I8Clamp, llvm::NVPTXISD::Suld2DArrayV2I8Trap, llvm::NVPTXISD::Suld2DArrayV2I8Zero, llvm::NVPTXISD::Suld2DArrayV4I16Clamp, llvm::NVPTXISD::Suld2DArrayV4I16Trap, llvm::NVPTXISD::Suld2DArrayV4I16Zero, llvm::NVPTXISD::Suld2DArrayV4I32Clamp, llvm::NVPTXISD::Suld2DArrayV4I32Trap, llvm::NVPTXISD::Suld2DArrayV4I32Zero, llvm::NVPTXISD::Suld2DArrayV4I8Clamp, llvm::NVPTXISD::Suld2DArrayV4I8Trap, llvm::NVPTXISD::Suld2DArrayV4I8Zero, llvm::NVPTXISD::Suld2DI16Clamp, llvm::NVPTXISD::Suld2DI16Trap, llvm::NVPTXISD::Suld2DI16Zero, llvm::NVPTXISD::Suld2DI32Clamp, llvm::NVPTXISD::Suld2DI32Trap, llvm::NVPTXISD::Suld2DI32Zero, llvm::NVPTXISD::Suld2DI64Clamp, llvm::NVPTXISD::Suld2DI64Trap, llvm::NVPTXISD::Suld2DI64Zero, llvm::NVPTXISD::Suld2DI8Clamp, llvm::NVPTXISD::Suld2DI8Trap, llvm::NVPTXISD::Suld2DI8Zero, llvm::NVPTXISD::Suld2DV2I16Clamp, llvm::NVPTXISD::Suld2DV2I16Trap, llvm::NVPTXISD::Suld2DV2I16Zero, llvm::NVPTXISD::Suld2DV2I32Clamp, llvm::NVPTXISD::Suld2DV2I32Trap, llvm::NVPTXISD::Suld2DV2I32Zero, llvm::NVPTXISD::Suld2DV2I64Clamp, llvm::NVPTXISD::Suld2DV2I64Trap, llvm::NVPTXISD::Suld2DV2I64Zero, llvm::NVPTXISD::Suld2DV2I8Clamp, llvm::NVPTXISD::Suld2DV2I8Trap, llvm::NVPTXISD::Suld2DV2I8Zero, llvm::NVPTXISD::Suld2DV4I16Clamp, llvm::NVPTXISD::Suld2DV4I16Trap, llvm::NVPTXISD::Suld2DV4I16Zero, llvm::NVPTXISD::Suld2DV4I32Clamp, llvm::NVPTXISD::Suld2DV4I32Trap, llvm::NVPTXISD::Suld2DV4I32Zero, llvm::NVPTXISD::Suld2DV4I8Clamp, llvm::NVPTXISD::Suld2DV4I8Trap, llvm::NVPTXISD::Suld2DV4I8Zero, llvm::NVPTXISD::Suld3DI16Clamp, llvm::NVPTXISD::Suld3DI16Trap, llvm::NVPTXISD::Suld3DI16Zero, llvm::NVPTXISD::Suld3DI32Clamp, llvm::NVPTXISD::Suld3DI32Trap, llvm::NVPTXISD::Suld3DI32Zero, llvm::NVPTXISD::Suld3DI64Clamp, llvm::NVPTXISD::Suld3DI64Trap, llvm::NVPTXISD::Suld3DI64Zero, llvm::NVPTXISD::Suld3DI8Clamp, llvm::NVPTXISD::Suld3DI8Trap, llvm::NVPTXISD::Suld3DI8Zero, llvm::NVPTXISD::Suld3DV2I16Clamp, llvm::NVPTXISD::Suld3DV2I16Trap, llvm::NVPTXISD::Suld3DV2I16Zero, llvm::NVPTXISD::Suld3DV2I32Clamp, llvm::NVPTXISD::Suld3DV2I32Trap, llvm::NVPTXISD::Suld3DV2I32Zero, llvm::NVPTXISD::Suld3DV2I64Clamp, llvm::NVPTXISD::Suld3DV2I64Trap, llvm::NVPTXISD::Suld3DV2I64Zero, llvm::NVPTXISD::Suld3DV2I8Clamp, llvm::NVPTXISD::Suld3DV2I8Trap, llvm::NVPTXISD::Suld3DV2I8Zero, llvm::NVPTXISD::Suld3DV4I16Clamp, llvm::NVPTXISD::Suld3DV4I16Trap, llvm::NVPTXISD::Suld3DV4I16Zero, llvm::NVPTXISD::Suld3DV4I32Clamp, llvm::NVPTXISD::Suld3DV4I32Trap, llvm::NVPTXISD::Suld3DV4I32Zero, llvm::NVPTXISD::Suld3DV4I8Clamp, llvm::NVPTXISD::Suld3DV4I8Trap, llvm::NVPTXISD::Suld3DV4I8Zero, llvm::NVPTXISD::Tex1DArrayFloatFloat, llvm::NVPTXISD::Tex1DArrayFloatFloatGrad, llvm::NVPTXISD::Tex1DArrayFloatFloatLevel, llvm::NVPTXISD::Tex1DArrayFloatS32, llvm::NVPTXISD::Tex1DArrayS32Float, llvm::NVPTXISD::Tex1DArrayS32FloatGrad, llvm::NVPTXISD::Tex1DArrayS32FloatLevel, llvm::NVPTXISD::Tex1DArrayS32S32, llvm::NVPTXISD::Tex1DArrayU32Float, llvm::NVPTXISD::Tex1DArrayU32FloatGrad, llvm::NVPTXISD::Tex1DArrayU32FloatLevel, llvm::NVPTXISD::Tex1DArrayU32S32, llvm::NVPTXISD::Tex1DFloatFloat, llvm::NVPTXISD::Tex1DFloatFloatGrad, llvm::NVPTXISD::Tex1DFloatFloatLevel, llvm::NVPTXISD::Tex1DFloatS32, llvm::NVPTXISD::Tex1DS32Float, llvm::NVPTXISD::Tex1DS32FloatGrad, llvm::NVPTXISD::Tex1DS32FloatLevel, llvm::NVPTXISD::Tex1DS32S32, llvm::NVPTXISD::Tex1DU32Float, llvm::NVPTXISD::Tex1DU32FloatGrad, llvm::NVPTXISD::Tex1DU32FloatLevel, llvm::NVPTXISD::Tex1DU32S32, llvm::NVPTXISD::Tex2DArrayFloatFloat, llvm::NVPTXISD::Tex2DArrayFloatFloatGrad, llvm::NVPTXISD::Tex2DArrayFloatFloatLevel, llvm::NVPTXISD::Tex2DArrayFloatS32, llvm::NVPTXISD::Tex2DArrayS32Float, llvm::NVPTXISD::Tex2DArrayS32FloatGrad, llvm::NVPTXISD::Tex2DArrayS32FloatLevel, llvm::NVPTXISD::Tex2DArrayS32S32, llvm::NVPTXISD::Tex2DArrayU32Float, llvm::NVPTXISD::Tex2DArrayU32FloatGrad, llvm::NVPTXISD::Tex2DArrayU32FloatLevel, llvm::NVPTXISD::Tex2DArrayU32S32, llvm::NVPTXISD::Tex2DFloatFloat, llvm::NVPTXISD::Tex2DFloatFloatGrad, llvm::NVPTXISD::Tex2DFloatFloatLevel, llvm::NVPTXISD::Tex2DFloatS32, llvm::NVPTXISD::Tex2DS32Float, llvm::NVPTXISD::Tex2DS32FloatGrad, llvm::NVPTXISD::Tex2DS32FloatLevel, llvm::NVPTXISD::Tex2DS32S32, llvm::NVPTXISD::Tex2DU32Float, llvm::NVPTXISD::Tex2DU32FloatGrad, llvm::NVPTXISD::Tex2DU32FloatLevel, llvm::NVPTXISD::Tex2DU32S32, llvm::NVPTXISD::Tex3DFloatFloat, llvm::NVPTXISD::Tex3DFloatFloatGrad, llvm::NVPTXISD::Tex3DFloatFloatLevel, llvm::NVPTXISD::Tex3DFloatS32, llvm::NVPTXISD::Tex3DS32Float, llvm::NVPTXISD::Tex3DS32FloatGrad, llvm::NVPTXISD::Tex3DS32FloatLevel, llvm::NVPTXISD::Tex3DS32S32, llvm::NVPTXISD::Tex3DU32Float, llvm::NVPTXISD::Tex3DU32FloatGrad, llvm::NVPTXISD::Tex3DU32FloatLevel, llvm::NVPTXISD::Tex3DU32S32, llvm::NVPTXISD::TexCubeArrayFloatFloat, llvm::NVPTXISD::TexCubeArrayFloatFloatLevel, llvm::NVPTXISD::TexCubeArrayS32Float, llvm::NVPTXISD::TexCubeArrayS32FloatLevel, llvm::NVPTXISD::TexCubeArrayU32Float, llvm::NVPTXISD::TexCubeArrayU32FloatLevel, llvm::NVPTXISD::TexCubeFloatFloat, llvm::NVPTXISD::TexCubeFloatFloatLevel, llvm::NVPTXISD::TexCubeS32Float, llvm::NVPTXISD::TexCubeS32FloatLevel, llvm::NVPTXISD::TexCubeU32Float, llvm::NVPTXISD::TexCubeU32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayFloatFloat, llvm::NVPTXISD::TexUnified1DArrayFloatFloatGrad, llvm::NVPTXISD::TexUnified1DArrayFloatFloatLevel, llvm::NVPTXISD::TexUnified1DArrayFloatS32, llvm::NVPTXISD::TexUnified1DArrayS32Float, llvm::NVPTXISD::TexUnified1DArrayS32FloatGrad, llvm::NVPTXISD::TexUnified1DArrayS32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayS32S32, llvm::NVPTXISD::TexUnified1DArrayU32Float, llvm::NVPTXISD::TexUnified1DArrayU32FloatGrad, llvm::NVPTXISD::TexUnified1DArrayU32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayU32S32, llvm::NVPTXISD::TexUnified1DFloatFloat, llvm::NVPTXISD::TexUnified1DFloatFloatGrad, llvm::NVPTXISD::TexUnified1DFloatFloatLevel, llvm::NVPTXISD::TexUnified1DFloatS32, llvm::NVPTXISD::TexUnified1DS32Float, llvm::NVPTXISD::TexUnified1DS32FloatGrad, llvm::NVPTXISD::TexUnified1DS32FloatLevel, llvm::NVPTXISD::TexUnified1DS32S32, llvm::NVPTXISD::TexUnified1DU32Float, llvm::NVPTXISD::TexUnified1DU32FloatGrad, llvm::NVPTXISD::TexUnified1DU32FloatLevel, llvm::NVPTXISD::TexUnified1DU32S32, llvm::NVPTXISD::TexUnified2DArrayFloatFloat, llvm::NVPTXISD::TexUnified2DArrayFloatFloatGrad, llvm::NVPTXISD::TexUnified2DArrayFloatFloatLevel, llvm::NVPTXISD::TexUnified2DArrayFloatS32, llvm::NVPTXISD::TexUnified2DArrayS32Float, llvm::NVPTXISD::TexUnified2DArrayS32FloatGrad, llvm::NVPTXISD::TexUnified2DArrayS32FloatLevel, llvm::NVPTXISD::TexUnified2DArrayS32S32, llvm::NVPTXISD::TexUnified2DArrayU32Float, llvm::NVPTXISD::TexUnified2DArrayU32FloatGrad, llvm::NVPTXISD::TexUnified2DArrayU32FloatLevel, llvm::NVPTXISD::TexUnified2DArrayU32S32, llvm::NVPTXISD::TexUnified2DFloatFloat, llvm::NVPTXISD::TexUnified2DFloatFloatGrad, llvm::NVPTXISD::TexUnified2DFloatFloatLevel, llvm::NVPTXISD::TexUnified2DFloatS32, llvm::NVPTXISD::TexUnified2DS32Float, llvm::NVPTXISD::TexUnified2DS32FloatGrad, llvm::NVPTXISD::TexUnified2DS32FloatLevel, llvm::NVPTXISD::TexUnified2DS32S32, llvm::NVPTXISD::TexUnified2DU32Float, llvm::NVPTXISD::TexUnified2DU32FloatGrad, llvm::NVPTXISD::TexUnified2DU32FloatLevel, llvm::NVPTXISD::TexUnified2DU32S32, llvm::NVPTXISD::TexUnified3DFloatFloat, llvm::NVPTXISD::TexUnified3DFloatFloatGrad, llvm::NVPTXISD::TexUnified3DFloatFloatLevel, llvm::NVPTXISD::TexUnified3DFloatS32, llvm::NVPTXISD::TexUnified3DS32Float, llvm::NVPTXISD::TexUnified3DS32FloatGrad, llvm::NVPTXISD::TexUnified3DS32FloatLevel, llvm::NVPTXISD::TexUnified3DS32S32, llvm::NVPTXISD::TexUnified3DU32Float, llvm::NVPTXISD::TexUnified3DU32FloatGrad, llvm::NVPTXISD::TexUnified3DU32FloatLevel, llvm::NVPTXISD::TexUnified3DU32S32, llvm::NVPTXISD::TexUnifiedCubeArrayFloatFloat, llvm::NVPTXISD::TexUnifiedCubeArrayFloatFloatLevel, llvm::NVPTXISD::TexUnifiedCubeArrayS32Float, llvm::NVPTXISD::TexUnifiedCubeArrayS32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeArrayU32Float, llvm::NVPTXISD::TexUnifiedCubeArrayU32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeFloatFloat, llvm::NVPTXISD::TexUnifiedCubeFloatFloatLevel, llvm::NVPTXISD::TexUnifiedCubeS32Float, llvm::NVPTXISD::TexUnifiedCubeS32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeU32Float, llvm::NVPTXISD::TexUnifiedCubeU32FloatLevel, llvm::NVPTXISD::Tld4A2DFloatFloat, llvm::NVPTXISD::Tld4A2DS64Float, llvm::NVPTXISD::Tld4A2DU64Float, llvm::NVPTXISD::Tld4B2DFloatFloat, llvm::NVPTXISD::Tld4B2DS64Float, llvm::NVPTXISD::Tld4B2DU64Float, llvm::NVPTXISD::Tld4G2DFloatFloat, llvm::NVPTXISD::Tld4G2DS64Float, llvm::NVPTXISD::Tld4G2DU64Float, llvm::NVPTXISD::Tld4R2DFloatFloat, llvm::NVPTXISD::Tld4R2DS64Float, llvm::NVPTXISD::Tld4R2DU64Float, llvm::NVPTXISD::Tld4UnifiedA2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedA2DS64Float, llvm::NVPTXISD::Tld4UnifiedA2DU64Float, llvm::NVPTXISD::Tld4UnifiedB2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedB2DS64Float, llvm::NVPTXISD::Tld4UnifiedB2DU64Float, llvm::NVPTXISD::Tld4UnifiedG2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedG2DS64Float, llvm::NVPTXISD::Tld4UnifiedG2DU64Float, llvm::NVPTXISD::Tld4UnifiedR2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedR2DS64Float, llvm::NVPTXISD::Tld4UnifiedR2DU64Float, llvm::NVPTXTargetLowering::useF32FTZ(), llvm::NVPTXTargetLowering::usePrecSqrtF32(), and llvm::NVPTXTargetMachine::useShortPointers().

◆ SelectInlineAsmMemoryOperand()

|

overridevirtual |

SelectInlineAsmMemoryOperand - Implement addressing mode selection for inline asm expressions.

Reimplemented from llvm::SelectionDAGISel.

Definition at line 3691 of file NVPTXISelDAGToDAG.cpp.

References llvm::InlineAsm::Constraint_m, llvm::SelectionDAGISel::CurDAG, llvm::SDValue::getNode(), llvm::SelectionDAG::getTargetConstant(), llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, and llvm::MVT::SimpleTy.

Member Data Documentation

◆ Subtarget

| const NVPTXSubtarget* llvm::NVPTXDAGToDAGISel::Subtarget |

Definition at line 49 of file NVPTXISelDAGToDAG.h.

Referenced by pickOpcodeForVT(), and runOnMachineFunction().

The documentation for this class was generated from the following files:

- lib/Target/NVPTX/NVPTXISelDAGToDAG.h

- lib/Target/NVPTX/NVPTXISelDAGToDAG.cpp

1.8.13

1.8.13