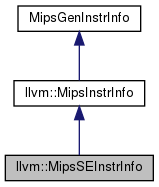

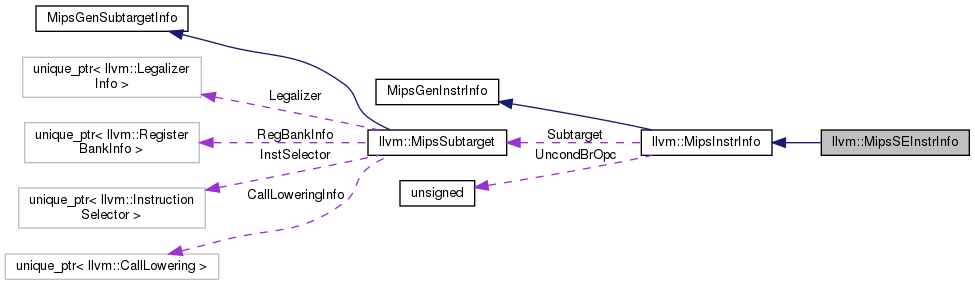

#include "Target/Mips/MipsSEInstrInfo.h"

Public Member Functions | |

| MipsSEInstrInfo (const MipsSubtarget &STI) | |

| const MipsRegisterInfo & | getRegisterInfo () const override |

| getRegisterInfo - TargetInstrInfo is a superset of MRegister info. More... | |

| unsigned | isLoadFromStackSlot (const MachineInstr &MI, int &FrameIndex) const override |

| isLoadFromStackSlot - If the specified machine instruction is a direct load from a stack slot, return the virtual or physical register number of the destination along with the FrameIndex of the loaded stack slot. More... | |

| unsigned | isStoreToStackSlot (const MachineInstr &MI, int &FrameIndex) const override |

| isStoreToStackSlot - If the specified machine instruction is a direct store to a stack slot, return the virtual or physical register number of the source reg along with the FrameIndex of the loaded stack slot. More... | |

| void | copyPhysReg (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, const DebugLoc &DL, unsigned DestReg, unsigned SrcReg, bool KillSrc) const override |

| void | storeRegToStack (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI, int64_t Offset) const override |

| void | loadRegFromStack (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI, int64_t Offset) const override |

| bool | expandPostRAPseudo (MachineInstr &MI) const override |

| unsigned | getOppositeBranchOpc (unsigned Opc) const override |

| getOppositeBranchOpc - Return the inverse of the specified opcode, e.g. More... | |

| void | adjustStackPtr (unsigned SP, int64_t Amount, MachineBasicBlock &MBB, MachineBasicBlock::iterator I) const override |

| Adjust SP by Amount bytes. More... | |

| unsigned | loadImmediate (int64_t Imm, MachineBasicBlock &MBB, MachineBasicBlock::iterator II, const DebugLoc &DL, unsigned *NewImm) const |

| Emit a series of instructions to load an immediate. More... | |

Public Member Functions inherited from llvm::MipsInstrInfo Public Member Functions inherited from llvm::MipsInstrInfo | |

| MipsInstrInfo (const MipsSubtarget &STI, unsigned UncondBrOpc) | |

| bool | analyzeBranch (MachineBasicBlock &MBB, MachineBasicBlock *&TBB, MachineBasicBlock *&FBB, SmallVectorImpl< MachineOperand > &Cond, bool AllowModify) const override |

| Branch Analysis. More... | |

| unsigned | removeBranch (MachineBasicBlock &MBB, int *BytesRemoved=nullptr) const override |

| unsigned | insertBranch (MachineBasicBlock &MBB, MachineBasicBlock *TBB, MachineBasicBlock *FBB, ArrayRef< MachineOperand > Cond, const DebugLoc &DL, int *BytesAdded=nullptr) const override |

| bool | reverseBranchCondition (SmallVectorImpl< MachineOperand > &Cond) const override |

| reverseBranchCondition - Return the inverse opcode of the specified Branch instruction. More... | |

| BranchType | analyzeBranch (MachineBasicBlock &MBB, MachineBasicBlock *&TBB, MachineBasicBlock *&FBB, SmallVectorImpl< MachineOperand > &Cond, bool AllowModify, SmallVectorImpl< MachineInstr *> &BranchInstrs) const |

| unsigned | getEquivalentCompactForm (const MachineBasicBlock::iterator I) const |

| Determine the opcode of a non-delay slot form for a branch if one exists. More... | |

| bool | isBranchOffsetInRange (unsigned BranchOpc, int64_t BrOffset) const override |

| Determine if the branch target is in range. More... | |

| bool | SafeInForbiddenSlot (const MachineInstr &MI) const |

| Predicate to determine if an instruction can go in a forbidden slot. More... | |

| bool | HasForbiddenSlot (const MachineInstr &MI) const |

| Predicate to determine if an instruction has a forbidden slot. More... | |

| void | insertNoop (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI) const override |

| Insert nop instruction when hazard condition is found. More... | |

| unsigned | getInstSizeInBytes (const MachineInstr &MI) const override |

| Return the number of bytes of code the specified instruction may be. More... | |

| void | storeRegToStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MBBI, unsigned SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| void | loadRegFromStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MBBI, unsigned DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| MachineInstrBuilder | genInstrWithNewOpc (unsigned NewOpc, MachineBasicBlock::iterator I) const |

| Create an instruction which has the same operands and memory operands as MI but has a new opcode. More... | |

| bool | findCommutedOpIndices (MachineInstr &MI, unsigned &SrcOpIdx1, unsigned &SrcOpIdx2) const override |

| bool | verifyInstruction (const MachineInstr &MI, StringRef &ErrInfo) const override |

| Perform target specific instruction verification. More... | |

| std::pair< unsigned, unsigned > | decomposeMachineOperandsTargetFlags (unsigned TF) const override |

| ArrayRef< std::pair< unsigned, const char * > > | getSerializableDirectMachineOperandTargetFlags () const override |

Protected Member Functions | |

| bool | isCopyInstrImpl (const MachineInstr &MI, const MachineOperand *&Source, const MachineOperand *&Destination) const override |

| If the specific machine instruction is a instruction that moves/copies value from one register to another register return true along with machine operand and machine operand. More... | |

Protected Member Functions inherited from llvm::MipsInstrInfo Protected Member Functions inherited from llvm::MipsInstrInfo | |

| bool | isZeroImm (const MachineOperand &op) const |

| MachineMemOperand * | GetMemOperand (MachineBasicBlock &MBB, int FI, MachineMemOperand::Flags Flags) const |

Additional Inherited Members | |

Public Types inherited from llvm::MipsInstrInfo Public Types inherited from llvm::MipsInstrInfo | |

| enum | BranchType { BT_None, BT_NoBranch, BT_Uncond, BT_Cond, BT_CondUncond, BT_Indirect } |

Static Public Member Functions inherited from llvm::MipsInstrInfo Static Public Member Functions inherited from llvm::MipsInstrInfo | |

| static const MipsInstrInfo * | create (MipsSubtarget &STI) |

Protected Attributes inherited from llvm::MipsInstrInfo Protected Attributes inherited from llvm::MipsInstrInfo | |

| const MipsSubtarget & | Subtarget |

| unsigned | UncondBrOpc |

Detailed Description

Definition at line 22 of file MipsSEInstrInfo.h.

Constructor & Destructor Documentation

◆ MipsSEInstrInfo()

|

explicit |

Definition at line 34 of file MipsSEInstrInfo.cpp.

Referenced by llvm::createMipsSEInstrInfo().

Member Function Documentation

◆ adjustStackPtr()

|

overridevirtual |

Adjust SP by Amount bytes.

Implements llvm::MipsInstrInfo.

Definition at line 581 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MipsSubtarget::getABI(), llvm::MipsABIInfo::GetPtrAddiuOp(), llvm::MipsABIInfo::GetPtrAdduOp(), llvm::MipsABIInfo::GetPtrSubuOp(), llvm::isInt< 16 >(), llvm::RegState::Kill, loadImmediate(), Reg, and llvm::MipsInstrInfo::Subtarget.

◆ copyPhysReg()

|

override |

Definition at line 84 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), contains(), llvm::RegState::Define, llvm::getKillRegState(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::MipsSubtarget::inMicroMipsMode(), llvm::MipsISD::MFHI, llvm::MipsISD::MFLO, OR, and llvm::MipsInstrInfo::Subtarget.

◆ expandPostRAPseudo()

|

override |

Definition at line 409 of file MipsSEInstrInfo.cpp.

References llvm::MipsISD::BuildPairF64, llvm::MachineBasicBlock::erase(), llvm::MipsISD::ERet, llvm::MipsISD::ExtractElementF64, llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getOpcode(), llvm::MachineInstr::getParent(), llvm::MipsSubtarget::inMicroMipsMode(), llvm::MipsISD::MFHI, llvm::MipsISD::MFLO, and llvm::MipsInstrInfo::Subtarget.

◆ getOppositeBranchOpc()

getOppositeBranchOpc - Return the inverse of the specified opcode, e.g.

turning BEQ to BNE.

Implements llvm::MipsInstrInfo.

Definition at line 494 of file MipsSEInstrInfo.cpp.

References llvm_unreachable.

◆ getRegisterInfo()

|

overridevirtual |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info.

As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Implements llvm::MipsInstrInfo.

Definition at line 37 of file MipsSEInstrInfo.cpp.

Referenced by loadImmediate().

◆ isCopyInstrImpl()

|

overrideprotected |

If the specific machine instruction is a instruction that moves/copies value from one register to another register return true along with machine operand and machine operand.

We check for the common case of 'or', as it's MIPS' preferred instruction for GPRs but we have to check the operands to ensure that is the case.

Other move instructions for MIPS are directly identifiable.

Definition at line 225 of file MipsSEInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::isImm(), llvm::MachineInstr::isMoveReg(), isORCopyInst(), isReadOrWriteToDSPReg(), and storeRegToStack().

◆ isLoadFromStackSlot()

|

override |

isLoadFromStackSlot - If the specified machine instruction is a direct load from a stack slot, return the virtual or physical register number of the destination along with the FrameIndex of the loaded stack slot.

If not, return 0. This predicate must return 0 if the instruction has any side effects other than loading from the stack slot.

Definition at line 46 of file MipsSEInstrInfo.cpp.

References llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), llvm::MipsInstrInfo::isZeroImm(), and llvm::ARM_MB::LD.

◆ isStoreToStackSlot()

|

override |

isStoreToStackSlot - If the specified machine instruction is a direct store to a stack slot, return the virtual or physical register number of the source reg along with the FrameIndex of the loaded stack slot.

If not, return 0. This predicate must return 0 if the instruction has any side effects other than storing to the stack slot.

Definition at line 68 of file MipsSEInstrInfo.cpp.

References llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MipsInstrInfo::isZeroImm().

◆ loadImmediate()

| unsigned MipsSEInstrInfo::loadImmediate | ( | int64_t | Imm, |

| MachineBasicBlock & | MBB, | ||

| MachineBasicBlock::iterator | II, | ||

| const DebugLoc & | DL, | ||

| unsigned * | NewImm | ||

| ) | const |

Emit a series of instructions to load an immediate.

This function generates the sequence of instructions needed to get the result of adding register REG and immediate IMM.

If NewImm is a non-NULL parameter, the last instruction is not emitted, but instead its immediate operand is returned in NewImm.

Definition at line 609 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MipsAnalyzeImmediate::Analyze(), assert(), B, llvm::SmallVectorTemplateCommon< T, typename >::begin(), llvm::BuildMI(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::RegState::Define, llvm::SmallVectorTemplateCommon< T, typename >::end(), llvm::MipsSubtarget::getABI(), llvm::getKillRegState(), llvm::MachineBasicBlock::getParent(), llvm::MipsABIInfo::GetPtrAdduOp(), llvm::MachineOperand::getReg(), getRegClass(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), llvm::MCRegisterInfo::getSubReg(), llvm::MachineFunction::getTarget(), llvm::MipsSubtarget::hasMips32r2(), llvm::MipsSubtarget::hasMTHC1(), I, llvm::MipsSubtarget::isABI_FPXX(), llvm::MipsSubtarget::isABI_N64(), llvm::MipsSubtarget::isFP64bit(), llvm::MipsSubtarget::isGP64bit(), llvm::MachineOperand::isKill(), llvm::TargetMachine::isPositionIndependent(), llvm::RegState::Kill, llvm_unreachable, N, llvm::MCInstrDesc::NumOperands, RA, Reg, Size, llvm::SmallVectorBase::size(), SubReg, llvm::MipsInstrInfo::Subtarget, llvm::SystemZISD::TM, TRI, llvm::RegState::Undef, and llvm::MipsSubtarget::useOddSPReg().

Referenced by adjustStackPtr(), and getLoadStoreOffsetAlign().

◆ loadRegFromStack()

|

overridevirtual |

Implements llvm::MipsInstrInfo.

Definition at line 325 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::MipsABIInfo::ArePtrs64bit(), assert(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::MipsSubtarget::getABI(), llvm::MachineFunction::getFunction(), llvm::MipsInstrInfo::GetMemOperand(), llvm::MachineBasicBlock::getParent(), llvm::Function::hasFnAttribute(), llvm::TargetRegisterInfo::isTypeLegalForClass(), llvm::ARM_MB::LD, llvm::MachineMemOperand::MOLoad, Reg, llvm::MipsInstrInfo::Subtarget, llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8f16, and llvm::MVT::v8i16.

Referenced by storeRegToStack().

◆ storeRegToStack()

|

overridevirtual |

Implements llvm::MipsInstrInfo.

Definition at line 251 of file MipsSEInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), llvm::MachineFunction::getFunction(), llvm::getKillRegState(), llvm::MipsInstrInfo::GetMemOperand(), llvm::MachineBasicBlock::getParent(), llvm::Function::hasFnAttribute(), llvm::TargetRegisterInfo::isTypeLegalForClass(), loadRegFromStack(), llvm::MipsISD::MFHI, llvm::MipsISD::MFLO, llvm::MachineMemOperand::MOStore, llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8f16, and llvm::MVT::v8i16.

Referenced by isCopyInstrImpl().

The documentation for this class was generated from the following files:

- lib/Target/Mips/MipsSEInstrInfo.h

- lib/Target/Mips/MipsSEInstrInfo.cpp

1.8.13

1.8.13