#include "Target/Mips/MipsInstrInfo.h"

Public Types | |

| enum | BranchType { BT_None, BT_NoBranch, BT_Uncond, BT_Cond, BT_CondUncond, BT_Indirect } |

Static Public Member Functions | |

| static const MipsInstrInfo * | create (MipsSubtarget &STI) |

Protected Member Functions | |

| bool | isZeroImm (const MachineOperand &op) const |

| MachineMemOperand * | GetMemOperand (MachineBasicBlock &MBB, int FI, MachineMemOperand::Flags Flags) const |

Protected Attributes | |

| const MipsSubtarget & | Subtarget |

| unsigned | UncondBrOpc |

Detailed Description

Definition at line 42 of file MipsInstrInfo.h.

Member Enumeration Documentation

◆ BranchType

| Enumerator | |

|---|---|

| BT_None | |

| BT_NoBranch | |

| BT_Uncond | |

| BT_Cond | |

| BT_CondUncond | |

| BT_Indirect | |

Definition at line 50 of file MipsInstrInfo.h.

Constructor & Destructor Documentation

◆ MipsInstrInfo()

|

explicit |

Definition at line 40 of file MipsInstrInfo.cpp.

Member Function Documentation

◆ adjustStackPtr()

|

pure virtual |

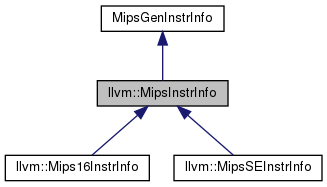

Implemented in llvm::Mips16InstrInfo, and llvm::MipsSEInstrInfo.

Referenced by llvm::MipsFrameLowering::eliminateCallFramePseudoInstr(), and loadRegFromStackSlot().

◆ analyzeBranch() [1/2]

|

override |

Branch Analysis.

Definition at line 95 of file MipsInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addMBB(), assert(), BT_Indirect, BT_None, llvm::BuildMI(), isReg(), and llvm::ArrayRef< T >::size().

◆ analyzeBranch() [2/2]

| MipsInstrInfo::BranchType MipsInstrInfo::analyzeBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock *& | TBB, | ||

| MachineBasicBlock *& | FBB, | ||

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| bool | AllowModify, | ||

| SmallVectorImpl< MachineInstr *> & | BranchInstrs | ||

| ) | const |

Definition at line 191 of file MipsInstrInfo.cpp.

References llvm::SmallVectorTemplateCommon< T, typename >::begin(), BT_Cond, BT_CondUncond, BT_Indirect, BT_NoBranch, BT_None, BT_Uncond, llvm::MachineInstr::eraseFromParent(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), I, llvm::SmallVectorImpl< T >::insert(), llvm::MachineInstr::isIndirectBranch(), llvm::MachineInstr::isUnconditionalBranch(), llvm::SmallVectorTemplateBase< T, bool >::pop_back(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::MachineBasicBlock::rbegin(), and llvm::MachineBasicBlock::rend().

◆ create()

|

static |

Definition at line 44 of file MipsInstrInfo.cpp.

References llvm::createMips16InstrInfo(), llvm::createMipsSEInstrInfo(), and llvm::MipsSubtarget::inMips16Mode().

◆ decomposeMachineOperandsTargetFlags()

|

override |

Definition at line 807 of file MipsInstrInfo.cpp.

Referenced by loadRegFromStackSlot().

◆ findCommutedOpIndices()

|

override |

Definition at line 680 of file MipsInstrInfo.cpp.

References assert(), llvm::TargetInstrInfo::findCommutedOpIndices(), llvm::MachineInstr::getDesc(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::isBundle(), and llvm::MachineOperand::isReg().

Referenced by loadRegFromStackSlot().

◆ genInstrWithNewOpc()

| MachineInstrBuilder MipsInstrInfo::genInstrWithNewOpc | ( | unsigned | NewOpc, |

| MachineBasicBlock::iterator | I | ||

| ) | const |

Create an instruction which has the same operands and memory operands as MI but has a new opcode.

Definition at line 594 of file MipsInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addSym(), llvm::BuildMI(), llvm::MachineInstrBuilder::cloneMemRefs(), llvm::MachineInstrBuilder::copyImplicitOps(), E, llvm::MachineOperand::getMCSymbol(), llvm::MachineOperand::getTargetFlags(), I, llvm::MachineOperand::isMCSymbol(), llvm::MipsII::MO_JALR, llvm::MachineInstr::RemoveOperand(), and TRI.

Referenced by loadRegFromStackSlot().

◆ getEquivalentCompactForm()

| unsigned MipsInstrInfo::getEquivalentCompactForm | ( | const MachineBasicBlock::iterator | I | ) | const |

Determine the opcode of a non-delay slot form for a branch if one exists.

Return the corresponding compact (no delay slot) form of a branch.

Definition at line 439 of file MipsInstrInfo.cpp.

References B, llvm::MipsSubtarget::getABI(), llvm::MipsABIInfo::GetZeroReg(), llvm::MipsSubtarget::hasMips32r6(), llvm::MipsSubtarget::inMicroMipsMode(), and Subtarget.

Referenced by getEquivalentCallShort().

◆ getInstSizeInBytes()

|

override |

Return the number of bytes of code the specified instruction may be.

Definition at line 577 of file MipsInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::TargetMachine::getMCAsmInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MCInstrDesc::getSize(), llvm::MachineOperand::getSymbolName(), llvm::MachineFunction::getTarget(), and llvm::ISD::INLINEASM.

Referenced by getEquivalentCallShort().

◆ GetMemOperand()

|

protected |

Definition at line 66 of file MipsInstrInfo.cpp.

References llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, assert(), llvm::MachineOperand::CreateImm(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getNumExplicitOperands(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), and llvm::SmallVectorTemplateBase< T >::push_back().

Referenced by llvm::MipsSEInstrInfo::loadRegFromStack(), llvm::Mips16InstrInfo::loadRegFromStack(), loadRegFromStackSlot(), llvm::MipsSEInstrInfo::storeRegToStack(), and llvm::Mips16InstrInfo::storeRegToStack().

◆ getOppositeBranchOpc()

Implemented in llvm::Mips16InstrInfo, and llvm::MipsSEInstrInfo.

Referenced by reverseBranchCondition().

◆ getRegisterInfo()

|

pure virtual |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info.

As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Implemented in llvm::Mips16InstrInfo, and llvm::MipsSEInstrInfo.

◆ getSerializableDirectMachineOperandTargetFlags()

|

override |

Definition at line 812 of file MipsInstrInfo.cpp.

References llvm::makeArrayRef(), llvm::LanaiII::MO_ABS_HI, llvm::LanaiII::MO_ABS_LO, llvm::MipsII::MO_CALL_HI16, llvm::MipsII::MO_CALL_LO16, llvm::MipsII::MO_DTPREL_HI, llvm::MipsII::MO_DTPREL_LO, llvm::AArch64II::MO_GOT, llvm::MipsII::MO_GOT_CALL, llvm::MipsII::MO_GOT_DISP, llvm::MipsII::MO_GOT_HI16, llvm::MipsII::MO_GOT_LO16, llvm::MipsII::MO_GOT_OFST, llvm::MipsII::MO_GOT_PAGE, llvm::MipsII::MO_GOTTPREL, llvm::MipsII::MO_GPOFF_HI, llvm::MipsII::MO_GPOFF_LO, llvm::HexagonII::MO_GPREL, llvm::MipsII::MO_HIGHER, llvm::MipsII::MO_HIGHEST, llvm::MipsII::MO_JALR, llvm::MipsII::MO_TLSGD, llvm::MipsII::MO_TLSLDM, llvm::MipsII::MO_TPREL_HI, and llvm::MipsII::MO_TPREL_LO.

Referenced by loadRegFromStackSlot().

◆ HasForbiddenSlot()

| bool MipsInstrInfo::HasForbiddenSlot | ( | const MachineInstr & | MI | ) | const |

Predicate to determine if an instruction has a forbidden slot.

Predicate for distingushing instructions that have forbidden slots.

Definition at line 572 of file MipsInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MipsII::HasForbiddenSlot, and llvm::MCInstrDesc::TSFlags.

◆ insertBranch()

|

override |

Definition at line 121 of file MipsInstrInfo.cpp.

References llvm::MachineInstrBuilder::addMBB(), assert(), llvm::BuildMI(), llvm::ArrayRef< T >::empty(), llvm::ArrayRef< T >::size(), and UncondBrOpc.

◆ insertNoop()

|

override |

Insert nop instruction when hazard condition is found.

insertNoop - If data hazard condition is found insert the target nop instruction.

Definition at line 59 of file MipsInstrInfo.cpp.

References llvm::BuildMI().

Referenced by isZeroImm().

◆ isBranchOffsetInRange()

Determine if the branch target is in range.

Definition at line 279 of file MipsInstrInfo.cpp.

References B, llvm::isInt< 8 >(), and llvm_unreachable.

◆ isZeroImm()

|

protected |

Definition at line 51 of file MipsInstrInfo.cpp.

References llvm::MachineOperand::getImm(), insertNoop(), and llvm::MachineOperand::isImm().

Referenced by llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), and loadRegFromStackSlot().

◆ loadRegFromStack()

|

pure virtual |

Implemented in llvm::Mips16InstrInfo, and llvm::MipsSEInstrInfo.

Referenced by loadRegFromStackSlot().

◆ loadRegFromStackSlot()

|

inlineoverride |

Definition at line 121 of file MipsInstrInfo.h.

References adjustStackPtr(), llvm::createMips16InstrInfo(), llvm::createMipsSEInstrInfo(), decomposeMachineOperandsTargetFlags(), findCommutedOpIndices(), llvm::ISD::FrameIndex, genInstrWithNewOpc(), GetMemOperand(), getSerializableDirectMachineOperandTargetFlags(), I, isZeroImm(), loadRegFromStack(), MI, op, storeRegToStack(), TRI, and verifyInstruction().

Referenced by llvm::MipsSEFrameLowering::emitEpilogue().

◆ removeBranch()

|

override |

Definition at line 155 of file MipsInstrInfo.cpp.

References assert(), I, llvm::MachineBasicBlock::rbegin(), and llvm::MachineBasicBlock::rend().

◆ reverseBranchCondition()

|

override |

reverseBranchCondition - Return the inverse opcode of the specified Branch instruction.

Definition at line 183 of file MipsInstrInfo.cpp.

References assert(), getOppositeBranchOpc(), and llvm::SmallVectorBase::size().

◆ SafeInForbiddenSlot()

| bool MipsInstrInfo::SafeInForbiddenSlot | ( | const MachineInstr & | MI | ) | const |

Predicate to determine if an instruction can go in a forbidden slot.

Predicate for distingushing between control transfer instructions and all other instructions for handling forbidden slots.

Consider inline assembly as unsafe as well.

Definition at line 564 of file MipsInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MipsII::IsCTI, llvm::MachineInstr::isInlineAsm(), and llvm::MCInstrDesc::TSFlags.

◆ storeRegToStack()

|

pure virtual |

Implemented in llvm::Mips16InstrInfo, and llvm::MipsSEInstrInfo.

Referenced by llvm::MipsSEFrameLowering::emitPrologue(), loadRegFromStackSlot(), and storeRegToStackSlot().

◆ storeRegToStackSlot()

|

inlineoverride |

Definition at line 113 of file MipsInstrInfo.h.

References storeRegToStack().

◆ verifyInstruction()

|

override |

Perform target specific instruction verification.

Definition at line 758 of file MipsInstrInfo.cpp.

References llvm::AArch64ISD::EXT, llvm::MachineInstr::getOpcode(), Subtarget, llvm::MipsSubtarget::useIndirectJumpsHazard(), and verifyInsExtInstruction().

Referenced by loadRegFromStackSlot().

Member Data Documentation

◆ Subtarget

|

protected |

Definition at line 46 of file MipsInstrInfo.h.

Referenced by llvm::MipsSEInstrInfo::adjustStackPtr(), llvm::MipsSEInstrInfo::copyPhysReg(), llvm::MipsSEInstrInfo::expandPostRAPseudo(), getEquivalentCompactForm(), llvm::MipsSEInstrInfo::loadImmediate(), llvm::MipsSEInstrInfo::loadRegFromStack(), and verifyInstruction().

◆ UncondBrOpc

|

protected |

Definition at line 47 of file MipsInstrInfo.h.

Referenced by insertBranch().

The documentation for this class was generated from the following files:

- lib/Target/Mips/MipsInstrInfo.h

- lib/Target/Mips/MipsInstrInfo.cpp

1.8.13

1.8.13