#include "Target/AMDGPU/AMDGPUSubtarget.h"

Public Types | |

| enum | { ISAVersion0_0_0, ISAVersion6_0_0, ISAVersion6_0_1, ISAVersion7_0_0, ISAVersion7_0_1, ISAVersion7_0_2, ISAVersion7_0_3, ISAVersion7_0_4, ISAVersion8_0_1, ISAVersion8_0_2, ISAVersion8_0_3, ISAVersion8_1_0, ISAVersion9_0_0, ISAVersion9_0_2, ISAVersion9_0_4, ISAVersion9_0_6, ISAVersion9_0_9 } |

| enum | TrapHandlerAbi { TrapHandlerAbiNone = 0, TrapHandlerAbiHsa = 1 } |

| enum | TrapID { TrapIDHardwareReserved = 0, TrapIDHSADebugTrap = 1, TrapIDLLVMTrap = 2, TrapIDLLVMDebugTrap = 3, TrapIDDebugBreakpoint = 7, TrapIDDebugReserved8 = 8, TrapIDDebugReservedFE = 0xfe, TrapIDDebugReservedFF = 0xff } |

| enum | TrapRegValues { LLVMTrapHandlerRegValue = 1 } |

Public Types inherited from llvm::AMDGPUSubtarget Public Types inherited from llvm::AMDGPUSubtarget | |

| enum | Generation { R600 = 0, R700 = 1, EVERGREEN = 2, NORTHERN_ISLANDS = 3, SOUTHERN_ISLANDS = 4, SEA_ISLANDS = 5, VOLCANIC_ISLANDS = 6, GFX9 = 7 } |

Static Public Member Functions | |

| static bool | hasHalfRate64Ops (const TargetSubtargetInfo &STI) |

Static Public Member Functions inherited from llvm::AMDGPUSubtarget Static Public Member Functions inherited from llvm::AMDGPUSubtarget | |

| static const AMDGPUSubtarget & | get (const MachineFunction &MF) |

| static const AMDGPUSubtarget & | get (const TargetMachine &TM, const Function &F) |

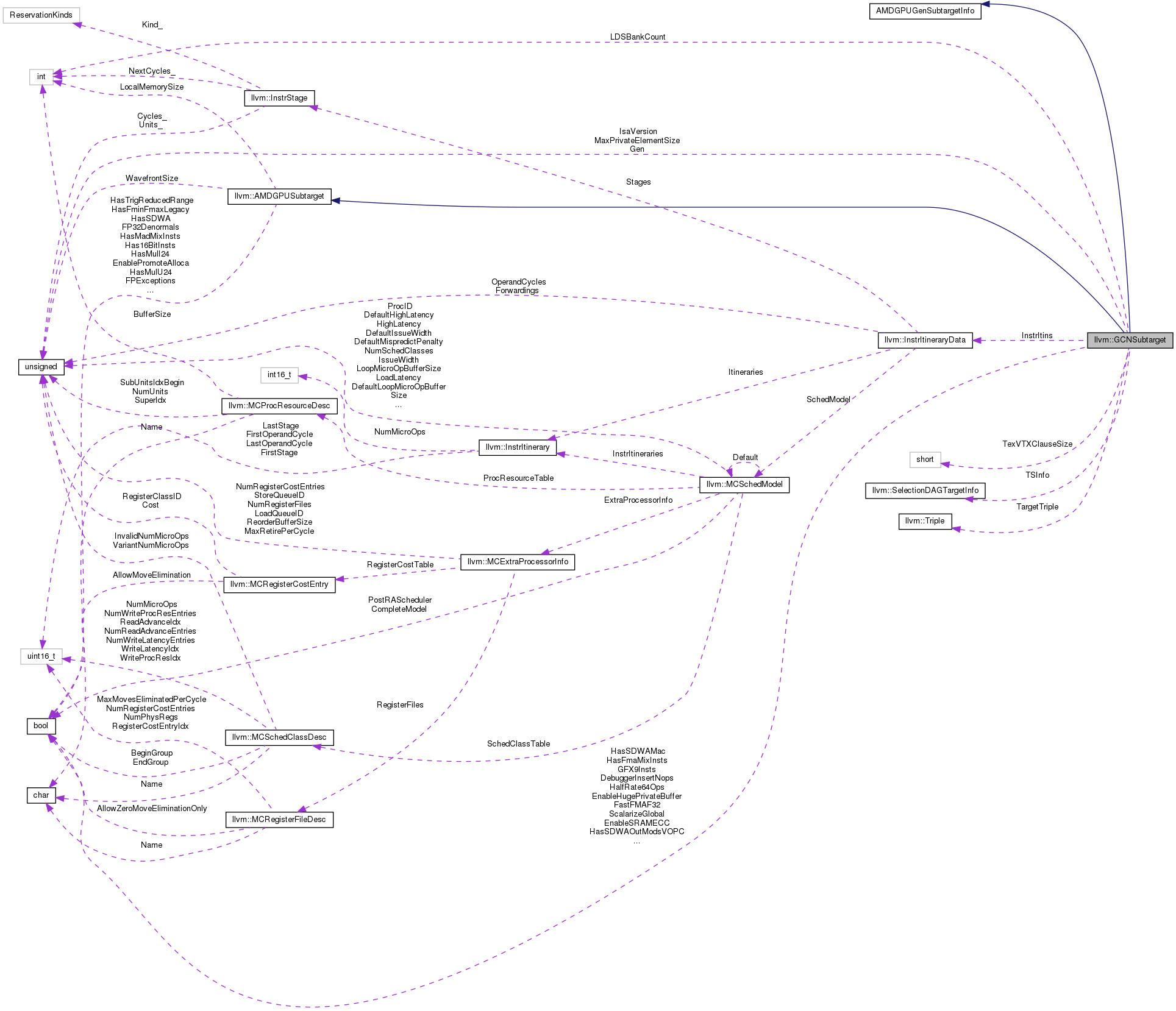

Detailed Description

Definition at line 246 of file AMDGPUSubtarget.h.

Member Enumeration Documentation

◆ anonymous enum

| anonymous enum |

Definition at line 249 of file AMDGPUSubtarget.h.

◆ TrapHandlerAbi

| Enumerator | |

|---|---|

| TrapHandlerAbiNone | |

| TrapHandlerAbiHsa | |

Definition at line 269 of file AMDGPUSubtarget.h.

◆ TrapID

| Enumerator | |

|---|---|

| TrapIDHardwareReserved | |

| TrapIDHSADebugTrap | |

| TrapIDLLVMTrap | |

| TrapIDLLVMDebugTrap | |

| TrapIDDebugBreakpoint | |

| TrapIDDebugReserved8 | |

| TrapIDDebugReservedFE | |

| TrapIDDebugReservedFF | |

Definition at line 274 of file AMDGPUSubtarget.h.

◆ TrapRegValues

| Enumerator | |

|---|---|

| LLVMTrapHandlerRegValue | |

Definition at line 285 of file AMDGPUSubtarget.h.

Constructor & Destructor Documentation

◆ GCNSubtarget()

| GCNSubtarget::GCNSubtarget | ( | const Triple & | TT, |

| StringRef | GPU, | ||

| StringRef | FS, | ||

| const GCNTargetMachine & | TM | ||

| ) |

Definition at line 150 of file AMDGPUSubtarget.cpp.

References getRegisterInfo(), and getTargetLowering().

◆ ~GCNSubtarget()

|

overridedefault |

Member Function Documentation

◆ debuggerEmitPrologue()

|

inline |

Definition at line 816 of file AMDGPUSubtarget.h.

Referenced by llvm::SIFrameLowering::emitEntryFunctionPrologue(), hasAnyNonFlatUseOfReg(), llvm::AMDGPUAsmPrinter::runOnMachineFunction(), and llvm::SIMachineFunctionInfo::SIMachineFunctionInfo().

◆ debuggerInsertNops()

|

inline |

Definition at line 812 of file AMDGPUSubtarget.h.

Referenced by llvm::createSIDebuggerInsertNopsPass().

◆ debuggerSupported()

|

inline |

Definition at line 808 of file AMDGPUSubtarget.h.

◆ dumpCode()

|

inline |

Definition at line 536 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::getMaxLocalMemSizeWithWaveCount().

Referenced by llvm::AMDGPUAsmPrinter::EmitBasicBlockStart(), llvm::AMDGPUAsmPrinter::EmitFunctionEntryLabel(), and llvm::AMDGPUAsmPrinter::runOnMachineFunction().

◆ enableDX10Clamp()

|

inline |

Definition at line 557 of file AMDGPUSubtarget.h.

Referenced by getMad64_32(), getSplatConstantFP(), hasAnyNonFlatUseOfReg(), isClampZeroToOne(), and llvm::SITargetLowering::isKnownNeverNaNForTargetNode().

◆ enableEarlyIfConversion()

|

inlineoverride |

Definition at line 756 of file AMDGPUSubtarget.h.

◆ enableHugePrivateBuffer()

|

inline |

Definition at line 528 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::LowerFormalArguments().

◆ enableIEEEBit()

|

inline |

Definition at line 561 of file AMDGPUSubtarget.h.

References llvm::Function::getCallingConv(), llvm::MachineFunction::getFunction(), and llvm::AMDGPU::isCompute().

Referenced by findUser(), and hasAnyNonFlatUseOfReg().

◆ enableMachineScheduler()

|

inlineoverride |

Definition at line 711 of file AMDGPUSubtarget.h.

◆ enableSIScheduler()

|

inline |

Definition at line 804 of file AMDGPUSubtarget.h.

Referenced by llvm::R600TargetMachine::createPassConfig().

◆ enableSubRegLiveness()

|

inlineoverride |

Definition at line 715 of file AMDGPUSubtarget.h.

◆ flatScratchIsPointer()

|

inline |

- Returns

- true if the flat_scratch register should be initialized with the pointer to the wave's scratch memory rather than a size and offset.

Definition at line 859 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by getAllSGPRs().

◆ getAddressableNumSGPRs()

|

inline |

- Returns

- Addressable number of SGPRs supported by the subtarget.

Definition at line 885 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getAddressableNumSGPRs().

Referenced by hasAnyNonFlatUseOfReg().

◆ getAddressableNumVGPRs()

|

inline |

- Returns

- Addressable number of VGPRs supported by the subtarget.

Definition at line 930 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getAddressableNumVGPRs().

◆ getCallLowering()

|

inlineoverride |

Definition at line 405 of file AMDGPUSubtarget.h.

◆ getEUsPerCU()

|

inline |

- Returns

- Number of execution units per compute unit supported by the subtarget.

Definition at line 724 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getEUsPerCU().

◆ getFrameLowering()

|

inlineoverride |

Definition at line 393 of file AMDGPUSubtarget.h.

◆ getGeneration()

|

inline |

Definition at line 432 of file AMDGPUSubtarget.h.

Referenced by addRegsToSet(), llvm::AMDGPULegalizerInfo::AMDGPULegalizerInfo(), getFPTernOp(), getLoadExtOrTrunc(), llvm::SITargetLowering::getRegisterByName(), getSmrdOpcode(), hasAnyNonFlatUseOfReg(), llvm::SITargetLowering::isLegalAddressingMode(), llvm::SITargetLowering::LowerFormalArguments(), parseTexFail(), llvm::SIMachineFunctionInfo::SIMachineFunctionInfo(), llvm::SITargetLowering::SITargetLowering(), llvm::AMDGPU::splitMUBUFOffset(), and subtargetEncodingFamily().

◆ getInstrInfo()

|

inlineoverride |

Definition at line 389 of file AMDGPUSubtarget.h.

Referenced by addRegsToSet(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::AMDGPULegalizerInfo::AMDGPULegalizerInfo(), bitOpWithConstantIsReducible(), buildMUBUFOffsetLoadStore(), canMoveInstsAcrossMemOp(), checkRegOnlyPHIInputs(), llvm::createSIAddIMGInitPass(), llvm::createSIDebuggerInsertNopsPass(), llvm::createSIModeRegisterPass(), llvm::createSIWholeQuadModePass(), llvm::SIFrameLowering::eliminateCallFramePseudoInstr(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::SIFrameLowering::emitEntryFunctionPrologue(), llvm::SIFrameLowering::emitEpilogue(), emitIndirectDst(), emitIndirectSrc(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::SIFrameLowering::emitPrologue(), findSingleRegDef(), fixupGlobalSaddr(), getAllSGPRs(), getPermuteMask(), getSplatConstantFP(), llvm::SITargetLowering::getTgtMemIntrinsic(), hasAnyNonFlatUseOfReg(), hoistAndMergeSGPRInits(), llvm::SITargetLowering::insertCopiesSplitCSR(), insertUndefLaneMask(), isLiveOut(), llvm::SITargetLowering::isSDNodeSourceOfDivergence(), matchSwap(), llvm::SIRegisterInfo::materializeFrameBaseRegister(), optimizeVcndVcmpPair(), llvm::SITargetLowering::PostISelFolding(), llvm::SIFrameLowering::processFunctionBeforeFrameFinalized(), llvm::SIRegisterInfo::resolveFrameIndex(), llvm::SIRegisterInfo::restoreSGPR(), llvm::AMDGPUAsmPrinter::runOnMachineFunction(), llvm::SIRegisterInfo::spillSGPR(), llvm::SITargetLowering::splitKillBlock(), and llvm::SITargetLowering::wrapAddr64Rsrc().

◆ getInstrItineraryData()

|

inlineoverride |

Definition at line 426 of file AMDGPUSubtarget.h.

◆ getInstructionSelector()

|

inlineoverride |

Definition at line 409 of file AMDGPUSubtarget.h.

◆ getLDSBankCount()

|

inline |

Definition at line 440 of file AMDGPUSubtarget.h.

◆ getLegalizerInfo()

|

inlineoverride |

Definition at line 413 of file AMDGPUSubtarget.h.

◆ getMaxFlatWorkGroupSize()

|

inlineoverridevirtual |

- Returns

- Maximum flat work group size supported by the subtarget.

Implements llvm::AMDGPUSubtarget.

Definition at line 972 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxFlatWorkGroupSize().

Referenced by llvm::AMDGPUSubtarget::getFlatWorkGroupSizes().

◆ getMaxLocalMemSizeWithWaveCount()

| unsigned llvm::GCNSubtarget::getMaxLocalMemSizeWithWaveCount | ( | unsigned | WaveCount, |

| const Function & | |||

| ) | const |

Return the amount of LDS that can be used that will not restrict the occupancy lower than WaveCount.

◆ getMaxNumSGPRs() [1/2]

- Returns

- Maximum number of SGPRs that meets the given number of waves per execution unit requirement supported by the subtarget.

Definition at line 897 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxNumSGPRs().

Referenced by getAllSGPR128(), getAllSGPRs(), llvm::SIRegisterInfo::getRegPressureLimit(), llvm::SIRegisterInfo::getReservedRegs(), llvm::GCNMaxOccupancySchedStrategy::initialize(), llvm::SIRegisterInfo::reservedPrivateSegmentBufferReg(), and llvm::SIRegisterInfo::reservedPrivateSegmentWaveByteOffsetReg().

◆ getMaxNumSGPRs() [2/2]

| unsigned GCNSubtarget::getMaxNumSGPRs | ( | const MachineFunction & | MF | ) | const |

- Returns

- Maximum number of SGPRs that meets number of waves per execution unit requirement for function

MF, or number of SGPRs explicitly requested using "amdgpu-num-sgpr" attribute attached to functionMF. - Value that meets number of waves per execution unit requirement if explicitly requested value cannot be converted to integer, violates subtarget's specifications, or does not meet number of waves per execution unit requirement.

Definition at line 548 of file AMDGPUSubtarget.cpp.

References F(), llvm::AMDGPU::IsaInfo::FIXED_NUM_SGPRS_FOR_INIT_BUG, llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), llvm::AMDGPU::getIntegerAttribute(), llvm::AMDGPU::IsaInfo::getMaxNumSGPRs(), llvm::AMDGPU::IsaInfo::getMinNumSGPRs(), llvm::SIMachineFunctionInfo::getNumPreloadedSGPRs(), llvm::SIMachineFunctionInfo::getWavesPerEU(), and llvm::Function::hasFnAttribute().

◆ getMaxNumUserSGPRs()

|

inline |

Definition at line 763 of file AMDGPUSubtarget.h.

Referenced by hasAnyNonFlatUseOfReg().

◆ getMaxNumVGPRs() [1/2]

- Returns

- Maximum number of VGPRs that meets given number of waves per execution unit requirement supported by the subtarget.

Definition at line 942 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxNumVGPRs().

Referenced by llvm::SIRegisterInfo::getRegPressureLimit(), llvm::SIRegisterInfo::getReservedRegs(), and llvm::GCNMaxOccupancySchedStrategy::initialize().

◆ getMaxNumVGPRs() [2/2]

| unsigned GCNSubtarget::getMaxNumVGPRs | ( | const MachineFunction & | MF | ) | const |

- Returns

- Maximum number of VGPRs that meets number of waves per execution unit requirement for function

MF, or number of VGPRs explicitly requested using "amdgpu-num-vgpr" attribute attached to functionMF. - Value that meets number of waves per execution unit requirement if explicitly requested value cannot be converted to integer, violates subtarget's specifications, or does not meet number of waves per execution unit requirement.

Definition at line 598 of file AMDGPUSubtarget.cpp.

References llvm::SUnit::addPred(), llvm::SUnit::addPredBarrier(), llvm::cl::apply(), llvm::SDep::Artificial, llvm::ScheduleDAG::ExitSU, F(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), llvm::SUnit::getInstr(), llvm::AMDGPU::getIntegerAttribute(), llvm::AMDGPU::IsaInfo::getMaxNumVGPRs(), llvm::AMDGPU::IsaInfo::getMinNumVGPRs(), llvm::SDep::getSUnit(), llvm::SIMachineFunctionInfo::getWavesPerEU(), llvm::Function::hasFnAttribute(), llvm::SIInstrInfo::isDS(), llvm::SIInstrInfo::isFLAT(), llvm::SIInstrInfo::isSMRD(), llvm::SIInstrInfo::isVMEM(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), llvm::SUnit::Preds, SI, llvm::SUnit::Succs, llvm::ScheduleDAG::SUnits, and TII.

◆ getMaxPrivateElementSize()

|

inline |

Definition at line 444 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::canMergeStoresTo(), getFPTernOp(), and getLoadExtOrTrunc().

◆ getMaxWavesPerCU() [1/2]

|

inline |

- Returns

- Maximum number of waves per compute unit supported by the subtarget without any kind of limitation.

Definition at line 730 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxWavesPerCU().

◆ getMaxWavesPerCU() [2/2]

- Returns

- Maximum number of waves per compute unit supported by the subtarget and limited by given

FlatWorkGroupSize.

Definition at line 736 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxWavesPerCU().

◆ getMaxWavesPerEU() [1/2]

|

inline |

- Returns

- Maximum number of waves per execution unit supported by the subtarget without any kind of limitation.

Definition at line 742 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxWavesPerEU().

Referenced by llvm::AMDGPUSubtarget::getMaxLocalMemSizeWithWaveCount(), llvm::AMDGPUSubtarget::getOccupancyWithLocalMemSize(), and llvm::AMDGPUSubtarget::getWavesPerEU().

◆ getMaxWavesPerEU() [2/2]

|

inlineoverridevirtual |

- Returns

- Maximum number of waves per execution unit supported by the subtarget and limited by given

FlatWorkGroupSize.

Implements llvm::AMDGPUSubtarget.

Definition at line 978 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxWavesPerEU().

◆ getMaxWorkGroupsPerCU()

|

inlineoverridevirtual |

- Returns

- Maximum number of work groups per compute unit supported by the subtarget and limited by given

FlatWorkGroupSize.

Implements llvm::AMDGPUSubtarget.

Definition at line 962 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMaxWorkGroupsPerCU().

Referenced by llvm::AMDGPUSubtarget::getMaxLocalMemSizeWithWaveCount(), and llvm::AMDGPUSubtarget::getOccupancyWithLocalMemSize().

◆ getMinFlatWorkGroupSize()

|

inlineoverridevirtual |

- Returns

- Minimum flat work group size supported by the subtarget.

Implements llvm::AMDGPUSubtarget.

Definition at line 967 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMinFlatWorkGroupSize().

Referenced by llvm::AMDGPUSubtarget::getFlatWorkGroupSizes().

◆ getMinNumSGPRs()

- Returns

- Minimum number of SGPRs that meets the given number of waves per execution unit requirement supported by the subtarget.

Definition at line 891 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMinNumSGPRs().

Referenced by hasAnyNonFlatUseOfReg().

◆ getMinNumVGPRs()

- Returns

- Minimum number of VGPRs that meets given number of waves per execution unit requirement supported by the subtarget.

Definition at line 936 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMinNumVGPRs().

Referenced by hasAnyNonFlatUseOfReg().

◆ getMinWavesPerEU()

|

inlineoverridevirtual |

- Returns

- Minimum number of waves per execution unit supported by the subtarget.

Implements llvm::AMDGPUSubtarget.

Definition at line 984 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getMinWavesPerEU().

Referenced by llvm::AMDGPUSubtarget::getWavesPerEU().

◆ getOccupancyWithNumSGPRs()

Return the maximum number of waves per SIMD for kernels using SGPRs SGPRs.

Definition at line 489 of file AMDGPUSubtarget.cpp.

References llvm::R600Subtarget::getGeneration(), and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

Referenced by llvm::GCNRegPressure::getOccupancy(), llvm::GCNRegPressure::less(), and llvm::GCNRegPressure::print().

◆ getOccupancyWithNumVGPRs()

Return the maximum number of waves per SIMD for kernels using VGPRs VGPRs.

Definition at line 512 of file AMDGPUSubtarget.cpp.

Referenced by llvm::GCNRegPressure::getOccupancy(), llvm::GCNRegPressure::less(), and llvm::GCNRegPressure::print().

◆ getPostRAMutations()

|

override |

Definition at line 679 of file AMDGPUSubtarget.cpp.

◆ getRegBankInfo()

|

inlineoverride |

Definition at line 417 of file AMDGPUSubtarget.h.

◆ getRegisterInfo()

|

inlineoverride |

Definition at line 401 of file AMDGPUSubtarget.h.

References llvm::SIInstrInfo::getRegisterInfo().

Referenced by addRegsToSet(), llvm::SIMachineFunctionInfo::allocateSGPRSpillToVGPR(), checkRegOnlyPHIInputs(), llvm::createSIAddIMGInitPass(), llvm::createSIFixWWMLivenessPass(), llvm::createSIWholeQuadModePass(), llvm::SITargetLowering::finalizeLowering(), findScratchNonCalleeSaveRegister(), findSingleRegDef(), fixupGlobalSaddr(), GCNSubtarget(), getOModValue(), llvm::SITargetLowering::getRegisterByName(), hoistAndMergeSGPRInits(), llvm::SITargetLowering::insertCopiesSplitCSR(), llvm::SITargetLowering::isEligibleForTailCallOptimization(), isLiveOut(), llvm::SITargetLowering::LowerCall(), llvm::SITargetLowering::LowerFormalArguments(), llvm::SITargetLowering::LowerReturn(), optimizeVcndVcmpPair(), llvm::SITargetLowering::passSpecialInputs(), readsVCCZ(), llvm::GCNHazardRecognizer::RecedeCycle(), and llvm::SITargetLowering::SITargetLowering().

◆ getReservedNumSGPRs()

| unsigned GCNSubtarget::getReservedNumSGPRs | ( | const MachineFunction & | MF | ) | const |

- Returns

- Reserved number of SGPRs for given function

MF.

Definition at line 534 of file AMDGPUSubtarget.cpp.

References llvm::R600Subtarget::getGeneration(), llvm::MachineFunction::getInfo(), llvm::SIMachineFunctionInfo::hasFlatScratchInit(), llvm::AMDGPUSubtarget::SEA_ISLANDS, and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

◆ getScalarizeGlobalBehavior()

|

inline |

Definition at line 720 of file AMDGPUSubtarget.h.

References ScalarizeGlobal.

Referenced by getLoadExtOrTrunc().

◆ getSelectionDAGInfo()

|

inlineoverride |

Definition at line 422 of file AMDGPUSubtarget.h.

◆ getSGPRAllocGranule()

|

inline |

- Returns

- SGPR allocation granularity supported by the subtarget.

Definition at line 870 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getSGPRAllocGranule().

◆ getSGPREncodingGranule()

|

inline |

- Returns

- SGPR encoding granularity supported by the subtarget.

Definition at line 875 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getSGPREncodingGranule().

◆ getStackAlignment()

|

inline |

Definition at line 707 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::LowerCall().

◆ getTargetLowering()

|

inlineoverride |

Definition at line 397 of file AMDGPUSubtarget.h.

Referenced by canMoveInstsAcrossMemOp(), and GCNSubtarget().

◆ getTotalNumSGPRs()

|

inline |

- Returns

- Total number of SGPRs supported by the subtarget.

Definition at line 880 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getTotalNumSGPRs().

◆ getTotalNumVGPRs()

|

inline |

- Returns

- Total number of VGPRs supported by the subtarget.

Definition at line 925 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getTotalNumVGPRs().

◆ getTrapHandlerAbi()

|

inline |

Definition at line 524 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::isAmdHsaOS().

Referenced by findUser().

◆ getVGPRAllocGranule()

|

inline |

- Returns

- VGPR allocation granularity supported by the subtarget.

Definition at line 915 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getVGPRAllocGranule().

◆ getVGPREncodingGranule()

|

inline |

- Returns

- VGPR encoding granularity supported by the subtarget.

Definition at line 920 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getVGPREncodingGranule().

◆ getWavefrontSizeLog2()

|

inline |

Definition at line 436 of file AMDGPUSubtarget.h.

References llvm::Log2_32(), and llvm::AMDGPUSubtarget::WavefrontSize.

Referenced by llvm::AMDGPUTargetLowering::computeKnownBitsForTargetNode().

◆ getWavesPerWorkGroup()

- Returns

- Number of waves per work group supported by the subtarget and limited by given

FlatWorkGroupSize.

Definition at line 748 of file AMDGPUSubtarget.h.

References llvm::AMDGPU::IsaInfo::getWavesPerWorkGroup().

◆ has12DWordStoreHazard()

|

inline |

Definition at line 828 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::SOUTHERN_ISLANDS.

Referenced by addRegsToSet().

◆ hasAddNoCarry()

|

inline |

Definition at line 646 of file AMDGPUSubtarget.h.

◆ hasAddr64()

|

inline |

Definition at line 472 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

Referenced by llvm::SITargetLowering::isLegalGlobalAddressingMode().

◆ hasApertureRegs()

|

inline |

Definition at line 604 of file AMDGPUSubtarget.h.

Referenced by copyFeaturesToFunction(), and findUser().

◆ hasAutoWaitcntBeforeBarrier()

|

inline |

Definition at line 587 of file AMDGPUSubtarget.h.

◆ hasBCNT()

Definition at line 488 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::SITargetLowering().

◆ hasBFE()

|

inline |

Definition at line 476 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::SITargetLowering().

◆ hasBFI()

|

inline |

Definition at line 480 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::SITargetLowering().

◆ hasBFM()

|

inline |

Definition at line 484 of file AMDGPUSubtarget.h.

◆ hasCARRY()

|

inline |

Definition at line 512 of file AMDGPUSubtarget.h.

◆ hasCodeObjectV3()

|

inline |

Definition at line 591 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::isAmdHsaOS().

Referenced by llvm::AMDGPUAsmPrinter::EmitFunctionBodyStart().

◆ hasD16LoadStore()

|

inline |

Definition at line 636 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

◆ hasDLInsts()

|

inline |

Definition at line 687 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::isFMAFasterThanFMulAndFAdd().

◆ hasDotInsts()

|

inline |

Definition at line 691 of file AMDGPUSubtarget.h.

Referenced by getMad64_32().

◆ hasDPP()

|

inline |

Definition at line 796 of file AMDGPUSubtarget.h.

◆ hasDwordx3LoadStores()

|

inline |

Definition at line 833 of file AMDGPUSubtarget.h.

Referenced by canMoveInstsAcrossMemOp().

◆ hasFastFMAF32()

|

inline |

Definition at line 464 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::isFMAFasterThanFMulAndFAdd().

◆ hasFFBH()

|

inline |

Definition at line 496 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::SITargetLowering().

◆ hasFFBL()

|

inline |

Definition at line 492 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::SITargetLowering().

◆ hasFlatAddressSpace()

|

inline |

Definition at line 616 of file AMDGPUSubtarget.h.

Referenced by llvm::AMDGPULegalizerInfo::AMDGPULegalizerInfo(), copyFeaturesToFunction(), llvm::GCNTTIImpl::getFlatAddressSpace(), llvm::SIMachineFunctionInfo::SIMachineFunctionInfo(), and llvm::SITargetLowering::SITargetLowering().

◆ hasFlatGlobalInsts()

|

inline |

Definition at line 624 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::isLegalGlobalAddressingMode().

◆ hasFlatInstOffsets()

|

inline |

Definition at line 620 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::getAddrModeArguments().

◆ hasFlatLgkmVMemCountInOrder()

|

inline |

Definition at line 632 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

◆ hasFlatScratchInsts()

|

inline |

Definition at line 628 of file AMDGPUSubtarget.h.

◆ hasFMA()

|

inline |

Definition at line 516 of file AMDGPUSubtarget.h.

References llvm::ISD::FMA.

◆ hasFmaMixInsts()

|

inline |

Definition at line 508 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::isFPExtFoldable().

◆ hasFP16Denormals()

|

inline |

Definition at line 545 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::denormalsEnabledForType(), isClampZeroToOne(), llvm::SITargetLowering::isFMAFasterThanFMulAndFAdd(), and llvm::SITargetLowering::SITargetLowering().

◆ hasFP64()

|

inline |

Definition at line 452 of file AMDGPUSubtarget.h.

◆ hasFP64Denormals()

|

inline |

Definition at line 549 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::denormalsEnabledForType(), and getFPMode().

◆ hasHalfRate64Ops() [1/2]

|

inline |

Definition at line 468 of file AMDGPUSubtarget.h.

◆ hasHalfRate64Ops() [2/2]

|

static |

◆ hasHWFP64()

|

inline |

Definition at line 460 of file AMDGPUSubtarget.h.

◆ hasIntClamp()

|

inline |

Definition at line 448 of file AMDGPUSubtarget.h.

◆ hasMad64_32()

|

inline |

Definition at line 659 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::SEA_ISLANDS.

Referenced by getMad64_32().

◆ hasMed3_16()

|

inline |

Definition at line 500 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by getSplatConstantFP(), and minMaxOpcToMin3Max3Opc().

◆ hasMergedShaders()

|

inline |

- Returns

- true if the machine has merged shaders in which s0-s7 are reserved by the hardware and user SGPRs start at s8

Definition at line 865 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by llvm::SIFrameLowering::emitEntryFunctionPrologue().

◆ hasMIMG_R128()

|

inline |

Definition at line 456 of file AMDGPUSubtarget.h.

◆ hasMin3Max3_16()

|

inline |

Definition at line 504 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by getSplatConstantFP().

◆ hasMovrel()

|

inline |

Definition at line 771 of file AMDGPUSubtarget.h.

◆ hasR128A16()

|

inline |

Definition at line 800 of file AMDGPUSubtarget.h.

◆ hasReadM0MovRelInterpHazard()

|

inline |

Definition at line 841 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ hasReadM0SendMsgHazard()

|

inline |

Definition at line 845 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoops().

◆ hasScalarAtomics()

|

inline |

Definition at line 791 of file AMDGPUSubtarget.h.

◆ hasScalarCompareEq64()

|

inline |

Definition at line 783 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

◆ hasScalarStores()

|

inline |

Definition at line 787 of file AMDGPUSubtarget.h.

Referenced by llvm::SIInstrInfo::loadRegFromStackSlot(), llvm::SIRegisterInfo::SIRegisterInfo(), and llvm::SIInstrInfo::storeRegToStackSlot().

◆ hasSDWAMac()

|

inline |

Definition at line 675 of file AMDGPUSubtarget.h.

Referenced by findSingleRegDef().

◆ hasSDWAOmod()

|

inline |

Definition at line 663 of file AMDGPUSubtarget.h.

Referenced by findSingleRegDef(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasSDWAOutModsVOPC()

|

inline |

Definition at line 679 of file AMDGPUSubtarget.h.

Referenced by findSingleRegDef(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasSDWAScalar()

|

inline |

Definition at line 667 of file AMDGPUSubtarget.h.

Referenced by findSingleRegDef(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasSDWASdst()

|

inline |

Definition at line 671 of file AMDGPUSubtarget.h.

Referenced by findSingleRegDef(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasSGPRInitBug()

|

inline |

Definition at line 824 of file AMDGPUSubtarget.h.

Referenced by getAllSGPRs(), and hasAnyNonFlatUseOfReg().

◆ hasSMemRealTime()

|

inline |

Definition at line 767 of file AMDGPUSubtarget.h.

◆ hasSMovFedHazard()

|

inline |

Definition at line 837 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by addRegsToSet().

◆ hasSwap()

|

inline |

Definition at line 520 of file AMDGPUSubtarget.h.

Referenced by matchSwap().

◆ hasUnalignedBufferAccess()

|

inline |

Definition at line 596 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::allowsMisalignedMemoryAccesses().

◆ hasUnalignedScratchAccess()

|

inline |

Definition at line 600 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::allowsMisalignedMemoryAccesses().

◆ hasUnpackedD16VMem()

|

inline |

Definition at line 650 of file AMDGPUSubtarget.h.

Referenced by adjustLoadValueTypeImpl(), llvm::createSIAddIMGInitPass(), parseTexFail(), and llvm::SIInstrInfo::verifyInstruction().

◆ hasVGPRIndexMode()

|

inline |

Definition at line 775 of file AMDGPUSubtarget.h.

◆ initializeSubtargetDependencies()

| GCNSubtarget & GCNSubtarget::initializeSubtargetDependencies | ( | const Triple & | TT, |

| StringRef | GPU, | ||

| StringRef | FS | ||

| ) |

Definition at line 67 of file AMDGPUSubtarget.cpp.

References llvm::Triple::amdgcn, assert(), llvm::StringRef::contains(), llvm::Triple::getArch(), llvm::R600Subtarget::getGeneration(), llvm::AMDGPUSubtarget::HasFminFmaxLegacy, llvm::AMDGPUSubtarget::isAmdHsaOS(), llvm::AMDGPUSubtarget::LocalMemorySize, llvm::R600Subtarget::ParseSubtargetFeatures(), llvm::AMDGPUSubtarget::SOUTHERN_ISLANDS, and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

◆ isMesaGfxShader()

Definition at line 655 of file AMDGPUSubtarget.h.

References llvm::Function::getCallingConv(), llvm::AMDGPUSubtarget::isMesa3DOS(), and llvm::AMDGPU::isShader().

Referenced by llvm::SIFrameLowering::emitEntryFunctionPrologue(), and llvm::SIMachineFunctionInfo::SIMachineFunctionInfo().

◆ isSRAMECCEnabled()

|

inline |

Definition at line 695 of file AMDGPUSubtarget.h.

◆ isTrapHandlerEnabled()

|

inline |

Definition at line 608 of file AMDGPUSubtarget.h.

Referenced by findUser(), and hasAnyNonFlatUseOfReg().

◆ isXNACKEnabled()

|

inline |

Definition at line 612 of file AMDGPUSubtarget.h.

Referenced by addRegsToSet().

◆ ldsRequiresM0Init()

|

inline |

Return if most LDS instructions have an m0 use that require m0 to be iniitalized.

Definition at line 642 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by canMoveInstsAcrossMemOp().

◆ loadStoreOptEnabled()

|

inline |

Definition at line 820 of file AMDGPUSubtarget.h.

References EnableLoadStoreOpt.

Referenced by canMoveInstsAcrossMemOp().

◆ overrideSchedPolicy()

|

override |

Definition at line 472 of file AMDGPUSubtarget.cpp.

References llvm::MachineSchedPolicy::OnlyBottomUp, llvm::MachineSchedPolicy::OnlyTopDown, llvm::MachineSchedPolicy::ShouldTrackLaneMasks, and llvm::MachineSchedPolicy::ShouldTrackPressure.

◆ ParseSubtargetFeatures()

◆ privateMemoryResourceIsRangeChecked()

|

inline |

- Returns

- If MUBUF instructions always perform range checking, even for buffer resources used for private memory access.

Definition at line 577 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

◆ setScalarizeGlobalBehavior()

|

inline |

Definition at line 719 of file AMDGPUSubtarget.h.

◆ supportsMinMaxDenormModes()

|

inline |

Definition at line 553 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::GFX9.

Referenced by llvm::SITargetLowering::isCanonicalized().

◆ unsafeDSOffsetFoldingEnabled()

|

inline |

Definition at line 532 of file AMDGPUSubtarget.h.

◆ useDS128()

|

inline |

- Returns

- If target supports ds_read/write_b128 and user enables generation of ds_read/write_b128.

Definition at line 571 of file AMDGPUSubtarget.h.

Referenced by getFPTernOp(), and getLoadExtOrTrunc().

◆ useFlatForGlobal()

|

inline |

Definition at line 565 of file AMDGPUSubtarget.h.

Referenced by llvm::SITargetLowering::isLegalGlobalAddressingMode().

◆ usePRTStrictNull()

|

inline |

- Returns

- If target requires PRT Struct NULL support (zero result registers for sparse texture support).

Definition at line 583 of file AMDGPUSubtarget.h.

Referenced by llvm::createSIAddIMGInitPass().

◆ useVGPRIndexMode()

Definition at line 779 of file AMDGPUSubtarget.h.

Referenced by emitIndirectDst(), and emitIndirectSrc().

◆ vmemWriteNeedsExpWaitcnt()

|

inline |

Definition at line 683 of file AMDGPUSubtarget.h.

References llvm::AMDGPUSubtarget::SEA_ISLANDS.

Member Data Documentation

◆ AddNoCarryInsts

|

protected |

Definition at line 363 of file AMDGPUSubtarget.h.

◆ AutoWaitcntBeforeBarrier

|

protected |

Definition at line 313 of file AMDGPUSubtarget.h.

◆ CaymanISA

|

protected |

Definition at line 366 of file AMDGPUSubtarget.h.

◆ CFALUBug

|

protected |

Definition at line 367 of file AMDGPUSubtarget.h.

◆ CIInsts

|

protected |

Definition at line 338 of file AMDGPUSubtarget.h.

◆ CodeObjectV3

|

protected |

Definition at line 314 of file AMDGPUSubtarget.h.

◆ DebuggerEmitPrologue

|

protected |

Definition at line 321 of file AMDGPUSubtarget.h.

◆ DebuggerInsertNops

|

protected |

Definition at line 320 of file AMDGPUSubtarget.h.

◆ DumpCode

|

protected |

Definition at line 330 of file AMDGPUSubtarget.h.

◆ DX10Clamp

|

protected |

Definition at line 311 of file AMDGPUSubtarget.h.

◆ EnableDS128

|

protected |

Definition at line 328 of file AMDGPUSubtarget.h.

◆ EnableHugePrivateBuffer

|

protected |

Definition at line 324 of file AMDGPUSubtarget.h.

◆ EnableLoadStoreOpt

|

protected |

Definition at line 325 of file AMDGPUSubtarget.h.

◆ EnablePRTStrictNull

|

protected |

Definition at line 329 of file AMDGPUSubtarget.h.

◆ EnableSIScheduler

|

protected |

Definition at line 327 of file AMDGPUSubtarget.h.

◆ EnableSRAMECC

|

protected |

Definition at line 358 of file AMDGPUSubtarget.h.

◆ EnableUnsafeDSOffsetFolding

|

protected |

Definition at line 326 of file AMDGPUSubtarget.h.

◆ EnableXNACK

|

protected |

Definition at line 318 of file AMDGPUSubtarget.h.

◆ FastFMAF32

|

protected |

Definition at line 306 of file AMDGPUSubtarget.h.

◆ FeatureDisable

|

protected |

Definition at line 373 of file AMDGPUSubtarget.h.

◆ FlatAddressSpace

|

protected |

Definition at line 359 of file AMDGPUSubtarget.h.

◆ FlatForGlobal

|

protected |

Definition at line 312 of file AMDGPUSubtarget.h.

◆ FlatGlobalInsts

|

protected |

Definition at line 361 of file AMDGPUSubtarget.h.

◆ FlatInstOffsets

|

protected |

Definition at line 360 of file AMDGPUSubtarget.h.

◆ FlatScratchInsts

|

protected |

Definition at line 362 of file AMDGPUSubtarget.h.

◆ FMA

|

protected |

Definition at line 334 of file AMDGPUSubtarget.h.

◆ FP64

|

protected |

Definition at line 333 of file AMDGPUSubtarget.h.

◆ FP64FP16Denormals

|

protected |

Definition at line 310 of file AMDGPUSubtarget.h.

◆ GCN3Encoding

|

protected |

Definition at line 337 of file AMDGPUSubtarget.h.

◆ Gen

|

protected |

Definition at line 299 of file AMDGPUSubtarget.h.

◆ GFX9Insts

|

protected |

Definition at line 340 of file AMDGPUSubtarget.h.

◆ HalfRate64Ops

|

protected |

Definition at line 307 of file AMDGPUSubtarget.h.

◆ HasApertureRegs

|

protected |

Definition at line 317 of file AMDGPUSubtarget.h.

◆ HasDLInsts

|

protected |

Definition at line 356 of file AMDGPUSubtarget.h.

◆ HasDotInsts

|

protected |

Definition at line 357 of file AMDGPUSubtarget.h.

◆ HasDPP

|

protected |

Definition at line 354 of file AMDGPUSubtarget.h.

◆ HasFmaMixInsts

|

protected |

Definition at line 344 of file AMDGPUSubtarget.h.

◆ HasIntClamp

|

protected |

Definition at line 343 of file AMDGPUSubtarget.h.

◆ HasMovrel

|

protected |

Definition at line 345 of file AMDGPUSubtarget.h.

◆ HasR128A16

|

protected |

Definition at line 355 of file AMDGPUSubtarget.h.

◆ HasScalarAtomics

|

protected |

Definition at line 348 of file AMDGPUSubtarget.h.

◆ HasScalarStores

|

protected |

Definition at line 347 of file AMDGPUSubtarget.h.

◆ HasSDWAMac

|

protected |

Definition at line 352 of file AMDGPUSubtarget.h.

◆ HasSDWAOmod

|

protected |

Definition at line 349 of file AMDGPUSubtarget.h.

◆ HasSDWAOutModsVOPC

|

protected |

Definition at line 353 of file AMDGPUSubtarget.h.

◆ HasSDWAScalar

|

protected |

Definition at line 350 of file AMDGPUSubtarget.h.

◆ HasSDWASdst

|

protected |

Definition at line 351 of file AMDGPUSubtarget.h.

◆ HasSMemRealTime

|

protected |

Definition at line 342 of file AMDGPUSubtarget.h.

◆ HasUnpackedD16VMem

|

protected |

Definition at line 364 of file AMDGPUSubtarget.h.

◆ HasVertexCache

|

protected |

Definition at line 368 of file AMDGPUSubtarget.h.

◆ HasVGPRIndexMode

|

protected |

Definition at line 346 of file AMDGPUSubtarget.h.

◆ InstrItins

|

protected |

Definition at line 301 of file AMDGPUSubtarget.h.

◆ IsaVersion

|

protected |

Definition at line 300 of file AMDGPUSubtarget.h.

◆ IsGCN

|

protected |

Definition at line 336 of file AMDGPUSubtarget.h.

◆ LDSBankCount

|

protected |

Definition at line 302 of file AMDGPUSubtarget.h.

◆ MaxPrivateElementSize

|

protected |

Definition at line 303 of file AMDGPUSubtarget.h.

◆ MIMG_R128

|

protected |

Definition at line 335 of file AMDGPUSubtarget.h.

◆ R600ALUInst

|

protected |

Definition at line 365 of file AMDGPUSubtarget.h.

◆ ScalarizeGlobal

|

protected |

Definition at line 370 of file AMDGPUSubtarget.h.

◆ SGPRInitBug

|

protected |

Definition at line 341 of file AMDGPUSubtarget.h.

◆ TargetTriple

|

protected |

Definition at line 298 of file AMDGPUSubtarget.h.

◆ TexVTXClauseSize

|

protected |

Definition at line 369 of file AMDGPUSubtarget.h.

◆ TrapHandler

|

protected |

Definition at line 319 of file AMDGPUSubtarget.h.

◆ TSInfo

|

protected |

Definition at line 375 of file AMDGPUSubtarget.h.

◆ UnalignedBufferAccess

|

protected |

Definition at line 316 of file AMDGPUSubtarget.h.

◆ UnalignedScratchAccess

|

protected |

Definition at line 315 of file AMDGPUSubtarget.h.

◆ VIInsts

|

protected |

Definition at line 339 of file AMDGPUSubtarget.h.

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPUSubtarget.h

- lib/Target/AMDGPU/AMDGPUSubtarget.cpp

1.8.13

1.8.13