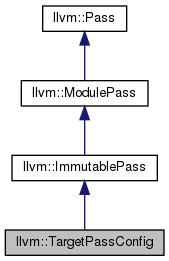

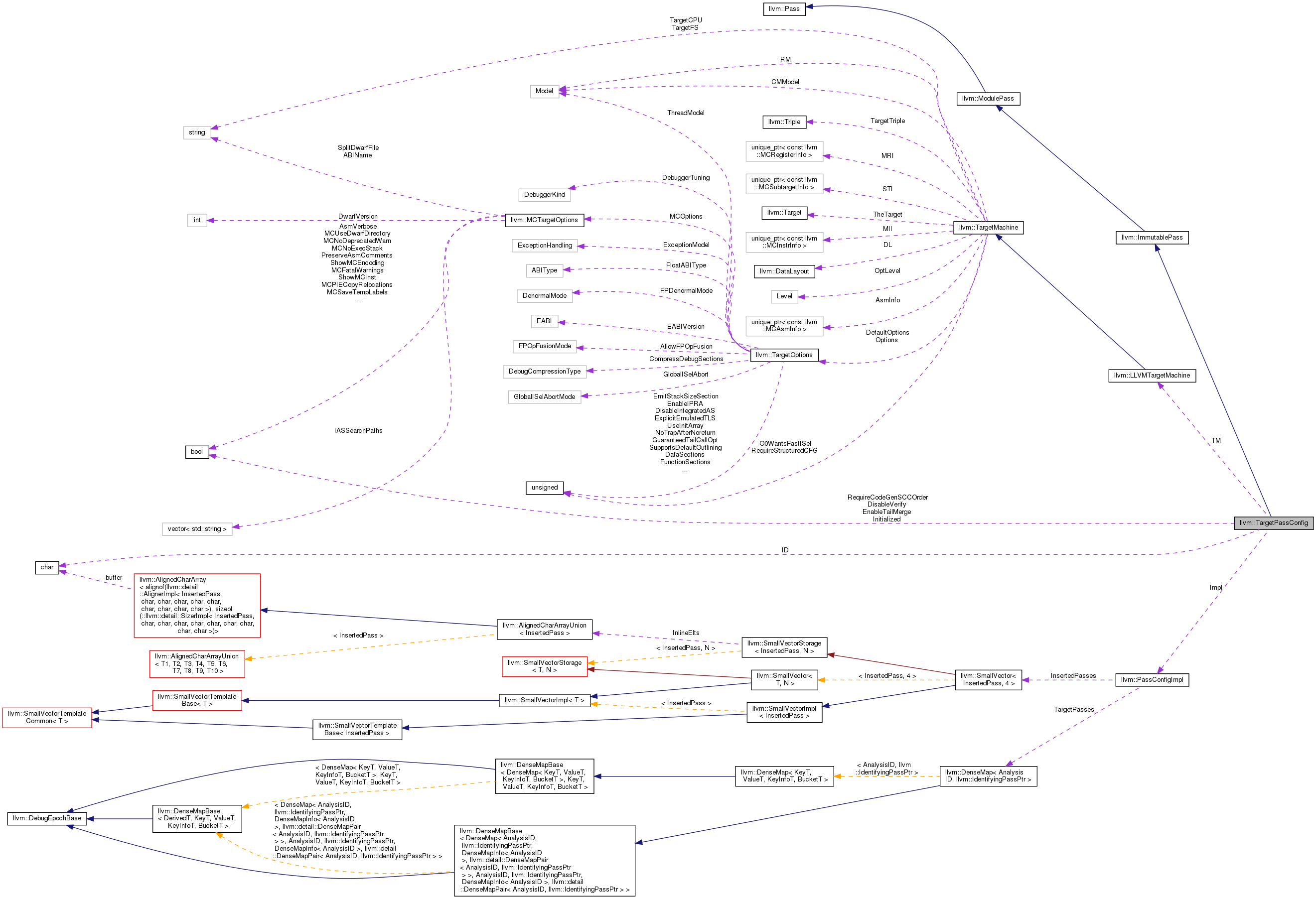

Target-Independent Code Generator Pass Configuration Options. More...

#include "llvm/CodeGen/TargetPassConfig.h"

Public Member Functions | |

| TargetPassConfig (LLVMTargetMachine &TM, PassManagerBase &pm) | |

| TargetPassConfig () | |

| ~TargetPassConfig () override | |

| template<typename TMC > | |

| TMC & | getTM () const |

| Get the right type of TargetMachine for this target. More... | |

| void | setInitialized () |

| CodeGenOpt::Level | getOptLevel () const |

| std::string | getLimitedCodeGenPipelineReason (const char *Separator="/") const |

If hasLimitedCodeGenPipeline is true, this method returns a string with the name of the options, separated by Separator that caused this pipeline to be limited. More... | |

| void | setDisableVerify (bool Disable) |

| bool | getEnableTailMerge () const |

| void | setEnableTailMerge (bool Enable) |

| bool | requiresCodeGenSCCOrder () const |

| void | setRequiresCodeGenSCCOrder (bool Enable=true) |

| void | substitutePass (AnalysisID StandardID, IdentifyingPassPtr TargetID) |

| Allow the target to override a specific pass without overriding the pass pipeline. More... | |

| void | insertPass (AnalysisID TargetPassID, IdentifyingPassPtr InsertedPassID, bool VerifyAfter=true, bool PrintAfter=true) |

| Insert InsertedPassID pass after TargetPassID pass. More... | |

| void | enablePass (AnalysisID PassID) |

| Allow the target to enable a specific standard pass by default. More... | |

| void | disablePass (AnalysisID PassID) |

| Allow the target to disable a specific standard pass by default. More... | |

| IdentifyingPassPtr | getPassSubstitution (AnalysisID StandardID) const |

| Return the pass substituted for StandardID by the target. More... | |

| bool | isPassSubstitutedOrOverridden (AnalysisID ID) const |

| Return true if the pass has been substituted by the target or overridden on the command line. More... | |

| bool | getOptimizeRegAlloc () const |

| Return true if the optimized regalloc pipeline is enabled. More... | |

| bool | usingDefaultRegAlloc () const |

| Return true if the default global register allocator is in use and has not be overriden on the command line with '-regalloc=...'. More... | |

| bool | addISelPasses () |

| High level function that adds all passes necessary to go from llvm IR representation to the MI representation. More... | |

| virtual void | addIRPasses () |

| Add common target configurable passes that perform LLVM IR to IR transforms following machine independent optimization. More... | |

| void | addPassesToHandleExceptions () |

| Add passes to lower exception handling for the code generator. More... | |

| virtual void | addCodeGenPrepare () |

| Add pass to prepare the LLVM IR for code generation. More... | |

| virtual void | addISelPrepare () |

| Add common passes that perform LLVM IR to IR transforms in preparation for instruction selection. More... | |

| virtual bool | addInstSelector () |

| addInstSelector - This method should install an instruction selector pass, which converts from LLVM code to machine instructions. More... | |

| virtual bool | addIRTranslator () |

| This method should install an IR translator pass, which converts from LLVM code to machine instructions with possibly generic opcodes. More... | |

| virtual void | addPreLegalizeMachineIR () |

| This method may be implemented by targets that want to run passes immediately before legalization. More... | |

| virtual bool | addLegalizeMachineIR () |

| This method should install a legalize pass, which converts the instruction sequence into one that can be selected by the target. More... | |

| virtual void | addPreRegBankSelect () |

| This method may be implemented by targets that want to run passes immediately before the register bank selection. More... | |

| virtual bool | addRegBankSelect () |

| This method should install a register bank selector pass, which assigns register banks to virtual registers without a register class or register banks. More... | |

| virtual void | addPreGlobalInstructionSelect () |

| This method may be implemented by targets that want to run passes immediately before the (global) instruction selection. More... | |

| virtual bool | addGlobalInstructionSelect () |

| This method should install a (global) instruction selector pass, which converts possibly generic instructions to fully target-specific instructions, thereby constraining all generic virtual registers to register classes. More... | |

| virtual void | addMachinePasses () |

| Add the complete, standard set of LLVM CodeGen passes. More... | |

| false **Return NULL to select the | default (generic) machine scheduler. */virtual ScheduleDAGInstrs *createMachineScheduler(MachineSchedContext *C) const |

| Create an instance of ScheduleDAGInstrs to be run within the standard MachineScheduler pass for this function and target at the current optimization level. More... | |

| virtual ScheduleDAGInstrs * | createPostMachineScheduler (MachineSchedContext *C) const |

| Similar to createMachineScheduler but used when postRA machine scheduling is enabled. More... | |

| void | printAndVerify (const std::string &Banner) |

| printAndVerify - Add a pass to dump then verify the machine function, if those steps are enabled. More... | |

| void | addPrintPass (const std::string &Banner) |

| Add a pass to print the machine function if printing is enabled. More... | |

| void | addVerifyPass (const std::string &Banner) |

| Add a pass to perform basic verification of the machine function if verification is enabled. More... | |

| bool | isGlobalISelAbortEnabled () const |

| Check whether or not GlobalISel should abort on error. More... | |

| virtual bool | reportDiagnosticWhenGlobalISelFallback () const |

| Check whether or not a diagnostic should be emitted when GlobalISel uses the fallback path. More... | |

Public Member Functions inherited from llvm::ImmutablePass Public Member Functions inherited from llvm::ImmutablePass | |

| ImmutablePass (char &pid) | |

| ~ImmutablePass () override | |

| virtual void | initializePass () |

| initializePass - This method may be overriden by immutable passes to allow them to perform various initialization actions they require. More... | |

| ImmutablePass * | getAsImmutablePass () override |

| bool | runOnModule (Module &) override |

| ImmutablePasses are never run. More... | |

Public Member Functions inherited from llvm::ModulePass Public Member Functions inherited from llvm::ModulePass | |

| ModulePass (char &pid) | |

| ~ModulePass () override | |

| Pass * | createPrinterPass (raw_ostream &OS, const std::string &Banner) const override |

| createPrinterPass - Get a module printer pass. More... | |

| void | assignPassManager (PMStack &PMS, PassManagerType T) override |

| Find appropriate Module Pass Manager in the PM Stack and add self into that manager. More... | |

| PassManagerType | getPotentialPassManagerType () const override |

| Return what kind of Pass Manager can manage this pass. More... | |

Public Member Functions inherited from llvm::Pass Public Member Functions inherited from llvm::Pass | |

| Pass (PassKind K, char &pid) | |

| Pass (const Pass &)=delete | |

| Pass & | operator= (const Pass &)=delete |

| virtual | ~Pass () |

| PassKind | getPassKind () const |

| virtual StringRef | getPassName () const |

| getPassName - Return a nice clean name for a pass. More... | |

| AnalysisID | getPassID () const |

| getPassID - Return the PassID number that corresponds to this pass. More... | |

| virtual bool | doInitialization (Module &) |

| doInitialization - Virtual method overridden by subclasses to do any necessary initialization before any pass is run. More... | |

| virtual bool | doFinalization (Module &) |

| doFinalization - Virtual method overriden by subclasses to do any necessary clean up after all passes have run. More... | |

| virtual void | print (raw_ostream &OS, const Module *M) const |

| print - Print out the internal state of the pass. More... | |

| void | dump () const |

| virtual void | preparePassManager (PMStack &) |

| Check if available pass managers are suitable for this pass or not. More... | |

| void | setResolver (AnalysisResolver *AR) |

| AnalysisResolver * | getResolver () const |

| virtual void | getAnalysisUsage (AnalysisUsage &) const |

| getAnalysisUsage - This function should be overriden by passes that need analysis information to do their job. More... | |

| virtual void | releaseMemory () |

| releaseMemory() - This member can be implemented by a pass if it wants to be able to release its memory when it is no longer needed. More... | |

| virtual void * | getAdjustedAnalysisPointer (AnalysisID ID) |

| getAdjustedAnalysisPointer - This method is used when a pass implements an analysis interface through multiple inheritance. More... | |

| virtual PMDataManager * | getAsPMDataManager () |

| virtual void | verifyAnalysis () const |

| verifyAnalysis() - This member can be implemented by a analysis pass to check state of analysis information. More... | |

| virtual void | dumpPassStructure (unsigned Offset=0) |

| template<typename AnalysisType > | |

| AnalysisType * | getAnalysisIfAvailable () const |

| getAnalysisIfAvailable<AnalysisType>() - Subclasses use this function to get analysis information that might be around, for example to update it. More... | |

| bool | mustPreserveAnalysisID (char &AID) const |

| mustPreserveAnalysisID - This method serves the same function as getAnalysisIfAvailable, but works if you just have an AnalysisID. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis () const |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysis (Function &F) |

| getAnalysis<AnalysisType>() - This function is used by subclasses to get to the analysis information that they claim to use by overriding the getAnalysisUsage function. More... | |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI) const |

| template<typename AnalysisType > | |

| AnalysisType & | getAnalysisID (AnalysisID PI, Function &F) |

Static Public Member Functions | |

| static bool | hasLimitedCodeGenPipeline () |

Returns true if one of the -start-after, -start-before, -stop-after or -stop-before options is set. More... | |

| static bool | willCompleteCodeGenPipeline () |

Returns true if none of the -stop-before and -stop-after options is set. More... | |

Static Public Member Functions inherited from llvm::Pass Static Public Member Functions inherited from llvm::Pass | |

| static const PassInfo * | lookupPassInfo (const void *TI) |

| static const PassInfo * | lookupPassInfo (StringRef Arg) |

| static Pass * | createPass (AnalysisID ID) |

Static Public Attributes | |

| static char | ID |

Protected Member Functions | |

| bool | addCoreISelPasses () |

| Add the actual instruction selection passes. More... | |

| void | setOpt (bool &Opt, bool Val) |

| virtual bool | addPreISel () |

| Methods with trivial inline returns are convenient points in the common codegen pass pipeline where targets may insert passes. More... | |

| virtual void | addMachineSSAOptimization () |

| addMachineSSAOptimization - Add standard passes that optimize machine instructions in SSA form. More... | |

| virtual bool | addILPOpts () |

| Add passes that optimize instruction level parallelism for out-of-order targets. More... | |

| virtual void | addPreRegAlloc () |

| This method may be implemented by targets that want to run passes immediately before register allocation. More... | |

| virtual FunctionPass * | createTargetRegisterAllocator (bool Optimized) |

| createTargetRegisterAllocator - Create the register allocator pass for this target at the current optimization level. More... | |

| virtual void | addFastRegAlloc (FunctionPass *RegAllocPass) |

| addFastRegAlloc - Add the minimum set of target-independent passes that are required for fast register allocation. More... | |

| virtual void | addOptimizedRegAlloc (FunctionPass *RegAllocPass) |

| addOptimizedRegAlloc - Add passes related to register allocation. More... | |

| virtual bool | addPreRewrite () |

| addPreRewrite - Add passes to the optimized register allocation pipeline after register allocation is complete, but before virtual registers are rewritten to physical registers. More... | |

| virtual void | addPostRegAlloc () |

| This method may be implemented by targets that want to run passes after register allocation pass pipeline but before prolog-epilog insertion. More... | |

| virtual void | addMachineLateOptimization () |

| Add passes that optimize machine instructions after register allocation. More... | |

| virtual void | addPreSched2 () |

| This method may be implemented by targets that want to run passes after prolog-epilog insertion and before the second instruction scheduling pass. More... | |

| virtual bool | addGCPasses () |

| addGCPasses - Add late codegen passes that analyze code for garbage collection. More... | |

| virtual void | addBlockPlacement () |

| Add standard basic block placement passes. More... | |

| virtual void | addPreEmitPass () |

| This pass may be implemented by targets that want to run passes immediately before machine code is emitted. More... | |

| virtual void | addPreEmitPass2 () |

| Targets may add passes immediately before machine code is emitted in this callback. More... | |

| AnalysisID | addPass (AnalysisID PassID, bool verifyAfter=true, bool printAfter=true) |

| Utilities for targets to add passes to the pass manager. More... | |

| void | addPass (Pass *P, bool verifyAfter=true, bool printAfter=true) |

| Add a pass to the PassManager if that pass is supposed to be run, as determined by the StartAfter and StopAfter options. More... | |

| FunctionPass * | createRegAllocPass (bool Optimized) |

| addMachinePasses helper to create the target-selected or overriden regalloc pass. More... | |

Protected Member Functions inherited from llvm::ModulePass Protected Member Functions inherited from llvm::ModulePass | |

| bool | skipModule (Module &M) const |

| Optional passes call this function to check whether the pass should be skipped. More... | |

Protected Attributes | |

| LLVMTargetMachine * | TM |

| PassConfigImpl * | Impl = nullptr |

| bool | Initialized = false |

| bool | DisableVerify = false |

| bool | EnableTailMerge = true |

| Default setting for -enable-tail-merge on this target. More... | |

| bool | RequireCodeGenSCCOrder = false |

| Require processing of functions such that callees are generated before callers. More... | |

Detailed Description

Target-Independent Code Generator Pass Configuration Options.

This is an ImmutablePass solely for the purpose of exposing CodeGen options to the internals of other CodeGen passes.

Definition at line 86 of file TargetPassConfig.h.

Constructor & Destructor Documentation

◆ TargetPassConfig() [1/2]

| TargetPassConfig::TargetPassConfig | ( | LLVMTargetMachine & | TM, |

| PassManagerBase & | pm | ||

| ) |

Definition at line 392 of file TargetPassConfig.cpp.

References EnableIPRA, llvm::TargetOptions::EnableIPRA, llvm::cl::Option::getNumOccurrences(), llvm::PassRegistry::getPassRegistry(), llvm::cl::opt_storage< DataType, ExternalStorage, std::is_class< DataType >::value >::getValue(), llvm::TargetOptions::GlobalISelAbort, if(), Impl, llvm::initializeAAResultsWrapperPassPass(), llvm::initializeBasicAAWrapperPassPass(), llvm::initializeCodeGen(), llvm::TargetMachine::Options, llvm::TargetOptions::PrintMachineCode, setRequiresCodeGenSCCOrder(), TM, and llvm::LLVMTargetMachine::useIPRA().

◆ TargetPassConfig() [2/2]

| TargetPassConfig::TargetPassConfig | ( | ) |

Definition at line 448 of file TargetPassConfig.cpp.

References llvm::report_fatal_error().

Referenced by llvm::LLVMTargetMachine::createPassConfig().

◆ ~TargetPassConfig()

|

override |

Definition at line 327 of file TargetPassConfig.cpp.

Member Function Documentation

◆ addBlockPlacement()

|

protectedvirtual |

Add standard basic block placement passes.

Definition at line 1206 of file TargetPassConfig.cpp.

References addPass(), EnableBlockPlacementStats, llvm::MachineBlockPlacementID, and llvm::MachineBlockPlacementStatsID.

Referenced by addMachinePasses().

◆ addCodeGenPrepare()

|

virtual |

Add pass to prepare the LLVM IR for code generation.

This should be done before exception handling preparation passes.

Definition at line 725 of file TargetPassConfig.cpp.

References addPass(), llvm::createCodeGenPreparePass(), llvm::createRewriteSymbolsPass(), DisableCGP, getOptLevel(), and llvm::CodeGenOpt::None.

Referenced by addISelPasses(), llvm::ARMBaseTargetMachine::createPassConfig(), and llvm::GCNTargetMachine::getTargetTransformInfo().

◆ addCoreISelPasses()

|

protected |

Add the actual instruction selection passes.

This does not include preparation passes on IR.

Definition at line 755 of file TargetPassConfig.cpp.

References addGlobalInstructionSelect(), addInstSelector(), addIRTranslator(), addLegalizeMachineIR(), addPass(), addPreGlobalInstructionSelect(), addPreLegalizeMachineIR(), addPreRegBankSelect(), addRegBankSelect(), llvm::cl::BOU_FALSE, llvm::cl::BOU_TRUE, llvm::createResetMachineFunctionPass(), llvm::TargetOptions::EnableGlobalISel, llvm::TargetMachine::getO0WantsFastISel(), llvm::TargetMachine::getOptLevel(), isGlobalISelAbortEnabled(), llvm::CodeGenOpt::None, llvm::TargetMachine::Options, reportDiagnosticWhenGlobalISelFallback(), llvm::TargetMachine::setFastISel(), llvm::TargetMachine::setGlobalISel(), llvm::TargetMachine::setO0WantsFastISel(), and TM.

Referenced by addISelPasses().

◆ addFastRegAlloc()

|

protectedvirtual |

addFastRegAlloc - Add the minimum set of target-independent passes that are required for fast register allocation.

Add the minimum set of target-independent passes that are required for register allocation.

No coalescing or scheduling.

Definition at line 1109 of file TargetPassConfig.cpp.

References addPass(), llvm::PHIEliminationID, and llvm::TwoAddressInstructionPassID.

Referenced by addMachinePasses(), and llvm::R600TargetMachine::createPassConfig().

◆ addGCPasses()

|

protectedvirtual |

addGCPasses - Add late codegen passes that analyze code for garbage collection.

Add standard GC passes.

This should return true if GC info should be printed after these passes.

Definition at line 1200 of file TargetPassConfig.cpp.

References addPass(), and llvm::GCMachineCodeAnalysisID.

Referenced by addMachinePasses().

◆ addGlobalInstructionSelect()

|

inlinevirtual |

This method should install a (global) instruction selector pass, which converts possibly generic instructions to fully target-specific instructions, thereby constraining all generic virtual registers to register classes.

Definition at line 274 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addILPOpts()

|

inlineprotectedvirtual |

Add passes that optimize instruction level parallelism for out-of-order targets.

These passes are run while the machine code is still in SSA form, so they can use MachineTraceMetrics to control their heuristics.

All passes added here should preserve the MachineDominatorTree, MachineLoopInfo, and MachineTraceMetrics analyses.

Definition at line 349 of file TargetPassConfig.h.

Referenced by addMachineSSAOptimization(), and llvm::R600TargetMachine::createPassConfig().

◆ addInstSelector()

|

inlinevirtual |

addInstSelector - This method should install an instruction selector pass, which converts from LLVM code to machine instructions.

Definition at line 241 of file TargetPassConfig.h.

Referenced by addCoreISelPasses(), and llvm::WebAssemblyTargetMachine::createPassConfig().

◆ addIRPasses()

|

virtual |

Add common target configurable passes that perform LLVM IR to IR transforms following machine independent optimization.

Definition at line 607 of file TargetPassConfig.cpp.

References addPass(), Andersen, Both, llvm::createBasicAAWrapperPass(), llvm::createCFLAndersAAWrapperPass(), llvm::createCFLSteensAAWrapperPass(), llvm::createConstantHoistingPass(), llvm::createExpandMemCmpPass(), llvm::createExpandReductionsPass(), llvm::createGCLoweringPass(), llvm::createLoopStrengthReducePass(), llvm::createMergeICmpsPass(), llvm::createPartiallyInlineLibCallsPass(), llvm::createPostInlineEntryExitInstrumenterPass(), llvm::createPrintFunctionPass(), llvm::createScalarizeMaskedMemIntrinPass(), llvm::createScopedNoAliasAAWrapperPass(), llvm::createShadowStackGCLoweringPass(), llvm::createTypeBasedAAWrapperPass(), llvm::createUnreachableBlockEliminationPass(), llvm::createVerifierPass(), llvm::dbgs(), DisableConstantHoisting, DisableLSR, DisableMergeICmps, DisablePartialLibcallInlining, DisableVerify, getOptLevel(), llvm::CodeGenOpt::None, PrintLSR, and Steensgaard.

Referenced by addISelPasses(), llvm::RISCVTargetMachine::createPassConfig(), llvm::SparcTargetMachine::createPassConfig(), llvm::WebAssemblyTargetMachine::createPassConfig(), llvm::HexagonTargetMachine::createPassConfig(), llvm::XCoreTargetMachine::createPassConfig(), llvm::AArch64TargetMachine::createPassConfig(), llvm::PPCTargetMachine::createPassConfig(), llvm::X86TargetMachine::createPassConfig(), llvm::ARMBaseTargetMachine::createPassConfig(), llvm::MipsTargetMachine::createPassConfig(), llvm::NVPTXTargetMachine::getTargetTransformInfo(), llvm::GCNTargetMachine::getTargetTransformInfo(), and llvm::SystemZTargetMachine::SystemZTargetMachine().

◆ addIRTranslator()

|

inlinevirtual |

This method should install an IR translator pass, which converts from LLVM code to machine instructions with possibly generic opcodes.

Definition at line 247 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addISelPasses()

| bool TargetPassConfig::addISelPasses | ( | ) |

High level function that adds all passes necessary to go from llvm IR representation to the MI representation.

Adds IR based lowering and target specific optimization passes and finally the core instruction selection passes.

- Returns

- true if an error occurred, false otherwise.

Definition at line 821 of file TargetPassConfig.cpp.

References addCodeGenPrepare(), addCoreISelPasses(), addIRPasses(), addISelPrepare(), addPass(), addPassesToHandleExceptions(), llvm::createLowerEmuTLSPass(), llvm::createPreISelIntrinsicLoweringPass(), llvm::createTargetTransformInfoWrapperPass(), llvm::TargetMachine::getTargetIRAnalysis(), TM, and llvm::TargetMachine::useEmulatedTLS().

Referenced by addPassesToGenerateCode().

◆ addISelPrepare()

|

virtual |

Add common passes that perform LLVM IR to IR transforms in preparation for instruction selection.

Definition at line 733 of file TargetPassConfig.cpp.

References addPass(), addPreISel(), llvm::createPrintFunctionPass(), llvm::createSafeStackPass(), llvm::createStackProtectorPass(), llvm::createVerifierPass(), llvm::dbgs(), DisableVerify, PrintISelInput, and requiresCodeGenSCCOrder().

Referenced by addISelPasses().

◆ addLegalizeMachineIR()

|

inlinevirtual |

This method should install a legalize pass, which converts the instruction sequence into one that can be selected by the target.

Definition at line 255 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addMachineLateOptimization()

|

protectedvirtual |

Add passes that optimize machine instructions after register allocation.

Post RegAlloc Pass Configuration.

Add passes that optimize machine instructions after register allocation.

Definition at line 1184 of file TargetPassConfig.cpp.

References addPass(), llvm::BranchFolderPassID, llvm::MachineCopyPropagationID, llvm::TargetMachine::requiresStructuredCFG(), llvm::TailDuplicateID, and TM.

Referenced by addMachinePasses().

◆ addMachinePasses()

|

virtual |

Add the complete, standard set of LLVM CodeGen passes.

Add the complete set of target-independent postISel code generator passes.

Fully developed targets will not generally override this.

This can be read as the standard order of major LLVM CodeGen stages. Stages with nontrivial configuration or multiple passes are broken out below in addStage routines.

Any TargetPassConfig::addXX routine may be overriden by the Target. The addPre/Post methods with empty header implementations allow injecting target-specific fixups just before or after major stages. Additionally, targets have the flexibility to change pass order within a stage by overriding default implementation of addStage routines below. Each technique has maintainability tradeoffs because alternate pass orders are not well supported. addPre/Post works better if the target pass is easily tied to a common pass. But if it has subtle dependencies on multiple passes, the target should override the stage instead.

TODO: We could use a single addPre/Post(ID) hook to allow pass injection before/after any target-independent pass. But it's currently overkill.

Add passes that optimize machine instructions after register allocation.

Definition at line 860 of file TargetPassConfig.cpp.

References addBlockPlacement(), addFastRegAlloc(), addGCPasses(), addMachineLateOptimization(), addMachineSSAOptimization(), addOptimizedRegAlloc(), addPass(), addPostRegAlloc(), addPreEmitPass(), addPreEmitPass2(), addPreRegAlloc(), addPreSched2(), AlwaysOutline, assert(), llvm::createFastRegisterAllocator(), llvm::createGCInfoPrinter(), llvm::createMachineOutlinerPass(), llvm::createPrologEpilogInserterPass(), createRegAllocPass(), llvm::createRegUsageInfoCollector(), llvm::createRegUsageInfoPropPass(), llvm::dbgs(), EnableImplicitNullChecks, llvm::TargetOptions::EnableIPRA, llvm::TargetOptions::EnableMachineOutliner, llvm::StringRef::equals(), llvm::ExpandISelPseudosID, llvm::ExpandPostRAPseudosID, llvm::FEntryInserterID, llvm::FuncletLayoutID, getOptimizeRegAlloc(), getOptLevel(), llvm::PassRegistry::getPassInfo(), getPassInfo(), llvm::PassRegistry::getPassRegistry(), llvm::PassInfo::getTypeInfo(), llvm::cl::opt_storage< DataType, ExternalStorage, std::is_class< DataType >::value >::getValue(), llvm::ImplicitNullChecksID, insertPass(), isPassSubstitutedOrOverridden(), llvm::LiveDebugValuesID, llvm::LocalStackSlotAllocationID, NeverOutline, llvm::CodeGenOpt::None, llvm::TargetMachine::Options, llvm::PatchableFunctionID, llvm::PostMachineSchedulerID, llvm::PostRAMachineSinkingID, llvm::PostRASchedulerID, printAndVerify(), PrintGCInfo, llvm::PrologEpilogCodeInserterID, llvm::report_fatal_error(), llvm::ShrinkWrapID, llvm::StackMapLivenessID, llvm::TargetOptions::SupportsDefaultOutlining, llvm::TargetMachine::targetSchedulesPostRAScheduling(), TM, useDefaultRegisterAllocator(), and llvm::XRayInstrumentationID.

Referenced by addPassesToGenerateCode().

◆ addMachineSSAOptimization()

|

protectedvirtual |

addMachineSSAOptimization - Add standard passes that optimize machine instructions in SSA form.

Add passes that optimize machine instructions in SSA form.

Definition at line 991 of file TargetPassConfig.cpp.

References addILPOpts(), addPass(), llvm::DeadMachineInstructionElimID, llvm::EarlyMachineLICMID, llvm::EarlyTailDuplicateID, llvm::LocalStackSlotAllocationID, llvm::MachineCSEID, llvm::MachineSinkingID, llvm::OptimizePHIsID, llvm::PeepholeOptimizerID, and llvm::StackColoringID.

Referenced by addMachinePasses(), llvm::BPFTargetMachine::createPassConfig(), llvm::PPCTargetMachine::createPassConfig(), llvm::X86TargetMachine::createPassConfig(), and llvm::R600TargetMachine::createPassConfig().

◆ addOptimizedRegAlloc()

|

protectedvirtual |

addOptimizedRegAlloc - Add passes related to register allocation.

Add standard target-independent passes that are tightly coupled with optimized register allocation, including coalescing, machine instruction scheduling, and register allocation itself.

LLVMTargetMachine provides standard regalloc passes for most targets.

Definition at line 1120 of file TargetPassConfig.cpp.

References addPass(), addPreRewrite(), llvm::DetectDeadLanesID, llvm::LiveIntervalsID, llvm::LiveVariablesID, llvm::MachineCopyPropagationID, llvm::MachineLICMID, llvm::MachineLoopInfoID, llvm::MachineSchedulerID, llvm::PHIEliminationID, llvm::ProcessImplicitDefsID, llvm::RegisterCoalescerID, llvm::RenameIndependentSubregsID, llvm::StackSlotColoringID, llvm::TwoAddressInstructionPassID, and llvm::VirtRegRewriterID.

Referenced by addMachinePasses(), and llvm::R600TargetMachine::createPassConfig().

◆ addPass() [1/2]

|

protected |

Utilities for targets to add passes to the pass manager.

Add a CodeGen pass at this point in the pipeline after checking for target and command line overrides.

Add a CodeGen pass at this point in the pipeline after checking overrides. Return the pass that was added, or zero if no pass was added. printAfter if true and adding a machine function pass add an extra machine printer pass afterwards verifyAfter if true and adding a machine function pass add an extra machine verification pass afterwards.

addPass cannot return a pointer to the pass instance because is internal the PassManager and the instance we create here may already be freed.

Definition at line 564 of file TargetPassConfig.cpp.

References llvm::Pass::createPass(), llvm::IdentifyingPassPtr::getID(), llvm::IdentifyingPassPtr::getInstance(), llvm::Pass::getPassID(), getPassSubstitution(), llvm::IdentifyingPassPtr::isInstance(), llvm::IdentifyingPassPtr::isValid(), llvm_unreachable, overridePass(), and P.

Referenced by addBlockPlacement(), addCodeGenPrepare(), addCoreISelPasses(), addFastRegAlloc(), addGCPasses(), addIRPasses(), addISelPasses(), addISelPrepare(), addMachineLateOptimization(), addMachinePasses(), addMachineSSAOptimization(), addOptimizedRegAlloc(), addPass(), and addPassesToHandleExceptions().

◆ addPass() [2/2]

|

protected |

Add a pass to the PassManager if that pass is supposed to be run, as determined by the StartAfter and StopAfter options.

Add a pass to the PassManager if that pass is supposed to be run.

Takes ownership of the pass. printAfter if true and adding a machine function pass add an extra machine printer pass afterwards verifyAfter if true and adding a machine function pass add an extra machine verification pass afterwards.

If the Started/Stopped flags indicate either that the compilation should start at a later pass or that it should stop after an earlier pass, then do not add the pass. Finally, compare the current pass against the StartAfter and StopAfter options and change the Started/Stopped flags accordingly.

Definition at line 515 of file TargetPassConfig.cpp.

References llvm::legacy::PassManagerBase::add(), addPass(), addPrintPass(), addVerifyPass(), assert(), llvm::Pass::getPassID(), llvm::Pass::getPassName(), Impl, Initialized, llvm::PassConfigImpl::InsertedPasses, P, and llvm::report_fatal_error().

◆ addPassesToHandleExceptions()

| void TargetPassConfig::addPassesToHandleExceptions | ( | ) |

Add passes to lower exception handling for the code generator.

Turn exception handling constructs into something the code generators can handle.

Definition at line 682 of file TargetPassConfig.cpp.

References addPass(), llvm::ARM, assert(), llvm::createDwarfEHPass(), llvm::createLowerInvokePass(), llvm::createSjLjEHPreparePass(), llvm::createUnreachableBlockEliminationPass(), llvm::createWasmEHPass(), llvm::createWinEHPass(), llvm::DwarfCFI, llvm::MCAsmInfo::getExceptionHandlingType(), llvm::TargetMachine::getMCAsmInfo(), LLVM_FALLTHROUGH, llvm::None, llvm::SjLj, TM, llvm::Wasm, and llvm::WinEH.

Referenced by addISelPasses().

◆ addPostRegAlloc()

|

inlineprotectedvirtual |

This method may be implemented by targets that want to run passes after register allocation pass pipeline but before prolog-epilog insertion.

Definition at line 383 of file TargetPassConfig.h.

Referenced by addMachinePasses(), llvm::WebAssemblyTargetMachine::createPassConfig(), and llvm::R600TargetMachine::createPassConfig().

◆ addPreEmitPass()

|

inlineprotectedvirtual |

This pass may be implemented by targets that want to run passes immediately before machine code is emitted.

Definition at line 402 of file TargetPassConfig.h.

Referenced by addMachinePasses(), and llvm::WebAssemblyTargetMachine::createPassConfig().

◆ addPreEmitPass2()

|

inlineprotectedvirtual |

Targets may add passes immediately before machine code is emitted in this callback.

This is called even later than addPreEmitPass.

Definition at line 409 of file TargetPassConfig.h.

References P.

Referenced by addMachinePasses().

◆ addPreGlobalInstructionSelect()

|

inlinevirtual |

This method may be implemented by targets that want to run passes immediately before the (global) instruction selection.

Definition at line 268 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addPreISel()

|

inlineprotectedvirtual |

Methods with trivial inline returns are convenient points in the common codegen pass pipeline where targets may insert passes.

Methods with out-of-line standard implementations are major CodeGen stages called by addMachinePasses. Some targets may override major stages when inserting passes is insufficient, but maintaining overriden stages is more work.addPreISelPasses - This method should add any "last minute" LLVM->LLVM passes (which are run just before instruction selector).

Definition at line 335 of file TargetPassConfig.h.

Referenced by addISelPrepare().

◆ addPreLegalizeMachineIR()

|

inlinevirtual |

This method may be implemented by targets that want to run passes immediately before legalization.

Definition at line 251 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addPreRegAlloc()

|

inlineprotectedvirtual |

This method may be implemented by targets that want to run passes immediately before register allocation.

Definition at line 355 of file TargetPassConfig.h.

Referenced by addMachinePasses().

◆ addPreRegBankSelect()

|

inlinevirtual |

This method may be implemented by targets that want to run passes immediately before the register bank selection.

Definition at line 259 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addPreRewrite()

|

inlineprotectedvirtual |

addPreRewrite - Add passes to the optimized register allocation pipeline after register allocation is complete, but before virtual registers are rewritten to physical registers.

These passes must preserve VirtRegMap and LiveIntervals, and when running after RABasic or RAGreedy, they should take advantage of LiveRegMatrix. When these passes run, VirtRegMap contains legal physreg assignments for all virtual registers.

Definition at line 377 of file TargetPassConfig.h.

Referenced by addOptimizedRegAlloc().

◆ addPreSched2()

|

inlineprotectedvirtual |

This method may be implemented by targets that want to run passes after prolog-epilog insertion and before the second instruction scheduling pass.

Definition at line 390 of file TargetPassConfig.h.

Referenced by addMachinePasses().

◆ addPrintPass()

| void TargetPassConfig::addPrintPass | ( | const std::string & | Banner | ) |

Add a pass to print the machine function if printing is enabled.

Definition at line 590 of file TargetPassConfig.cpp.

References llvm::legacy::PassManagerBase::add(), llvm::createMachineFunctionPrinterPass(), llvm::dbgs(), llvm::TargetMachine::shouldPrintMachineCode(), and TM.

Referenced by addPass(), and printAndVerify().

◆ addRegBankSelect()

|

inlinevirtual |

This method should install a register bank selector pass, which assigns register banks to virtual registers without a register class or register banks.

Definition at line 264 of file TargetPassConfig.h.

Referenced by addCoreISelPasses().

◆ addVerifyPass()

| void TargetPassConfig::addVerifyPass | ( | const std::string & | Banner | ) |

Add a pass to perform basic verification of the machine function if verification is enabled.

Definition at line 595 of file TargetPassConfig.cpp.

References llvm::legacy::PassManagerBase::add(), llvm::cl::BOU_TRUE, llvm::cl::BOU_UNSET, llvm::createMachineVerifierPass(), llvm::LLVMTargetMachine::isMachineVerifierClean(), TM, Verify, and VerifyMachineCode.

Referenced by addPass(), and printAndVerify().

◆ createPostMachineScheduler()

|

inlinevirtual |

Similar to createMachineScheduler but used when postRA machine scheduling is enabled.

Definition at line 297 of file TargetPassConfig.h.

◆ createRegAllocPass()

|

protected |

addMachinePasses helper to create the target-selected or overriden regalloc pass.

Find and instantiate the register allocation pass requested by this target at the current optimization level.

Different register allocators are defined as separate passes because they may require different analysis.

This helper ensures that the regalloc= option is always available, even for targets that override the default allocator.

FIXME: When MachinePassRegistry register pass IDs instead of function ptrs, this can be folded into addPass.

Definition at line 1088 of file TargetPassConfig.cpp.

References llvm::call_once(), createTargetRegisterAllocator(), llvm::RegisterRegAlloc::getDefault(), initializeDefaultRegisterAllocatorOnce(), and useDefaultRegisterAllocator().

Referenced by addMachinePasses().

◆ createTargetRegisterAllocator()

|

protectedvirtual |

createTargetRegisterAllocator - Create the register allocator pass for this target at the current optimization level.

Instantiate the default register allocator pass for this target for either the optimized or unoptimized allocation path.

This will be added to the pass manager by addFastRegAlloc in the unoptimized case or addOptimizedRegAlloc in the optimized case.

A target that uses the standard regalloc pass order for fast or optimized allocation may still override this for per-target regalloc selection. But -regalloc=... always takes precedence.

Definition at line 1072 of file TargetPassConfig.cpp.

References llvm::createFastRegisterAllocator(), and llvm::createGreedyRegisterAllocator().

Referenced by createRegAllocPass().

◆ default()

|

inline |

Create an instance of ScheduleDAGInstrs to be run within the standard MachineScheduler pass for this function and target at the current optimization level.

This can also be used to plug a new MachineSchedStrategy into an instance of the standard ScheduleDAGMI: return new ScheduleDAGMI(C, make_unique<MyStrategy>(C), /*RemoveKillFlags=

Definition at line 288 of file TargetPassConfig.h.

◆ disablePass()

|

inline |

Allow the target to disable a specific standard pass by default.

Definition at line 198 of file TargetPassConfig.h.

◆ enablePass()

|

inline |

Allow the target to enable a specific standard pass by default.

Definition at line 195 of file TargetPassConfig.h.

◆ getEnableTailMerge()

|

inline |

Definition at line 177 of file TargetPassConfig.h.

Referenced by getLayoutSuccessorProbThreshold(), and INITIALIZE_PASS().

◆ getLimitedCodeGenPipelineReason()

If hasLimitedCodeGenPipeline is true, this method returns a string with the name of the options, separated by Separator that caused this pipeline to be limited.

Definition at line 465 of file TargetPassConfig.cpp.

References llvm::empty(), hasLimitedCodeGenPipeline(), StartAfterOpt, StartAfterOptName, StartBeforeOpt, StartBeforeOptName, StopAfterOpt, StopAfterOptName, and StopBeforeOpt.

◆ getOptimizeRegAlloc()

| bool TargetPassConfig::getOptimizeRegAlloc | ( | ) | const |

Return true if the optimized regalloc pipeline is enabled.

Register Allocation Pass Configuration.

Definition at line 1033 of file TargetPassConfig.cpp.

References llvm::cl::BOU_FALSE, llvm::cl::BOU_TRUE, llvm::cl::BOU_UNSET, getOptLevel(), llvm_unreachable, llvm::CodeGenOpt::None, OptimizeRegAlloc, and llvm::RegisterRegAlloc::Registry.

Referenced by addMachinePasses().

◆ getOptLevel()

| CodeGenOpt::Level TargetPassConfig::getOptLevel | ( | ) | const |

Definition at line 423 of file TargetPassConfig.cpp.

References llvm::TargetMachine::getOptLevel(), and TM.

Referenced by addCodeGenPrepare(), addIRPasses(), addMachinePasses(), getLayoutSuccessorProbThreshold(), getOptimizeRegAlloc(), INITIALIZE_PASS(), and llvm::Legalizer::runOnMachineFunction().

◆ getPassSubstitution()

| IdentifyingPassPtr TargetPassConfig::getPassSubstitution | ( | AnalysisID | StandardID | ) | const |

Return the pass substituted for StandardID by the target.

If no substitution exists, return StandardID.

Definition at line 495 of file TargetPassConfig.cpp.

References I, Impl, and llvm::PassConfigImpl::TargetPasses.

Referenced by addPass(), and isPassSubstitutedOrOverridden().

◆ getTM()

|

inline |

Get the right type of TargetMachine for this target.

Definition at line 152 of file TargetPassConfig.h.

References llvm::SystemZISD::TM.

Referenced by llvm::createFalkorMarkStridedAccessesPass().

◆ hasLimitedCodeGenPipeline()

|

static |

Returns true if one of the -start-after, -start-before, -stop-after or -stop-before options is set.

Definition at line 459 of file TargetPassConfig.cpp.

References StartAfterOpt, StartBeforeOpt, and willCompleteCodeGenPipeline().

Referenced by getLimitedCodeGenPipelineReason().

◆ insertPass()

| void TargetPassConfig::insertPass | ( | AnalysisID | TargetPassID, |

| IdentifyingPassPtr | InsertedPassID, | ||

| bool | VerifyAfter = true, |

||

| bool | PrintAfter = true |

||

| ) |

Insert InsertedPassID pass after TargetPassID pass.

Insert InsertedPassID pass after TargetPassID.

Definition at line 428 of file TargetPassConfig.cpp.

References assert(), llvm::SmallVectorImpl< T >::emplace_back(), llvm::IdentifyingPassPtr::getID(), llvm::IdentifyingPassPtr::getInstance(), llvm::Pass::getPassID(), Impl, llvm::PassConfigImpl::InsertedPasses, and llvm::IdentifyingPassPtr::isInstance().

Referenced by addMachinePasses().

◆ isGlobalISelAbortEnabled()

| bool TargetPassConfig::isGlobalISelAbortEnabled | ( | ) | const |

Check whether or not GlobalISel should abort on error.

GlobalISel Configuration.

When this is disabled, GlobalISel will fall back on SDISel instead of erroring out.

Definition at line 1217 of file TargetPassConfig.cpp.

References llvm::Enable, llvm::TargetOptions::GlobalISelAbort, llvm::TargetMachine::Options, and TM.

Referenced by addCoreISelPasses(), llvm::RegBankSelect::getAnalysisUsage(), and llvm::reportGISelFailure().

◆ isPassSubstitutedOrOverridden()

| bool TargetPassConfig::isPassSubstitutedOrOverridden | ( | AnalysisID | ID | ) | const |

Return true if the pass has been substituted by the target or overridden on the command line.

Definition at line 503 of file TargetPassConfig.cpp.

References llvm::IdentifyingPassPtr::getID(), getPassSubstitution(), ID, llvm::IdentifyingPassPtr::isInstance(), llvm::IdentifyingPassPtr::isValid(), and overridePass().

Referenced by addMachinePasses().

◆ printAndVerify()

| void TargetPassConfig::printAndVerify | ( | const std::string & | Banner | ) |

printAndVerify - Add a pass to dump then verify the machine function, if those steps are enabled.

Definition at line 585 of file TargetPassConfig.cpp.

References addPrintPass(), and addVerifyPass().

Referenced by addMachinePasses().

◆ reportDiagnosticWhenGlobalISelFallback()

|

virtual |

Check whether or not a diagnostic should be emitted when GlobalISel uses the fallback path.

In other words, it will emit a diagnostic when GlobalISel failed and isGlobalISelAbortEnabled is false.

Definition at line 1221 of file TargetPassConfig.cpp.

References llvm::DisableWithDiag, llvm::TargetOptions::GlobalISelAbort, llvm::TargetMachine::Options, and TM.

Referenced by addCoreISelPasses().

◆ requiresCodeGenSCCOrder()

|

inline |

Definition at line 180 of file TargetPassConfig.h.

Referenced by addISelPrepare().

◆ setDisableVerify()

|

inline |

Definition at line 175 of file TargetPassConfig.h.

Referenced by addPassesToGenerateCode().

◆ setEnableTailMerge()

|

inline |

Definition at line 178 of file TargetPassConfig.h.

◆ setInitialized()

|

inline |

Definition at line 157 of file TargetPassConfig.h.

Referenced by addPassesToGenerateCode().

◆ setOpt()

Definition at line 485 of file TargetPassConfig.cpp.

References assert(), and Initialized.

◆ setRequiresCodeGenSCCOrder()

Definition at line 181 of file TargetPassConfig.h.

References Enable, and PrintAfter().

Referenced by TargetPassConfig().

◆ substitutePass()

| void TargetPassConfig::substitutePass | ( | AnalysisID | StandardID, |

| IdentifyingPassPtr | TargetID | ||

| ) |

Allow the target to override a specific pass without overriding the pass pipeline.

When passes are added to the standard pipeline at the point where StandardID is expected, add TargetID in its place.

Definition at line 490 of file TargetPassConfig.cpp.

References Impl, and llvm::PassConfigImpl::TargetPasses.

◆ usingDefaultRegAlloc()

| bool TargetPassConfig::usingDefaultRegAlloc | ( | ) | const |

Return true if the default global register allocator is in use and has not be overriden on the command line with '-regalloc=...'.

Definition at line 1103 of file TargetPassConfig.cpp.

◆ willCompleteCodeGenPipeline()

|

static |

Returns true if none of the -stop-before and -stop-after options is set.

Definition at line 455 of file TargetPassConfig.cpp.

References StopAfterOpt, and StopBeforeOpt.

Referenced by llvm::LLVMTargetMachine::addPassesToEmitFile(), llvm::LLVMTargetMachine::addPassesToEmitMC(), and hasLimitedCodeGenPipeline().

Member Data Documentation

◆ DisableVerify

Definition at line 129 of file TargetPassConfig.h.

Referenced by addIRPasses(), and addISelPrepare().

◆ EnableTailMerge

Default setting for -enable-tail-merge on this target.

Definition at line 132 of file TargetPassConfig.h.

◆ ID

|

static |

Definition at line 149 of file TargetPassConfig.h.

Referenced by isPassSubstitutedOrOverridden(), and overridePass().

◆ Impl

|

protected |

Definition at line 124 of file TargetPassConfig.h.

Referenced by addPass(), getPassSubstitution(), insertPass(), substitutePass(), and TargetPassConfig().

◆ Initialized

Definition at line 125 of file TargetPassConfig.h.

◆ RequireCodeGenSCCOrder

Require processing of functions such that callees are generated before callers.

Definition at line 136 of file TargetPassConfig.h.

◆ TM

|

protected |

Definition at line 123 of file TargetPassConfig.h.

Referenced by addCoreISelPasses(), addISelPasses(), addMachineLateOptimization(), addMachinePasses(), addPassesToHandleExceptions(), addPrintPass(), addVerifyPass(), getOptLevel(), isGlobalISelAbortEnabled(), reportDiagnosticWhenGlobalISelFallback(), and TargetPassConfig().

The documentation for this class was generated from the following files:

- include/llvm/CodeGen/TargetPassConfig.h

- lib/CodeGen/TargetPassConfig.cpp

1.8.13

1.8.13