ScheduleDAGSDNodes - A ScheduleDAG for scheduling SDNode-based DAGs. More...

#include "CodeGen/SelectionDAG/ScheduleDAGSDNodes.h"

Classes | |

| class | RegDefIter |

| RegDefIter - In place iteration over the values defined by an SUnit. More... | |

Public Member Functions | |

| ScheduleDAGSDNodes (MachineFunction &mf) | |

| ~ScheduleDAGSDNodes () override=default | |

| void | Run (SelectionDAG *dag, MachineBasicBlock *bb) |

| Run - perform scheduling. More... | |

| SUnit * | newSUnit (SDNode *N) |

| NewSUnit - Creates a new SUnit and return a ptr to it. More... | |

| SUnit * | Clone (SUnit *Old) |

| Clone - Creates a clone of the specified SUnit. More... | |

| void | BuildSchedGraph (AliasAnalysis *AA) |

| BuildSchedGraph - Build the SUnit graph from the selection dag that we are input. More... | |

| void | InitNumRegDefsLeft (SUnit *SU) |

| InitNumRegDefsLeft - Determine the # of regs defined by this node. More... | |

| virtual void | computeLatency (SUnit *SU) |

| computeLatency - Compute node latency. More... | |

| virtual void | computeOperandLatency (SDNode *Def, SDNode *Use, unsigned OpIdx, SDep &dep) const |

| virtual void | Schedule ()=0 |

| Schedule - Order nodes according to selected style, filling in the Sequence member. More... | |

| void | VerifyScheduledSequence (bool isBottomUp) |

| VerifyScheduledSequence - Verify that all SUnits are scheduled and consistent with the Sequence of scheduled instructions. More... | |

| virtual MachineBasicBlock * | EmitSchedule (MachineBasicBlock::iterator &InsertPos) |

| EmitSchedule - Insert MachineInstrs into the MachineBasicBlock according to the order specified in Sequence. More... | |

| void | dumpNode (const SUnit &SU) const override |

| void | dump () const override |

| void | dumpSchedule () const |

| std::string | getGraphNodeLabel (const SUnit *SU) const override |

| Returns a label for an SUnit node in a visualization of the ScheduleDAG. More... | |

| std::string | getDAGName () const override |

| Return the basic block label. More... | |

| virtual void | getCustomGraphFeatures (GraphWriter< ScheduleDAG *> &GW) const |

Public Member Functions inherited from llvm::ScheduleDAG Public Member Functions inherited from llvm::ScheduleDAG | |

| ScheduleDAG (MachineFunction &mf) | |

| virtual | ~ScheduleDAG () |

| void | clearDAG () |

| Clears the DAG state (between regions). More... | |

| const MCInstrDesc * | getInstrDesc (const SUnit *SU) const |

| Returns the MCInstrDesc of this SUnit. More... | |

| virtual void | viewGraph (const Twine &Name, const Twine &Title) |

| Pops up a GraphViz/gv window with the ScheduleDAG rendered using 'dot'. More... | |

| virtual void | viewGraph () |

| Out-of-line implementation with no arguments is handy for gdb. More... | |

| void | dumpNodeName (const SUnit &SU) const |

| virtual void | addCustomGraphFeatures (GraphWriter< ScheduleDAG *> &) const |

| Adds custom features for a visualization of the ScheduleDAG. More... | |

| unsigned | VerifyScheduledDAG (bool isBottomUp) |

| Verifies that all SUnits were scheduled and that their state is consistent. More... | |

Static Public Member Functions | |

| static bool | isPassiveNode (SDNode *Node) |

| isPassiveNode - Return true if the node is a non-scheduled leaf. More... | |

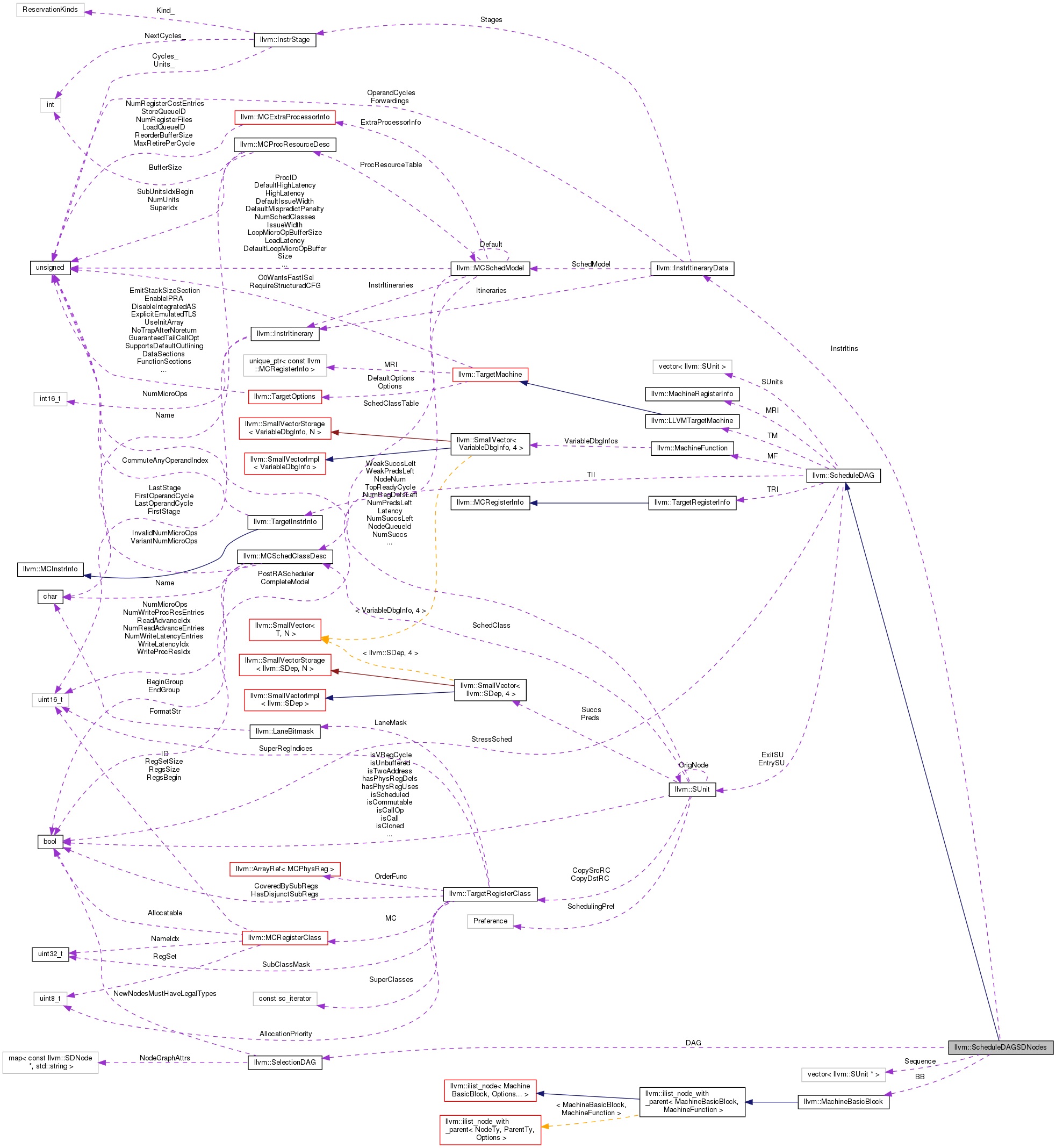

Public Attributes | |

| MachineBasicBlock * | BB |

| SelectionDAG * | DAG |

| const InstrItineraryData * | InstrItins |

| std::vector< SUnit * > | Sequence |

| The schedule. Null SUnit*'s represent noop instructions. More... | |

Public Attributes inherited from llvm::ScheduleDAG Public Attributes inherited from llvm::ScheduleDAG | |

| const LLVMTargetMachine & | TM |

| Target processor. More... | |

| const TargetInstrInfo * | TII |

| Target instruction information. More... | |

| const TargetRegisterInfo * | TRI |

| Target processor register info. More... | |

| MachineFunction & | MF |

| Machine function. More... | |

| MachineRegisterInfo & | MRI |

| Virtual/real register map. More... | |

| std::vector< SUnit > | SUnits |

| The scheduling units. More... | |

| SUnit | EntrySU |

| Special node for the region entry. More... | |

| SUnit | ExitSU |

| Special node for the region exit. More... | |

| bool | StressSched |

Protected Member Functions | |

| virtual bool | forceUnitLatencies () const |

| ForceUnitLatencies - Return true if all scheduling edges should be given a latency value of one. More... | |

Protected Member Functions inherited from llvm::ScheduleDAG Protected Member Functions inherited from llvm::ScheduleDAG | |

| void | dumpNodeAll (const SUnit &SU) const |

Detailed Description

ScheduleDAGSDNodes - A ScheduleDAG for scheduling SDNode-based DAGs.

Edges between SUnits are initially based on edges in the SelectionDAG, and additional edges can be added by the schedulers as heuristics. SDNodes such as Constants, Registers, and a few others that are not interesting to schedulers are not allocated SUnits.

SDNodes with MVT::Glue operands are grouped along with the flagged nodes into a single SUnit so that they are scheduled together.

SDNode-based scheduling graphs do not use SDep::Anti or SDep::Output edges. Physical register dependence information is not carried in the DAG and must be handled explicitly by schedulers.

Definition at line 46 of file ScheduleDAGSDNodes.h.

Constructor & Destructor Documentation

◆ ScheduleDAGSDNodes()

|

explicit |

Definition at line 49 of file ScheduleDAGSDNodes.cpp.

◆ ~ScheduleDAGSDNodes()

|

overridedefault |

Member Function Documentation

◆ BuildSchedGraph()

| void ScheduleDAGSDNodes::BuildSchedGraph | ( | AliasAnalysis * | AA | ) |

BuildSchedGraph - Build the SUnit graph from the selection dag that we are input.

This SUnit graph is similar to the SelectionDAG, but excludes nodes that aren't interesting to scheduling, and represents flagged together nodes with a single SUnit.

This SUnit graph is similar to the SelectionDAG, but excludes nodes that aren't interesting to scheduling, and represents glued together nodes with a single SUnit.

Definition at line 513 of file ScheduleDAGSDNodes.cpp.

References llvm::ISD::CopyFromReg, llvm::SDNode::getMachineOpcode(), llvm::SDNode::getNumValues(), llvm::SDNode::getOpcode(), llvm::SDNode::getValueType(), llvm::SDNode::isMachineOpcode(), and llvm::MVT::Other.

◆ Clone()

Clone - Creates a clone of the specified SUnit.

It does not copy the predecessors / successors info nor the temporary scheduling states.

Definition at line 90 of file ScheduleDAGSDNodes.cpp.

References llvm::SUnit::getNode(), llvm::SUnit::hasPhysRegClobbers, llvm::SUnit::hasPhysRegDefs, llvm::SUnit::isCall, llvm::SUnit::isCallOp, llvm::SUnit::isCloned, llvm::SUnit::isCommutable, llvm::SUnit::isScheduleHigh, llvm::SUnit::isScheduleLow, llvm::SUnit::isTwoAddress, llvm::SUnit::isVRegCycle, llvm::SUnit::Latency, newSUnit(), llvm::SUnit::OrigNode, and llvm::SUnit::SchedulingPref.

◆ computeLatency()

|

virtual |

computeLatency - Compute node latency.

Definition at line 590 of file ScheduleDAGSDNodes.cpp.

References forceUnitLatencies(), llvm::SDNode::getGluedNode(), llvm::TargetInstrInfo::getInstrLatency(), llvm::SDNode::getMachineOpcode(), llvm::SUnit::getNode(), llvm::SDNode::getOpcode(), HighLatencyCycles, InstrItins, llvm::InstrItineraryData::isEmpty(), llvm::TargetInstrInfo::isHighLatencyDef(), llvm::SDNode::isMachineOpcode(), llvm::SUnit::Latency, N, llvm::ScheduleDAG::TII, and llvm::ISD::TokenFactor.

◆ computeOperandLatency()

|

virtual |

Definition at line 624 of file ScheduleDAGSDNodes.cpp.

References BB, llvm::ISD::CopyToReg, llvm::SDep::Data, forceUnitLatencies(), llvm::MCInstrInfo::get(), llvm::SDep::getKind(), llvm::SDNode::getMachineOpcode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::TargetInstrInfo::getOperandLatency(), getReg(), llvm::SDValue::getResNo(), InstrItins, llvm::SDNode::isMachineOpcode(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::Latency, Reg, llvm::SDep::setLatency(), llvm::MachineBasicBlock::succ_empty(), and llvm::ScheduleDAG::TII.

◆ dump()

|

overridevirtual |

Implements llvm::ScheduleDAG.

Definition at line 675 of file ScheduleDAGSDNodes.cpp.

References llvm::ScheduleDAG::dumpNodeAll(), llvm::ScheduleDAG::EntrySU, llvm::ScheduleDAG::ExitSU, llvm::SUnit::getNode(), and llvm::ScheduleDAG::SUnits.

◆ dumpNode()

Implements llvm::ScheduleDAG.

Definition at line 651 of file ScheduleDAGSDNodes.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), llvm::dbgs(), llvm::SDNode::dump(), llvm::ScheduleDAG::dumpNodeName(), llvm::SmallVectorBase::empty(), llvm::SDNode::getGluedNode(), llvm::SUnit::getNode(), N, llvm::SmallVectorTemplateBase< T >::pop_back(), and llvm::SmallVectorTemplateBase< T >::push_back().

Referenced by dumpSchedule().

◆ dumpSchedule()

| void ScheduleDAGSDNodes::dumpSchedule | ( | ) | const |

Definition at line 687 of file ScheduleDAGSDNodes.cpp.

References llvm::dbgs(), dumpNode(), and Sequence.

◆ EmitSchedule()

|

virtual |

EmitSchedule - Insert MachineInstrs into the MachineBasicBlock according to the order specified in Sequence.

EmitSchedule - Emit the machine code in scheduled order.

Return the new InsertPos and MachineBasicBlock that contains this insertion point. ScheduleDAGSDNodes holds a BB pointer for convenience, but this does not necessarily refer to returned BB. The emitter may split blocks.

Definition at line 810 of file ScheduleDAGSDNodes.cpp.

References assert(), llvm::SmallVectorTemplateCommon< T >::back(), BB, llvm::SmallVectorTemplateCommon< T >::begin(), llvm::MachineFunction::begin(), llvm::SelectionDAG::ByvalParmDbgBegin(), llvm::SelectionDAG::ByvalParmDbgEnd(), DAG, llvm::SelectionDAG::DbgBegin(), llvm::SelectionDAG::DbgEnd(), llvm::SelectionDAG::DbgLabelBegin(), llvm::SelectionDAG::DbgLabelEnd(), llvm::InstrEmitter::EmitDbgLabel(), llvm::InstrEmitter::EmitDbgValue(), llvm::InstrEmitter::EmitNode(), llvm::SmallVectorBase::empty(), llvm::SmallVectorTemplateCommon< T >::end(), llvm::InstrEmitter::getBlock(), llvm::MachineBasicBlock::getFirstNonPHI(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::SDNode::getGluedNode(), llvm::InstrEmitter::getInsertPos(), llvm::SUnit::getNode(), llvm::SDDbgValue::getOrder(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::SelectionDAG::hasDebugValues(), llvm::MachineBasicBlock::insert(), llvm::TargetInstrInfo::insertNoop(), llvm::SUnit::isCloned, MI, N, llvm::SUnit::OrigNode, llvm::SmallVectorTemplateBase< T >::pop_back(), ProcessSourceNode(), llvm::SmallVectorTemplateBase< T >::push_back(), Sequence, llvm::SmallVectorBase::size(), and llvm::ScheduleDAG::TII.

Referenced by ProcessSourceNode().

◆ forceUnitLatencies()

|

inlineprotectedvirtual |

ForceUnitLatencies - Return true if all scheduling edges should be given a latency value of one.

The default is to return false; schedulers may override this as needed.

Definition at line 173 of file ScheduleDAGSDNodes.h.

Referenced by computeLatency(), and computeOperandLatency().

◆ getCustomGraphFeatures()

|

virtual |

Definition at line 296 of file SelectionDAGPrinter.cpp.

References llvm::GraphWriter< GraphType >::emitEdge(), llvm::GraphWriter< GraphType >::emitSimpleNode(), and llvm::SDNode::getNodeId().

◆ getDAGName()

|

overridevirtual |

Return the basic block label.

Implements llvm::ScheduleDAG.

Definition at line 968 of file ScheduleDAGSDNodes.cpp.

References BB, and llvm::MachineBasicBlock::getFullName().

◆ getGraphNodeLabel()

Returns a label for an SUnit node in a visualization of the ScheduleDAG.

Implements llvm::ScheduleDAG.

Definition at line 275 of file SelectionDAGPrinter.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), llvm::SmallVectorBase::empty(), llvm::SDNode::getGluedNode(), llvm::SUnit::getNode(), N, llvm::SUnit::NodeNum, llvm::RISCVFenceField::O, llvm::SmallVectorTemplateBase< T >::pop_back(), llvm::SmallVectorTemplateBase< T >::push_back(), and llvm::raw_string_ostream::str().

◆ InitNumRegDefsLeft()

| void ScheduleDAGSDNodes::InitNumRegDefsLeft | ( | SUnit * | SU | ) |

InitNumRegDefsLeft - Determine the # of regs defined by this node.

Definition at line 582 of file ScheduleDAGSDNodes.cpp.

References assert(), I, and llvm::SUnit::NumRegDefsLeft.

◆ isPassiveNode()

isPassiveNode - Return true if the node is a non-scheduled leaf.

Definition at line 65 of file ScheduleDAGSDNodes.h.

◆ newSUnit()

NewSUnit - Creates a new SUnit and return a ptr to it.

Definition at line 69 of file ScheduleDAGSDNodes.cpp.

References assert(), DAG, llvm::SDNode::getMachineOpcode(), llvm::TargetLoweringBase::getSchedulingPreference(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SDNode::isMachineOpcode(), llvm::Sched::None, llvm::SUnit::SchedulingPref, and llvm::ScheduleDAG::SUnits.

Referenced by Clone().

◆ Run()

| void ScheduleDAGSDNodes::Run | ( | SelectionDAG * | dag, |

| MachineBasicBlock * | bb | ||

| ) |

Run - perform scheduling.

Definition at line 55 of file ScheduleDAGSDNodes.cpp.

References BB, llvm::ScheduleDAG::clearDAG(), DAG, Schedule(), and Sequence.

◆ Schedule()

|

pure virtual |

Schedule - Order nodes according to selected style, filling in the Sequence member.

Referenced by Run().

◆ VerifyScheduledSequence()

| void ScheduleDAGSDNodes::VerifyScheduledSequence | ( | bool | isBottomUp | ) |

VerifyScheduledSequence - Verify that all SUnits are scheduled and consistent with the Sequence of scheduled instructions.

VerifyScheduledSequence - Verify that all SUnits were scheduled and that their state is consistent with the nodes listed in Sequence.

Definition at line 701 of file ScheduleDAGSDNodes.cpp.

References assert(), Sequence, and llvm::ScheduleDAG::VerifyScheduledDAG().

Member Data Documentation

◆ BB

| MachineBasicBlock* llvm::ScheduleDAGSDNodes::BB |

Definition at line 48 of file ScheduleDAGSDNodes.h.

Referenced by computeOperandLatency(), EmitSchedule(), getDAGName(), ProcessSDDbgValues(), ProcessSourceNode(), and Run().

◆ DAG

| SelectionDAG* llvm::ScheduleDAGSDNodes::DAG |

Definition at line 49 of file ScheduleDAGSDNodes.h.

Referenced by EmitSchedule(), newSUnit(), and Run().

◆ InstrItins

| const InstrItineraryData* llvm::ScheduleDAGSDNodes::InstrItins |

Definition at line 50 of file ScheduleDAGSDNodes.h.

Referenced by computeLatency(), and computeOperandLatency().

◆ Sequence

| std::vector<SUnit*> llvm::ScheduleDAGSDNodes::Sequence |

The schedule. Null SUnit*'s represent noop instructions.

Definition at line 53 of file ScheduleDAGSDNodes.h.

Referenced by dumpSchedule(), EmitSchedule(), Run(), and VerifyScheduledSequence().

The documentation for this class was generated from the following files:

- lib/CodeGen/SelectionDAG/ScheduleDAGSDNodes.h

- lib/CodeGen/SelectionDAG/ScheduleDAGSDNodes.cpp

- lib/CodeGen/SelectionDAG/SelectionDAGPrinter.cpp

1.8.13

1.8.13