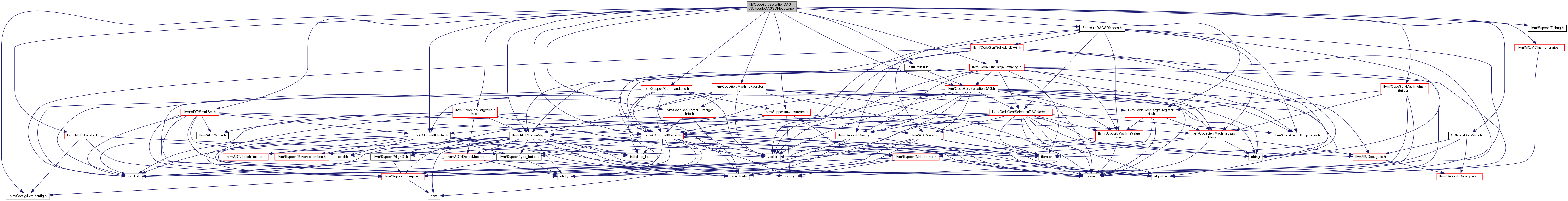

#include "ScheduleDAGSDNodes.h"#include "InstrEmitter.h"#include "SDNodeDbgValue.h"#include "llvm/ADT/DenseMap.h"#include "llvm/ADT/SmallPtrSet.h"#include "llvm/ADT/SmallSet.h"#include "llvm/ADT/SmallVector.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/SelectionDAG.h"#include "llvm/CodeGen/TargetInstrInfo.h"#include "llvm/CodeGen/TargetLowering.h"#include "llvm/CodeGen/TargetRegisterInfo.h"#include "llvm/CodeGen/TargetSubtargetInfo.h"#include "llvm/Config/llvm-config.h"#include "llvm/MC/MCInstrItineraries.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/raw_ostream.h"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "pre-RA-sched" |

Functions | |

| STATISTIC (LoadsClustered, "Number of loads clustered together") | |

| static void | CheckForPhysRegDependency (SDNode *Def, SDNode *User, unsigned Op, const TargetRegisterInfo *TRI, const TargetInstrInfo *TII, unsigned &PhysReg, int &Cost) |

| CheckForPhysRegDependency - Check if the dependency between def and use of a specified operand is a physical register dependency. More... | |

| static void | CloneNodeWithValues (SDNode *N, SelectionDAG *DAG, ArrayRef< EVT > VTs, SDValue ExtraOper=SDValue()) |

| static bool | AddGlue (SDNode *N, SDValue Glue, bool AddGlue, SelectionDAG *DAG) |

| static void | RemoveUnusedGlue (SDNode *N, SelectionDAG *DAG) |

| static void | ProcessSDDbgValues (SDNode *N, SelectionDAG *DAG, InstrEmitter &Emitter, SmallVectorImpl< std::pair< unsigned, MachineInstr *> > &Orders, DenseMap< SDValue, unsigned > &VRBaseMap, unsigned Order) |

| ProcessSDDbgValues - Process SDDbgValues associated with this node. More... | |

| static void | ProcessSourceNode (SDNode *N, SelectionDAG *DAG, InstrEmitter &Emitter, DenseMap< SDValue, unsigned > &VRBaseMap, SmallVectorImpl< std::pair< unsigned, MachineInstr *> > &Orders, SmallSet< unsigned, 8 > &Seen) |

Variables | |

| static cl::opt< int > | HighLatencyCycles ("sched-high-latency-cycles", cl::Hidden, cl::init(10), cl::desc("Roughly estimate the number of cycles that 'long latency'" "instructions take for targets with no itinerary")) |

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "pre-RA-sched" |

Definition at line 37 of file ScheduleDAGSDNodes.cpp.

Function Documentation

◆ AddGlue()

|

static |

Definition at line 162 of file ScheduleDAGSDNodes.cpp.

References CloneNodeWithValues(), llvm::SDValue::getNode(), llvm::SDNode::getNumOperands(), llvm::SDNode::getNumValues(), llvm::SDNode::getOperand(), llvm::SDNode::getValueType(), llvm::MVT::Glue, llvm::SDNode::value_begin(), and llvm::SDNode::value_end().

◆ CheckForPhysRegDependency()

|

static |

CheckForPhysRegDependency - Check if the dependency between def and use of a specified operand is a physical register dependency.

If so, returns the register and the cost of copying the register.

Definition at line 111 of file ScheduleDAGSDNodes.cpp.

References llvm::ISD::CopyFromReg, llvm::ISD::CopyToReg, llvm::MCInstrInfo::get(), llvm::TargetRegisterClass::getCopyCost(), llvm::SDNode::getMachineOpcode(), llvm::TargetRegisterInfo::getMinimalPhysRegClass(), llvm::MCInstrDesc::getNumDefs(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), getReg(), llvm::SDValue::getResNo(), llvm::SDNode::getSimpleValueType(), llvm::MCInstrDesc::ImplicitDefs, llvm::SDNode::isMachineOpcode(), llvm::TargetRegisterInfo::isVirtualRegister(), and Reg.

◆ CloneNodeWithValues()

|

static |

Definition at line 141 of file ScheduleDAGSDNodes.cpp.

References llvm::SmallVectorImpl< T >::assign(), llvm::dyn_cast(), llvm::SDNode::getOpcode(), llvm::SelectionDAG::getVTList(), llvm::MachineSDNode::memoperands_begin(), llvm::MachineSDNode::memoperands_end(), llvm::SelectionDAG::MorphNodeTo(), N, llvm::SDNode::op_begin(), llvm::SDNode::op_end(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), and llvm::SelectionDAG::setNodeMemRefs().

Referenced by AddGlue(), and RemoveUnusedGlue().

◆ ProcessSDDbgValues()

|

static |

ProcessSDDbgValues - Process SDDbgValues associated with this node.

Definition at line 714 of file ScheduleDAGSDNodes.cpp.

References llvm::ScheduleDAGSDNodes::BB, llvm::InstrEmitter::EmitDbgValue(), llvm::InstrEmitter::getBlock(), llvm::SelectionDAG::GetDbgValues(), llvm::SDNode::getHasDebugValue(), llvm::InstrEmitter::getInsertPos(), and llvm::MachineBasicBlock::insert().

Referenced by ProcessSourceNode().

◆ ProcessSourceNode()

|

static |

Definition at line 742 of file ScheduleDAGSDNodes.cpp.

References assert(), llvm::MachineBasicBlock::back(), llvm::ScheduleDAGSDNodes::BB, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::SUnit::CopyDstRC, llvm::MachineRegisterInfo::createVirtualRegister(), E, llvm::ScheduleDAGSDNodes::EmitSchedule(), llvm::DenseMapBase< DenseMap< KeyT, ValueT, KeyInfoT, BucketT >, KeyT, ValueT, KeyInfoT, BucketT >::end(), llvm::DenseMapBase< DenseMap< KeyT, ValueT, KeyInfoT, BucketT >, KeyT, ValueT, KeyInfoT, BucketT >::find(), llvm::MCInstrInfo::get(), llvm::InstrEmitter::getBlock(), llvm::InstrEmitter::getInsertPos(), llvm::SDNode::getIROrder(), I, llvm::SmallSet< T, N, C >::insert(), llvm::DenseMapBase< DenseMap< KeyT, ValueT, KeyInfoT, BucketT >, KeyT, ValueT, KeyInfoT, BucketT >::insert(), llvm::MachineInstr::isPHI(), llvm::ScheduleDAG::MRI, llvm::SUnit::Preds, ProcessSDDbgValues(), Reg, llvm::SUnit::Succs, and llvm::ScheduleDAG::TII.

Referenced by llvm::ScheduleDAGSDNodes::EmitSchedule().

◆ RemoveUnusedGlue()

|

static |

Definition at line 187 of file ScheduleDAGSDNodes.cpp.

References assert(), CloneNodeWithValues(), llvm::SDNode::getNumValues(), llvm::SDNode::getValueType(), llvm::MVT::Glue, llvm::SDNode::hasAnyUseOfValue(), llvm::makeArrayRef(), and llvm::SDNode::value_begin().

◆ STATISTIC()

| STATISTIC | ( | LoadsClustered | , |

| "Number of loads clustered together" | |||

| ) |

Variable Documentation

◆ HighLatencyCycles

|

static |

Referenced by llvm::ScheduleDAGSDNodes::computeLatency().

1.8.13

1.8.13