This class provides the information for the target register banks. More...

#include "Target/AMDGPU/AMDGPURegisterBankInfo.h"

Inheritance diagram for llvm::AMDGPUGenRegisterBankInfo:

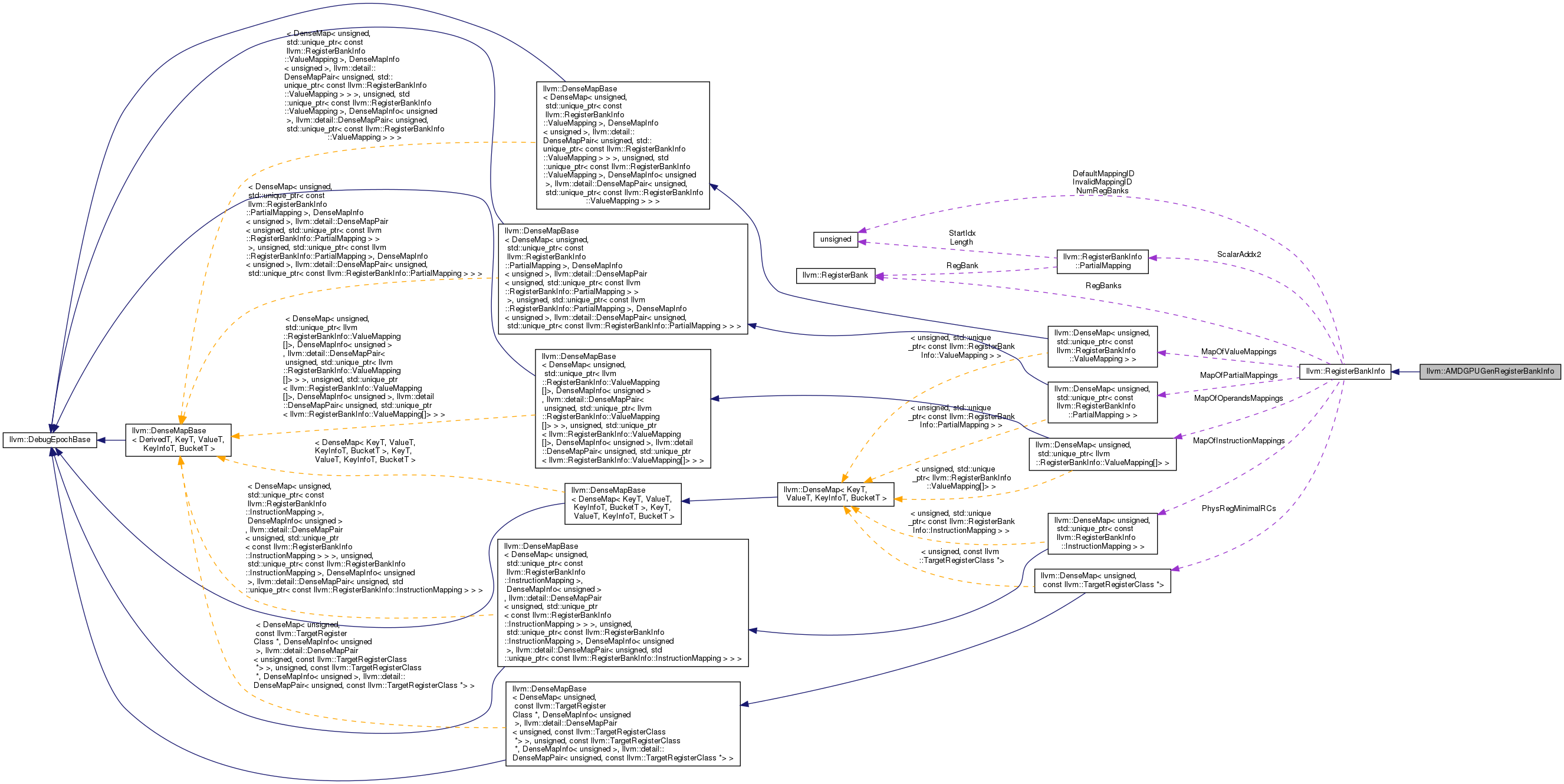

Collaboration diagram for llvm::AMDGPUGenRegisterBankInfo:

Additional Inherited Members | |

Public Types inherited from llvm::RegisterBankInfo Public Types inherited from llvm::RegisterBankInfo | |

| using | InstructionMappings = SmallVector< const InstructionMapping *, 4 > |

| Convenient type to represent the alternatives for mapping an instruction. More... | |

Public Member Functions inherited from llvm::RegisterBankInfo Public Member Functions inherited from llvm::RegisterBankInfo | |

| const RegisterBank * | getRegBankFromConstraints (const MachineInstr &MI, unsigned OpIdx, const TargetInstrInfo &TII, const TargetRegisterInfo &TRI) const |

Get the register bank for the OpIdx-th operand of MI form the encoding constraints, if any. More... | |

| virtual void | applyMappingImpl (const OperandsMapper &OpdMapper) const |

| See applyMapping. More... | |

| virtual | ~RegisterBankInfo ()=default |

| const RegisterBank & | getRegBank (unsigned ID) const |

Get the register bank identified by ID. More... | |

| const RegisterBank * | getRegBank (unsigned Reg, const MachineRegisterInfo &MRI, const TargetRegisterInfo &TRI) const |

Get the register bank of Reg. More... | |

| unsigned | getNumRegBanks () const |

| Get the total number of register banks. More... | |

| virtual const RegisterBank & | getRegBankFromRegClass (const TargetRegisterClass &RC) const |

Get a register bank that covers RC. More... | |

| virtual unsigned | copyCost (const RegisterBank &A, const RegisterBank &B, unsigned Size) const |

Get the cost of a copy from B to A, or put differently, get the cost of A = COPY B. More... | |

| virtual const InstructionMapping & | getInstrMapping (const MachineInstr &MI) const |

Get the mapping of the different operands of MI on the register bank. More... | |

| virtual InstructionMappings | getInstrAlternativeMappings (const MachineInstr &MI) const |

Get the alternative mappings for MI. More... | |

| const InstructionMapping & | getInstructionMapping (unsigned ID, unsigned Cost, const ValueMapping *OperandsMapping, unsigned NumOperands) const |

| Method to get a uniquely generated InstructionMapping. More... | |

| const InstructionMapping & | getInvalidInstructionMapping () const |

| Method to get a uniquely generated invalid InstructionMapping. More... | |

Static Public Member Functions inherited from llvm::RegisterBankInfo Static Public Member Functions inherited from llvm::RegisterBankInfo | |

| static void | applyDefaultMapping (const OperandsMapper &OpdMapper) |

| Helper method to apply something that is like the default mapping. More... | |

| static const TargetRegisterClass * | constrainGenericRegister (unsigned Reg, const TargetRegisterClass &RC, MachineRegisterInfo &MRI) |

Constrain the (possibly generic) virtual register Reg to RC. More... | |

Public Attributes inherited from llvm::RegisterBankInfo Public Attributes inherited from llvm::RegisterBankInfo | |

| struct llvm::RegisterBankInfo::PartialMapping | ScalarAddx2 |

| VectorAdd | |

Get the possible mapping for MI. More... | |

Static Public Attributes inherited from llvm::RegisterBankInfo Static Public Attributes inherited from llvm::RegisterBankInfo | |

| static const unsigned | DefaultMappingID = UINT_MAX |

| Identifier used when the related instruction mapping instance is generated by target independent code. More... | |

| static const unsigned | InvalidMappingID = UINT_MAX - 1 |

| Identifier used when the related instruction mapping instance is generated by the default constructor. More... | |

Protected Member Functions inherited from llvm::RegisterBankInfo Protected Member Functions inherited from llvm::RegisterBankInfo | |

| RegisterBankInfo (RegisterBank **RegBanks, unsigned NumRegBanks) | |

Create a RegisterBankInfo that can accommodate up to NumRegBanks RegisterBank instances. More... | |

| RegisterBankInfo () | |

| This constructor is meaningless. More... | |

| RegisterBank & | getRegBank (unsigned ID) |

Get the register bank identified by ID. More... | |

| const TargetRegisterClass & | getMinimalPhysRegClass (unsigned Reg, const TargetRegisterInfo &TRI) const |

| Get the MinimalPhysRegClass for Reg. More... | |

| const InstructionMapping & | getInstrMappingImpl (const MachineInstr &MI) const |

Try to get the mapping of MI. More... | |

| const PartialMapping & | getPartialMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| Get the uniquely generated PartialMapping for the given arguments. More... | |

| const ValueMapping & | getValueMapping (unsigned StartIdx, unsigned Length, const RegisterBank &RegBank) const |

| The most common ValueMapping consists of a single PartialMapping. More... | |

| const ValueMapping & | getValueMapping (const PartialMapping *BreakDown, unsigned NumBreakDowns) const |

| Get the ValueMapping for the given arguments. More... | |

| template<typename Iterator > | |

| const ValueMapping * | getOperandsMapping (Iterator Begin, Iterator End) const |

Get the uniquely generated array of ValueMapping for the elements of between Begin and End. More... | |

| const ValueMapping * | getOperandsMapping (const SmallVectorImpl< const ValueMapping *> &OpdsMapping) const |

Get the uniquely generated array of ValueMapping for the elements of OpdsMapping. More... | |

| const ValueMapping * | getOperandsMapping (std::initializer_list< const ValueMapping *> OpdsMapping) const |

| Get the uniquely generated array of ValueMapping for the given arguments. More... | |

Protected Attributes inherited from llvm::RegisterBankInfo Protected Attributes inherited from llvm::RegisterBankInfo | |

| RegisterBank ** | RegBanks |

| Hold the set of supported register banks. More... | |

| unsigned | NumRegBanks |

| Total number of register banks. More... | |

| DenseMap< unsigned, std::unique_ptr< const PartialMapping > > | MapOfPartialMappings |

| Keep dynamically allocated PartialMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const ValueMapping > > | MapOfValueMappings |

| Keep dynamically allocated ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< ValueMapping[]> > | MapOfOperandsMappings |

| Keep dynamically allocated array of ValueMapping in a separate map. More... | |

| DenseMap< unsigned, std::unique_ptr< const InstructionMapping > > | MapOfInstructionMappings |

| Keep dynamically allocated InstructionMapping in a separate map. More... | |

| DenseMap< unsigned, const TargetRegisterClass * > | PhysRegMinimalRCs |

| Getting the minimal register class of a physreg is expensive. More... | |

Detailed Description

This class provides the information for the target register banks.

Definition at line 29 of file AMDGPURegisterBankInfo.h.

The documentation for this class was generated from the following file:

- lib/Target/AMDGPU/AMDGPURegisterBankInfo.h

1.8.13

1.8.13