This file implements the targeting of the InstructionSelector class for X86. More...

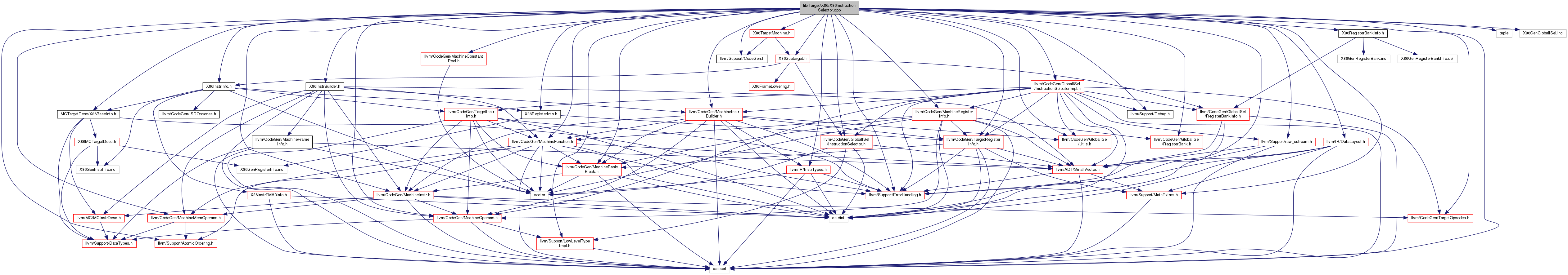

#include "MCTargetDesc/X86BaseInfo.h"#include "X86InstrBuilder.h"#include "X86InstrInfo.h"#include "X86RegisterBankInfo.h"#include "X86RegisterInfo.h"#include "X86Subtarget.h"#include "X86TargetMachine.h"#include "llvm/CodeGen/GlobalISel/InstructionSelector.h"#include "llvm/CodeGen/GlobalISel/InstructionSelectorImpl.h"#include "llvm/CodeGen/GlobalISel/RegisterBank.h"#include "llvm/CodeGen/GlobalISel/Utils.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineConstantPool.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineMemOperand.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/TargetOpcodes.h"#include "llvm/CodeGen/TargetRegisterInfo.h"#include "llvm/IR/DataLayout.h"#include "llvm/IR/InstrTypes.h"#include "llvm/Support/AtomicOrdering.h"#include "llvm/Support/CodeGen.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/LowLevelTypeImpl.h"#include "llvm/Support/MathExtras.h"#include "llvm/Support/raw_ostream.h"#include <cassert>#include <cstdint>#include <tuple>#include "X86GenGlobalISel.inc"

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "X86-isel" |

| #define | GET_GLOBALISEL_PREDICATE_BITSET |

| #define | GET_GLOBALISEL_PREDICATES_DECL |

| #define | GET_GLOBALISEL_TEMPORARIES_DECL |

| #define | GET_GLOBALISEL_IMPL |

| #define | GET_GLOBALISEL_PREDICATES_INIT |

| #define | GET_GLOBALISEL_TEMPORARIES_INIT |

Functions | |

| static const TargetRegisterClass * | getRegClassFromGRPhysReg (unsigned Reg) |

| static void | X86SelectAddress (const MachineInstr &I, const MachineRegisterInfo &MRI, X86AddressMode &AM) |

| static unsigned | getLeaOP (LLT Ty, const X86Subtarget &STI) |

| static bool | canTurnIntoCOPY (const TargetRegisterClass *DstRC, const TargetRegisterClass *SrcRC) |

Detailed Description

This file implements the targeting of the InstructionSelector class for X86.

- Todo:

- This should be generated by TableGen.

Definition in file X86InstructionSelector.cpp.

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "X86-isel" |

Definition at line 49 of file X86InstructionSelector.cpp.

◆ GET_GLOBALISEL_IMPL

| #define GET_GLOBALISEL_IMPL |

Definition at line 152 of file X86InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATE_BITSET

| #define GET_GLOBALISEL_PREDICATE_BITSET |

Definition at line 55 of file X86InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATES_DECL

| #define GET_GLOBALISEL_PREDICATES_DECL |

Definition at line 141 of file X86InstructionSelector.cpp.

◆ GET_GLOBALISEL_PREDICATES_INIT

| #define GET_GLOBALISEL_PREDICATES_INIT |

◆ GET_GLOBALISEL_TEMPORARIES_DECL

| #define GET_GLOBALISEL_TEMPORARIES_DECL |

Definition at line 145 of file X86InstructionSelector.cpp.

◆ GET_GLOBALISEL_TEMPORARIES_INIT

| #define GET_GLOBALISEL_TEMPORARIES_INIT |

Function Documentation

◆ canTurnIntoCOPY()

|

static |

Definition at line 676 of file X86InstructionSelector.cpp.

References llvm::addConstantPoolReference(), llvm::addDirectMem(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), llvm::AArch64CC::AL, llvm::AMDGPU::HSAMD::Kernel::Arg::Key::Align, assert(), llvm::sys::path::begin(), llvm::BuildMI(), llvm::constrainSelectedInstRegOperands(), llvm::MachineRegisterInfo::createGenericVirtualRegister(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::dbgs(), llvm::tgtok::Def, llvm::RegState::DefineNoRead, llvm::N86::EAX, llvm::N86::ECX, llvm::N86::EDX, llvm::sys::path::end(), llvm::MachineInstr::eraseFromParent(), llvm::find_if(), llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstantPoolIndex(), llvm::getConstantVRegVal(), llvm::MachineFunction::getDataLayout(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getFPImm(), llvm::RegisterBank::getID(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getIntrinsicID(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::DataLayout::getPointerSize(), llvm::MachineOperand::getPredicate(), llvm::MachineOperand::getReg(), getRegClass(), llvm::MachineRegisterInfo::getRegClassOrNull(), llvm::X86::getSETFromCond(), llvm::LLT::getSizeInBits(), llvm::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::MachineRegisterInfo::getVRegDef(), llvm::X86::getX86ConditionCode(), I, llvm::MachineInstr::isImplicitDef(), llvm::LLT::isVector(), llvm::RegState::Kill, llvm::AMDGPUISD::KILL, llvm::CodeModel::Large, llvm::X86::LAST_VALID_COND, LLVM_DEBUG, llvm_unreachable, llvm::X86II::MO_GOTOFF, llvm::X86II::MO_PIC_BASE_OFFSET, MRI, selectMergeValues(), selectUnmergeValues(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), llvm::MachineRegisterInfo::setRegBank(), llvm::MachineOperand::setSubReg(), llvm::CodeModel::Small, std::swap(), TII, llvm::SystemZISD::TM, llvm::Intrinsic::trap, llvm::ISD::TRAP, and TRI.

◆ getLeaOP()

|

static |

Definition at line 543 of file X86InstructionSelector.cpp.

References llvm::addFullAddress(), llvm::MachineInstrBuilder::addImm(), llvm::cflaa::addOffset(), llvm::MachineInstr::addOperand(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::X86AddressMode::Base, llvm::MachineOperand::ChangeToImmediate(), llvm::constrainSelectedInstRegOperands(), llvm::MachineOperand::getCImm(), llvm::MachineOperand::getGlobal(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::LLT::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::ConstantInt::getZExtValue(), llvm::X86AddressMode::GV, llvm::X86AddressMode::GVOpFlags, llvm::X86AddressMode::IndexReg, llvm::MachineOperand::isCImm(), llvm::isGlobalRelativeToPICBase(), llvm::isGlobalStubReference(), llvm::MachineOperand::isImm(), llvm::isInt< 32 >(), llvm::X86Subtarget::isTarget64BitILP32(), llvm_unreachable, llvm::X86AddressMode::Reg, llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), llvm::CodeModel::Small, TII, llvm::SystemZISD::TM, and TRI.

◆ getRegClassFromGRPhysReg()

|

static |

Definition at line 220 of file X86InstructionSelector.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), contains(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::dbgs(), llvm::MachineInstr::getDebugLoc(), llvm::RegisterBank::getID(), llvm::MachineInstr::getNumExplicitOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegClass(), llvm::MachineRegisterInfo::getRegClassOrNull(), llvm::MachineFunction::getRegInfo(), llvm::LLT::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::TargetRegisterClass::hasSubClassEq(), I, llvm::MachineInstr::isCopy(), llvm::isPreISelGenericOpcode(), llvm::LLT::isVector(), LLVM_DEBUG, llvm_unreachable, llvm::MachineInstr::print(), selectCopy(), llvm::mca::selectImpl(), selectMergeValues(), selectUnmergeValues(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setReg(), llvm::MachineOperand::setSubReg(), llvm::MachineOperand::substPhysReg(), TII, and TRI.

◆ X86SelectAddress()

|

static |

Definition at line 478 of file X86InstructionSelector.cpp.

References llvm::addFullAddress(), llvm::MachineInstrBuilder::addUse(), assert(), llvm::X86AddressMode::Base, llvm::X86AddressMode::BaseType, llvm::constrainSelectedInstRegOperands(), llvm::dbgs(), llvm::X86AddressMode::Disp, llvm::X86AddressMode::FrameIndex, llvm::getConstantVRegVal(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getType(), llvm::MachineRegisterInfo::getVRegDef(), llvm::isInt< 32 >(), llvm::MachineOperand::isReg(), LLVM_DEBUG, llvm::MachineInstr::memoperands_begin(), MRI, llvm::X86AddressMode::Reg, llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), TII, and TRI.

Referenced by computeBytesPoppedByCalleeForSRet(), and X86ChooseCmpImmediateOpcode().

1.8.13

1.8.13