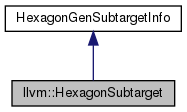

#include "Target/Hexagon/HexagonSubtarget.h"

Classes | |

| struct | BankConflictMutation |

| struct | CallMutation |

| struct | HVXMemLatencyMutation |

| struct | UsrOverflowMutation |

Public Attributes | |

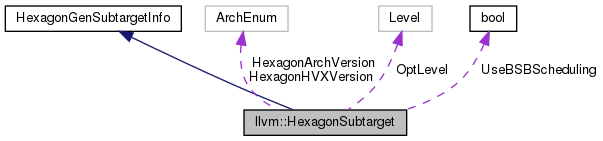

| Hexagon::ArchEnum | HexagonArchVersion |

| Hexagon::ArchEnum | HexagonHVXVersion = Hexagon::ArchEnum::NoArch |

| CodeGenOpt::Level | OptLevel |

| bool | UseBSBScheduling |

| True if the target should use Back-Skip-Back scheduling. More... | |

Detailed Description

Definition at line 43 of file HexagonSubtarget.h.

Constructor & Destructor Documentation

◆ HexagonSubtarget()

| HexagonSubtarget::HexagonSubtarget | ( | const Triple & | TT, |

| StringRef | CPU, | ||

| StringRef | FS, | ||

| const TargetMachine & | TM | ||

| ) |

Definition at line 80 of file HexagonSubtarget.cpp.

References assert(), and llvm::InstrItineraryData::Itineraries.

Member Function Documentation

◆ adjustSchedDependency()

|

override |

Perform target specific adjustments to the latency of a schedule dependency.

Definition at line 321 of file HexagonSubtarget.cpp.

References llvm::HexagonInstrInfo::canExecuteInBundle(), llvm::SmallSet< T, N, C >::clear(), EnableDotCurSched, llvm::SUnit::getInstr(), getInstrInfo(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::HexagonInstrInfo::getOperandLatency(), llvm::MachineOperand::getReg(), hasV60Ops(), llvm::MachineInstr::isCopy(), llvm::SUnit::isInstr(), llvm::MachineOperand::isReg(), llvm::MachineInstr::isRegSequence(), llvm::HexagonInstrInfo::isToBeScheduledASAP(), llvm::MachineOperand::isUse(), llvm::max(), llvm::SUnit::NumSuccs, llvm::SDep::setLatency(), and llvm::SUnit::Succs.

Referenced by getHexagonArchVersion().

◆ enableMachineSchedDefaultSched()

|

inlineoverride |

Definition at line 188 of file HexagonSubtarget.h.

◆ enableMachineScheduler()

|

override |

Definition at line 393 of file HexagonSubtarget.cpp.

References DisableHexagonMISched.

Referenced by useBSBScheduling().

◆ enablePostRAScheduler()

|

inlineoverride |

Definition at line 191 of file HexagonSubtarget.h.

References enableSubRegLiveness().

◆ enableSubRegLiveness()

|

override |

Definition at line 581 of file HexagonSubtarget.cpp.

References EnableSubregLiveness.

Referenced by enablePostRAScheduler().

◆ getAntiDepBreakMode()

|

inlineoverride |

Definition at line 190 of file HexagonSubtarget.h.

◆ getCPUString()

|

inline |

Definition at line 195 of file HexagonSubtarget.h.

◆ getFrameLowering()

|

inlineoverride |

Definition at line 111 of file HexagonSubtarget.h.

Referenced by llvm::HexagonDAGToDAGISel::EmitFunctionEntryCode(), llvm::HexagonInstrInfo::loadRegFromStackSlot(), llvm::HexagonDAGToDAGISel::SelectAddrFI(), llvm::HexagonDAGToDAGISel::SelectFrameIndex(), and llvm::HexagonInstrInfo::storeRegToStackSlot().

◆ getHexagonArchVersion()

|

inline |

Definition at line 197 of file HexagonSubtarget.h.

References adjustSchedDependency(), getPostRAMutations(), getSMSMutations(), HexagonArchVersion, use, and useAA().

Referenced by hasV55Ops(), hasV55OpsOnly(), hasV5Ops(), hasV5OpsOnly(), hasV60Ops(), hasV60OpsOnly(), hasV62Ops(), hasV62OpsOnly(), hasV65Ops(), hasV65OpsOnly(), hasV66Ops(), and hasV66OpsOnly().

◆ getHVXElementTypes()

Definition at line 226 of file HexagonSubtarget.h.

References llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i8, and llvm::makeArrayRef().

Referenced by llvm::HexagonTargetLowering::getPreferredVectorAction(), and isHVXVectorType().

◆ getInstrInfo()

|

inlineoverride |

Definition at line 104 of file HexagonSubtarget.h.

Referenced by adjustSchedDependency(), llvm::HexagonSubtarget::CallMutation::apply(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::HexagonAsmPrinter::EmitInstruction(), enableAllocFrameElim(), llvm::HexagonFrameLowering::getFrameIndexReference(), INITIALIZE_PASS(), llvm::HexagonFrameLowering::insertCFIInstructions(), llvm::VLIWResourceModel::isResourceAvailable(), moveInstrOut(), llvm::HexagonDAGToDAGISel::runOnMachineFunction(), llvm::ConvergingVLIWScheduler::SchedulingCost(), and usePredicatedCalls().

◆ getInstrItineraryData()

|

inlineoverride |

getInstrItins - Return the instruction itineraries based on subtarget selection.

Definition at line 101 of file HexagonSubtarget.h.

◆ getL1CacheLineSize()

| unsigned HexagonSubtarget::getL1CacheLineSize | ( | ) | const |

Definition at line 573 of file HexagonSubtarget.cpp.

Referenced by llvm::HexagonTTIImpl::getCacheLineSize(), and getTypeAlignment().

◆ getL1PrefetchDistance()

| unsigned HexagonSubtarget::getL1PrefetchDistance | ( | ) | const |

Definition at line 577 of file HexagonSubtarget.cpp.

Referenced by llvm::HexagonTTIImpl::getPrefetchDistance(), and getTypeAlignment().

◆ getPostRAMutations()

|

override |

Definition at line 377 of file HexagonSubtarget.cpp.

Referenced by getHexagonArchVersion().

◆ getRegisterInfo()

|

inlineoverride |

Definition at line 105 of file HexagonSubtarget.h.

Referenced by llvm::HexagonInstrInfo::copyPhysReg(), llvm::HexagonInstrInfo::DefinesPredicate(), llvm::HexagonInstrInfo::expandPostRAPseudo(), getInstrVecReg(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::HexagonInstrInfo::reduceLoopCount(), and llvm::HexagonDAGToDAGISel::runOnMachineFunction().

◆ getSelectionDAGInfo()

|

inlineoverride |

Definition at line 114 of file HexagonSubtarget.h.

References initializeSubtargetDependencies(), and ParseSubtargetFeatures().

◆ getSMSMutations()

|

override |

Definition at line 384 of file HexagonSubtarget.cpp.

Referenced by getHexagonArchVersion().

◆ getTargetLowering()

|

inlineoverride |

Definition at line 108 of file HexagonSubtarget.h.

◆ getTypeAlignment()

Definition at line 260 of file HexagonSubtarget.h.

References getL1CacheLineSize(), getL1PrefetchDistance(), llvm::MVT::getSizeInBits(), getVectorLength(), isHVXVectorType(), and TII.

Referenced by llvm::HexagonTargetLowering::LowerStore(), and llvm::HexagonTargetLowering::LowerUnalignedLoad().

◆ getVectorLength()

|

inline |

Definition at line 217 of file HexagonSubtarget.h.

References assert(), llvm_unreachable, useHVX128BOps(), useHVX64BOps(), and useHVXOps().

Referenced by llvm::HexagonTargetLowering::allowsMisalignedMemoryAccesses(), llvm::HexagonTTIImpl::getMinimumVF(), llvm::HexagonTTIImpl::getMinVectorRegisterBitWidth(), llvm::HexagonTargetLowering::getPreferredVectorAction(), getTypeAlignment(), isHVXVectorType(), and llvm::HvxSelector::selectRor().

◆ hasMemNoShuf()

|

inline |

Definition at line 176 of file HexagonSubtarget.h.

◆ hasReservedR19()

|

inline |

Definition at line 177 of file HexagonSubtarget.h.

References usePredicatedCalls().

Referenced by llvm::HexagonRegisterInfo::getReservedRegs().

◆ hasV55Ops()

|

inline |

Definition at line 131 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V55.

◆ hasV55OpsOnly()

|

inline |

Definition at line 134 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V55.

◆ hasV5Ops()

|

inline |

Definition at line 125 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V5.

◆ hasV5OpsOnly()

|

inline |

Definition at line 128 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V5.

◆ hasV60Ops()

|

inline |

Definition at line 137 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V60.

Referenced by adjustSchedDependency(), llvm::HexagonTargetLowering::getRegForInlineAsmConstraint(), getZeroLatency(), llvm::HexagonTargetLowering::HexagonTargetLowering(), initializeSubtargetDependencies(), and usePredicatedCalls().

◆ hasV60OpsOnly()

|

inline |

Definition at line 140 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V60.

Referenced by cannotCoexistAsymm().

◆ hasV62Ops()

|

inline |

Definition at line 143 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V62.

Referenced by llvm::HexagonInstrInfo::isPredicable().

◆ hasV62OpsOnly()

|

inline |

Definition at line 146 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V62.

◆ hasV65Ops()

|

inline |

Definition at line 149 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V65.

Referenced by llvm::HexagonPacketizerList::isLegalToPacketizeTogether().

◆ hasV65OpsOnly()

|

inline |

Definition at line 152 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V65.

◆ hasV66Ops()

|

inline |

Definition at line 155 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V66.

Referenced by llvm::HexagonTargetLowering::HexagonTargetLowering().

◆ hasV66OpsOnly()

|

inline |

Definition at line 158 of file HexagonSubtarget.h.

References getHexagonArchVersion(), and llvm::Hexagon::V66.

◆ initializeSubtargetDependencies()

| HexagonSubtarget & HexagonSubtarget::initializeSubtargetDependencies | ( | StringRef | CPU, |

| StringRef | FS | ||

| ) |

Definition at line 93 of file HexagonSubtarget.cpp.

References llvm::Hexagon_MC::completeHVXFeatures(), EnableBSBSched, Features, hasV60Ops(), HexagonArchVersion, llvm::HexagonDisableDuplex, llvm_unreachable, OverrideLongCalls, ParseSubtargetFeatures(), UseBSBScheduling, llvm::Hexagon::V5, llvm::Hexagon::V55, llvm::Hexagon::V60, llvm::Hexagon::V62, llvm::Hexagon::V65, and llvm::Hexagon::V66.

Referenced by getSelectionDAGInfo().

◆ isHVXVectorType()

Definition at line 231 of file HexagonSubtarget.h.

References llvm::any_of(), getHVXElementTypes(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), getVectorLength(), llvm::MVT::getVectorNumElements(), llvm::MVT::i1, llvm::MVT::isVector(), T, and useHVXOps().

Referenced by llvm::HexagonTargetLowering::allowsMisalignedMemoryAccesses(), getTypeAlignment(), llvm::HexagonTargetLowering::LowerVECTOR_SHUFFLE(), and llvm::HexagonDAGToDAGISel::SelectVAlign().

◆ noreturnStackElim()

|

inline |

Definition at line 180 of file HexagonSubtarget.h.

◆ ParseSubtargetFeatures()

ParseSubtargetFeatures - Parses features string setting specified subtarget options.

Definition of function is auto generated by tblgen.

Referenced by getSelectionDAGInfo(), and initializeSubtargetDependencies().

◆ useAA()

|

override |

Enable use of alias analysis during code generation (during MI scheduling, DAGCombine, etc.).

Definition at line 313 of file HexagonSubtarget.cpp.

References llvm::CodeGenOpt::None, and OptLevel.

Referenced by getHexagonArchVersion().

◆ useBSBScheduling()

|

inline |

Definition at line 182 of file HexagonSubtarget.h.

References enableMachineScheduler(), and UseBSBScheduling.

Referenced by usePredicatedCalls().

◆ useHVX128BOps()

|

inline |

Definition at line 173 of file HexagonSubtarget.h.

References useHVXOps().

Referenced by llvm::HexagonTargetLowering::getRegForInlineAsmConstraint(), and getVectorLength().

◆ useHVX64BOps()

|

inline |

Definition at line 174 of file HexagonSubtarget.h.

References useHVXOps().

Referenced by getVectorLength().

◆ useHVXOps()

|

inline |

Definition at line 170 of file HexagonSubtarget.h.

References llvm::Hexagon::NoArch.

Referenced by llvm::HexagonTargetLowering::CanLowerReturn(), llvm::HexagonTargetLowering::getConstraintType(), llvm::HexagonTargetLowering::getPreferredVectorAction(), getVectorLength(), llvm::HexagonTargetLowering::HexagonTargetLowering(), isHVXVectorType(), llvm::HexagonDAGToDAGISel::Select(), llvm::HexagonRegisterInfo::shouldCoalesce(), useHVX128BOps(), and useHVX64BOps().

◆ useLongCalls()

|

inline |

Definition at line 162 of file HexagonSubtarget.h.

◆ useMemops()

|

inline |

Definition at line 163 of file HexagonSubtarget.h.

◆ useNewValueJumps()

|

inline |

Definition at line 165 of file HexagonSubtarget.h.

Referenced by getNewValueJumpOpcode().

◆ useNewValueStores()

|

inline |

Definition at line 166 of file HexagonSubtarget.h.

◆ usePackets()

|

inline |

Definition at line 164 of file HexagonSubtarget.h.

◆ usePredicatedCalls()

| bool HexagonSubtarget::usePredicatedCalls | ( | ) | const |

Definition at line 399 of file HexagonSubtarget.cpp.

References assert(), EnablePredicatedCalls, F(), llvm::find(), llvm::SUnit::getInstr(), getInstrInfo(), llvm::SDep::getLatency(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::HexagonInstrInfo::getOperandLatency(), llvm::MachineOperand::getReg(), hasV60Ops(), I, llvm::SDep::isArtificial(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm::Latency, llvm::max(), llvm::SUnit::Preds, llvm::SDep::setLatency(), llvm::SDep::setSUnit(), llvm::SUnit::Succs, T, and useBSBScheduling().

Referenced by hasReservedR19(), and llvm::HexagonInstrInfo::isPredicable().

◆ useSmallData()

|

inline |

Definition at line 167 of file HexagonSubtarget.h.

◆ useZRegOps()

|

inline |

Definition at line 168 of file HexagonSubtarget.h.

Member Data Documentation

◆ HexagonArchVersion

| Hexagon::ArchEnum llvm::HexagonSubtarget::HexagonArchVersion |

Definition at line 63 of file HexagonSubtarget.h.

Referenced by getHexagonArchVersion(), and initializeSubtargetDependencies().

◆ HexagonHVXVersion

| Hexagon::ArchEnum llvm::HexagonSubtarget::HexagonHVXVersion = Hexagon::ArchEnum::NoArch |

Definition at line 64 of file HexagonSubtarget.h.

◆ OptLevel

| CodeGenOpt::Level llvm::HexagonSubtarget::OptLevel |

Definition at line 65 of file HexagonSubtarget.h.

Referenced by useAA().

◆ UseBSBScheduling

| bool llvm::HexagonSubtarget::UseBSBScheduling |

True if the target should use Back-Skip-Back scheduling.

This is the default for V60.

Definition at line 68 of file HexagonSubtarget.h.

Referenced by initializeSubtargetDependencies(), and useBSBScheduling().

The documentation for this class was generated from the following files:

- lib/Target/Hexagon/HexagonSubtarget.h

- lib/Target/Hexagon/HexagonSubtarget.cpp

1.8.13

1.8.13