#include "Target/AMDGPU/Disassembler/AMDGPUDisassembler.h"

Public Types | |

| enum | OpWidthTy { OPW32, OPW64, OPW128, OPW256, OPW512, OPW16, OPWV216, OPW_LAST_, OPW_FIRST_ = OPW32 } |

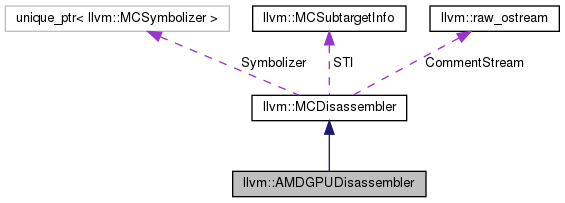

Public Types inherited from llvm::MCDisassembler Public Types inherited from llvm::MCDisassembler | |

| enum | DecodeStatus { Fail = 0, SoftFail = 1, Success = 3 } |

| Ternary decode status. More... | |

Static Public Member Functions | |

| static MCOperand | decodeIntImmed (unsigned Imm) |

| static MCOperand | decodeFPImmed (OpWidthTy Width, unsigned Imm) |

Additional Inherited Members | |

Public Attributes inherited from llvm::MCDisassembler Public Attributes inherited from llvm::MCDisassembler | |

| raw_ostream * | CommentStream = nullptr |

Protected Attributes inherited from llvm::MCDisassembler Protected Attributes inherited from llvm::MCDisassembler | |

| const MCSubtargetInfo & | STI |

| std::unique_ptr< MCSymbolizer > | Symbolizer |

Detailed Description

Definition at line 41 of file AMDGPUDisassembler.h.

Member Enumeration Documentation

◆ OpWidthTy

| Enumerator | |

|---|---|

| OPW32 | |

| OPW64 | |

| OPW128 | |

| OPW256 | |

| OPW512 | |

| OPW16 | |

| OPWV216 | |

| OPW_LAST_ | |

| OPW_FIRST_ | |

Definition at line 94 of file AMDGPUDisassembler.h.

Constructor & Destructor Documentation

◆ AMDGPUDisassembler()

|

inline |

Definition at line 50 of file AMDGPUDisassembler.h.

References llvm::Address, convertMIMGInst(), convertSDWAInst(), createRegOperand(), createSRegOperand(), decodeOperand_SReg_128(), decodeOperand_SReg_256(), decodeOperand_SReg_32(), decodeOperand_SReg_32_XEXEC_HI(), decodeOperand_SReg_32_XM0_XEXEC(), decodeOperand_SReg_512(), decodeOperand_SReg_64(), decodeOperand_SReg_64_XEXEC(), decodeOperand_VGPR_32(), decodeOperand_VReg_128(), decodeOperand_VReg_64(), decodeOperand_VReg_96(), decodeOperand_VS_128(), decodeOperand_VS_32(), decodeOperand_VS_64(), decodeOperand_VSrc16(), decodeOperand_VSrcV216(), errOperand(), getInstruction(), getRegClassName(), MI, Size, tryDecodeInst(), and ~AMDGPUDisassembler().

Referenced by createAMDGPUDisassembler().

◆ ~AMDGPUDisassembler()

|

overridedefault |

Referenced by AMDGPUDisassembler().

Member Function Documentation

◆ convertMIMGInst()

| DecodeStatus AMDGPUDisassembler::convertMIMGInst | ( | MCInst & | MI | ) | const |

Definition at line 291 of file AMDGPUDisassembler.cpp.

References assert(), llvm::countPopulation(), llvm::MCOperand::createReg(), llvm::SIInstrFlags::Gather4, llvm::MCOperand::getImm(), llvm::AMDGPU::getMaskedMIMGOp(), llvm::MCRegisterInfo::getMatchingSuperReg(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MCInst::getOpcode(), llvm::MCInst::getOperand(), llvm::MCOperand::getReg(), llvm::MCRegisterInfo::getRegClass(), llvm::MCRegisterInfo::getSubReg(), llvm::AMDGPU::hasPackedD16(), llvm::MCInst::setOpcode(), llvm::MCDisassembler::STI, and llvm::MCDisassembler::Success.

Referenced by AMDGPUDisassembler(), and getInstruction().

◆ convertSDWAInst()

| DecodeStatus AMDGPUDisassembler::convertSDWAInst | ( | MCInst & | MI | ) | const |

Definition at line 269 of file AMDGPUDisassembler.cpp.

References llvm::MCOperand::createImm(), createRegOperand(), llvm::MCSubtargetInfo::getFeatureBits(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MCInst::getOpcode(), insertNamedMCOperand(), llvm::MCDisassembler::STI, and llvm::MCDisassembler::Success.

Referenced by AMDGPUDisassembler(), and getInstruction().

◆ createRegOperand() [1/2]

Definition at line 390 of file AMDGPUDisassembler.cpp.

References llvm::MCOperand::createReg(), llvm::AMDGPU::getMCReg(), and llvm::MCDisassembler::STI.

Referenced by AMDGPUDisassembler(), convertSDWAInst(), createRegOperand(), createSRegOperand(), decodeOperand_VGPR_32(), decodeOperand_VReg_128(), decodeOperand_VReg_64(), decodeOperand_VReg_96(), decodeSDWASrc(), decodeSDWAVopcDst(), decodeSpecialReg32(), decodeSpecialReg64(), and decodeSrcOp().

◆ createRegOperand() [2/2]

Definition at line 395 of file AMDGPUDisassembler.cpp.

References createRegOperand(), errOperand(), and getRegClassName().

◆ createSRegOperand()

Definition at line 405 of file AMDGPUDisassembler.cpp.

References llvm::MCDisassembler::CommentStream, createRegOperand(), getRegClassName(), and llvm_unreachable.

Referenced by AMDGPUDisassembler(), decodeDstOp(), decodeSDWASrc(), decodeSDWAVopcDst(), and decodeSrcOp().

◆ decodeDstOp()

Definition at line 739 of file AMDGPUDisassembler.cpp.

References assert(), createSRegOperand(), getSgprClassId(), getTtmpClassId(), getTTmpIdx(), llvm_unreachable, OPW256, OPW512, llvm::AMDGPU::EncValues::SGPR_MAX, and llvm::AMDGPU::EncValues::SGPR_MIN.

Referenced by decodeOperand_SReg_256(), and decodeOperand_SReg_512().

◆ decodeFPImmed()

Definition at line 624 of file AMDGPUDisassembler.cpp.

References assert(), llvm::MCOperand::createImm(), getInlineImmVal16(), getInlineImmVal32(), getInlineImmVal64(), llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MAX, llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MIN, llvm_unreachable, OPW16, OPW32, OPW64, and OPWV216.

Referenced by decodeSDWASrc(), and decodeSrcOp().

◆ decodeIntImmed()

Definition at line 539 of file AMDGPUDisassembler.cpp.

References assert(), llvm::MCOperand::createImm(), llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MAX, llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MIN, and llvm::AMDGPU::EncValues::INLINE_INTEGER_C_POSITIVE_MAX.

Referenced by decodeSDWASrc(), and decodeSrcOp().

◆ decodeLiteralConstant()

| MCOperand AMDGPUDisassembler::decodeLiteralConstant | ( | ) | const |

Definition at line 524 of file AMDGPUDisassembler.cpp.

References llvm::MCOperand::createImm(), errOperand(), and llvm::ArrayRef< T >::size().

Referenced by decodeSrcOp().

◆ decodeOperand_SReg_128()

Definition at line 512 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW128.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_256()

Definition at line 516 of file AMDGPUDisassembler.cpp.

References decodeDstOp(), and OPW256.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_32()

Definition at line 485 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW32.

Referenced by AMDGPUDisassembler(), decodeOperand_SReg_32_XEXEC_HI(), and decodeOperand_SReg_32_XM0_XEXEC().

◆ decodeOperand_SReg_32_XEXEC_HI()

Definition at line 498 of file AMDGPUDisassembler.cpp.

References decodeOperand_SReg_32().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_32_XM0_XEXEC()

Definition at line 492 of file AMDGPUDisassembler.cpp.

References decodeOperand_SReg_32().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_512()

Definition at line 520 of file AMDGPUDisassembler.cpp.

References decodeDstOp(), and OPW512.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_64()

Definition at line 504 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW64.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_SReg_64_XEXEC()

Definition at line 508 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW64.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VGPR_32()

Definition at line 464 of file AMDGPUDisassembler.cpp.

References createRegOperand().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VReg_128()

Definition at line 481 of file AMDGPUDisassembler.cpp.

References createRegOperand().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VReg_64()

Definition at line 473 of file AMDGPUDisassembler.cpp.

References createRegOperand().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VReg_96()

Definition at line 477 of file AMDGPUDisassembler.cpp.

References createRegOperand().

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VS_128()

Definition at line 452 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW128.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VS_32()

Definition at line 444 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW32.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VS_64()

Definition at line 448 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW64.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VSrc16()

Definition at line 456 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPW16.

Referenced by AMDGPUDisassembler().

◆ decodeOperand_VSrcV216()

Definition at line 460 of file AMDGPUDisassembler.cpp.

References decodeSrcOp(), and OPWV216.

Referenced by AMDGPUDisassembler().

◆ decodeSDWASrc()

Definition at line 805 of file AMDGPUDisassembler.cpp.

References createRegOperand(), createSRegOperand(), decodeFPImmed(), decodeIntImmed(), decodeSpecialReg32(), llvm::MCSubtargetInfo::getFeatureBits(), getSgprClassId(), getTtmpClassId(), getVgprClassId(), llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MAX, llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MIN, llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MAX, llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MIN, llvm_unreachable, SDWA, llvm::AMDGPU::SDWA::SRC_SGPR_MAX, llvm::AMDGPU::SDWA::SRC_SGPR_MIN, llvm::AMDGPU::SDWA::SRC_TTMP_MAX, llvm::AMDGPU::SDWA::SRC_TTMP_MIN, llvm::AMDGPU::SDWA::SRC_VGPR_MAX, llvm::AMDGPU::SDWA::SRC_VGPR_MIN, and llvm::MCDisassembler::STI.

Referenced by decodeSDWASrc16(), and decodeSDWASrc32().

◆ decodeSDWASrc16()

Definition at line 844 of file AMDGPUDisassembler.cpp.

References decodeSDWASrc(), and OPW16.

◆ decodeSDWASrc32()

Definition at line 848 of file AMDGPUDisassembler.cpp.

References decodeSDWASrc(), and OPW32.

◆ decodeSDWAVopcDst()

Definition at line 852 of file AMDGPUDisassembler.cpp.

References assert(), createRegOperand(), createSRegOperand(), decodeSpecialReg64(), llvm::MCSubtargetInfo::getFeatureBits(), getSgprClassId(), getTtmpClassId(), getTTmpIdx(), OPW64, SDWA, llvm::AMDGPU::EncValues::SGPR_MAX, llvm::MCDisassembler::STI, llvm::AMDGPU::SDWA::VOPC_DST_SGPR_MASK, and llvm::AMDGPU::SDWA::VOPC_DST_VCC_MASK.

◆ decodeSpecialReg32()

Definition at line 758 of file AMDGPUDisassembler.cpp.

References assert(), createRegOperand(), errOperand(), and isGFX9().

Referenced by decodeSDWASrc(), and decodeSrcOp().

◆ decodeSpecialReg64()

Definition at line 790 of file AMDGPUDisassembler.cpp.

References assert(), createRegOperand(), errOperand(), and isGFX9().

Referenced by decodeSDWAVopcDst(), and decodeSrcOp().

◆ decodeSrcOp()

Definition at line 700 of file AMDGPUDisassembler.cpp.

References assert(), createRegOperand(), createSRegOperand(), decodeFPImmed(), decodeIntImmed(), decodeLiteralConstant(), decodeSpecialReg32(), decodeSpecialReg64(), getSgprClassId(), getTtmpClassId(), getTTmpIdx(), getVgprClassId(), llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MAX, llvm::AMDGPU::EncValues::INLINE_FLOATING_C_MIN, llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MAX, llvm::AMDGPU::EncValues::INLINE_INTEGER_C_MIN, llvm::AMDGPU::EncValues::LITERAL_CONST, llvm_unreachable, OPW16, OPW32, OPW64, OPWV216, llvm::AMDGPU::EncValues::SGPR_MAX, llvm::AMDGPU::EncValues::SGPR_MIN, llvm::AMDGPU::EncValues::VGPR_MAX, and llvm::AMDGPU::EncValues::VGPR_MIN.

Referenced by decodeOperand_SReg_128(), decodeOperand_SReg_32(), decodeOperand_SReg_64(), decodeOperand_SReg_64_XEXEC(), decodeOperand_VS_128(), decodeOperand_VS_32(), decodeOperand_VS_64(), decodeOperand_VSrc16(), and decodeOperand_VSrcV216().

◆ errOperand()

Definition at line 380 of file AMDGPUDisassembler.cpp.

References llvm::MCDisassembler::CommentStream.

Referenced by AMDGPUDisassembler(), createRegOperand(), decodeLiteralConstant(), decodeSpecialReg32(), and decodeSpecialReg64().

◆ getInstruction()

|

overridevirtual |

Returns the disassembly of a single instruction.

- Parameters

-

Instr - An MCInst to populate with the contents of the instruction. Size - A value to populate with the size of the instruction, or the number of bytes consumed while attempting to decode an invalid instruction. Address - The address, in the memory space of region, of the first byte of the instruction. Bytes - A reference to the actual bytes of the instruction. VStream - The stream to print warnings and diagnostic messages on. CStream - The stream to print comments and annotations on.

- Returns

- - MCDisassembler::Success if the instruction is valid, MCDisassembler::SoftFail if the instruction was disassemblable but invalid, MCDisassembler::Fail if the instruction was invalid.

Implements llvm::MCDisassembler.

Definition at line 171 of file AMDGPUDisassembler.cpp.

References llvm::MCDisassembler::CommentStream, convertMIMGInst(), convertSDWAInst(), llvm::MCOperand::createImm(), llvm::MCDisassembler::Fail, llvm::MCSubtargetInfo::getFeatureBits(), llvm::MCInst::getOpcode(), insertNamedMCOperand(), llvm::SIInstrFlags::MIMG, llvm::report_fatal_error(), llvm::ArrayRef< T >::size(), llvm::ArrayRef< T >::slice(), llvm::MCDisassembler::STI, and tryDecodeInst().

Referenced by AMDGPUDisassembler().

◆ getRegClassName()

Definition at line 374 of file AMDGPUDisassembler.cpp.

References llvm::MCDisassembler::getContext(), and llvm::MCContext::getRegisterInfo().

Referenced by AMDGPUDisassembler(), createRegOperand(), and createSRegOperand().

◆ getSgprClassId()

Definition at line 657 of file AMDGPUDisassembler.cpp.

References assert(), OPW128, OPW16, OPW256, OPW32, OPW512, OPW64, OPW_FIRST_, OPW_LAST_, and OPWV216.

Referenced by decodeDstOp(), decodeSDWASrc(), decodeSDWAVopcDst(), and decodeSrcOp().

◆ getTtmpClassId()

Definition at line 674 of file AMDGPUDisassembler.cpp.

References assert(), OPW128, OPW16, OPW256, OPW32, OPW512, OPW64, OPW_FIRST_, OPW_LAST_, and OPWV216.

Referenced by decodeDstOp(), decodeSDWASrc(), decodeSDWAVopcDst(), and decodeSrcOp().

◆ getTTmpIdx()

| int AMDGPUDisassembler::getTTmpIdx | ( | unsigned | Val | ) | const |

Definition at line 691 of file AMDGPUDisassembler.cpp.

References isGFX9(), llvm::AMDGPU::EncValues::TTMP_GFX9_MAX, llvm::AMDGPU::EncValues::TTMP_GFX9_MIN, llvm::AMDGPU::EncValues::TTMP_VI_MAX, and llvm::AMDGPU::EncValues::TTMP_VI_MIN.

Referenced by decodeDstOp(), decodeSDWAVopcDst(), and decodeSrcOp().

◆ getVgprClassId()

Definition at line 642 of file AMDGPUDisassembler.cpp.

References assert(), OPW128, OPW16, OPW32, OPW64, OPW_FIRST_, OPW_LAST_, and OPWV216.

Referenced by decodeSDWASrc(), and decodeSrcOp().

◆ isGFX9()

| bool AMDGPUDisassembler::isGFX9 | ( | ) | const |

Definition at line 877 of file AMDGPUDisassembler.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), and llvm::MCDisassembler::STI.

Referenced by decodeSpecialReg32(), decodeSpecialReg64(), and getTTmpIdx().

◆ isVI()

| bool AMDGPUDisassembler::isVI | ( | ) | const |

Definition at line 873 of file AMDGPUDisassembler.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), and llvm::MCDisassembler::STI.

◆ tryDecodeInst()

| DecodeStatus AMDGPUDisassembler::tryDecodeInst | ( | const uint8_t * | Table, |

| MCInst & | MI, | ||

| uint64_t | Inst, | ||

| uint64_t | Address | ||

| ) | const |

Definition at line 154 of file AMDGPUDisassembler.cpp.

References assert(), llvm::X86Disassembler::decodeInstruction(), llvm::MCDisassembler::Fail, llvm::MCInst::getNumOperands(), llvm::MCInst::getOpcode(), llvm::MCDisassembler::STI, and llvm::MCDisassembler::Success.

Referenced by AMDGPUDisassembler(), and getInstruction().

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/Disassembler/AMDGPUDisassembler.h

- lib/Target/AMDGPU/Disassembler/AMDGPUDisassembler.cpp

1.8.13

1.8.13