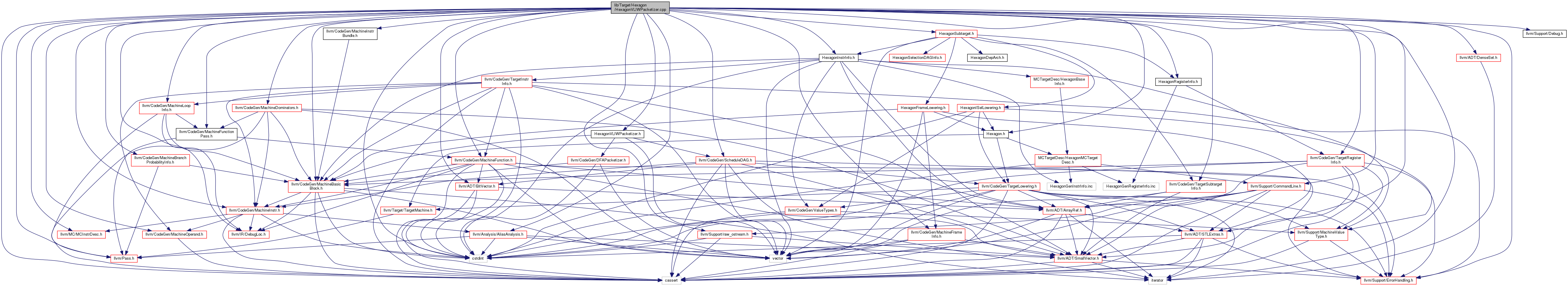

#include "HexagonVLIWPacketizer.h"#include "Hexagon.h"#include "HexagonInstrInfo.h"#include "HexagonRegisterInfo.h"#include "HexagonSubtarget.h"#include "llvm/ADT/BitVector.h"#include "llvm/ADT/DenseSet.h"#include "llvm/ADT/STLExtras.h"#include "llvm/Analysis/AliasAnalysis.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineBranchProbabilityInfo.h"#include "llvm/CodeGen/MachineDominators.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBundle.h"#include "llvm/CodeGen/MachineLoopInfo.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/ScheduleDAG.h"#include "llvm/CodeGen/TargetRegisterInfo.h"#include "llvm/CodeGen/TargetSubtargetInfo.h"#include "llvm/IR/DebugLoc.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/Pass.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/raw_ostream.h"#include <cassert>#include <cstdint>#include <iterator>

Go to the source code of this file.

Namespaces | |

| llvm | |

| This class represents lattice values for constants. | |

Macros | |

| #define | DEBUG_TYPE "packets" |

Enumerations | |

| enum | PredicateKind { PK_False, PK_True, PK_Unknown } |

Variables | |

| static cl::opt< bool > | DisablePacketizer ("disable-packetizer", cl::Hidden, cl::ZeroOrMore, cl::init(false), cl::desc("Disable Hexagon packetizer pass")) |

| cl::opt< bool > | Slot1Store ("slot1-store-slot0-load", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Allow slot1 store and slot0 load")) |

| static cl::opt< bool > | PacketizeVolatiles ("hexagon-packetize-volatiles", cl::ZeroOrMore, cl::Hidden, cl::init(true), cl::desc("Allow non-solo packetization of volatile memory references")) |

| static cl::opt< bool > | EnableGenAllInsnClass ("enable-gen-insn", cl::init(false), cl::Hidden, cl::ZeroOrMore, cl::desc("Generate all instruction with TC")) |

| static cl::opt< bool > | DisableVecDblNVStores ("disable-vecdbl-nv-stores", cl::init(false), cl::Hidden, cl::ZeroOrMore, cl::desc("Disable vector double new-value-stores")) |

| cl::opt< bool > | ScheduleInlineAsm |

| hexagon | packetizer |

| hexagon Hexagon | Packetizer |

| hexagon Hexagon | false |

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "packets" |

Definition at line 55 of file HexagonVLIWPacketizer.cpp.

Enumeration Type Documentation

◆ PredicateKind

| enum PredicateKind |

| Enumerator | |

|---|---|

| PK_False | |

| PK_True | |

| PK_Unknown | |

Definition at line 551 of file HexagonVLIWPacketizer.cpp.

Function Documentation

◆ cannotCoexistAsymm()

|

static |

Definition at line 1093 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineFunction::getSubtarget(), llvm::HexagonInstrInfo::getType(), llvm::HexagonSubtarget::hasV60OpsOnly(), llvm::MachineInstr::isBarrier(), llvm::MachineInstr::isBranch(), llvm::MachineInstr::isCall(), llvm::HexagonInstrInfo::isHVXMemWithAIndirect(), llvm::MachineInstr::isInlineAsm(), llvm::HexagonInstrInfo::isNewValueStore(), llvm::MachineInstr::isTerminator(), llvm::MachineInstr::mayStore(), llvm::HexagonII::TypeALU32_2op, llvm::HexagonII::TypeALU32_3op, and llvm::HexagonII::TypeALU32_ADDI.

Referenced by llvm::HexagonPacketizerList::cannotCoexist().

◆ doesModifyCalleeSavedReg()

|

static |

Returns true if the instruction modifies a callee-saved register.

Definition at line 341 of file HexagonVLIWPacketizer.cpp.

References llvm::TargetRegisterInfo::getCalleeSavedRegs(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), and llvm::MachineInstr::modifiesRegister().

Referenced by llvm::HexagonPacketizerList::hasControlDependence().

◆ getAbsSetOperand()

|

static |

Definition at line 621 of file HexagonVLIWPacketizer.cpp.

References assert(), llvm::MachineInstr::getOperand(), and isLoadAbsSet().

Referenced by llvm::HexagonPacketizerList::canPromoteToNewValueStore().

◆ getPostIncrementOperand()

|

static |

Definition at line 568 of file HexagonVLIWPacketizer.cpp.

References assert(), llvm::MachineInstr::getDesc(), llvm::MachineInstr::getOperand(), llvm::detail::DenseSetImpl< ValueT, MapTy, ValueInfoT >::insert(), llvm::HexagonInstrInfo::isPostIncrement(), llvm::MachineOperand::isReg(), llvm_unreachable, llvm::MachineInstr::mayLoad(), llvm::MCInstrDesc::mayStore(), and llvm::MachineInstr::operands().

Referenced by llvm::HexagonPacketizerList::canPromoteToNewValueStore().

◆ getPredicatedRegister()

|

static |

Gets the predicate register of a predicated instruction.

We use the following rule: The first predicate register that is a use is the predicate register of a predicated instruction.

Definition at line 940 of file HexagonVLIWPacketizer.cpp.

References assert(), llvm::HexagonInstrInfo::isPredicated(), llvm_unreachable, and llvm::MachineInstr::operands().

Referenced by llvm::HexagonPacketizerList::arePredicatesComplements().

◆ getPredicateSense()

|

static |

Returns true if an instruction is predicated on p0 and false if it's predicated on !p0.

Definition at line 559 of file HexagonVLIWPacketizer.cpp.

References llvm::HexagonInstrInfo::isPredicated(), llvm::HexagonInstrInfo::isPredicatedTrue(), PK_False, PK_True, and PK_Unknown.

Referenced by llvm::HexagonPacketizerList::arePredicatesComplements(), and llvm::HexagonPacketizerList::canPromoteToNewValueStore().

◆ getStoreValueOperand()

|

static |

Definition at line 602 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getNumOperands(), and llvm::MachineInstr::getOperand().

Referenced by llvm::HexagonPacketizerList::canPromoteToNewValueStore().

◆ hasWriteToReadDep()

|

static |

Definition at line 146 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::operands(), and llvm::MachineInstr::readsRegister().

Referenced by llvm::HexagonPacketizerList::unpacketizeSoloInstrs().

◆ INITIALIZE_PASS_BEGIN()

| INITIALIZE_PASS_BEGIN | ( | HexagonPacketizer | , |

| "hexagon-packetizer" | , | ||

| "Hexagon Packetizer" | , | ||

| false | , | ||

| false | |||

| ) |

◆ isControlFlow()

|

static |

Definition at line 336 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::isCall(), and llvm::MCInstrDesc::isTerminator().

Referenced by llvm::HexagonPacketizerList::hasControlDependence().

◆ isDirectJump()

|

static |

Definition at line 324 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by llvm::HexagonPacketizerList::isLegalToPacketizeTogether().

◆ isImplicitDependency()

|

static |

Definition at line 828 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::operands().

Referenced by llvm::HexagonPacketizerList::canPromoteToDotNew().

◆ isLoadAbsSet()

|

static |

Definition at line 607 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by llvm::HexagonPacketizerList::canPromoteToNewValueStore(), and getAbsSetOperand().

◆ isRegDependence()

|

static |

Definition at line 319 of file HexagonVLIWPacketizer.cpp.

References llvm::SDep::Anti, llvm::SDep::Data, and llvm::SDep::Output.

Referenced by llvm::HexagonPacketizerList::isLegalToPacketizeTogether().

◆ isSchedBarrier()

|

static |

Definition at line 328 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by llvm::HexagonPacketizerList::isSoloInstruction().

◆ isSystemInstr()

|

static |

Definition at line 1180 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by llvm::HexagonPacketizerList::hasDualStoreDependence().

◆ moveInstrOut()

|

static |

Definition at line 160 of file HexagonVLIWPacketizer.cpp.

References assert(), B, llvm::MachineInstr::BundledPred, llvm::MachineInstr::BundledSucc, llvm::MachineInstr::clearFlag(), DisablePacketizer, E, EnableGenAllInsnClass, llvm::MachineFunction::getFunction(), llvm::HexagonSubtarget::getInstrInfo(), llvm::MachineInstrBundleIterator< Ty, IsReverse >::getInstrIterator(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineInstr::getParent(), llvm::MachineFunction::getSubtarget(), I, llvm::MachineBasicBlock::instr_end(), llvm::MachineInstr::isBundledWithPred(), llvm::MachineInstr::isBundledWithSucc(), Packetizer, Size, llvm::MachineBasicBlock::splice(), and llvm::MachineInstr::unbundleFromPred().

Referenced by llvm::HexagonPacketizerList::unpacketizeSoloInstrs().

Variable Documentation

◆ DisablePacketizer

|

static |

Referenced by moveInstrOut().

◆ DisableVecDblNVStores

|

static |

Referenced by llvm::HexagonPacketizerList::canPromoteToDotNew().

◆ EnableGenAllInsnClass

|

static |

Referenced by moveInstrOut().

◆ false

| hexagon Hexagon false |

Definition at line 129 of file HexagonVLIWPacketizer.cpp.

◆ packetizer

| hexagon packetizer |

Definition at line 129 of file HexagonVLIWPacketizer.cpp.

◆ Packetizer

| hexagon Hexagon Packetizer |

Definition at line 129 of file HexagonVLIWPacketizer.cpp.

Referenced by moveInstrOut().

◆ PacketizeVolatiles

|

static |

Referenced by llvm::HexagonPacketizerList::isLegalToPacketizeTogether().

◆ ScheduleInlineAsm

◆ Slot1Store

| cl::opt<bool> Slot1Store("slot1-store-slot0-load", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Allow slot1 store and slot0 load")) |

Referenced by llvm::HexagonPacketizerList::isLegalToPacketizeTogether().

1.8.13

1.8.13