#include "llvm/MC/MCInstrAnalysis.h"

Public Member Functions | |

| MCInstrAnalysis (const MCInstrInfo *Info) | |

| virtual | ~MCInstrAnalysis ()=default |

| virtual bool | isBranch (const MCInst &Inst) const |

| virtual bool | isConditionalBranch (const MCInst &Inst) const |

| virtual bool | isUnconditionalBranch (const MCInst &Inst) const |

| virtual bool | isIndirectBranch (const MCInst &Inst) const |

| virtual bool | isCall (const MCInst &Inst) const |

| virtual bool | isReturn (const MCInst &Inst) const |

| virtual bool | isTerminator (const MCInst &Inst) const |

| virtual bool | clearsSuperRegisters (const MCRegisterInfo &MRI, const MCInst &Inst, APInt &Writes) const |

| Returns true if at least one of the register writes performed by. More... | |

| virtual bool | isZeroIdiom (const MCInst &MI, APInt &Mask, unsigned CPUID) const |

| Returns true if MI is a dependency breaking zero-idiom for the given subtarget. More... | |

| virtual bool | isDependencyBreaking (const MCInst &MI, APInt &Mask, unsigned CPUID) const |

| Returns true if MI is a dependency breaking instruction for the subtarget associated with CPUID . More... | |

| virtual bool | isOptimizableRegisterMove (const MCInst &MI, unsigned CPUID) const |

| Returns true if MI is a candidate for move elimination. More... | |

| virtual bool | evaluateBranch (const MCInst &Inst, uint64_t Addr, uint64_t Size, uint64_t &Target) const |

| Given a branch instruction try to get the address the branch targets. More... | |

| virtual std::vector< std::pair< uint64_t, uint64_t > > | findPltEntries (uint64_t PltSectionVA, ArrayRef< uint8_t > PltContents, uint64_t GotPltSectionVA, const Triple &TargetTriple) const |

| Returns (PLT virtual address, GOT virtual address) pairs for PLT entries. More... | |

Protected Attributes | |

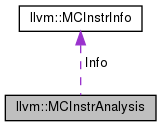

| const MCInstrInfo * | Info |

Friends | |

| class | Target |

Detailed Description

Definition at line 28 of file MCInstrAnalysis.h.

Constructor & Destructor Documentation

◆ MCInstrAnalysis()

|

inline |

Definition at line 35 of file MCInstrAnalysis.h.

References ~MCInstrAnalysis().

◆ ~MCInstrAnalysis()

|

virtualdefault |

Referenced by MCInstrAnalysis().

Member Function Documentation

◆ clearsSuperRegisters()

|

virtual |

Returns true if at least one of the register writes performed by.

- Parameters

-

Inst implicitly clears the upper portion of all super-registers.

Example: on X86-64, a write to EAX implicitly clears the upper half of RAX. Also (still on x86) an XMM write perfomed by an AVX 128-bit instruction implicitly clears the upper portion of the correspondent YMM register.

This method also updates an APInt which is used as mask of register writes. There is one bit for every explicit/implicit write performed by the instruction. If a write implicitly clears its super-registers, then the corresponding bit is set (vic. the corresponding bit is cleared).

The first bits in the APint are related to explicit writes. The remaining bits are related to implicit writes. The sequence of writes follows the machine operand sequence. For implicit writes, the sequence is defined by the MCInstrDesc.

The assumption is that the bit-width of the APInt is correctly set by the caller. The default implementation conservatively assumes that none of the writes clears the upper portion of a super-register.

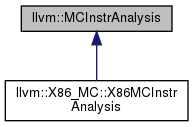

Reimplemented in llvm::X86_MC::X86MCInstrAnalysis.

Definition at line 20 of file MCInstrAnalysis.cpp.

References llvm::APInt::clearAllBits().

Referenced by llvm::mca::InstrBuilder::createInstruction(), and isTerminator().

◆ evaluateBranch()

|

virtual |

Given a branch instruction try to get the address the branch targets.

Return true on success, and the address in Target.

Definition at line 27 of file MCInstrAnalysis.cpp.

References llvm::MCInstrInfo::get(), llvm::MCOperand::getImm(), llvm::MCInst::getNumOperands(), llvm::MCInst::getOpcode(), llvm::MCInst::getOperand(), Info, and llvm::MCOI::OPERAND_PCREL.

Referenced by isOptimizableRegisterMove().

◆ findPltEntries()

|

inlinevirtual |

Returns (PLT virtual address, GOT virtual address) pairs for PLT entries.

Reimplemented in llvm::X86_MC::X86MCInstrAnalysis.

Definition at line 158 of file MCInstrAnalysis.h.

◆ isBranch()

Definition at line 38 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

◆ isCall()

Definition at line 54 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

◆ isConditionalBranch()

Definition at line 42 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

Referenced by createARMMCRelocationInfo(), and llvm::Hexagon_MC::GetELFFlags().

◆ isDependencyBreaking()

|

inlinevirtual |

Returns true if MI is a dependency breaking instruction for the subtarget associated with CPUID .

The value computed by a dependency breaking instruction is not dependent on the inputs. An example of dependency breaking instruction on X86 is XOR eax, eax.

If MI is a dependency breaking instruction for subtarget CPUID, then Mask can be inspected to identify independent operands.

Essentially, each bit of the mask corresponds to an input operand. Explicit operands are laid out first in the mask; implicit operands follow explicit operands. Bits are set for operands that are independent.

Note that the number of bits in Mask may not be equivalent to the sum of explicit and implicit operands in MI. Operands that don't have a corresponding bit in Mask are assumed "not independente".

The only exception is for when Mask is all zeroes. That means: explicit input operands of MI are independent.

Definition at line 134 of file MCInstrAnalysis.h.

References isZeroIdiom().

Referenced by llvm::mca::InstrBuilder::createInstruction().

◆ isIndirectBranch()

Definition at line 50 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

◆ isOptimizableRegisterMove()

|

inlinevirtual |

Returns true if MI is a candidate for move elimination.

Different subtargets may apply different constraints to optimizable register moves. For example, on most X86 subtargets, a candidate for move elimination cannot specify the same register for both source and destination.

Definition at line 145 of file MCInstrAnalysis.h.

References evaluateBranch(), and Size.

Referenced by llvm::mca::InstrBuilder::createInstruction().

◆ isReturn()

Definition at line 58 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

◆ isTerminator()

Definition at line 62 of file MCInstrAnalysis.h.

References clearsSuperRegisters(), llvm::MCInstrInfo::get(), llvm::MCInst::getOpcode(), and MRI.

◆ isUnconditionalBranch()

|

inlinevirtual |

Definition at line 46 of file MCInstrAnalysis.h.

References llvm::MCInstrInfo::get(), and llvm::MCInst::getOpcode().

Referenced by createARMMCRelocationInfo(), and llvm::Hexagon_MC::GetELFFlags().

◆ isZeroIdiom()

|

inlinevirtual |

Returns true if MI is a dependency breaking zero-idiom for the given subtarget.

Mask is used to identify input operands that have their dependency broken. Each bit of the mask is associated with a specific input operand. Bits associated with explicit input operands are laid out first in the mask; implicit operands come after explicit operands.

Dependencies are broken only for operands that have their corresponding bit set. Operands that have their bit cleared, or that don't have a corresponding bit in the mask don't have their dependency broken. Note that Mask may not be big enough to describe all operands. The assumption for operands that don't have a correspondent bit in the mask is that those are still data dependent.

The only exception to the rule is for when Mask has all zeroes. A zero mask means: dependencies are broken for all explicit register operands.

Definition at line 109 of file MCInstrAnalysis.h.

Referenced by llvm::mca::InstrBuilder::createInstruction(), and isDependencyBreaking().

Friends And Related Function Documentation

◆ Target

|

friend |

Definition at line 30 of file MCInstrAnalysis.h.

Member Data Documentation

◆ Info

|

protected |

Definition at line 32 of file MCInstrAnalysis.h.

Referenced by llvm::X86_MC::X86MCInstrAnalysis::clearsSuperRegisters(), and evaluateBranch().

The documentation for this class was generated from the following files:

- include/llvm/MC/MCInstrAnalysis.h

- lib/MC/MCInstrAnalysis.cpp

1.8.13

1.8.13