The SI code emitter produces machine code that can be executed directly on the GPU device. More...

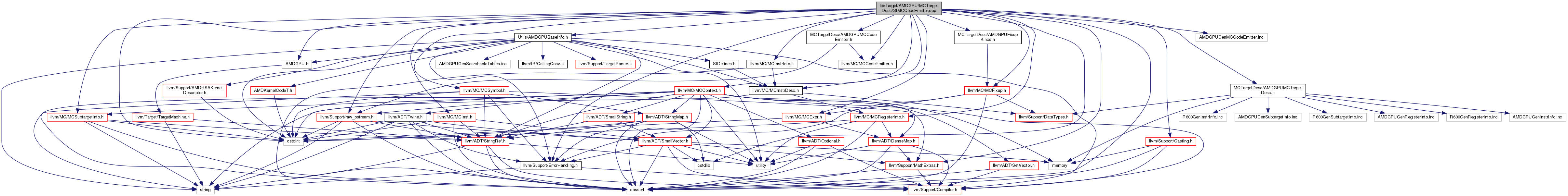

#include "AMDGPU.h"#include "MCTargetDesc/AMDGPUFixupKinds.h"#include "MCTargetDesc/AMDGPUMCCodeEmitter.h"#include "MCTargetDesc/AMDGPUMCTargetDesc.h"#include "Utils/AMDGPUBaseInfo.h"#include "llvm/MC/MCCodeEmitter.h"#include "llvm/MC/MCContext.h"#include "llvm/MC/MCExpr.h"#include "llvm/MC/MCFixup.h"#include "llvm/MC/MCInst.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/MC/MCInstrInfo.h"#include "llvm/MC/MCRegisterInfo.h"#include "llvm/MC/MCSubtargetInfo.h"#include "llvm/MC/MCSymbol.h"#include "llvm/Support/Casting.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/MathExtras.h"#include "llvm/Support/raw_ostream.h"#include <cassert>#include <cstdint>#include <cstdlib>#include "AMDGPUGenMCCodeEmitter.inc"

Go to the source code of this file.

Macros | |

| #define | ENABLE_INSTR_PREDICATE_VERIFIER |

Functions | |

| template<typename IntTy > | |

| static uint32_t | getIntInlineImmEncoding (IntTy Imm) |

| static uint32_t | getLit16Encoding (uint16_t Val, const MCSubtargetInfo &STI) |

| static uint32_t | getLit32Encoding (uint32_t Val, const MCSubtargetInfo &STI) |

| static uint32_t | getLit64Encoding (uint64_t Val, const MCSubtargetInfo &STI) |

| static bool | needsPCRel (const MCExpr *Expr) |

Detailed Description

The SI code emitter produces machine code that can be executed directly on the GPU device.

Definition in file SIMCCodeEmitter.cpp.

Macro Definition Documentation

◆ ENABLE_INSTR_PREDICATE_VERIFIER

| #define ENABLE_INSTR_PREDICATE_VERIFIER |

Definition at line 442 of file SIMCCodeEmitter.cpp.

Function Documentation

◆ getIntInlineImmEncoding()

|

static |

Definition at line 93 of file SIMCCodeEmitter.cpp.

References llvm::abs().

Referenced by getLit16Encoding(), getLit32Encoding(), and getLit64Encoding().

◆ getLit16Encoding()

|

static |

Definition at line 103 of file SIMCCodeEmitter.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), and getIntInlineImmEncoding().

Referenced by getLit64Encoding().

◆ getLit32Encoding()

|

static |

Definition at line 139 of file SIMCCodeEmitter.cpp.

References llvm::FloatToBits(), llvm::MCSubtargetInfo::getFeatureBits(), and getIntInlineImmEncoding().

Referenced by getLit64Encoding().

◆ getLit64Encoding()

|

static |

Definition at line 175 of file SIMCCodeEmitter.cpp.

References assert(), C, llvm::MCFixup::create(), llvm::DoubleToBits(), llvm::dyn_cast(), llvm::AMDGPU::fixup_si_sopp_br, llvm::MCOperand::getExpr(), llvm::MCSubtargetInfo::getFeatureBits(), llvm::MCOperand::getImm(), getIntInlineImmEncoding(), getLit16Encoding(), getLit32Encoding(), llvm::MCInst::getLoc(), llvm::MCInstrDesc::getNumOperands(), llvm::MCInst::getOpcode(), llvm::MCInst::getOperand(), llvm::MCOperand::getReg(), llvm::MCInstrDesc::getSize(), llvm::MCOperand::isExpr(), llvm::MCOperand::isFPImm(), llvm::MCOperand::isImm(), llvm::MCOperand::isReg(), llvm::AMDGPU::isSGPR(), llvm::AMDGPU::isSISrcOperand(), Kind, llvm_unreachable, llvm::AMDGPU::mc2PseudoReg(), MI, MRI, llvm::AMDGPU::OPERAND_REG_IMM_FP16, llvm::AMDGPU::OPERAND_REG_IMM_FP32, llvm::AMDGPU::OPERAND_REG_IMM_FP64, llvm::AMDGPU::OPERAND_REG_IMM_INT16, llvm::AMDGPU::OPERAND_REG_IMM_INT32, llvm::AMDGPU::OPERAND_REG_IMM_INT64, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP16, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP32, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP64, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT16, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT32, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT64, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2FP16, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2INT16, llvm::MCOperandInfo::OperandType, llvm::MCInstrDesc::OpInfo, llvm::SmallVectorTemplateBase< T >::push_back(), Reg, SDWA, llvm::AMDGPU::SDWA::SRC_SGPR_MASK, llvm::AMDGPU::SDWA::SRC_VGPR_MASK, llvm::AMDGPU::SDWA::VOPC_DST_SGPR_MASK, llvm::AMDGPU::SDWA::VOPC_DST_VCC_MASK, and llvm::raw_ostream::write().

◆ needsPCRel()

Definition at line 377 of file SIMCCodeEmitter.cpp.

References llvm::MCExpr::Binary, llvm::MCExpr::Constant, llvm::MCFixup::create(), llvm::FK_Data_4, llvm::FK_PCRel_4, llvm::MCOperand::getExpr(), llvm::MCOperand::getImm(), llvm::MCExpr::getKind(), llvm::MCInst::getLoc(), llvm::MCInst::getNumOperands(), llvm::MCInst::getOpcode(), llvm::MCInst::getOperand(), llvm::MCOperand::getReg(), llvm::MCInstrDesc::getSize(), llvm::MCOperand::isExpr(), llvm::MCOperand::isImm(), llvm::MCOperand::isReg(), llvm::AMDGPU::isSISrcOperand(), Kind, llvm_unreachable, MRI, llvm::MCInstrDesc::OpInfo, llvm::SmallVectorTemplateBase< T >::push_back(), llvm::MCBinaryExpr::Sub, llvm::MCExpr::SymbolRef, llvm::MCExpr::Target, and llvm::MCExpr::Unary.

1.8.13

1.8.13